Patents

Literature

81results about How to "More complex" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

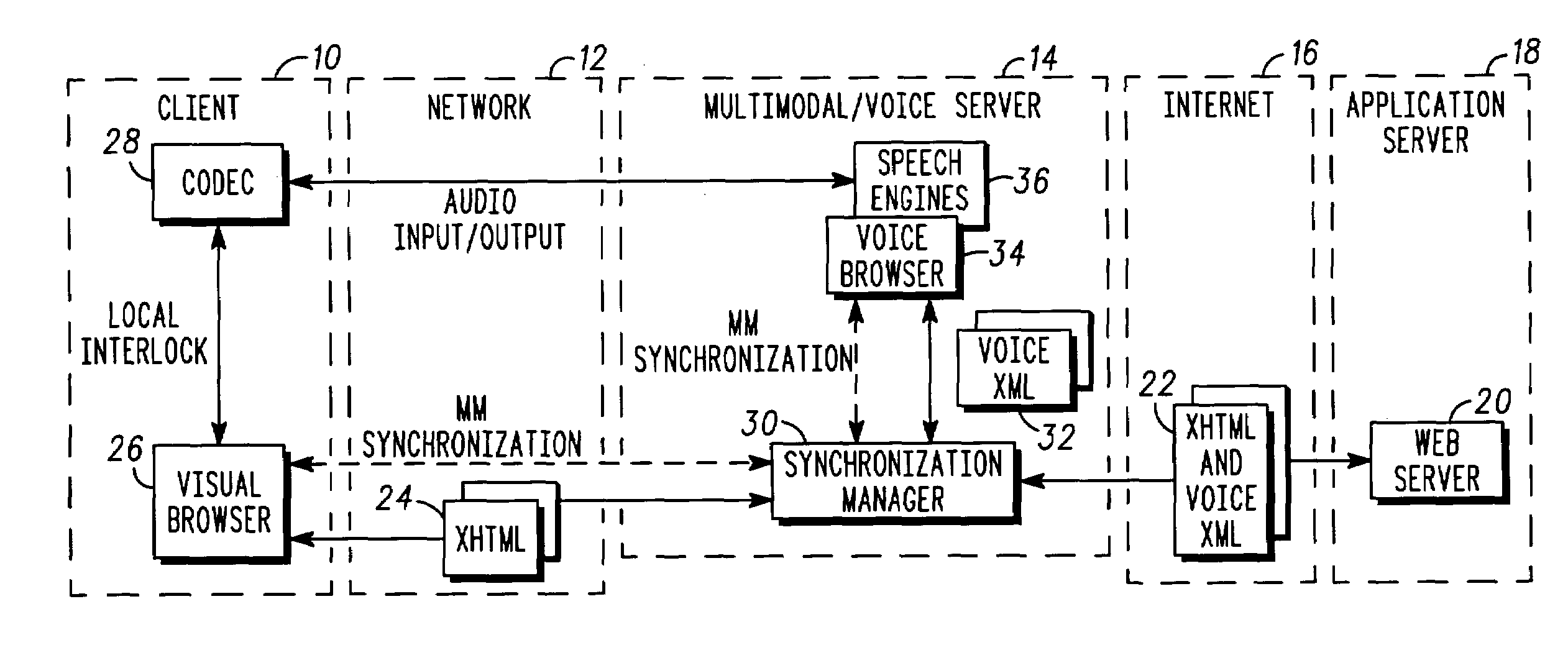

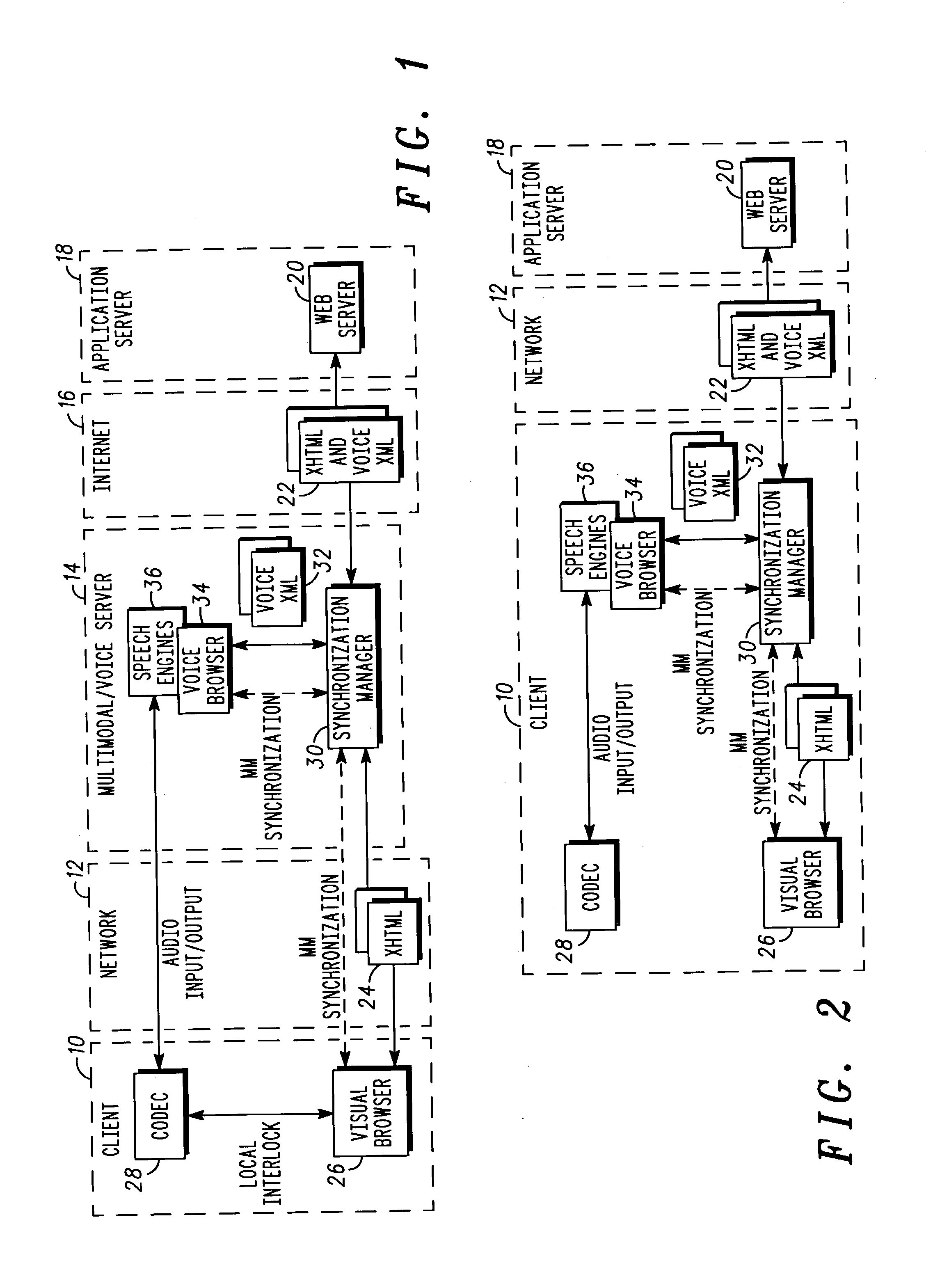

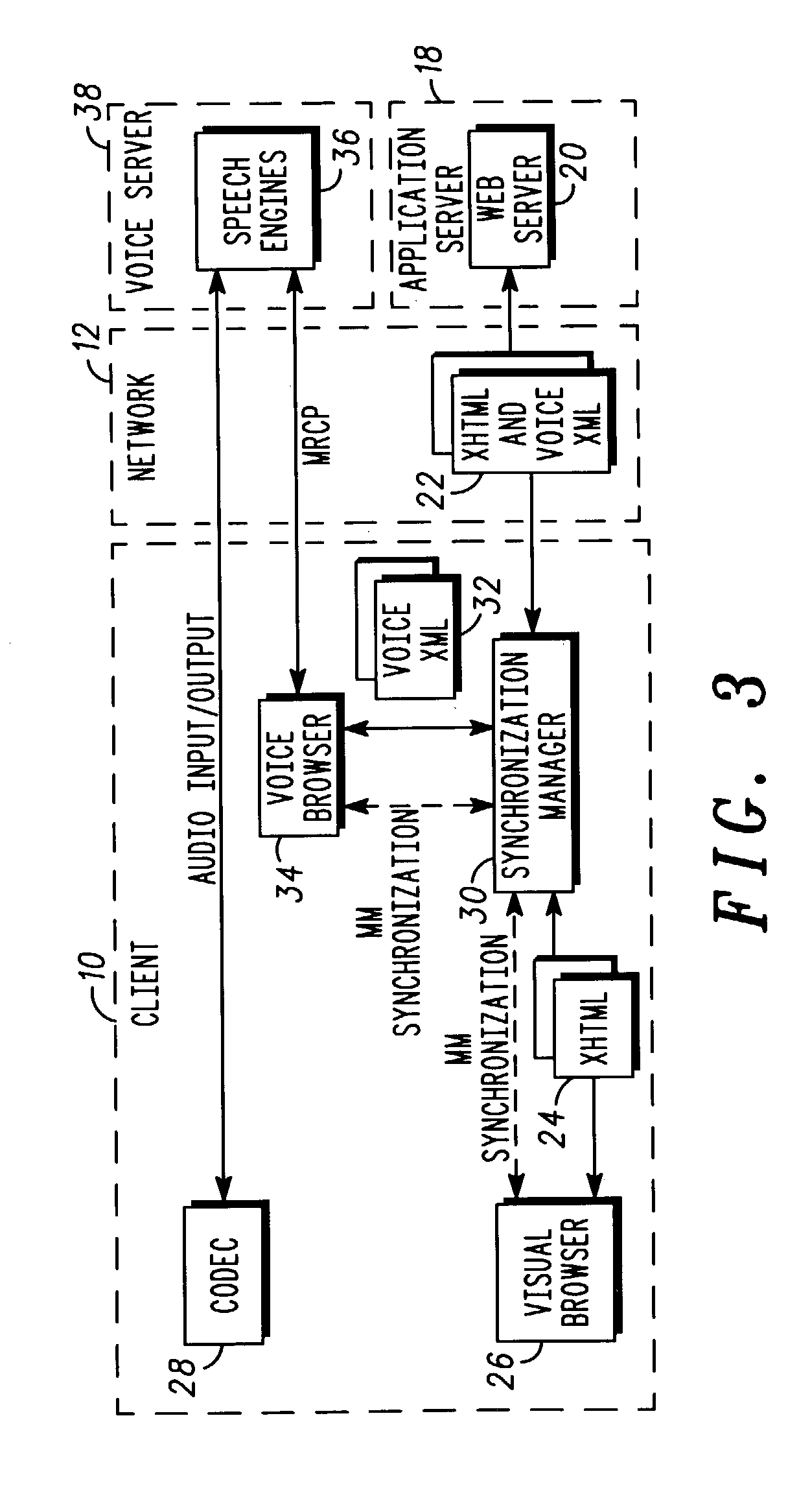

Dialog recognition and control in a voice browser

ActiveUS7003464B2Low costQuantity minimizationDevices with voice recognitionDigital computer detailsDocumentationSpeech sound

A voice browser dialog enabler for multimodal dialog uses a multimodal markup document with fields have markup-based forms associated with each field and defining fragments. A voice browser driver resides on a communication device and provides the fragments and identifiers that identify the fragments. A voice browser implementation resides on a remote voice server and receives the fragments from the driver and downloads a plurality of speech grammars. Input speech is matched against those speech grammars associated with the corresponding identifiers received in a recognition request from the voice browser driver.

Owner:GOOGLE TECH HLDG LLC

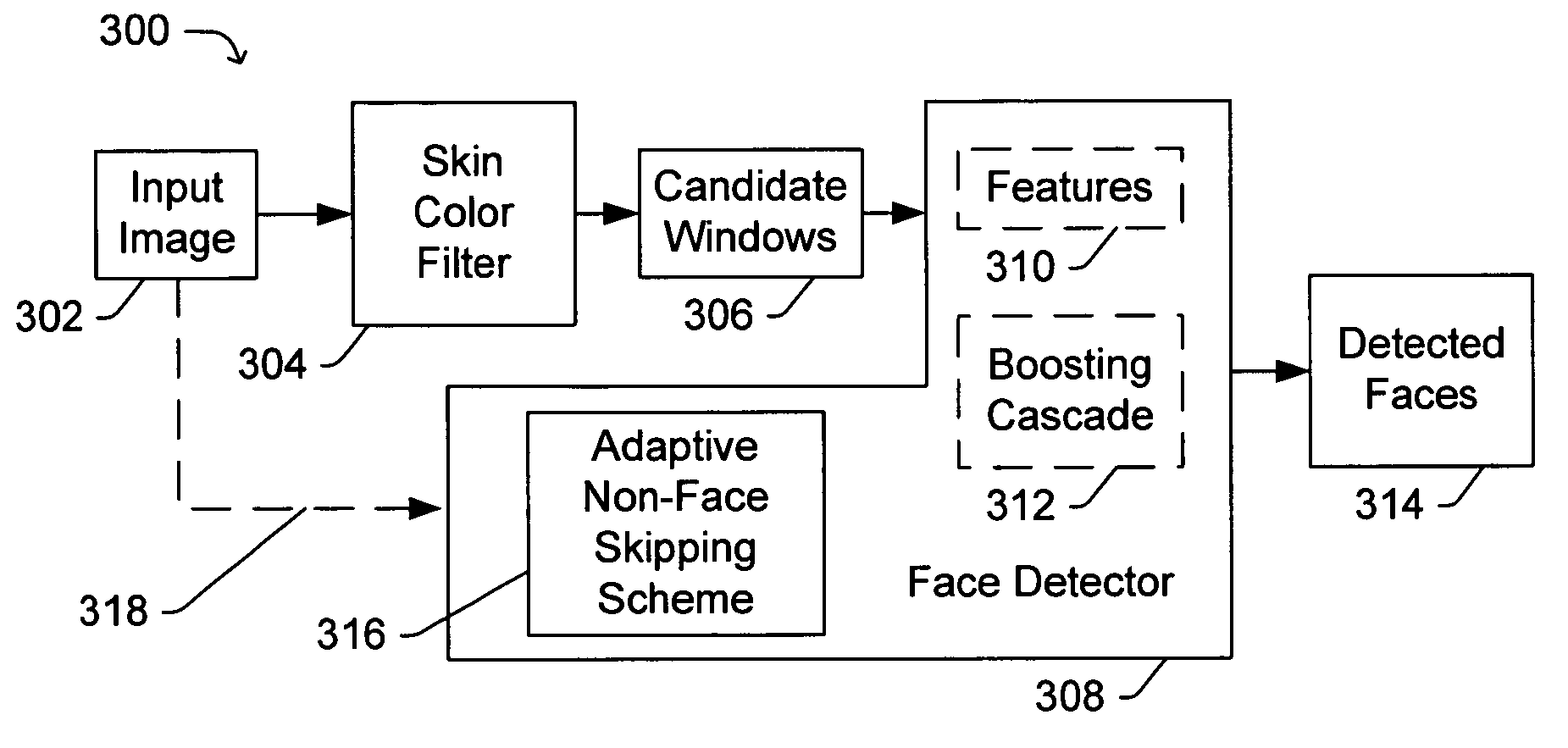

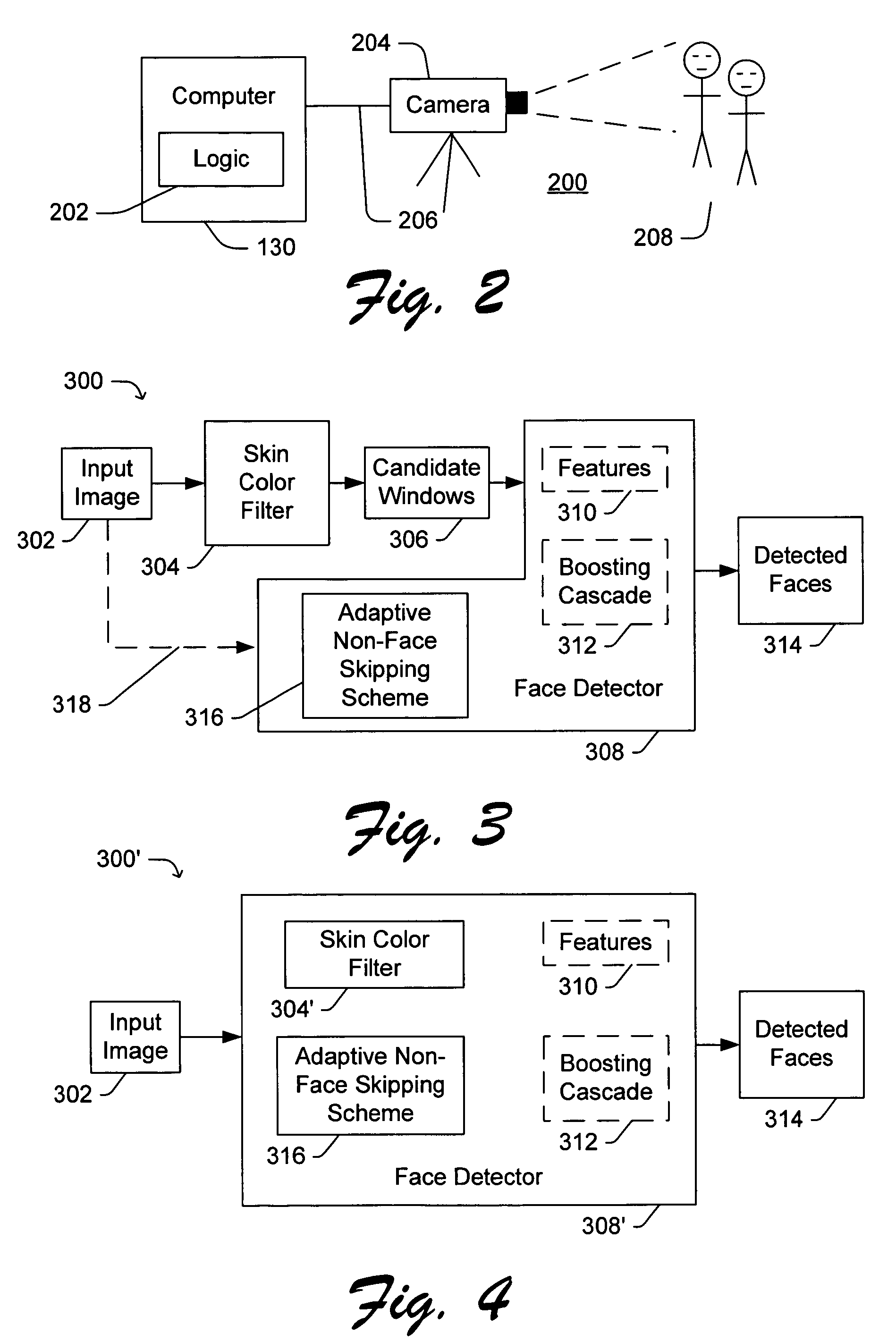

Speedup of face detection in digital images

ActiveUS7190829B2Increase face detection speedReduce in quantityCharacter and pattern recognitionFace detectionSkin color

Improved methods and apparatuses are provided for use in face detection. The methods and apparatuses significantly reduce the number of candidate windows within a digital image that need to be processed using more complex and / or time consuming face detection algorithms. The improved methods and apparatuses include a skin color filter and an adaptive non-face skipping scheme.

Owner:MICROSOFT TECH LICENSING LLC

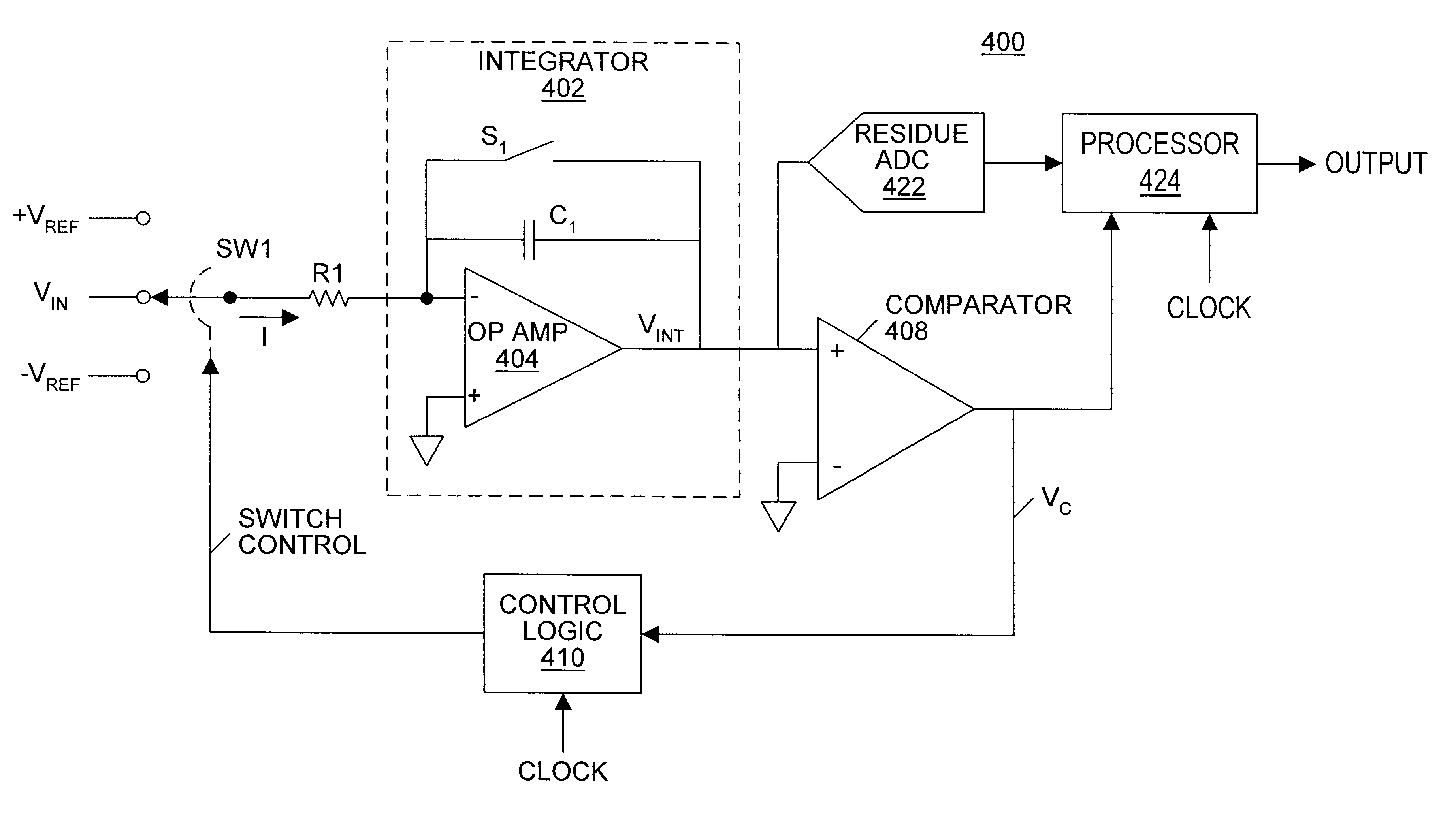

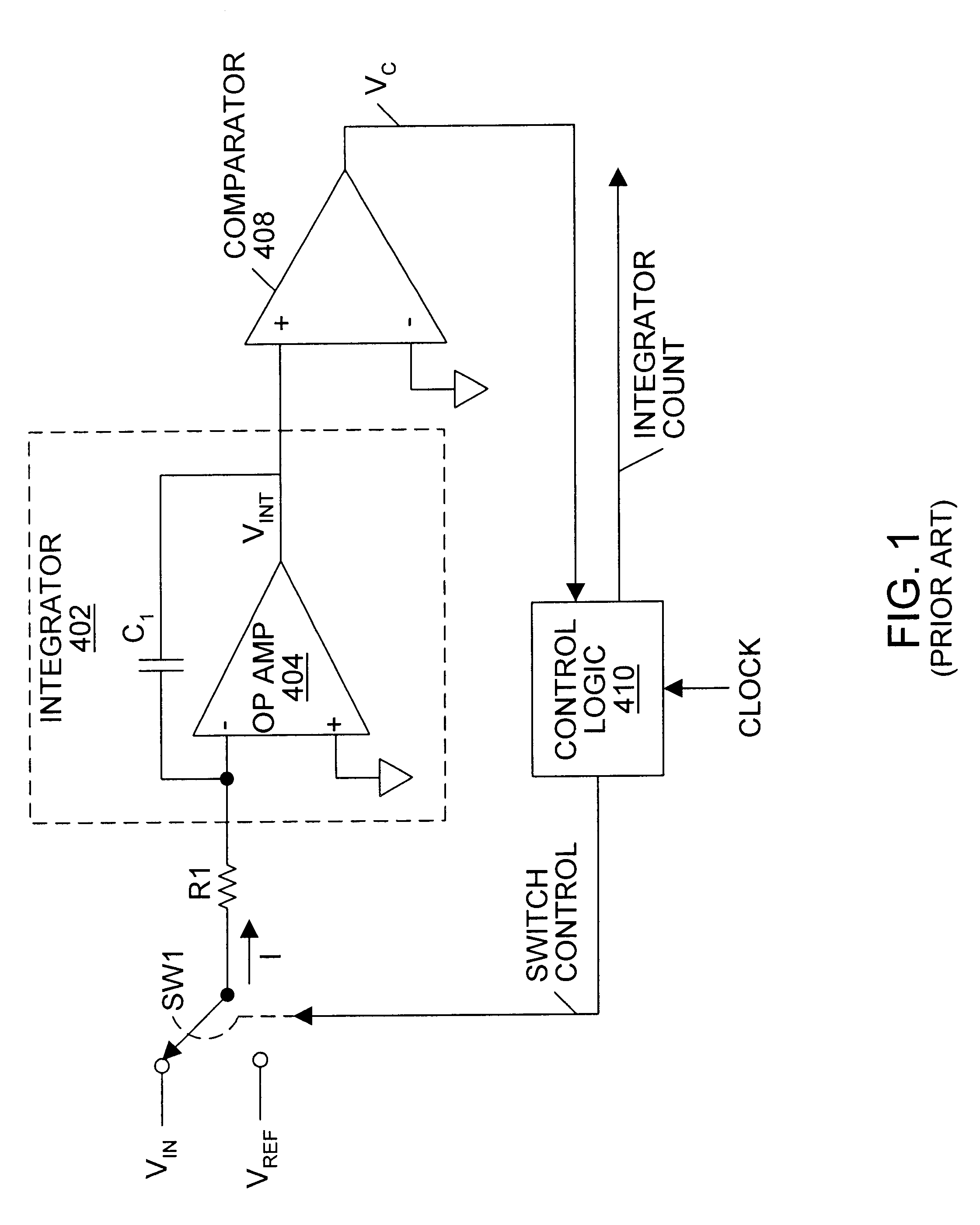

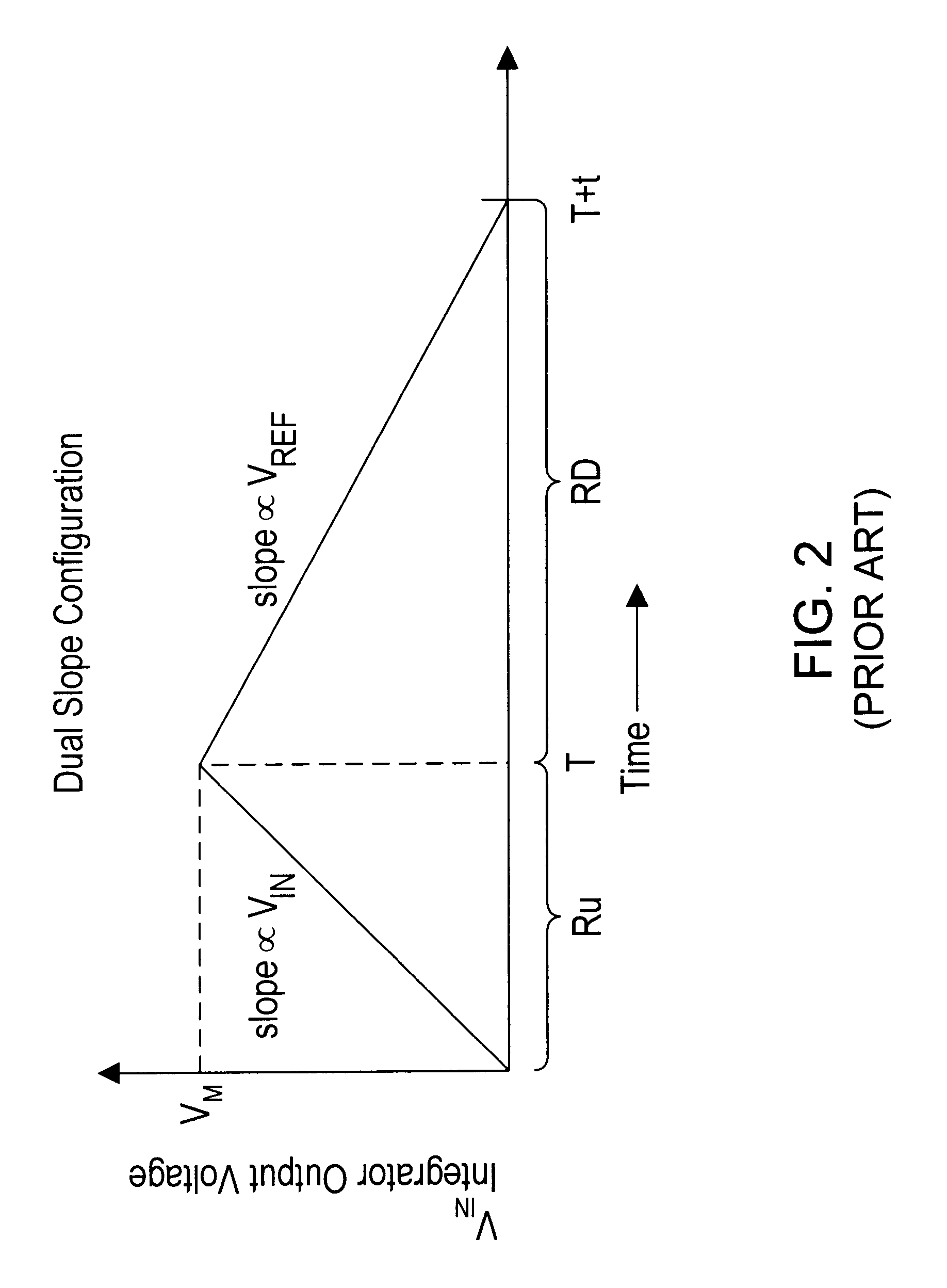

Integrating analog to digital converter with improved resolution

InactiveUS6243034B1More complexImprovements in resolution-speed tradeoffElectric signal transmission systemsAnalogue-digital convertersA d converterNumeric Value

An analog to digital (A / D) converter system and method which provides improved resolution and reduced noise for integrating-type ADCs, including dual slope, multi slope, and sigma-delta type A / D converters. After the ramp-up interval of either a dual slope or multi slope integrating A / D converter, the ramp-down interval occurs, wherein a reference signal is then applied to the integrator to return the integrator to its original value. The clock cycles are counted while the reference voltage is applied to determine a primary slope count value. During the ramp-down interval, while the reference voltage is applied, two or more integrator voltages are measured. In one embodiment, a first integrator voltage is measured before the original value and a second integrator voltage is measured after the original value, e.g., before and after the zero crossing. The method then determines a fractional slope count based on the measured two or more integrator voltages, i.e., the fractional slope count occurring before the return of the integrator to its original value. The fractional slope count is determined by extrapolating or interpolating the return of the integrator to its original value using the measured two or more integrator voltages. The total slope count is then calculated using the primary and fractional slope counts, and the output digital value is determined using the total slope count value.

Owner:NATIONAL INSTRUMENTS

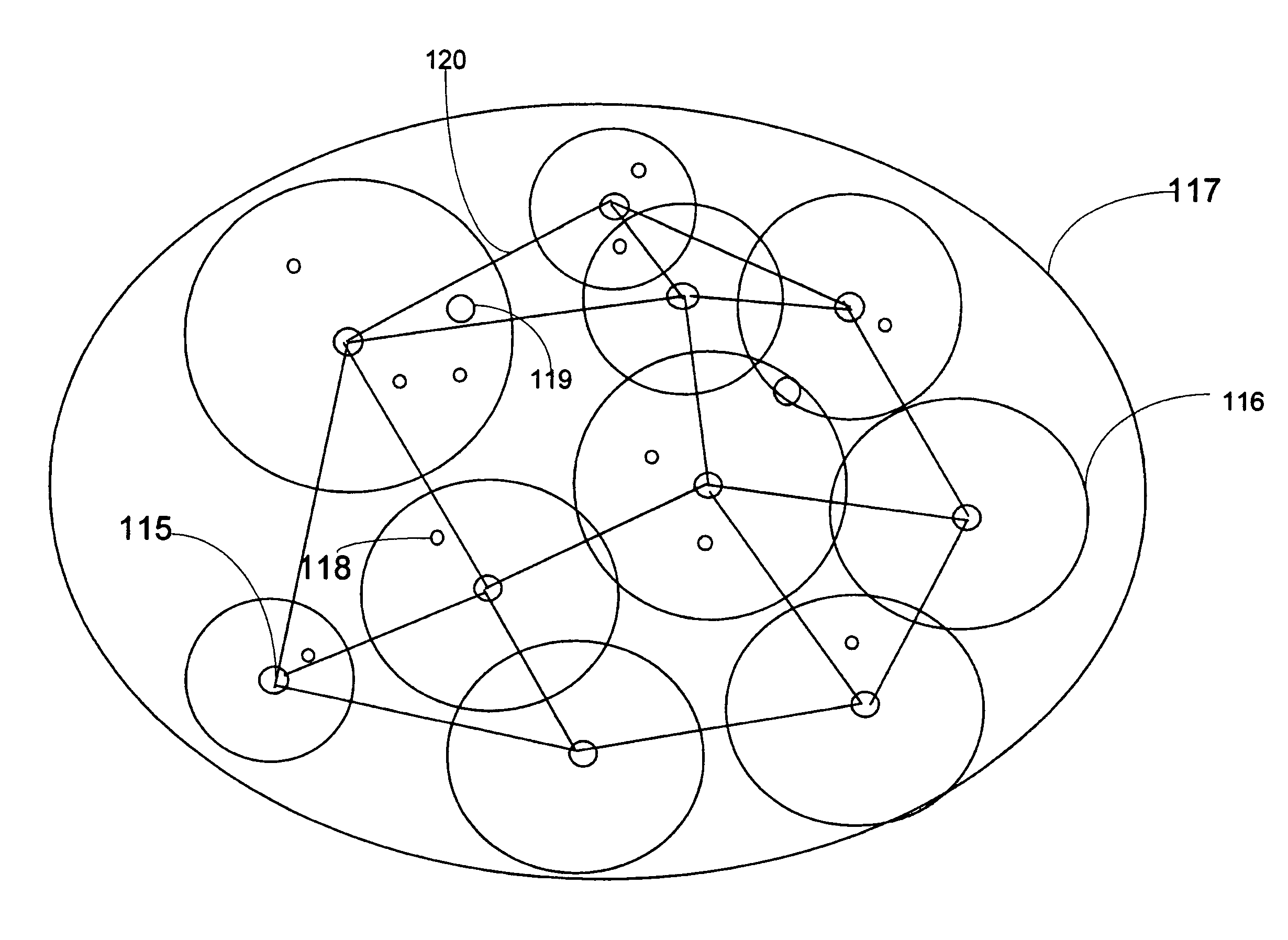

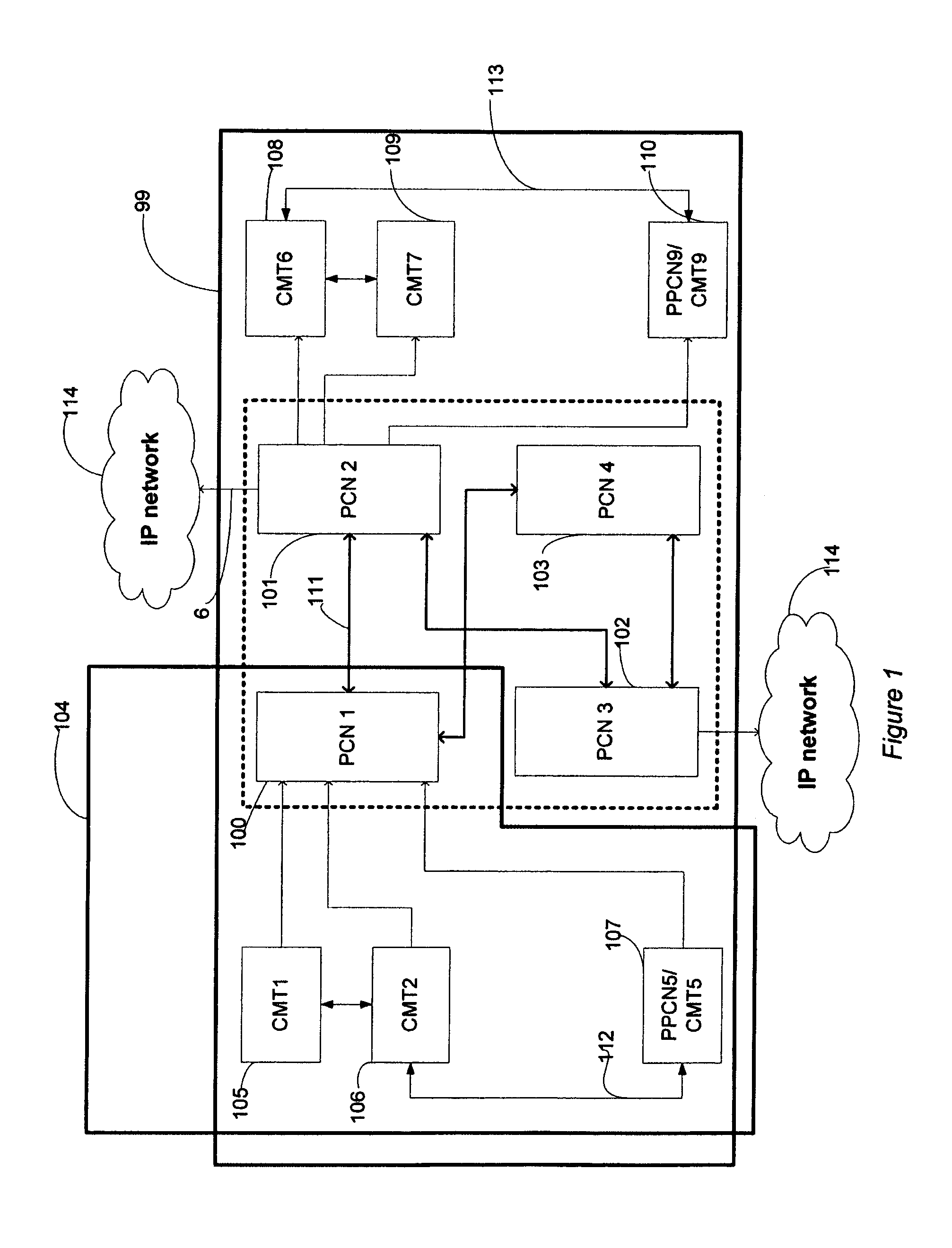

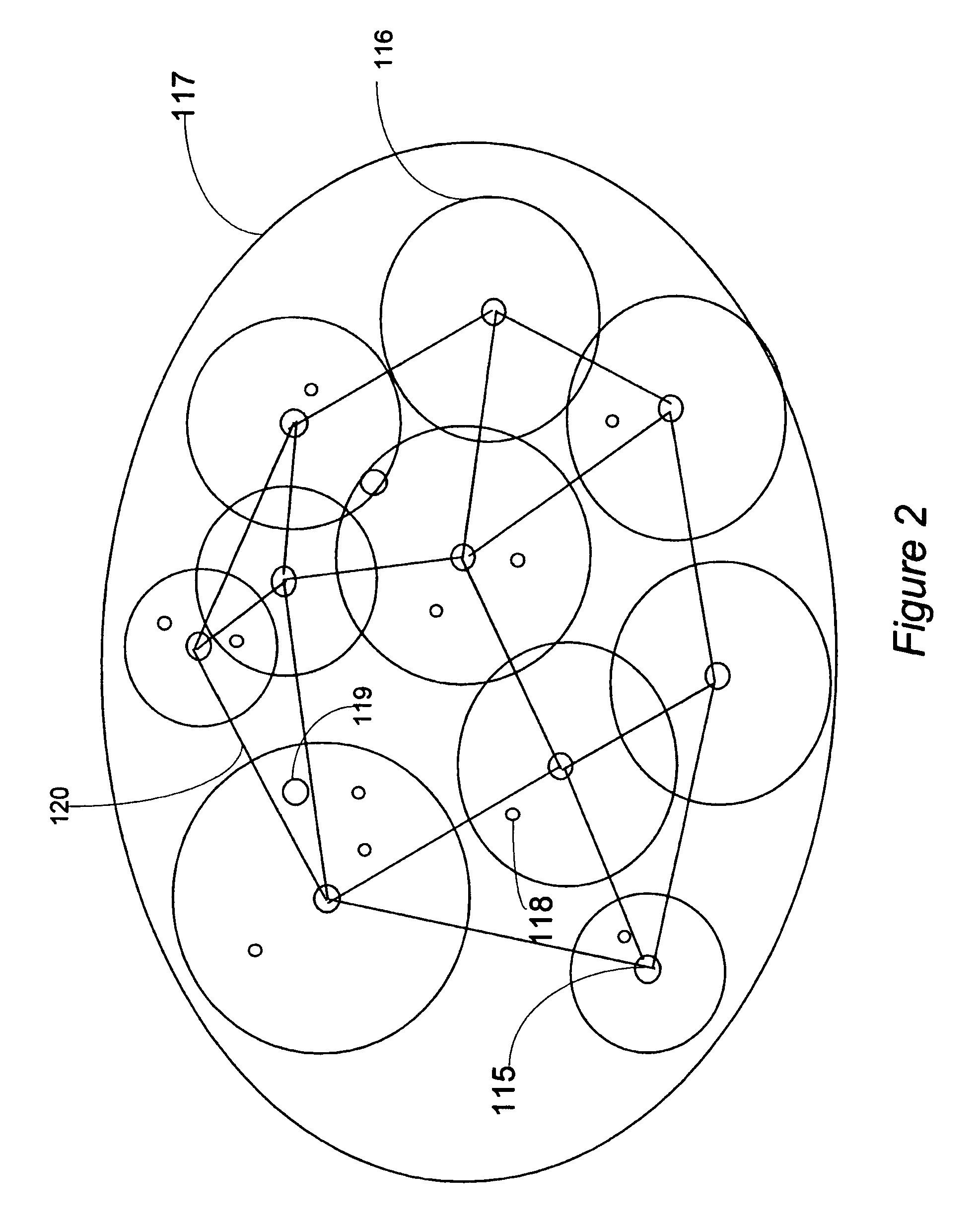

Dynamic cellular cognitive system

ActiveUS8094610B2High quality cognitive communicationReducing and eliminating interferenceNetwork traffic/resource managementCriteria allocationDevice typeFrequency spectrum

High quality communications among a diverse set of cognitive radio (CR) nodes is permitted while minimizing interference to primary and other secondary users by employing Dynamic Spectrum Access (DSA) in a Dynamic Cellular Cognitive System (DCCS). Diverse device types interoperate, cooperate, and communicate with high spectrum efficiency and do not require infrastructure to form the network. The dynamic cellular cognitive system can expand to a wider geographical distribution via linking to existing infrastructure.

Owner:VIRGINIA TECH INTPROP INC

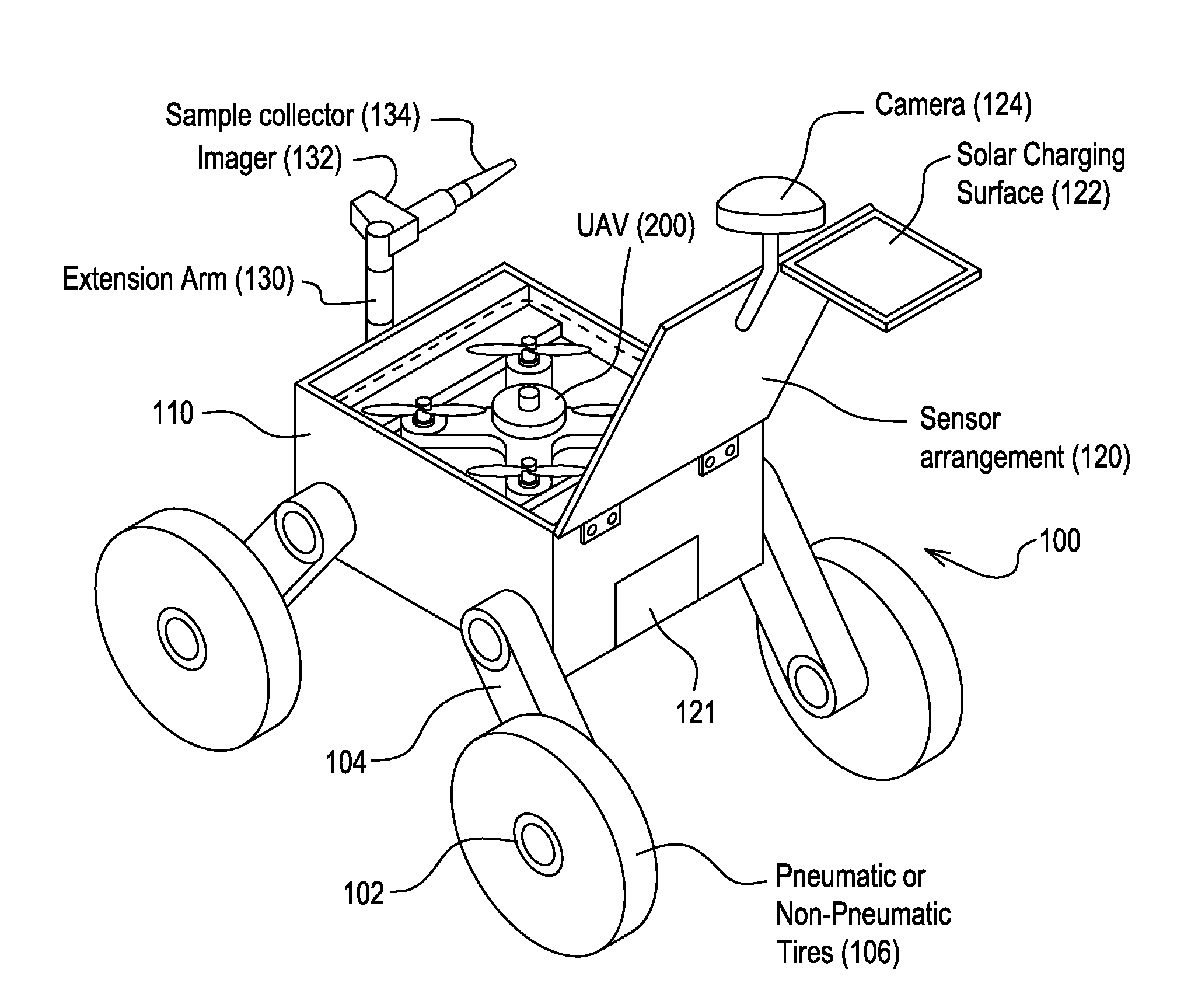

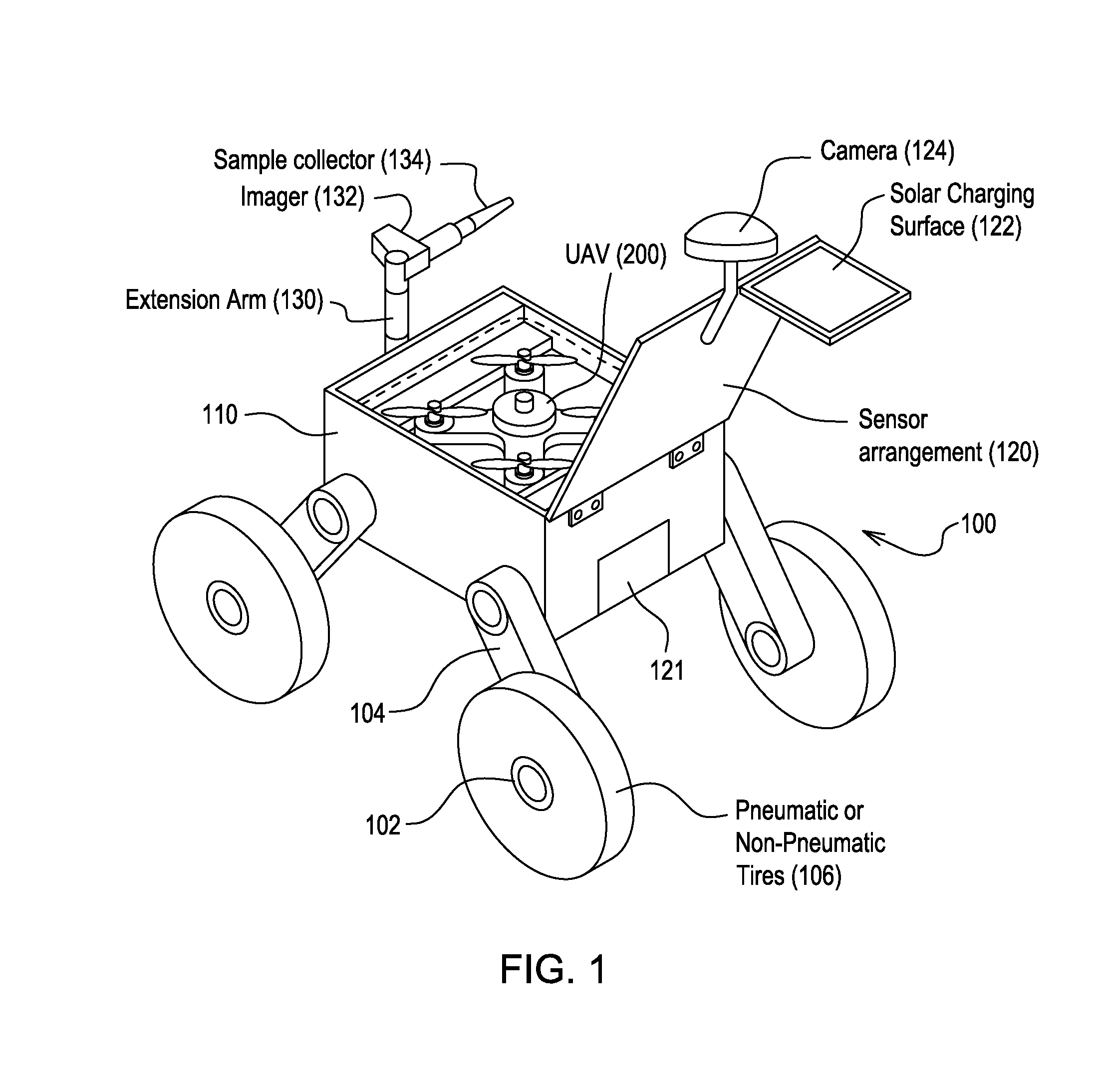

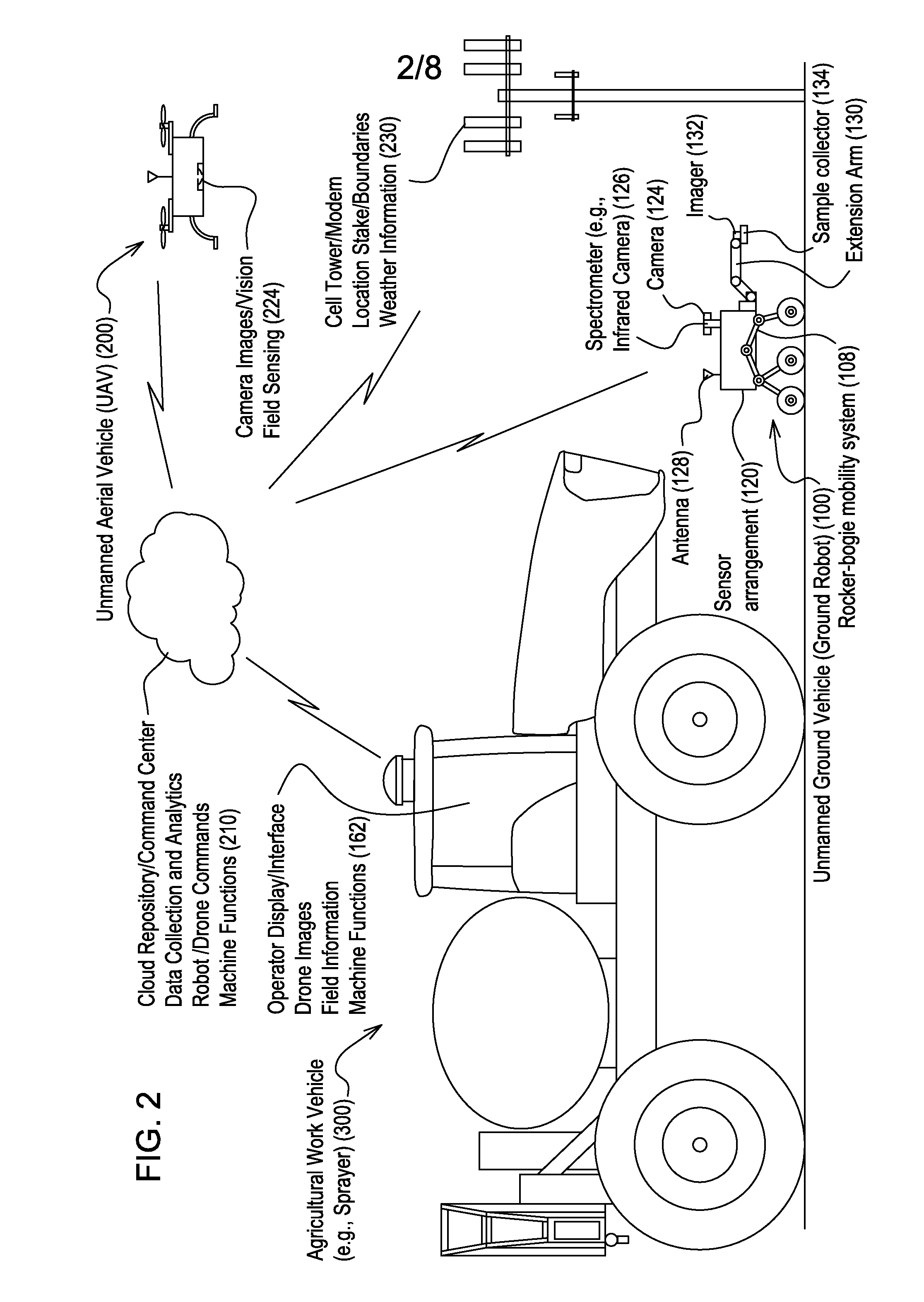

Scouting systems

ActiveUS20160157414A1More complexIncrease crop yieldAutonomous decision making processPosition fixationEngineeringBuddy system

Embodiments include a ground scout having an ability to identify the location of rows of crops and the end of the rows so that it can navigate, but in other embodiments, the ground scout can also rely more on an aerial drone to navigate, to act as a communication relay system, and so on. A buddy system including a ground scout and an air scout (e.g. drone) communicate their findings with each other.

Owner:DEERE & CO

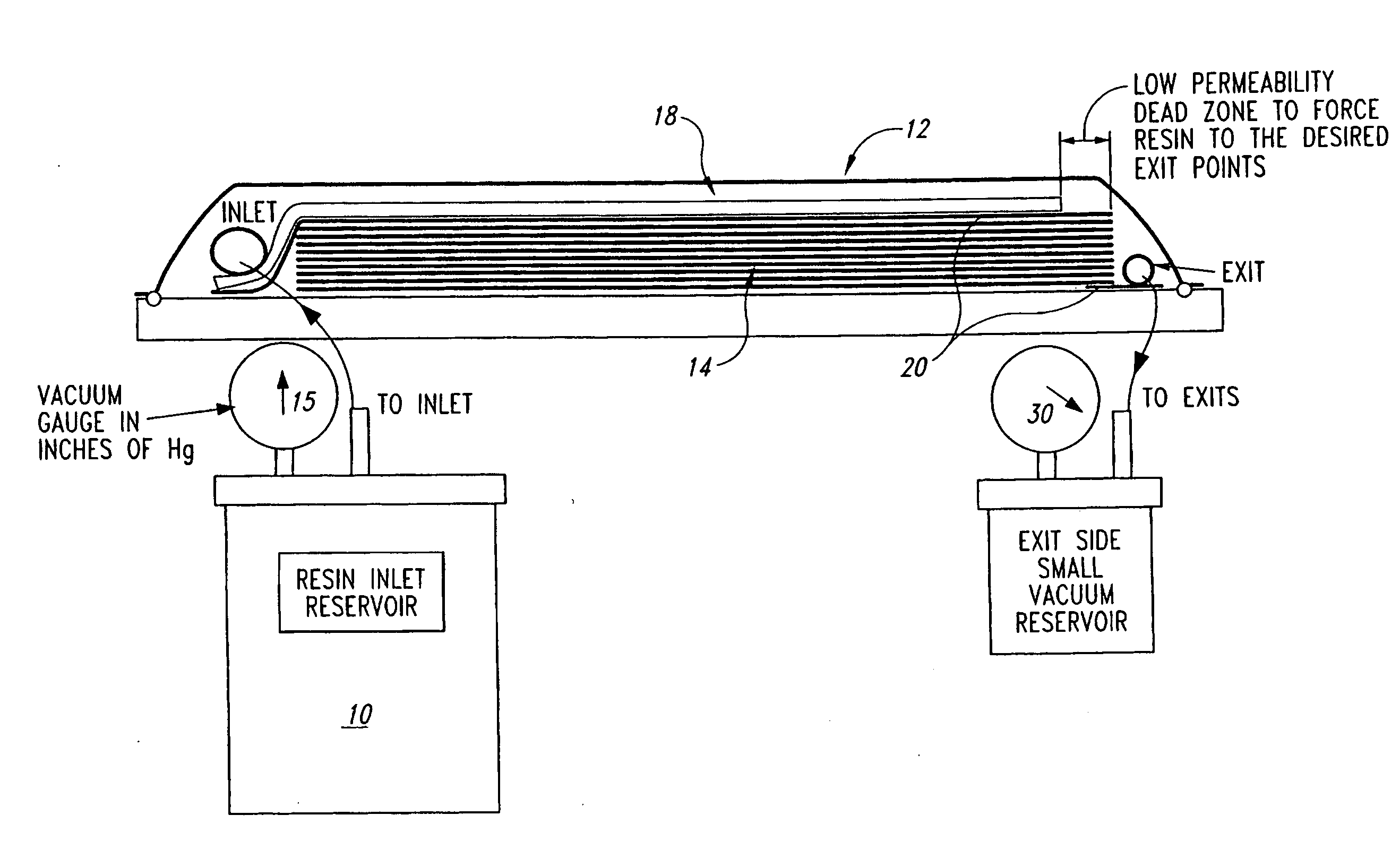

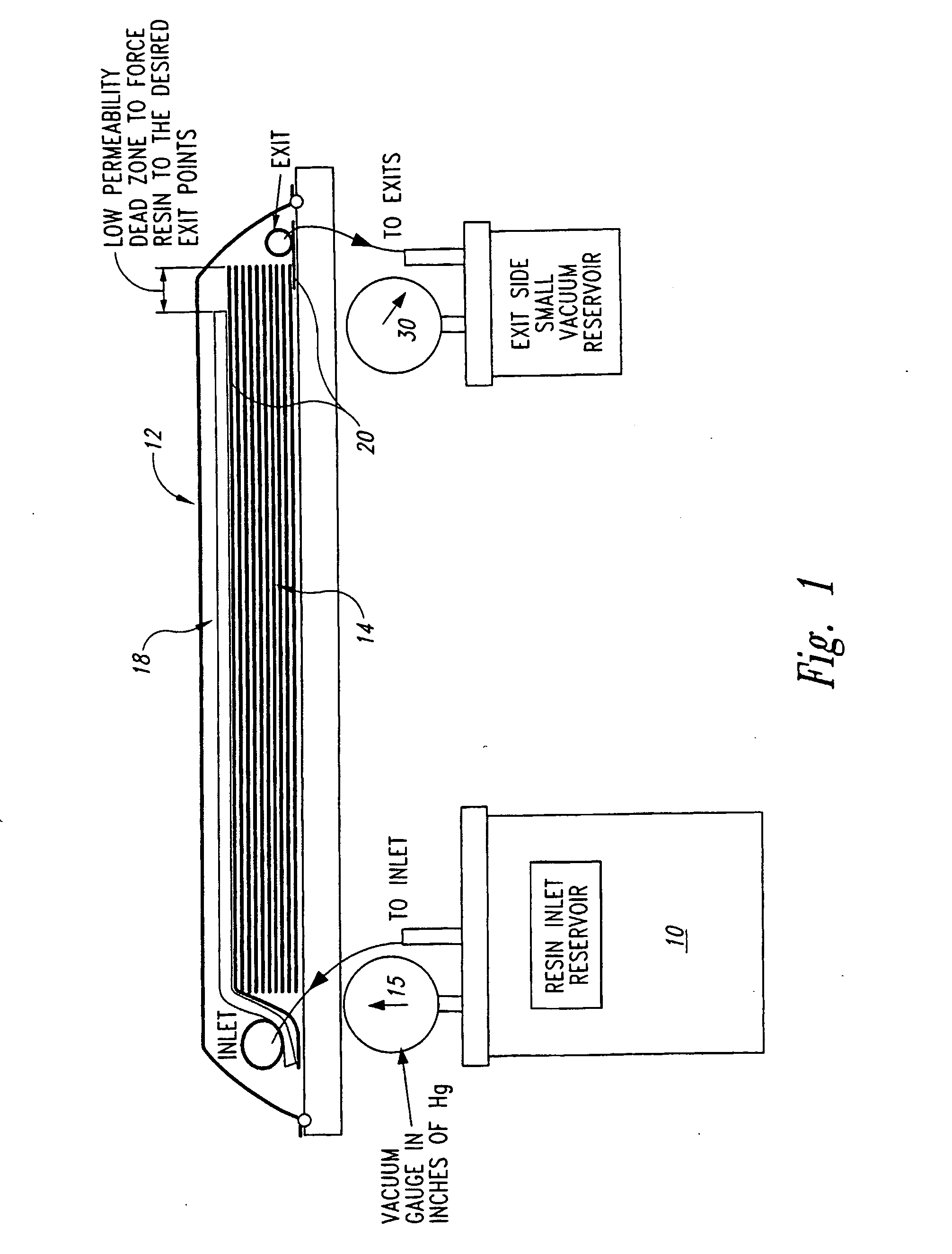

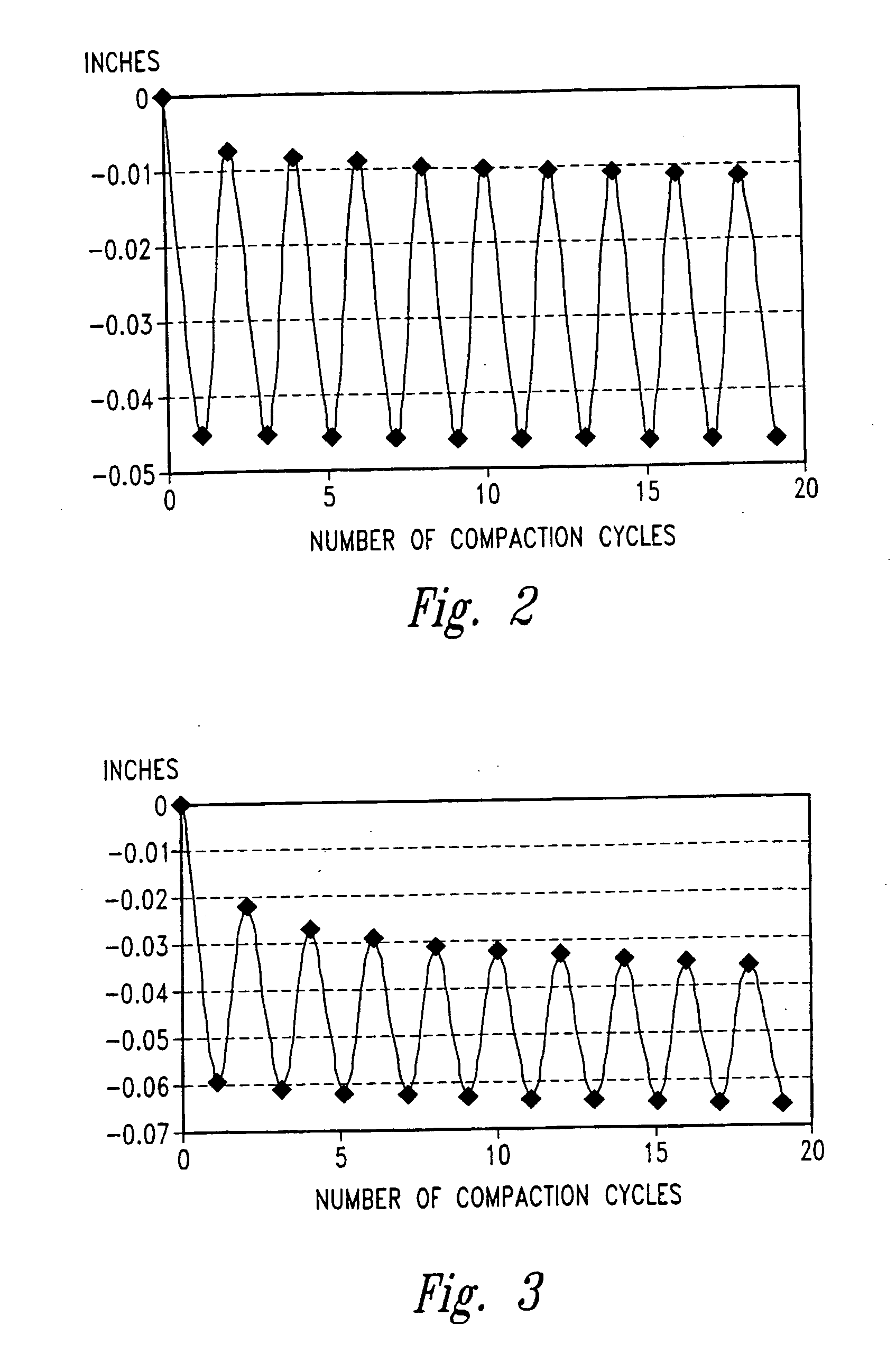

Controlled atmospheric pressure resin infusion process

ActiveUS20050073076A1Specific strength of partLow costLaminationLamination apparatusSurface finishEngineering

By evacuating the resin feed tank to a pressure below atmospheric pressure, employing cyclic compaction, and controlling the net compaction pressure, we are better able to control a resin infusion process, particularly a vacuum assisted resin transfer molding process, and produce aerospace-grade fiber-reinforced resin composite having fiber volume fractions and tool-side surface finishes comparable to or exceeding those made using an autoclave.

Owner:THE BOEING CO

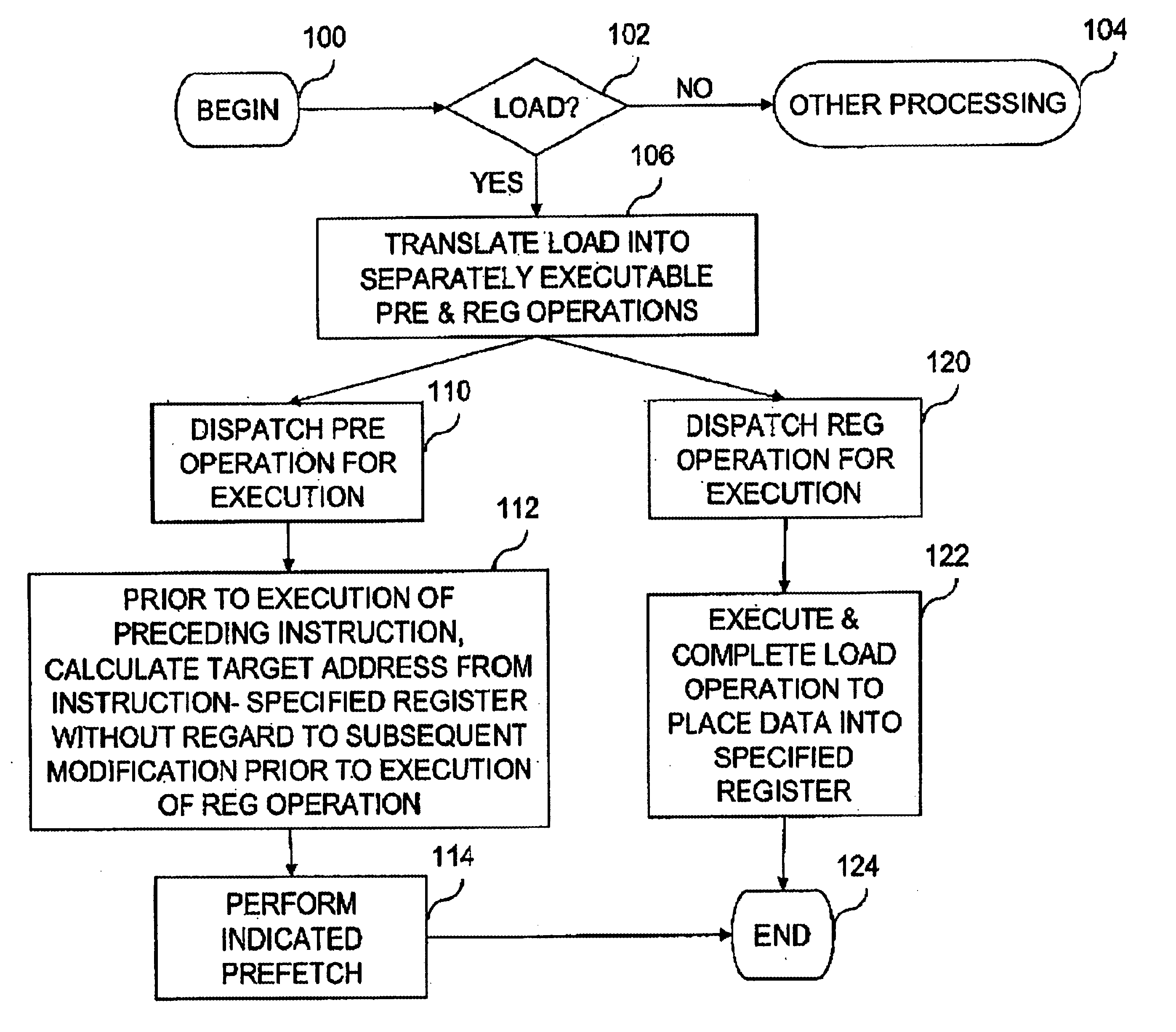

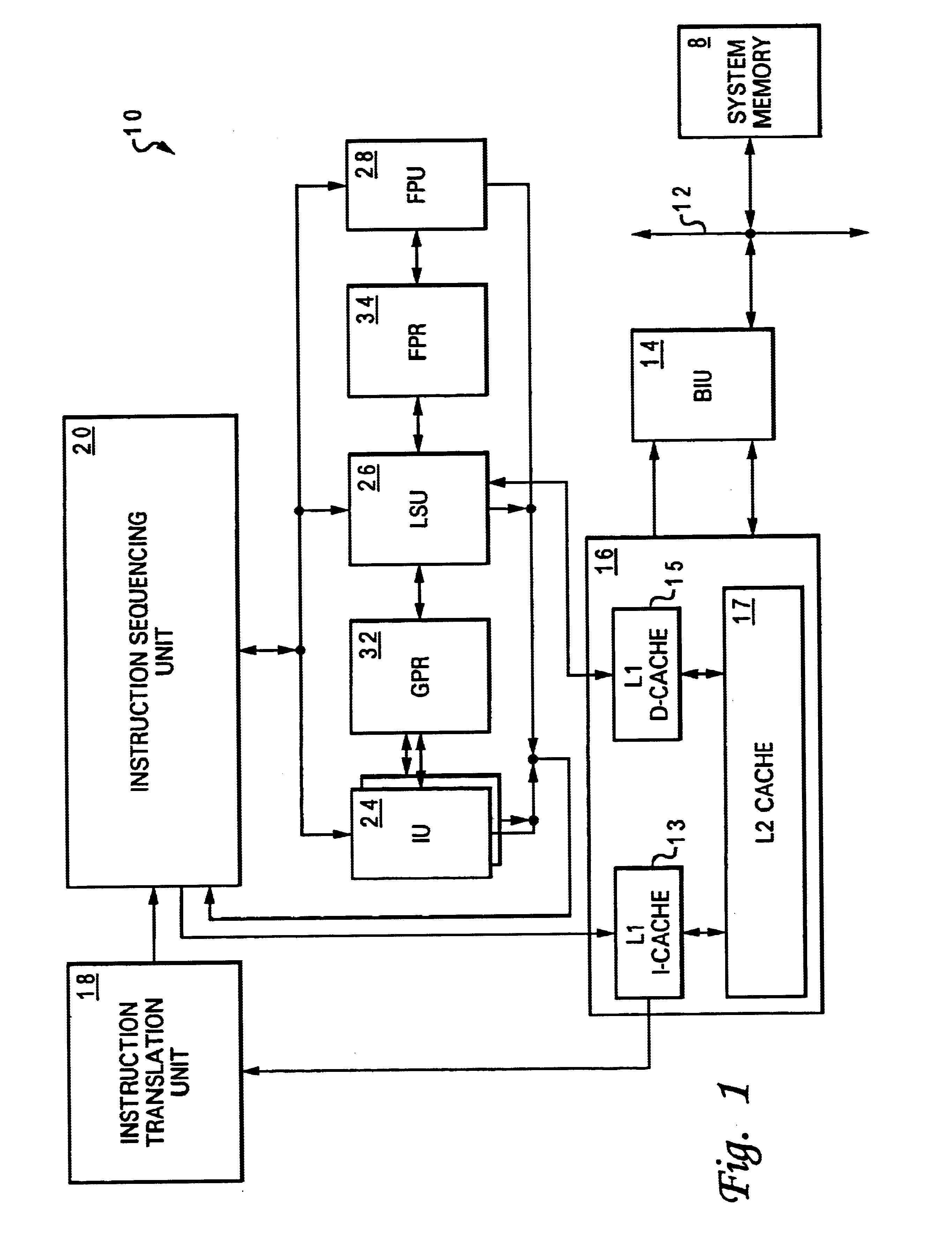

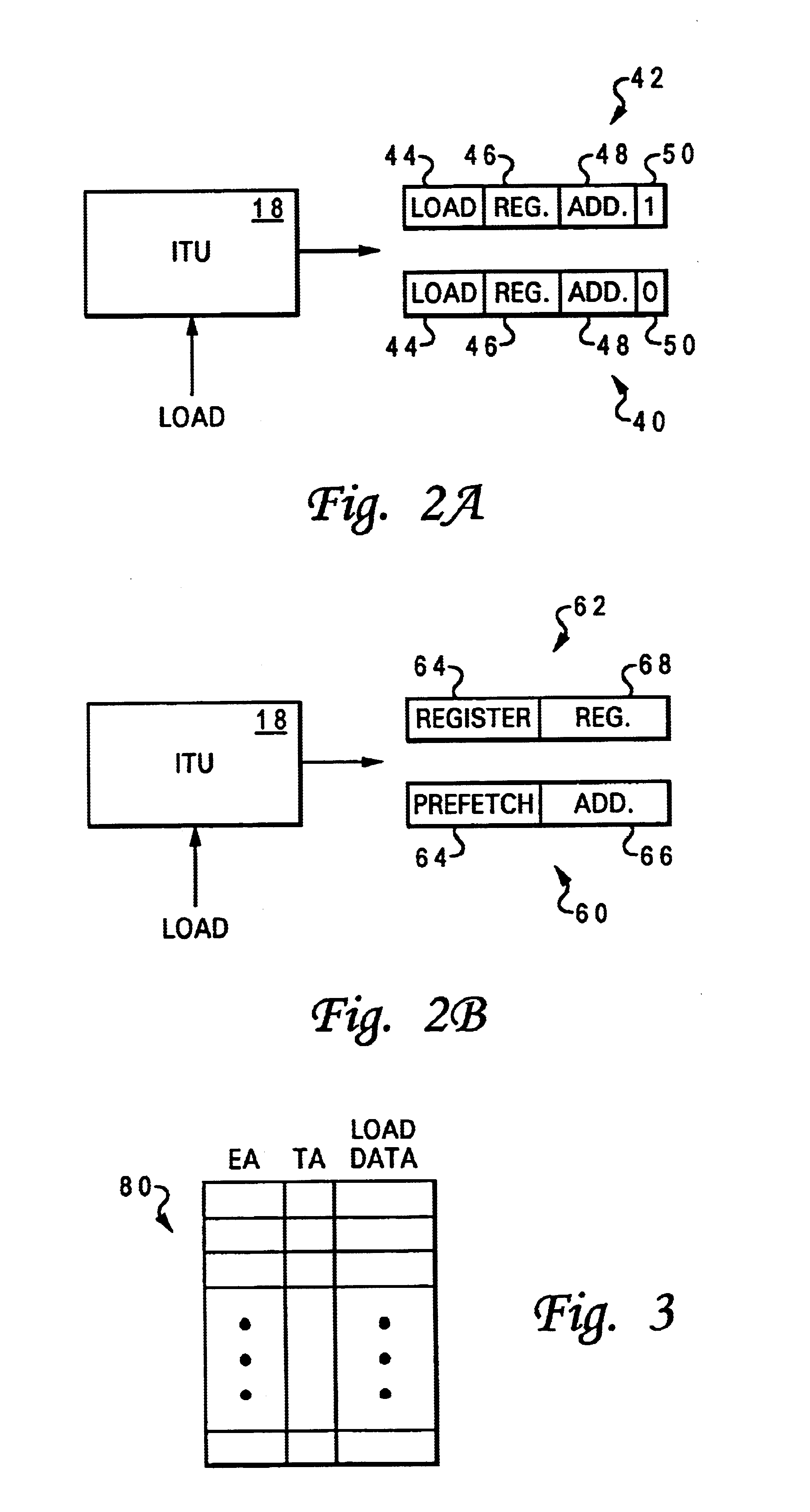

Processor and method of executing a load instruction that dynamically bifurcate a load instruction into separately executable prefetch and register operations

InactiveUS6871273B1Lower performance requirementsMore complexRuntime instruction translationDigital computer detailsLoad instructionProcessor register

A processor implementing an improved method for executing load instructions includes execution circuitry, a plurality of registers, and instruction processing circuitry. The instruction processing circuitry fetches a load instruction and a preceding instruction that precedes the load instruction in program order, and in response to detecting the load instruction, translates the load instruction into separately executable prefetch and register operations. The execution circuitry performs at least the prefetch operation out-of-order with respect to the preceding instruction to prefetch data into the processor and subsequently separately executes the register operation to place the data into a register specified by the load instruction. In an embodiment in which the processor is an in-order machine, the register operation is performed in-order with respect to the preceding instruction.

Owner:IBM CORP

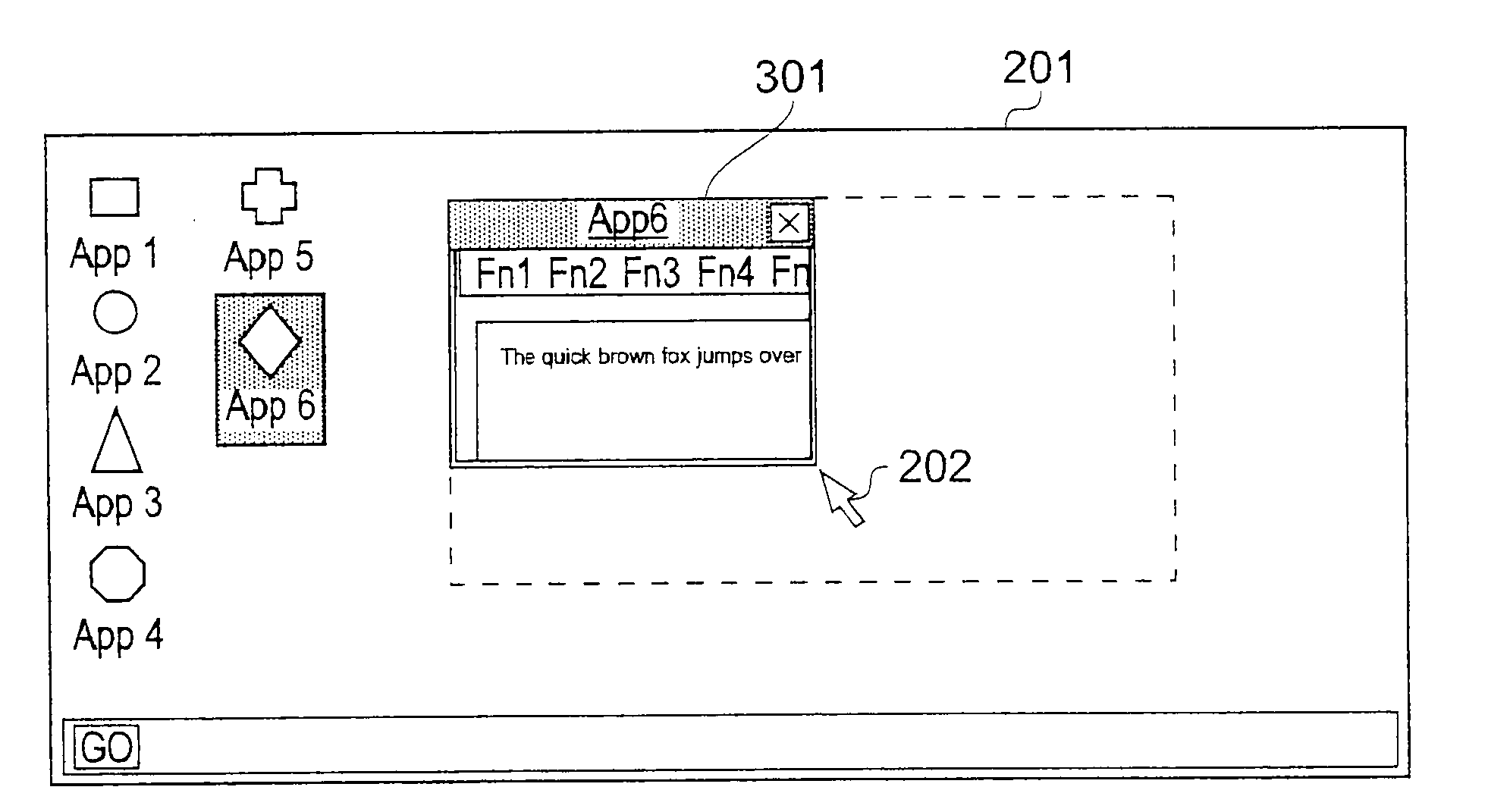

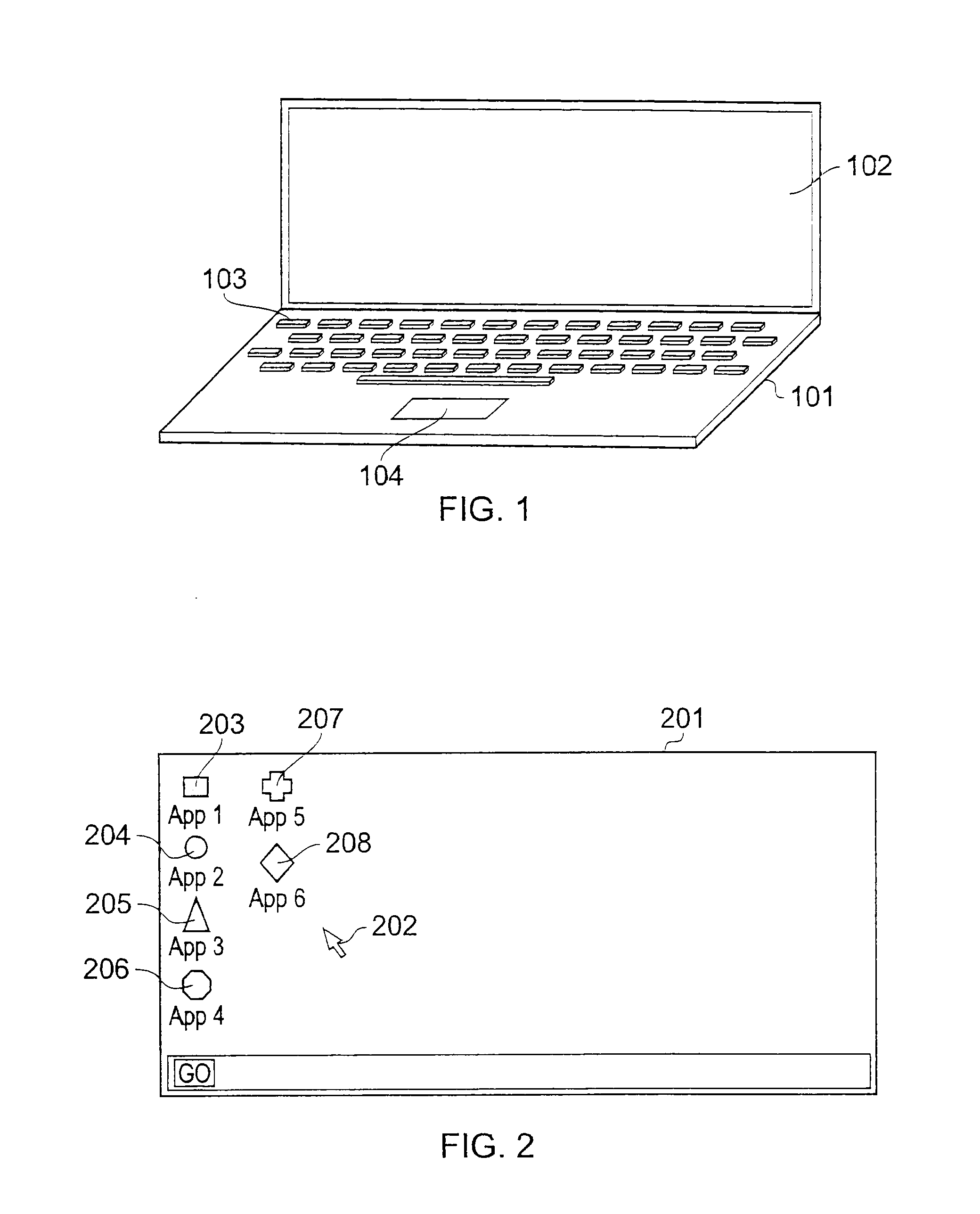

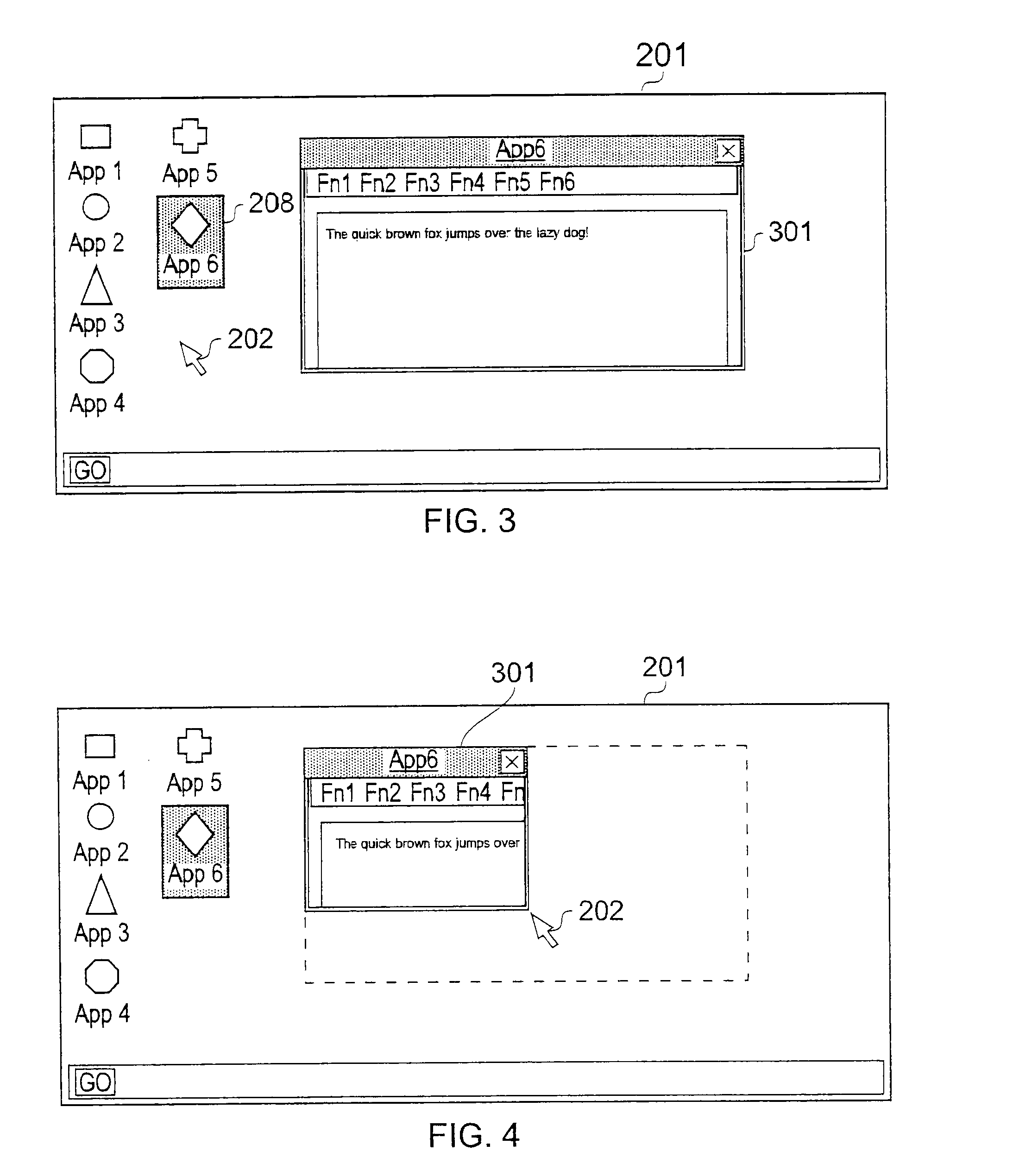

Data processing apparatus and method

ActiveUS20120017162A1Improve efficiencyPowerfulNatural language data processingFuel tanksGraphicsDisplay device

A data processing apparatus executes one or more computer program applications. The data programming, apparatus is operable to display at least one resizable graphical element from a plurality of resizable graphical elements on a display and resize the at least one displayed graphical element in response to a resize control input from a user control. The data processing device is operable to switch between which of the plurality of graphical elements is displayed if the displayed graphical element is resized to be greater in size or to be less in size than one of a plurality of predetermined threshold sizes. Each of the plurality of graphical elements includes at least one graphical object or interface control different from the other graphical elements of the plurality of graphical elements and a greater a size of one of the plurality of predetermined threshold sizes, a greater a number of controls and / or graphical objects included in the graphical element that is displayed when the displayed graphical element is resized to exceed that predetermined threshold size.

Owner:SONY CORP

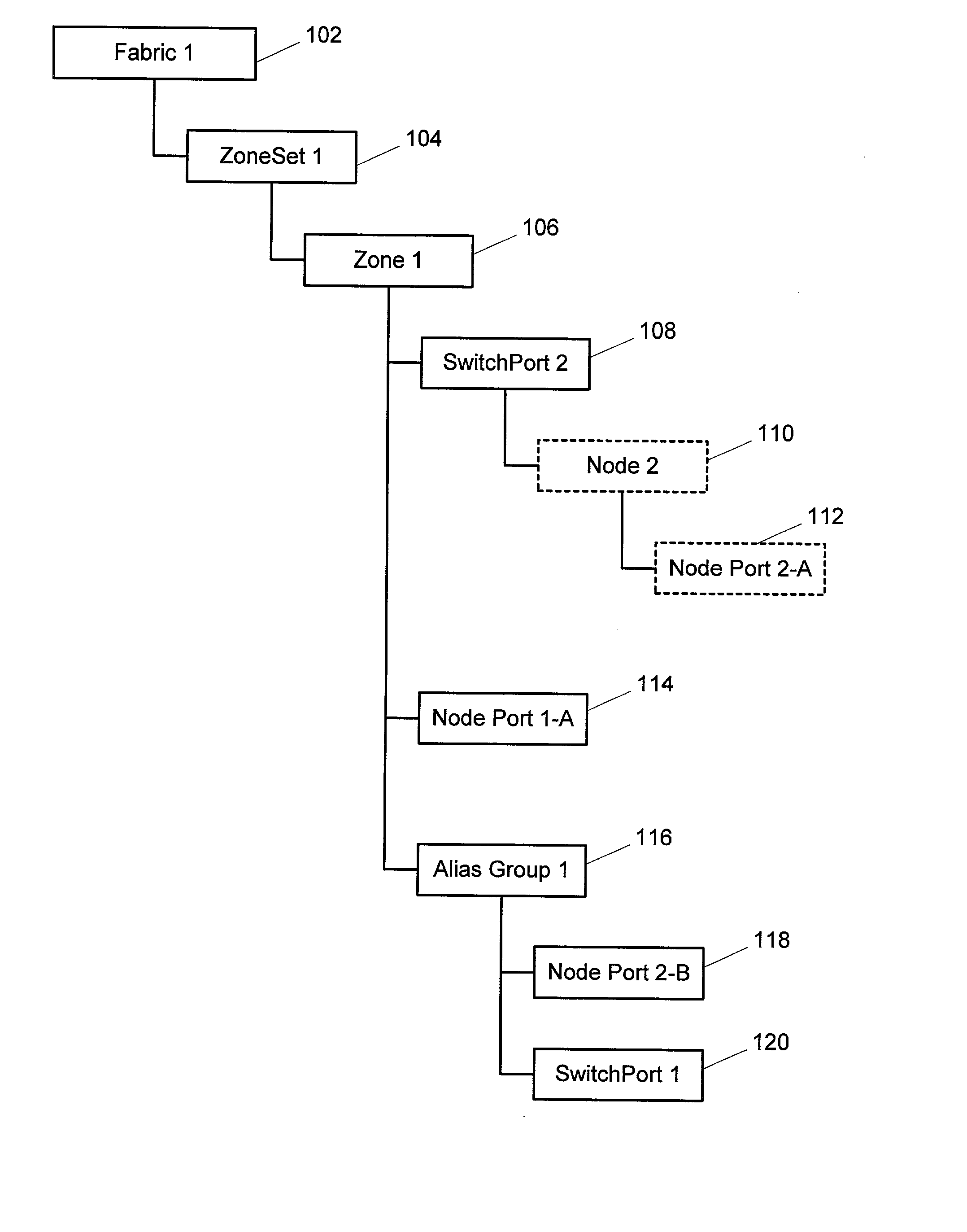

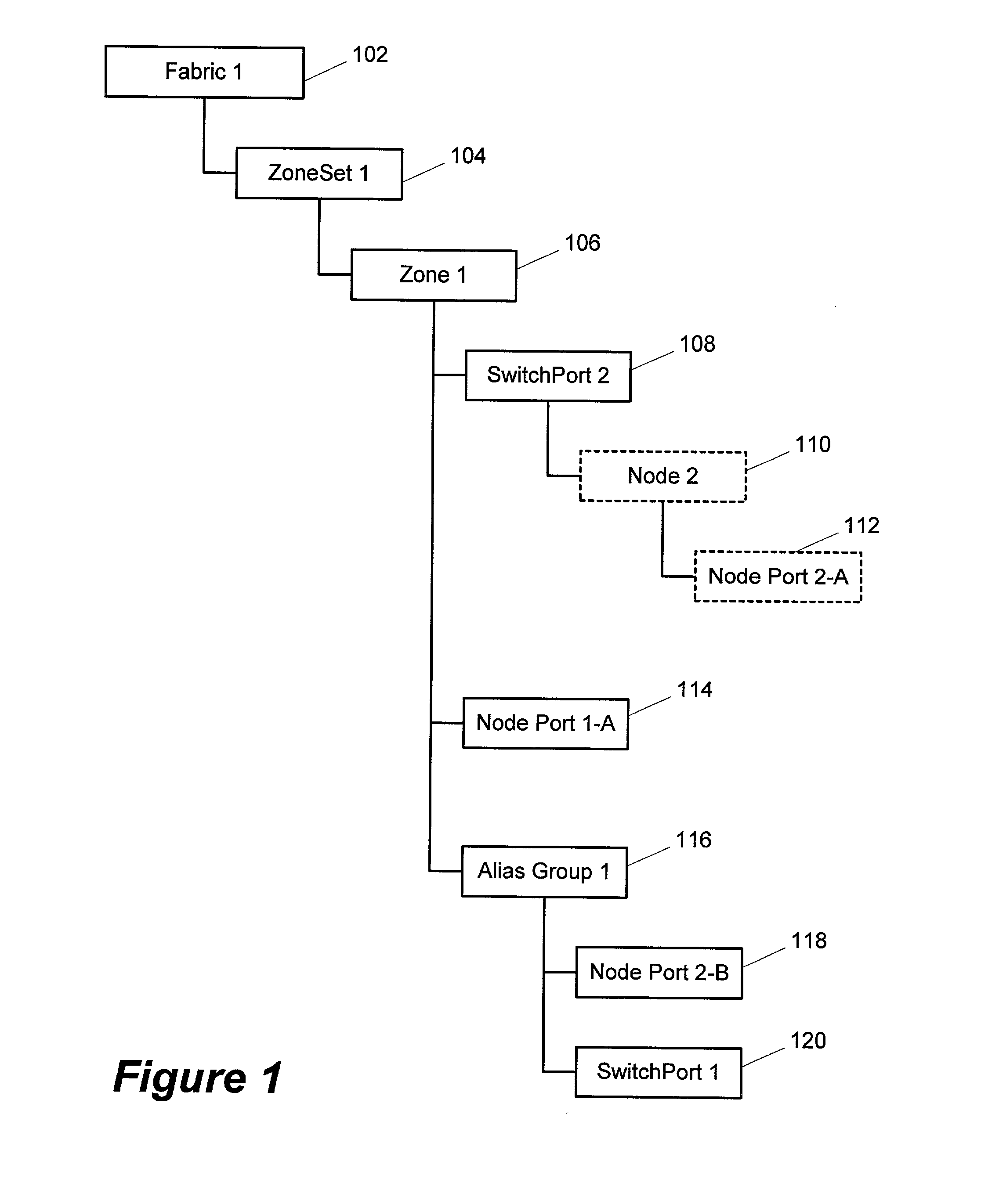

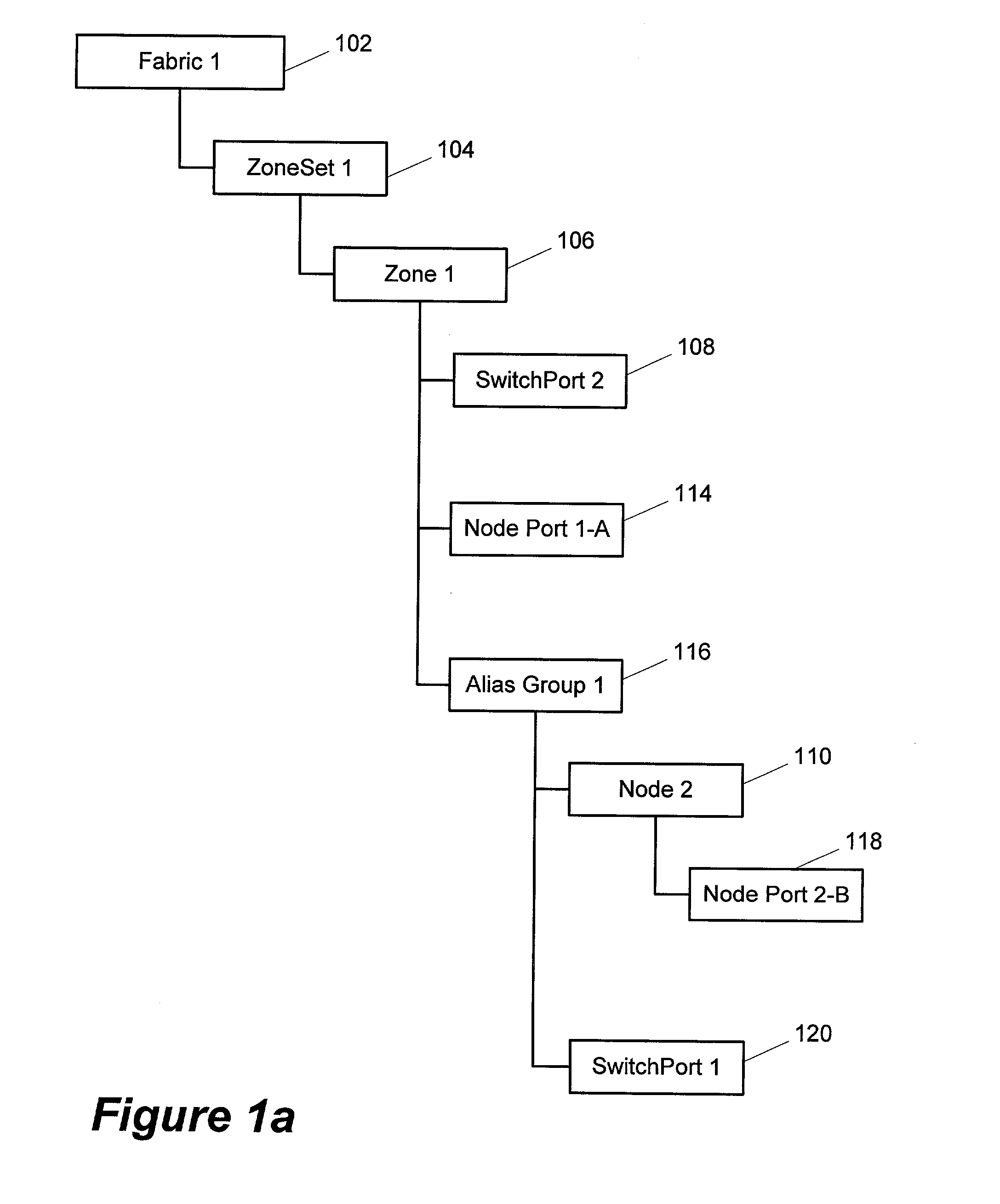

System and method for allocating unique zone membership

InactiveUS20030195956A1Risk minimizationMore complexInput/output to record carriersDigital computer detailsEngineeringIdentifying goals

The present disclosure describes a method and apparatus for ensuring the unique zoning membership representation in a network environment. In one aspect, the members of a container may be evaluated to determine whether any are subordinate to or children of a target member of the same container. The subordinate or child members may be removed from the container's configuration. Generally following the removal of any subordinate or child members of the target member, a determination may be made as to whether the target member is a child of or subordinate to any container members remaining in the container's configuration. If the target member is determined to be subordinate to or a child of a remaining container member, the target member may be removed from the container's configuration. Consequently, redundant member entries, unintentional communication paths and the complexities associated with creating a zoning configuration may be avoided.

Owner:CIPHERMAX

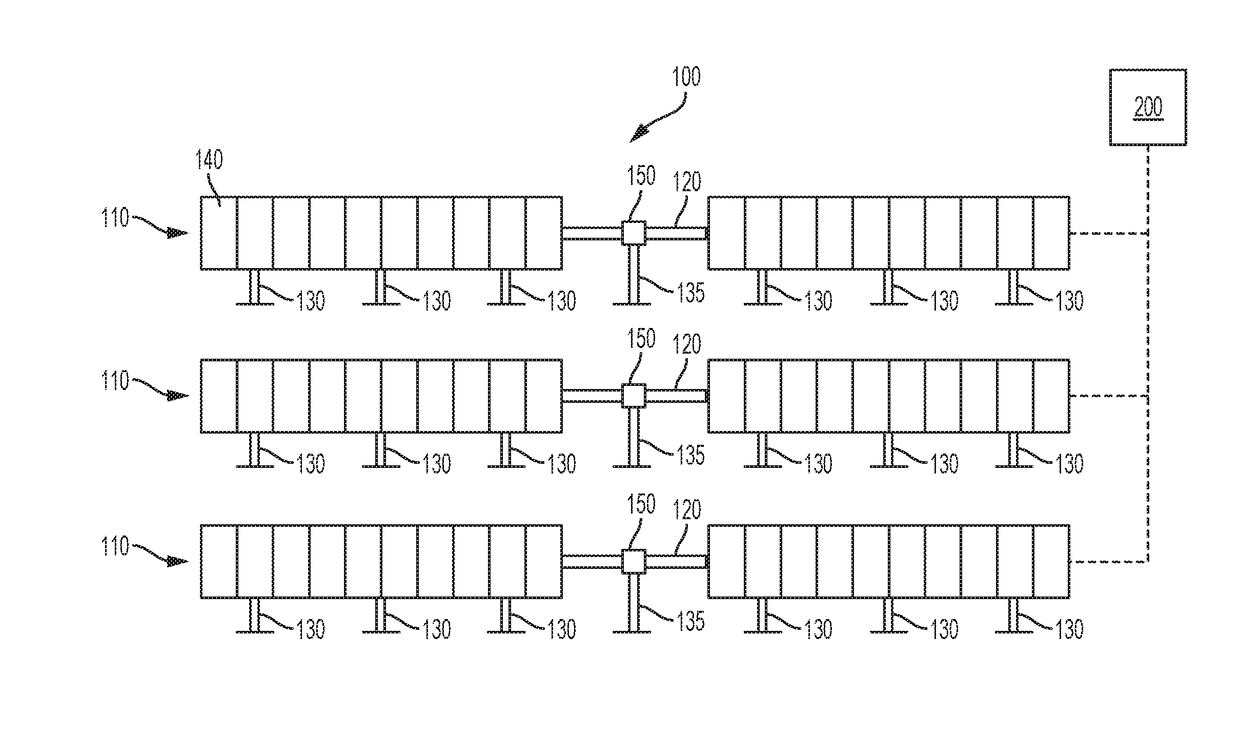

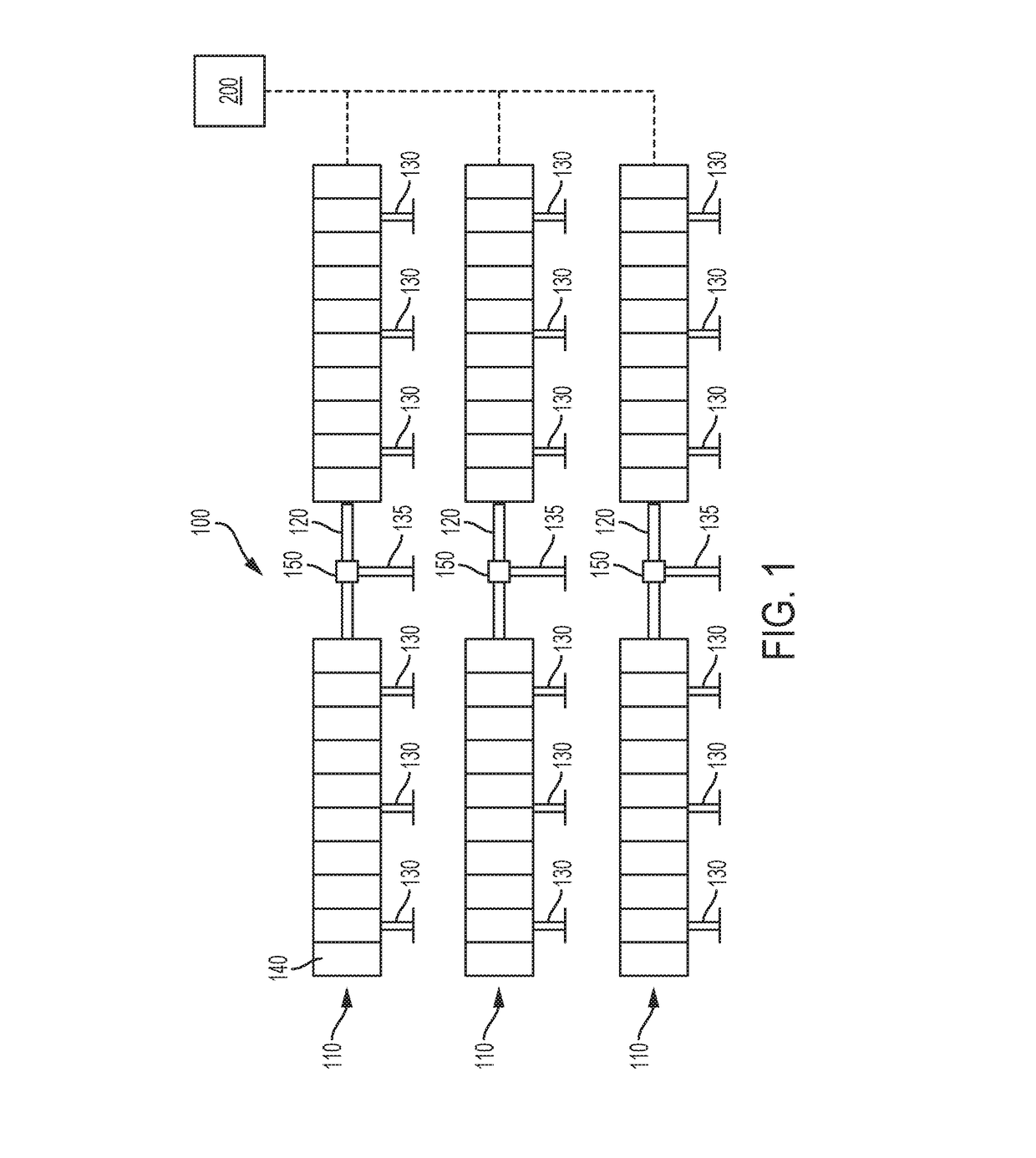

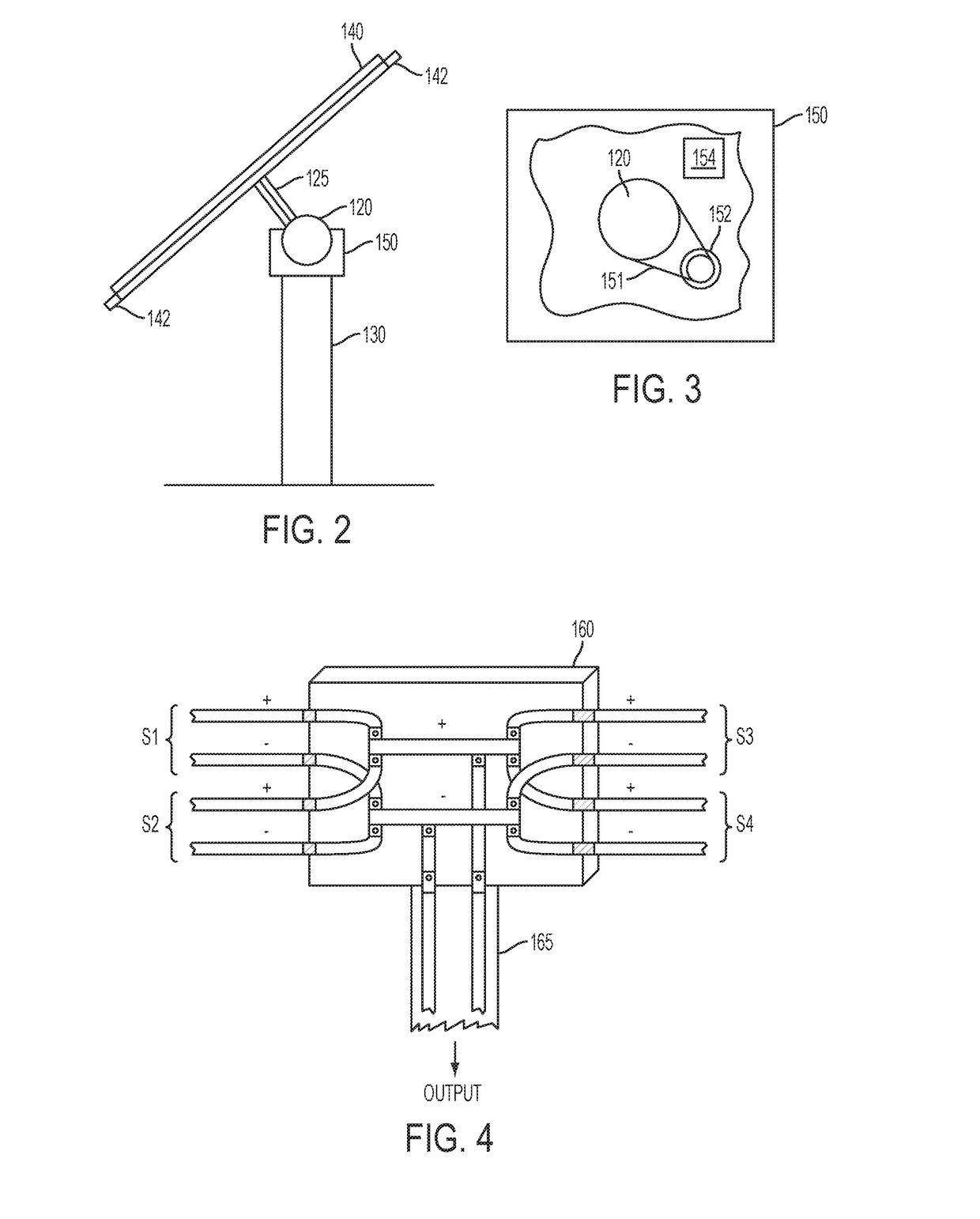

Array powered solar tracking system

InactiveUS20170093329A1Requires minimizationMinimizing amount of wiringPhotovoltaic supportsSolar heating energyElectricityComputer module

A self-powered solar tracker array system and related method, where a torque tube supporting a plurality of strings of photovoltaic (PV) modules, a DC drive motor with a motor controller circuit, and a drive assembly is capable to rotate the torque tube with torque generated by the drive motor, where the power for operating the drive motor is taken from electricity generated by the PV modules. The system can include a battery to provide a power source for rotating the torque tubes when the PV modules are not generating electricity.

Owner:SOLARCITY

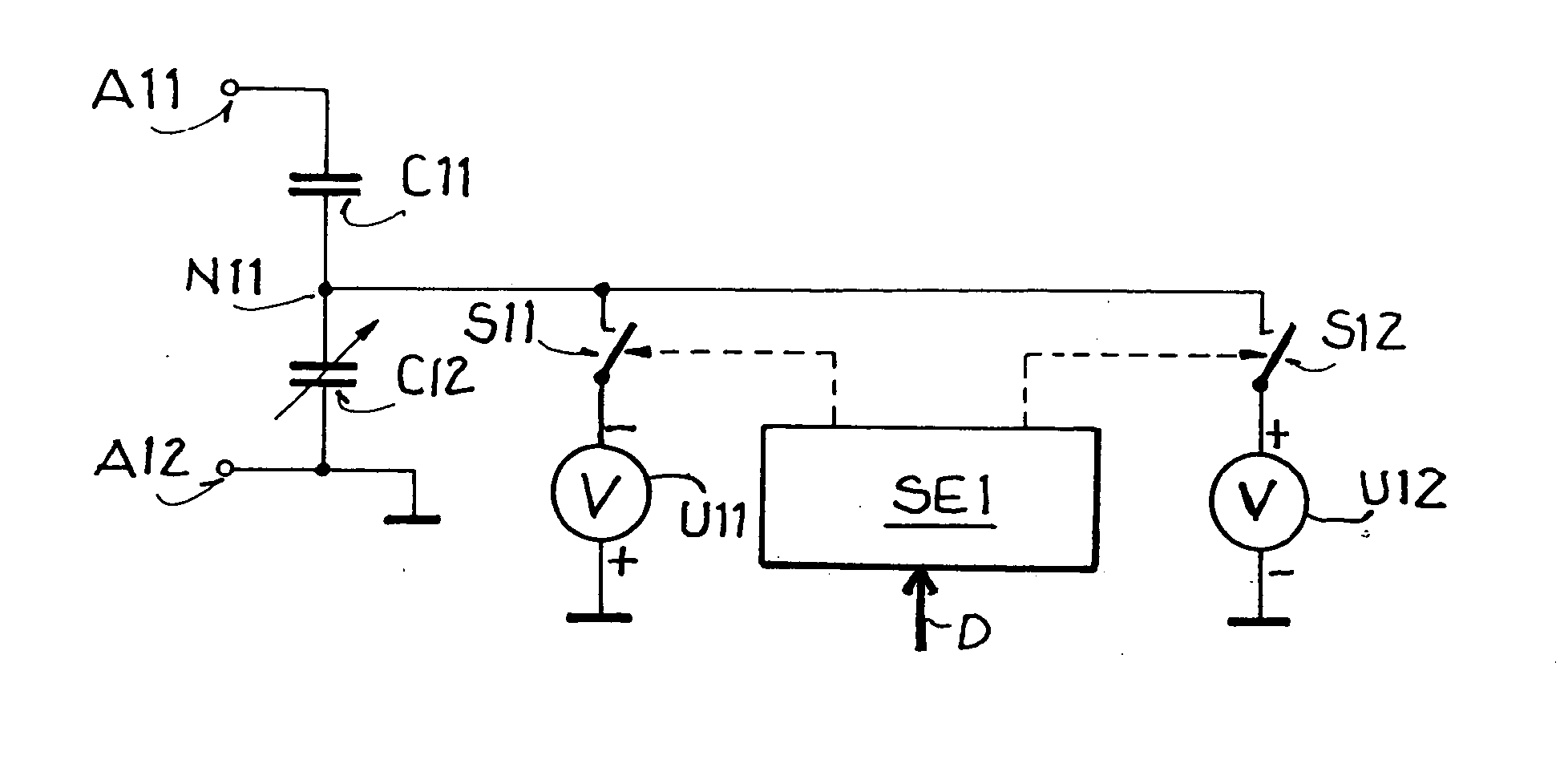

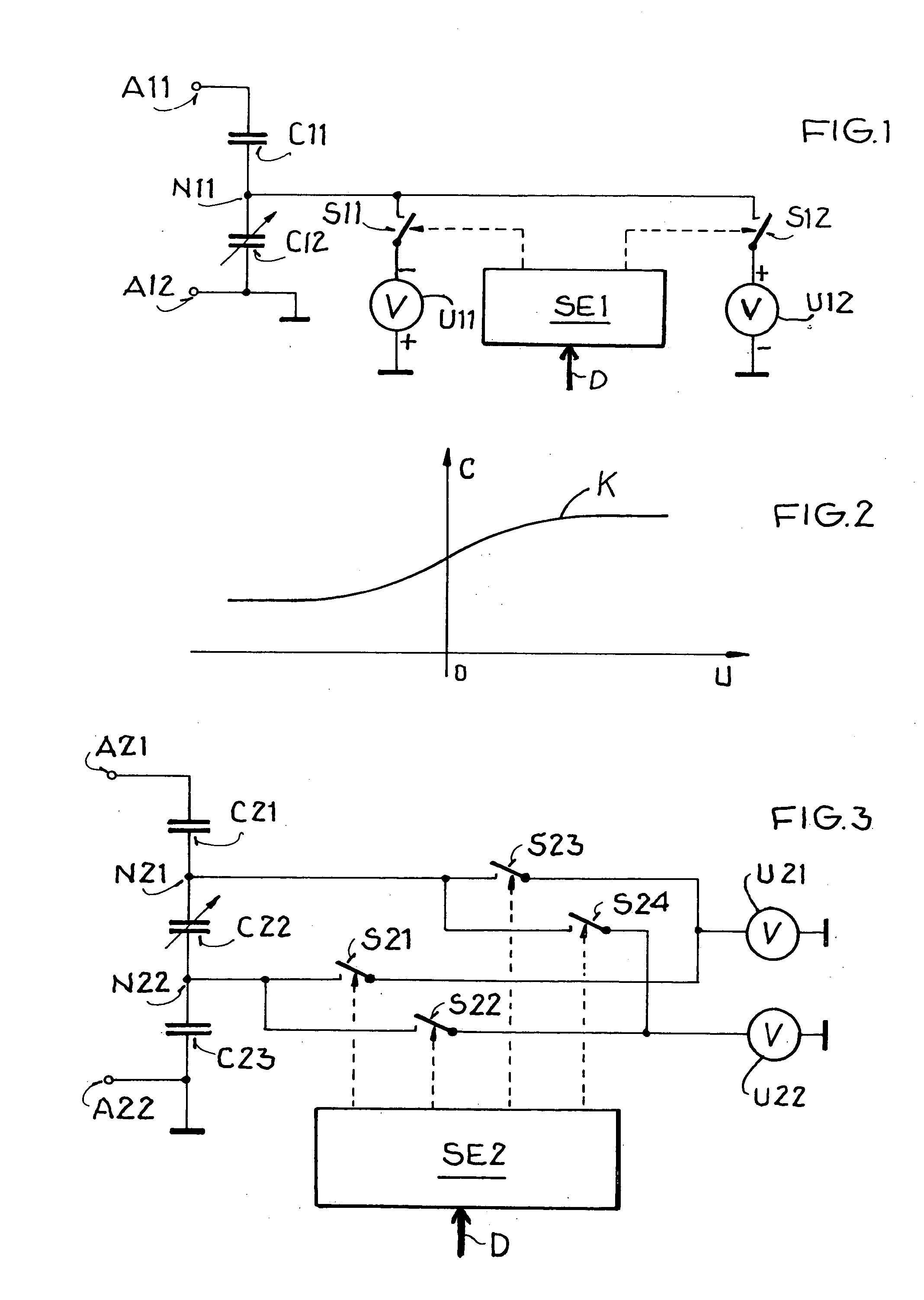

Circuit arrangement and method for phase modulation in a backscattering transponder

ActiveUS20040257220A1More complexMore costlyAngle modulation by variable impedenceFrequency-division multiplex detailsInput impedanceVoltage source

A circuit arrangement for phase modulation in an input circuit of a backscattering transponder includes a varactor and at least one capacitor connected in series between two antenna terminals, and at least two voltage sources selectively connected through at least two switches to at least one terminal of the varactor. A control unit selectively opens and closes the switches in response to the data to be phase-modulated onto the backscattered signal. By selectively connecting the different voltage values of the respective voltage sources to the varactor terminal(s) through the switches, the capacitance of the varactor and correspondingly the input impedance of the input circuit are thereby varied, so as to provide respective different phase positions of the phase modulation.

Owner:ATMEL CORP +1

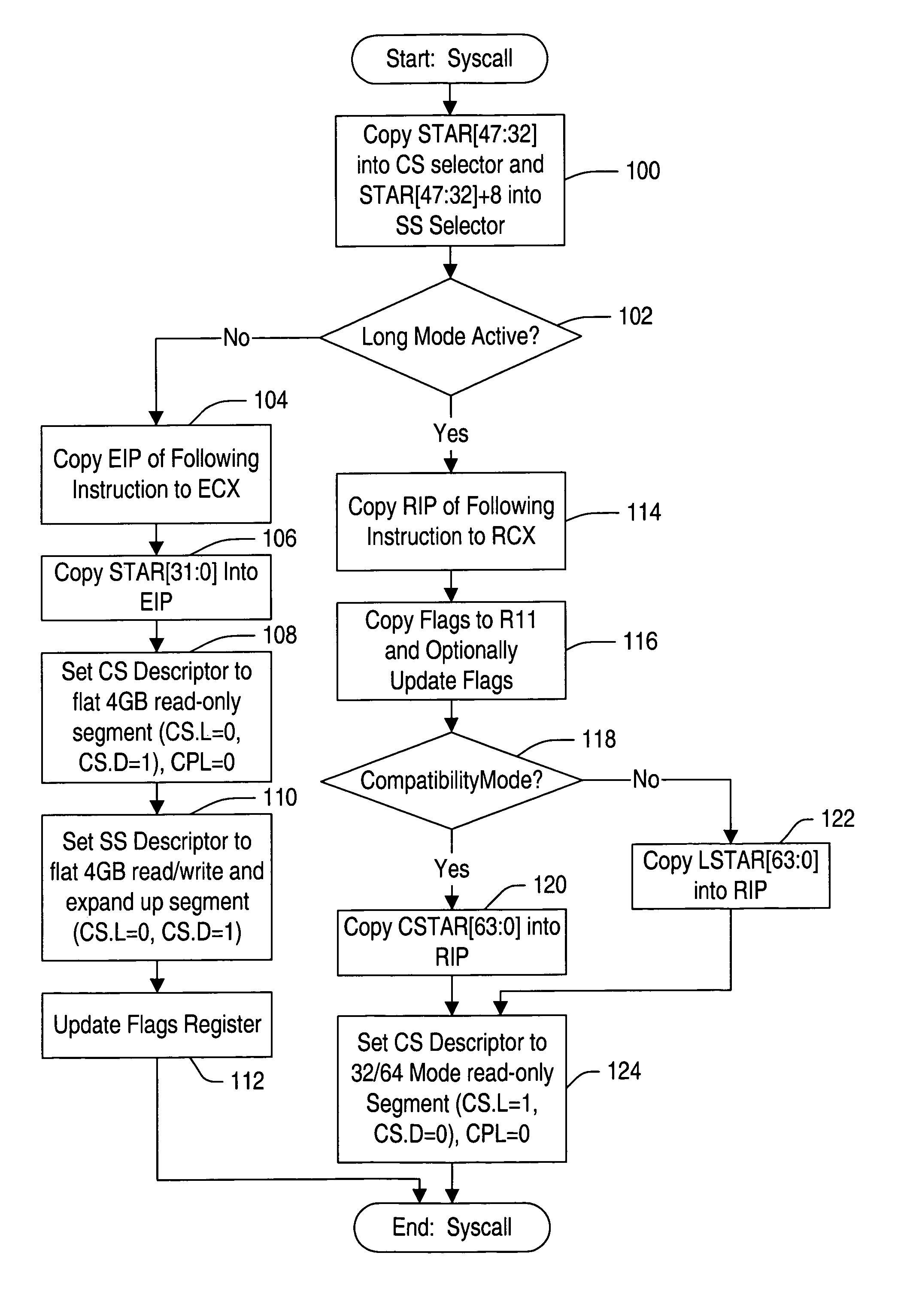

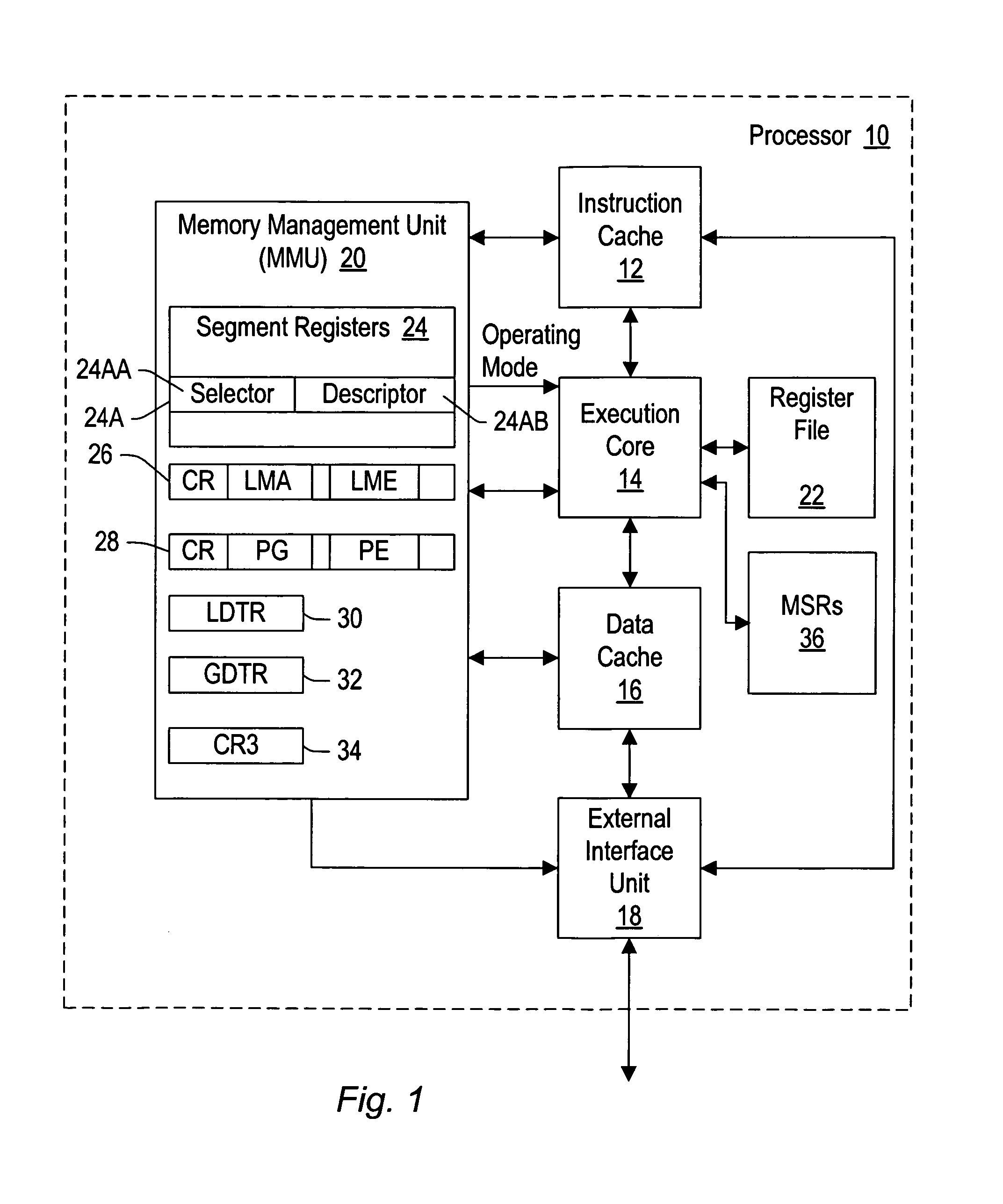

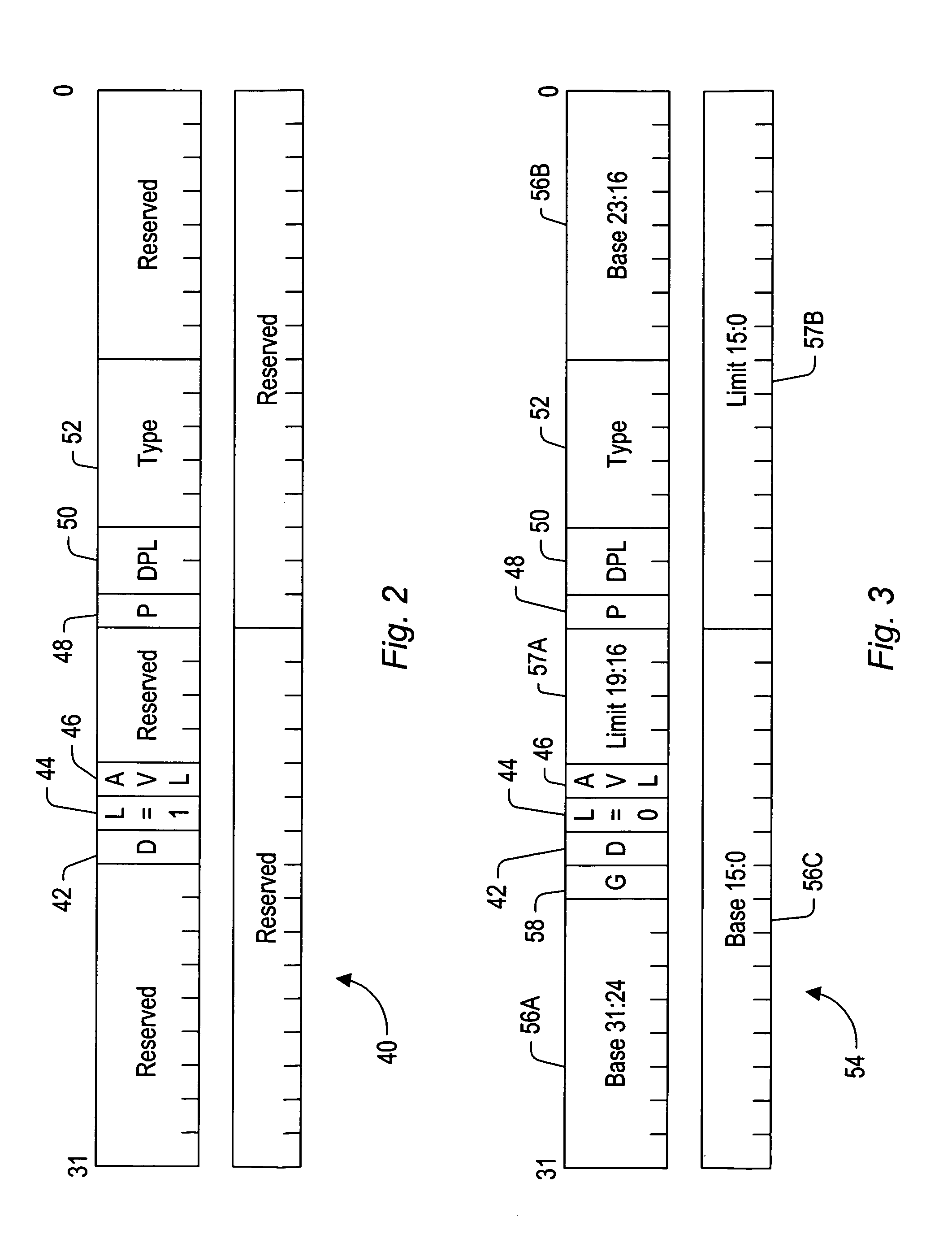

Multiple entry points for system call instructions

ActiveUS7100028B2Improve performanceSimplify System DesignDigital computer detailsNext instruction address formationOperation modeSystem call

A processor executes a system call instruction. The processor includes at least two registers in which target addresses may be stored, and selects the target address from one of the registers responsive to the operating mode. Different target addresses may be programmed into the registers, and thus the operating mode of the code sequence may be indicated by which target address is selected.

Owner:ADVANCED MICRO DEVICES INC

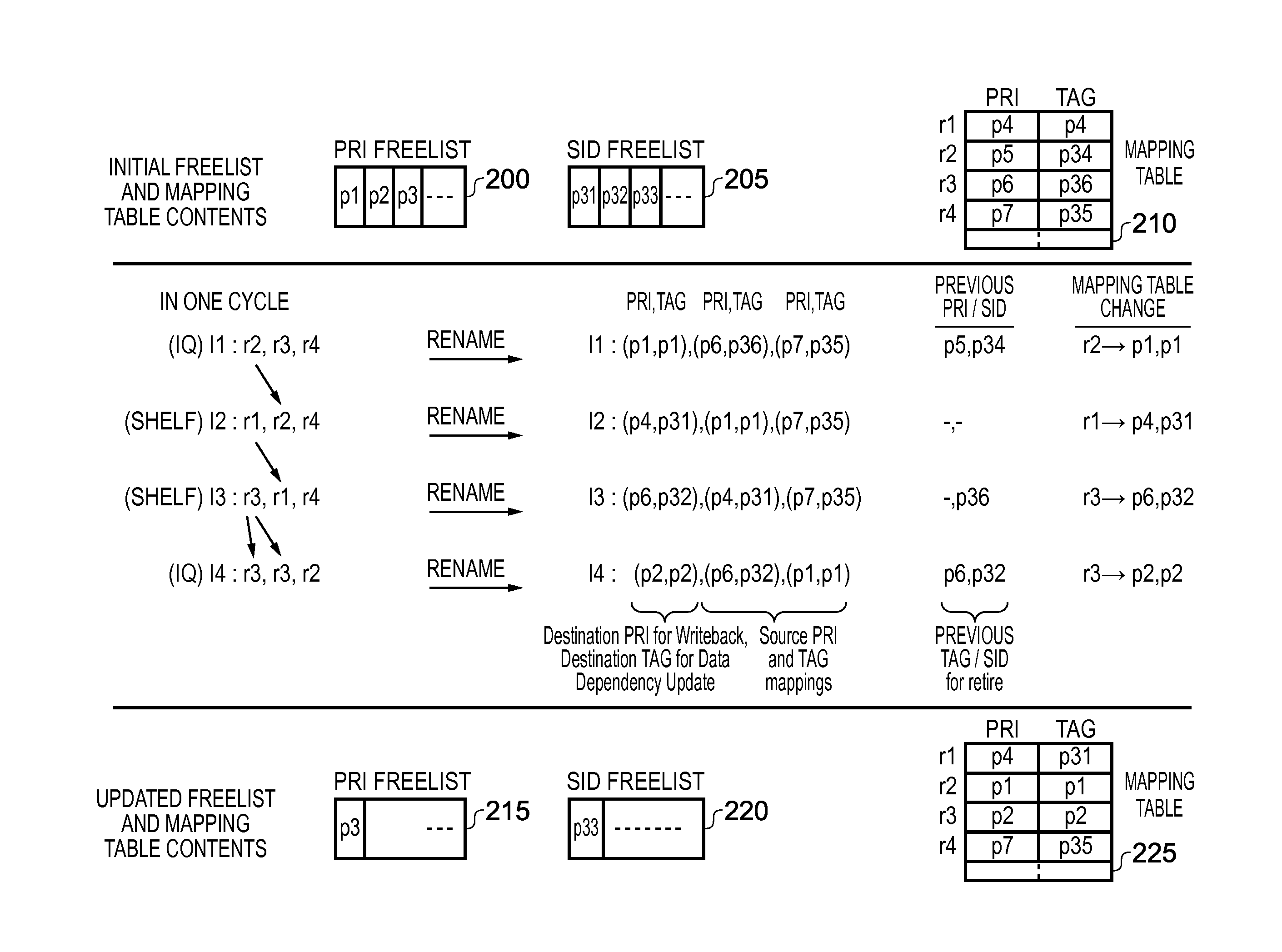

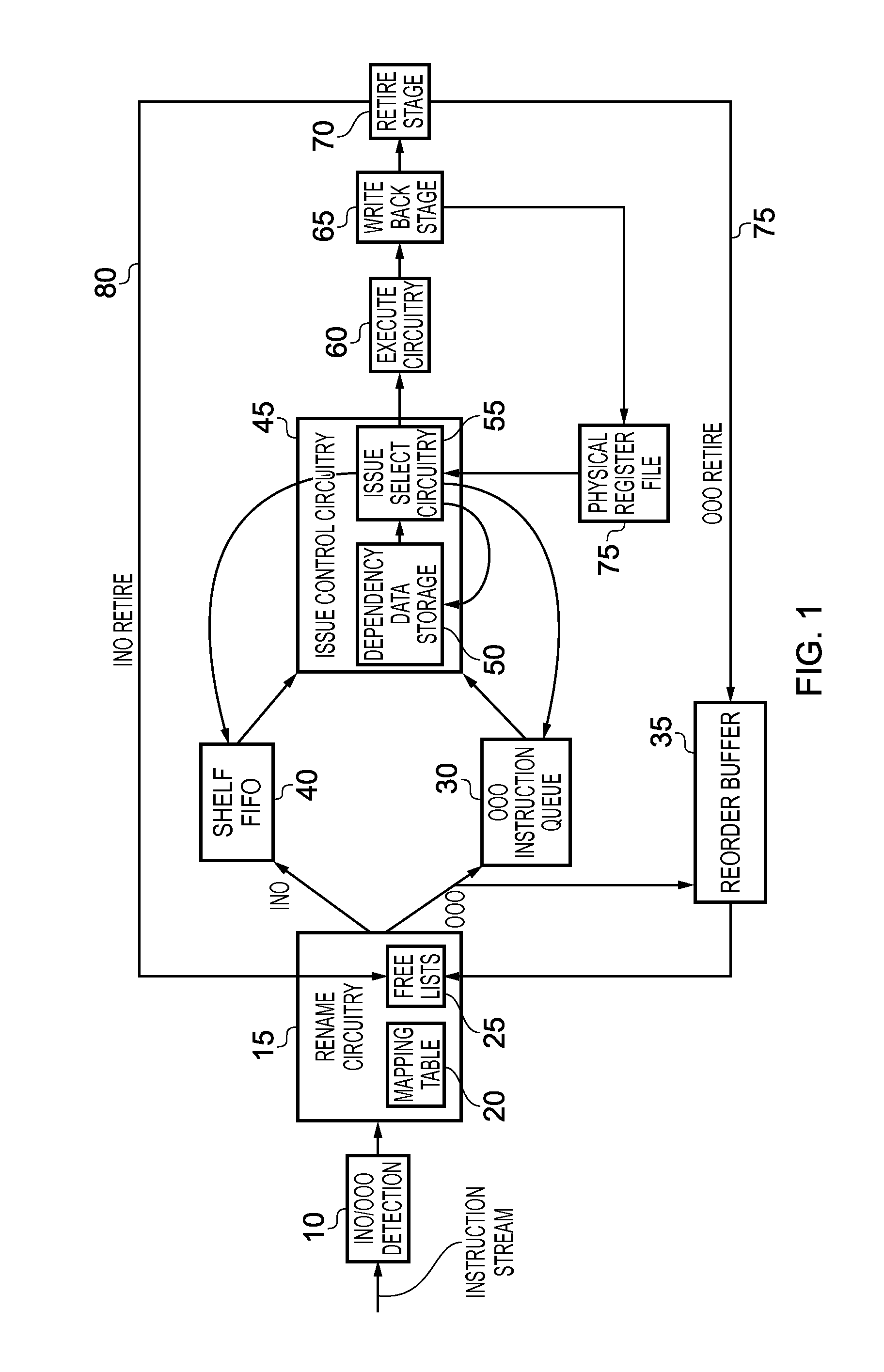

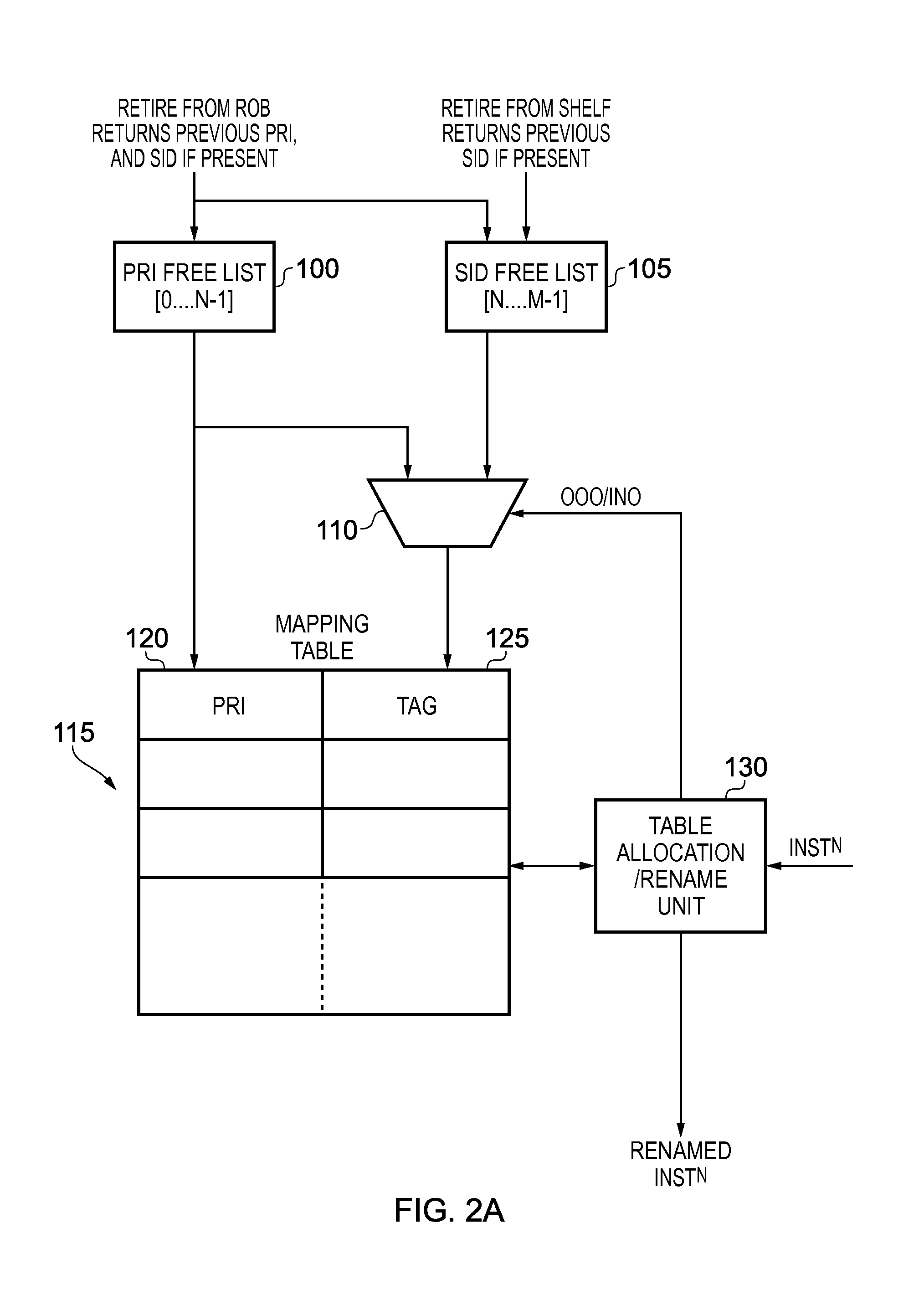

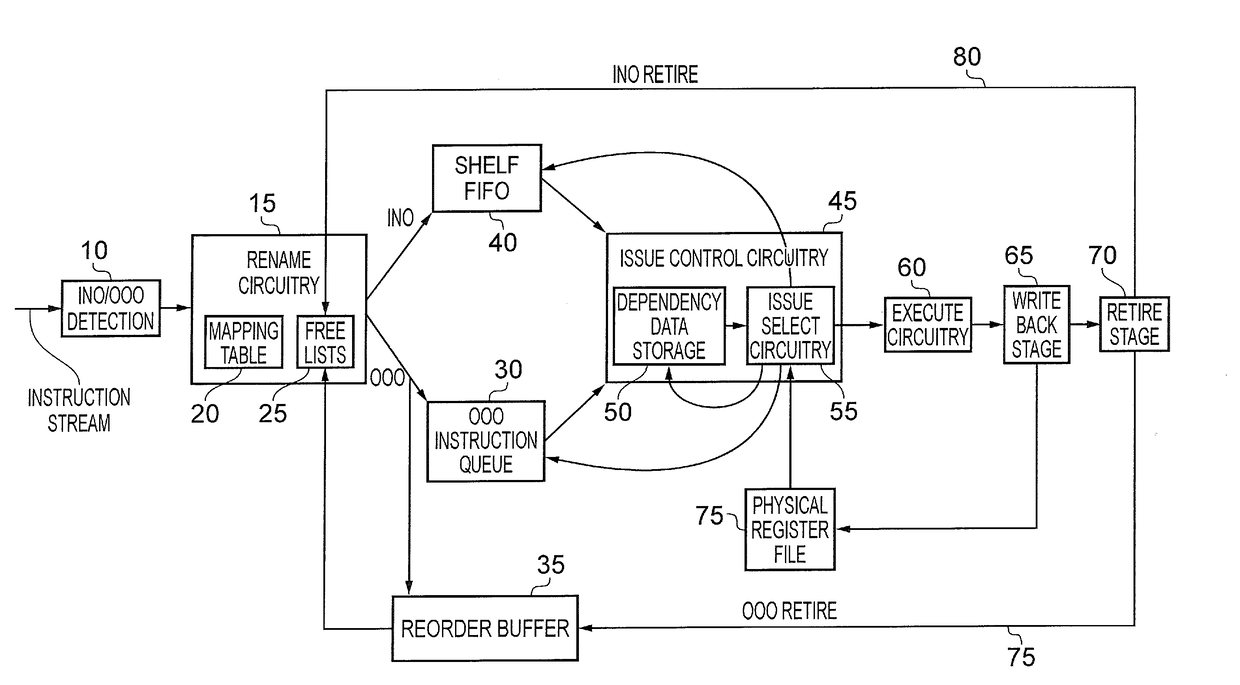

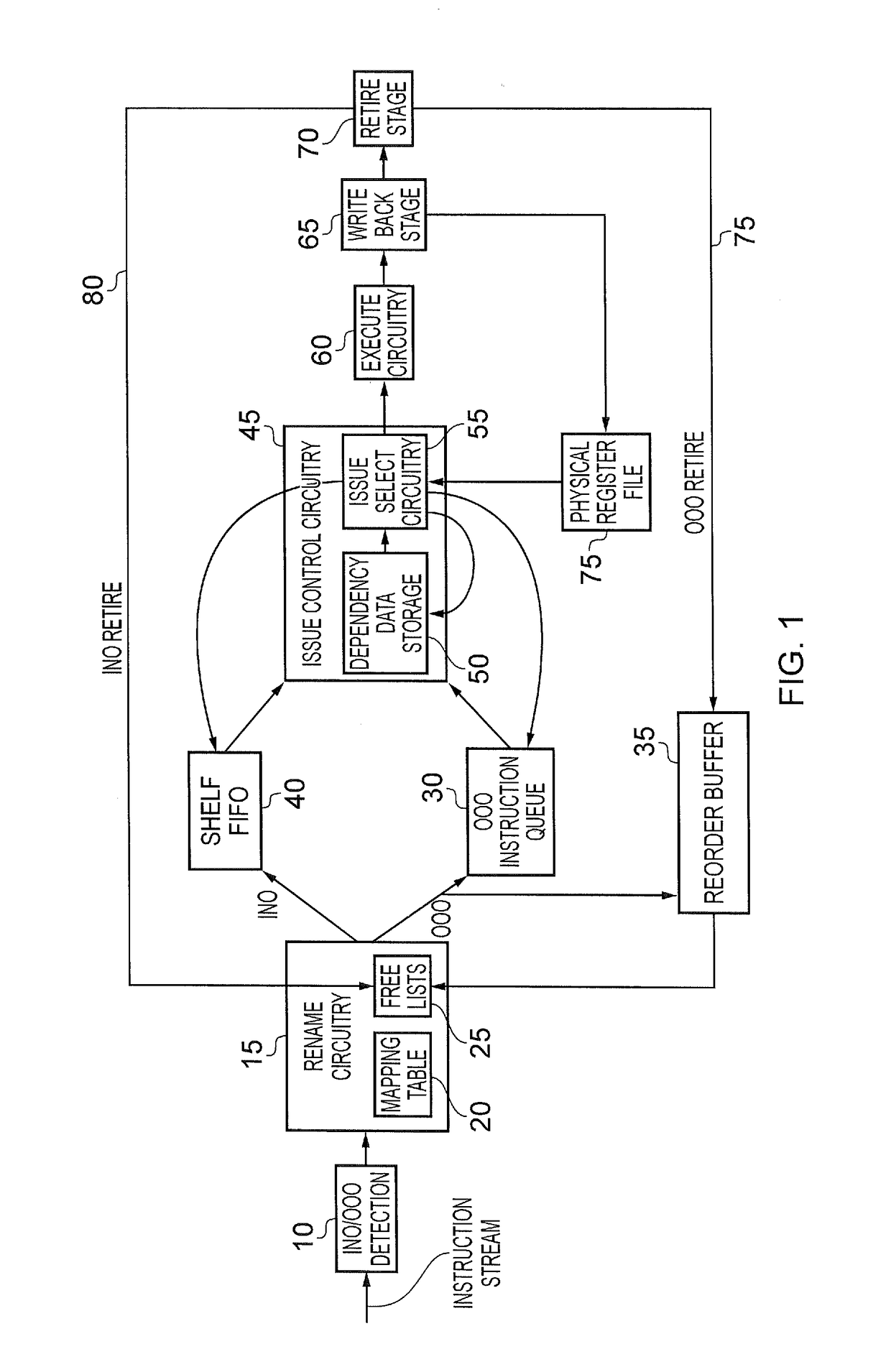

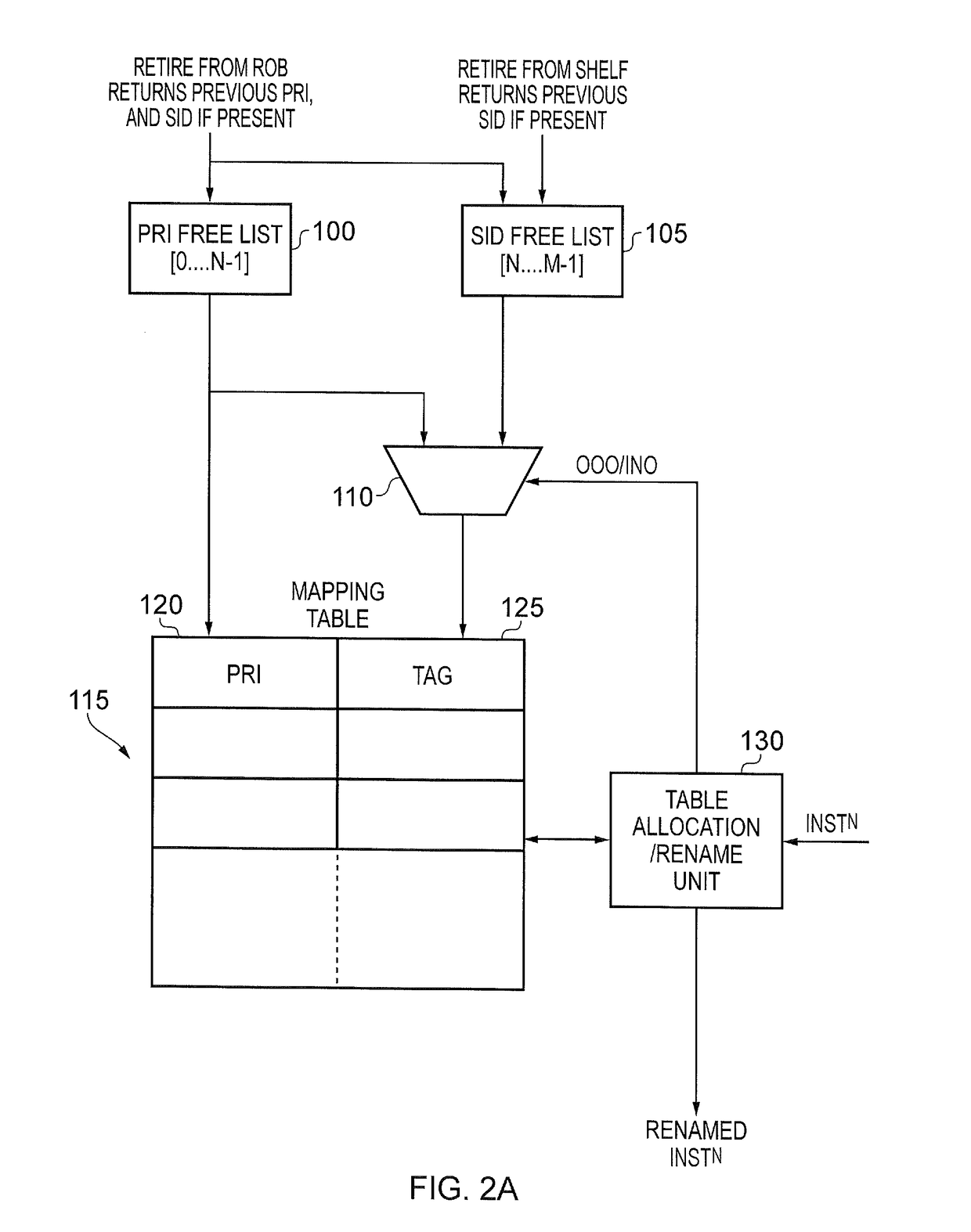

Data processing apparatus and method for executing a stream of instructions out of order with respect to original program order

InactiveUS20150277925A1Reduce energy consumptionIncreases effective instruction windowRegister arrangementsDigital computer detailsParallel computingComputer science

A data processing apparatus and method are provided for executing a stream of instructions out-of-order with respect to original program order. At least some of the instructions in the stream identify one or more architectural registers from a set of architectural registers. The apparatus comprises a plurality of out-of-order components configured to manage execution of a first subset of instructions out-of-order, the plurality of out-of-order components being configured to remove false dependencies between instructions in the first subset. The plurality of out-of-order components include a first issue queue into which the instructions in the first subset are buffered prior to execution. A second issue queue is used to buffer a second subset of instructions prior to execution, the second subset of instructions being constrained to execute in order. Issue control circuitry is configured to reference both issue queues in order to determine an order of execution of instructions, and is configured to constrain the order of execution of the first subset of instructions by true dependencies between the instructions in both the first and second issue queues, and to constrain the order of execution of the second subset of instructions by both the true dependencies and the false dependencies between the instructions in both the first and second issue queues. This approach provides improved performance and / or reduced energy consumption.

Owner:RGT UNIV OF MICHIGAN

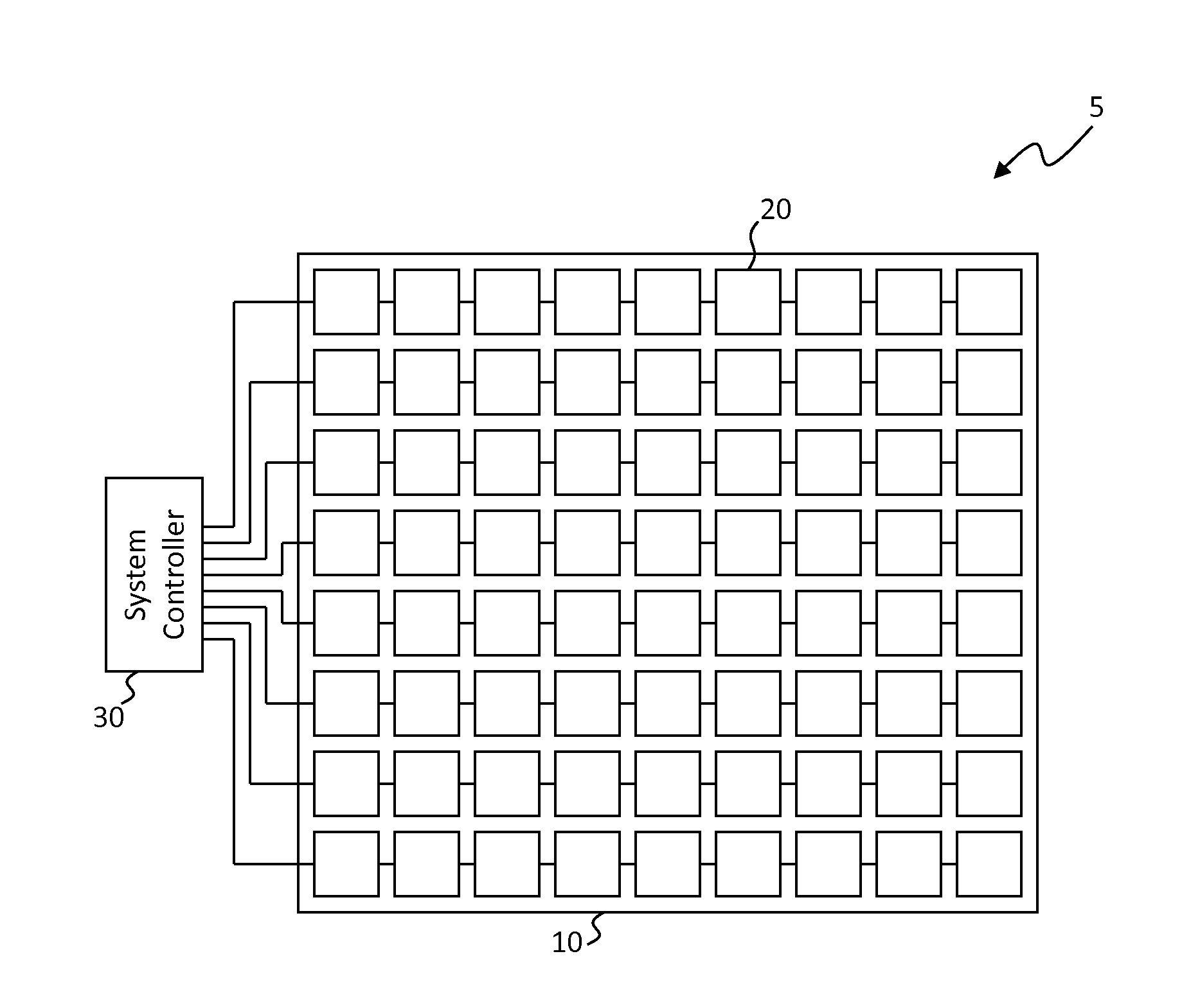

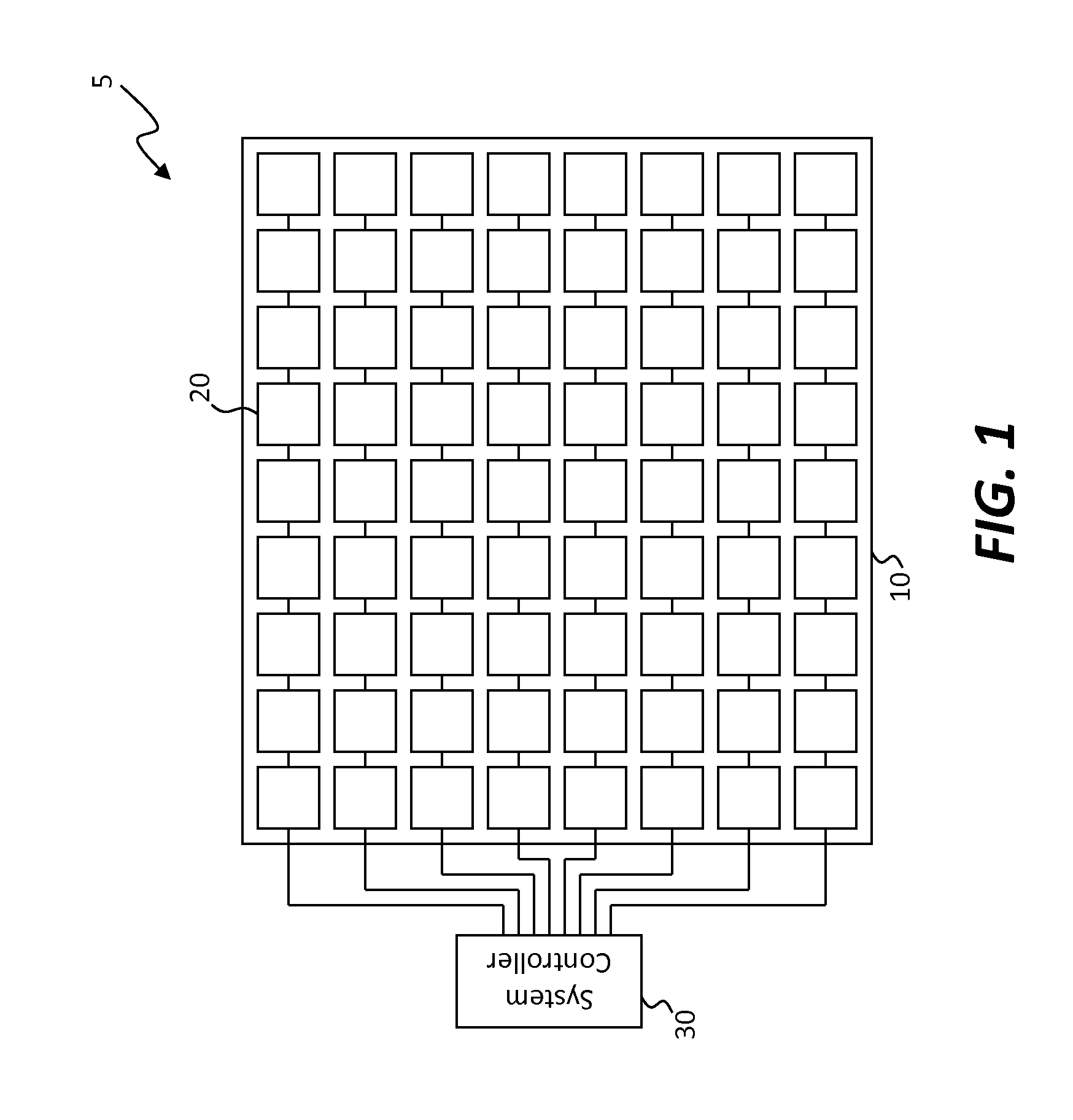

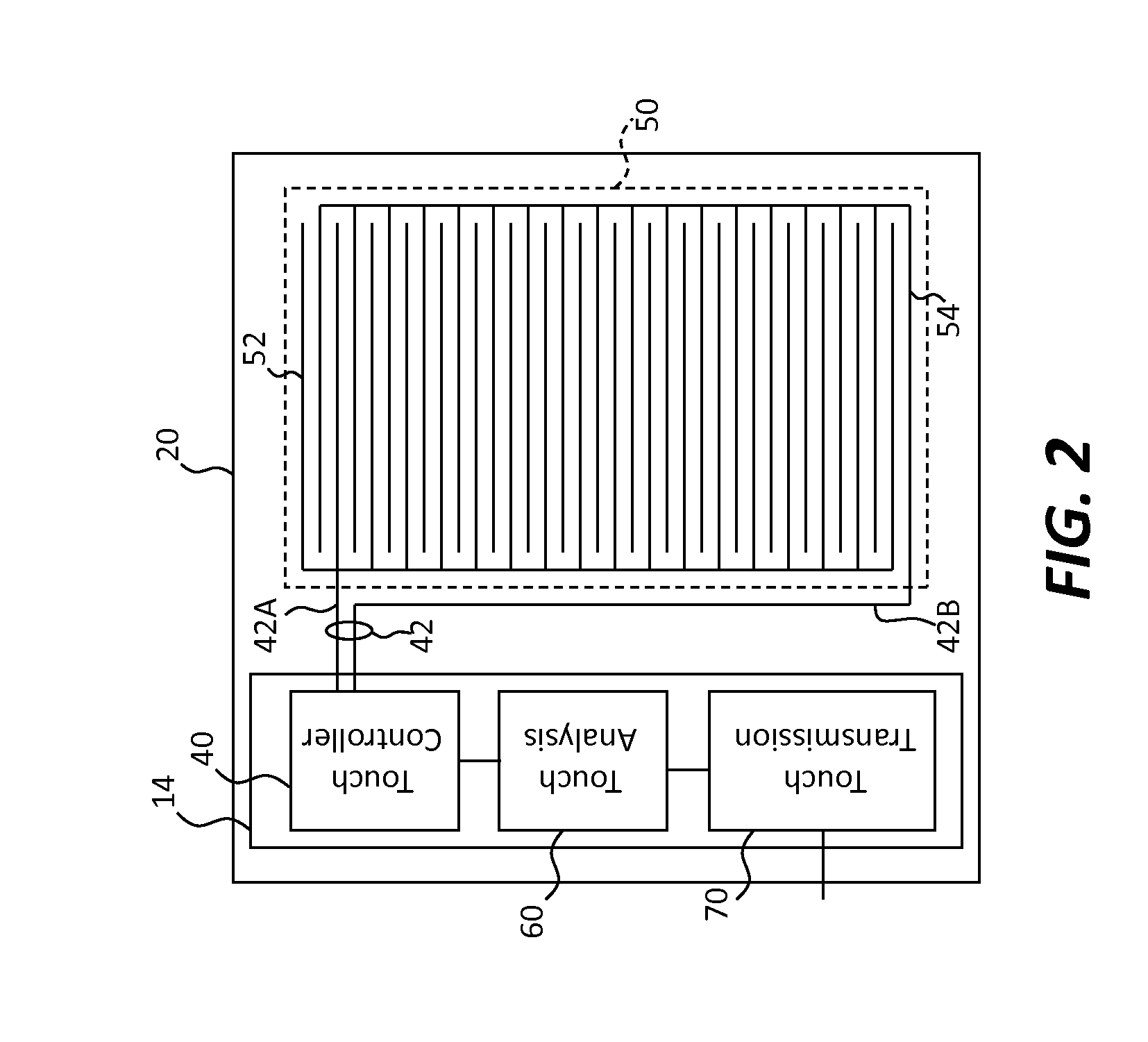

Active-matrix touchscreen

ActiveUS20170010706A1More complexImprove performanceSolid-state devicesInput/output processes for data processingActive matrixControl signal

An active-matrix touchscreen includes a substrate, a system controller, and a plurality of spatially separated independent touch elements disposed on the substrate. Each touch element includes a touch sensor and a touch controller circuit that provides one or more sensor-control signals to the touch sensor and receives a sense signal responsive to the sensor-control signals from the touch sensor. Each touch sensor operates independently of any other touch sensor.

Owner:X DISPLAY CO TECH LTD

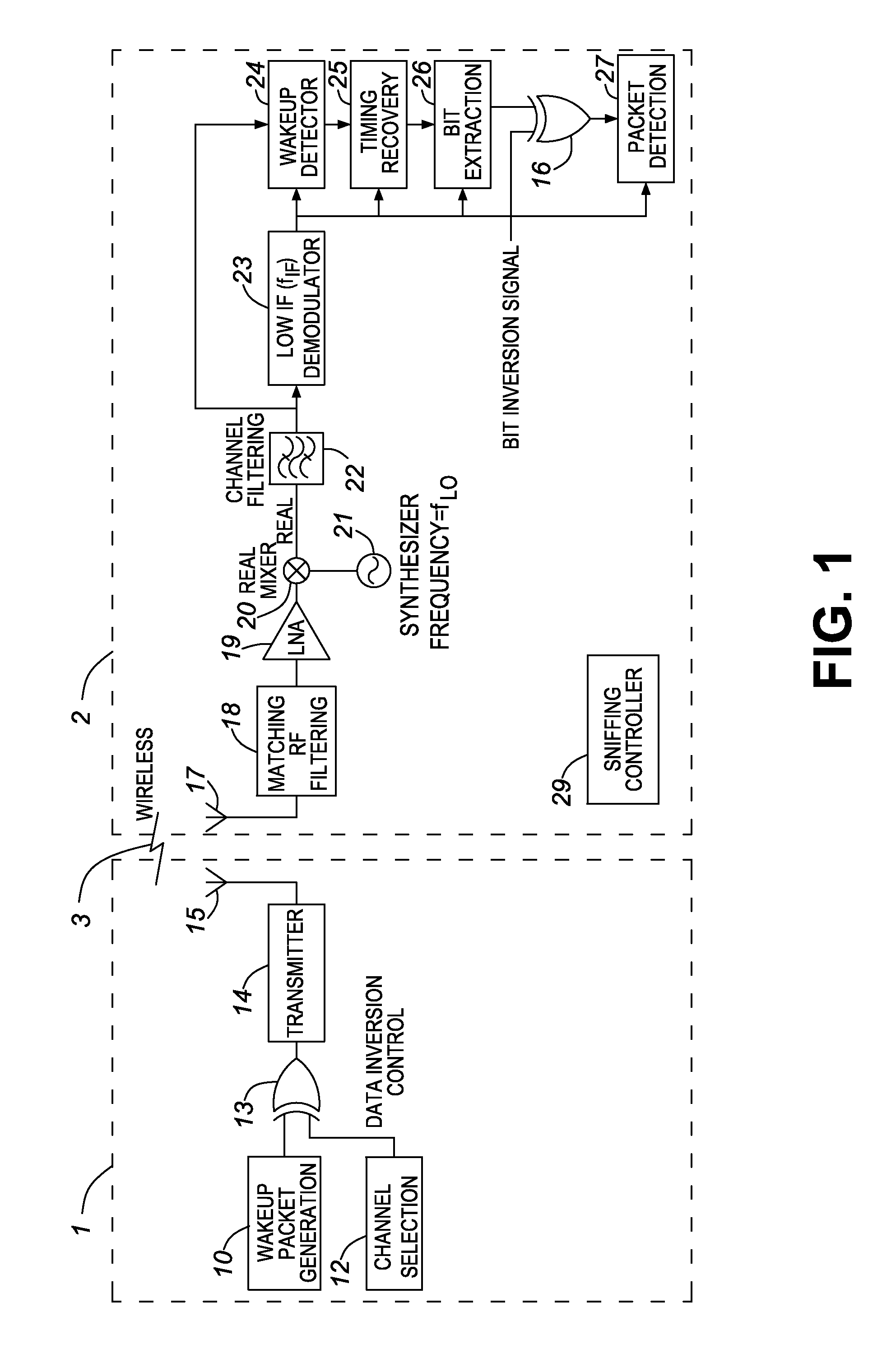

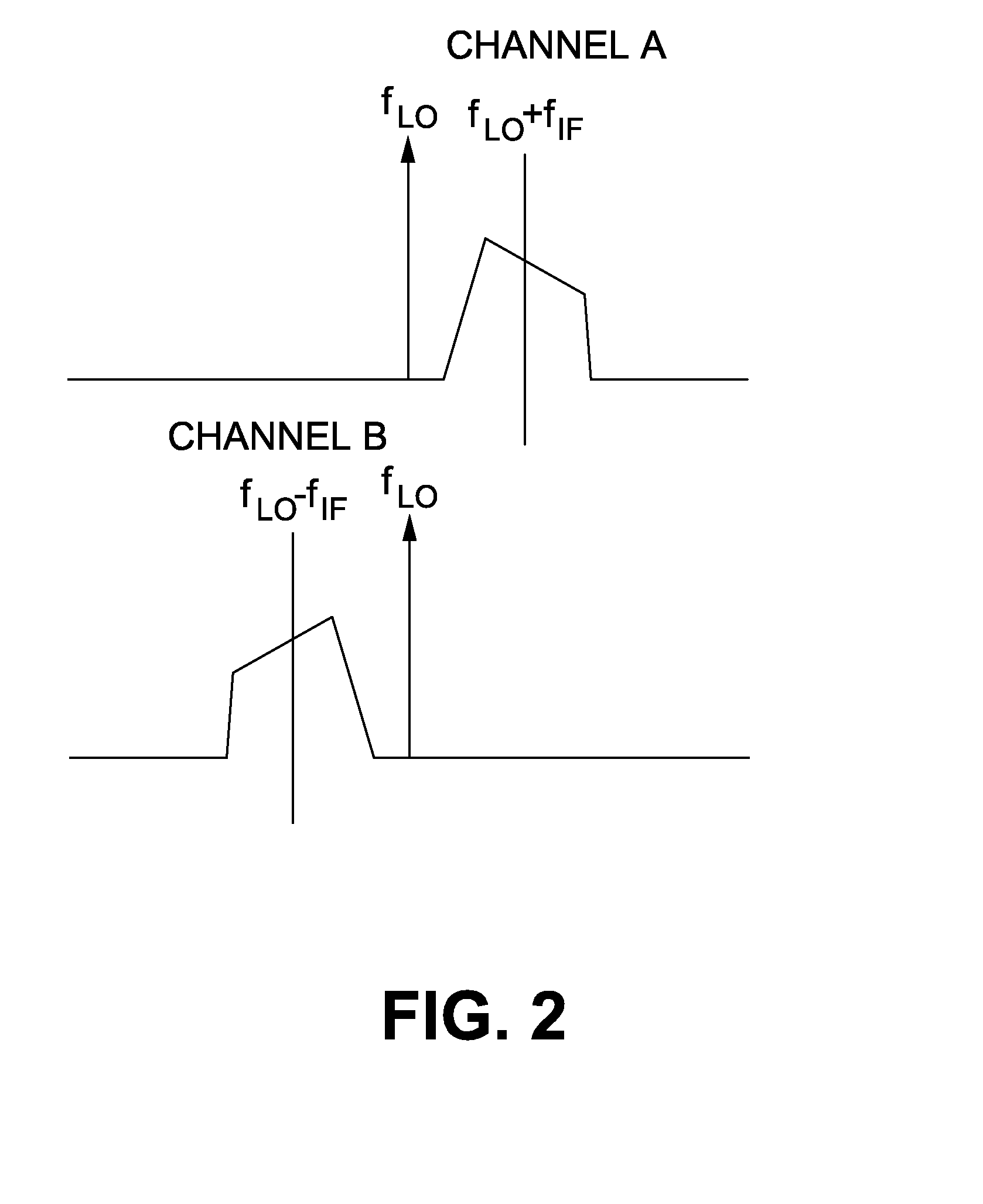

Multi-channel low power wake-up system

ActiveUS20150071151A1Reduce power consumptionTotal current dropPower managementTransmission systemsLocal oscillator signalIntermediate frequency

A wake-up system includes an instigator for transmitting a wake-up message from a primary node to a receiver at a secondary node. The instigator sends a wake-up on either first RF channel or a second RF channel having respective frequencies such that the second RF channel is an image of the first RF channel at a local oscillator frequency of the receiver. The receiver includes an RF filter that passes both the image and non-image channels, a frequency generator for generating a local oscillator signal at the local oscillator frequency, and a mixer for mixing the filtered modulated RF signal with said local oscillator signal to generate a modulated intermediate frequency (IF) signal. The receiver monitors both the image and non-image channels simultaneously for a valid wake-up message. A wake-up message detector indicates a wake-up condition in response to the reception of a valid wake-up message.

Owner:MICROSEMI

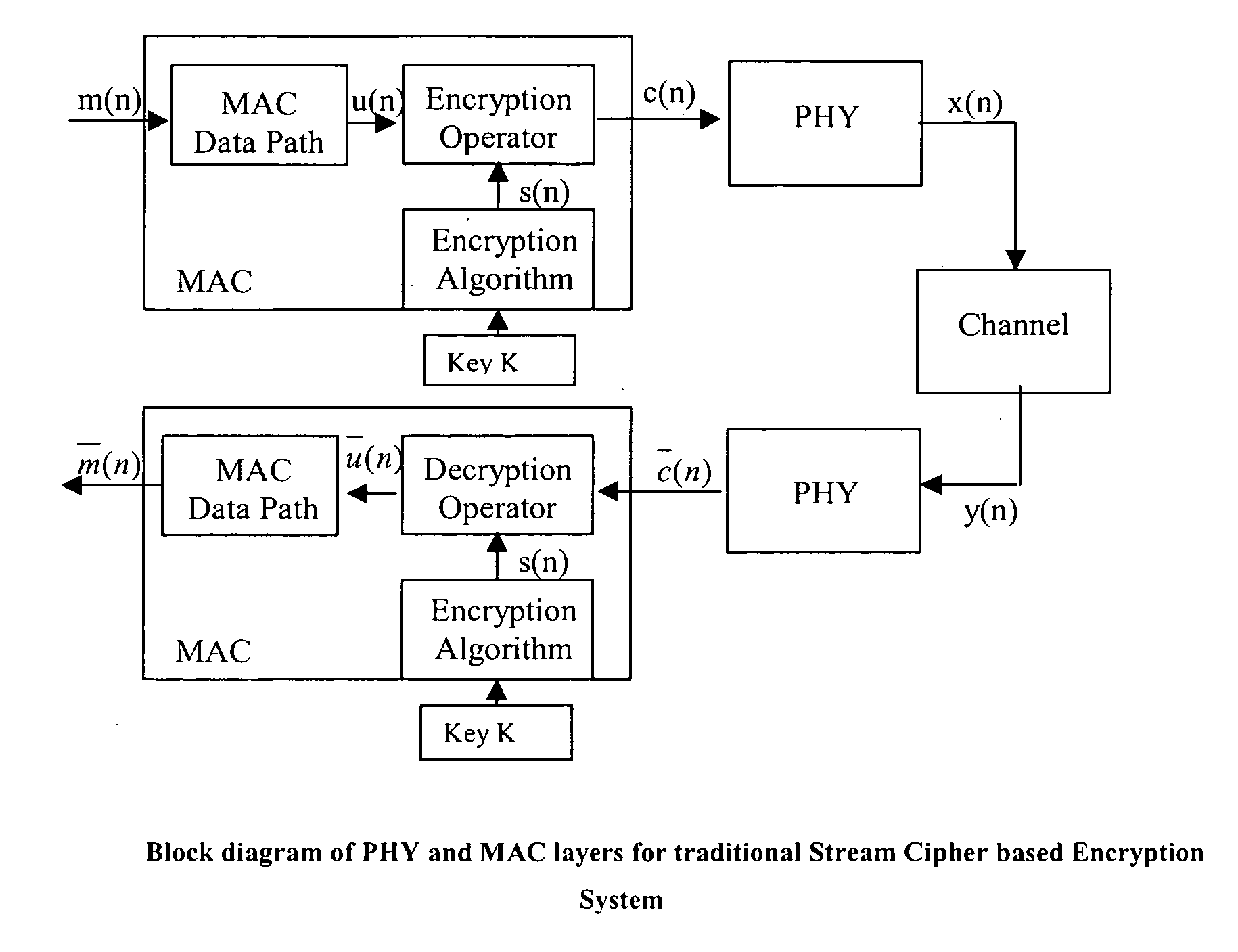

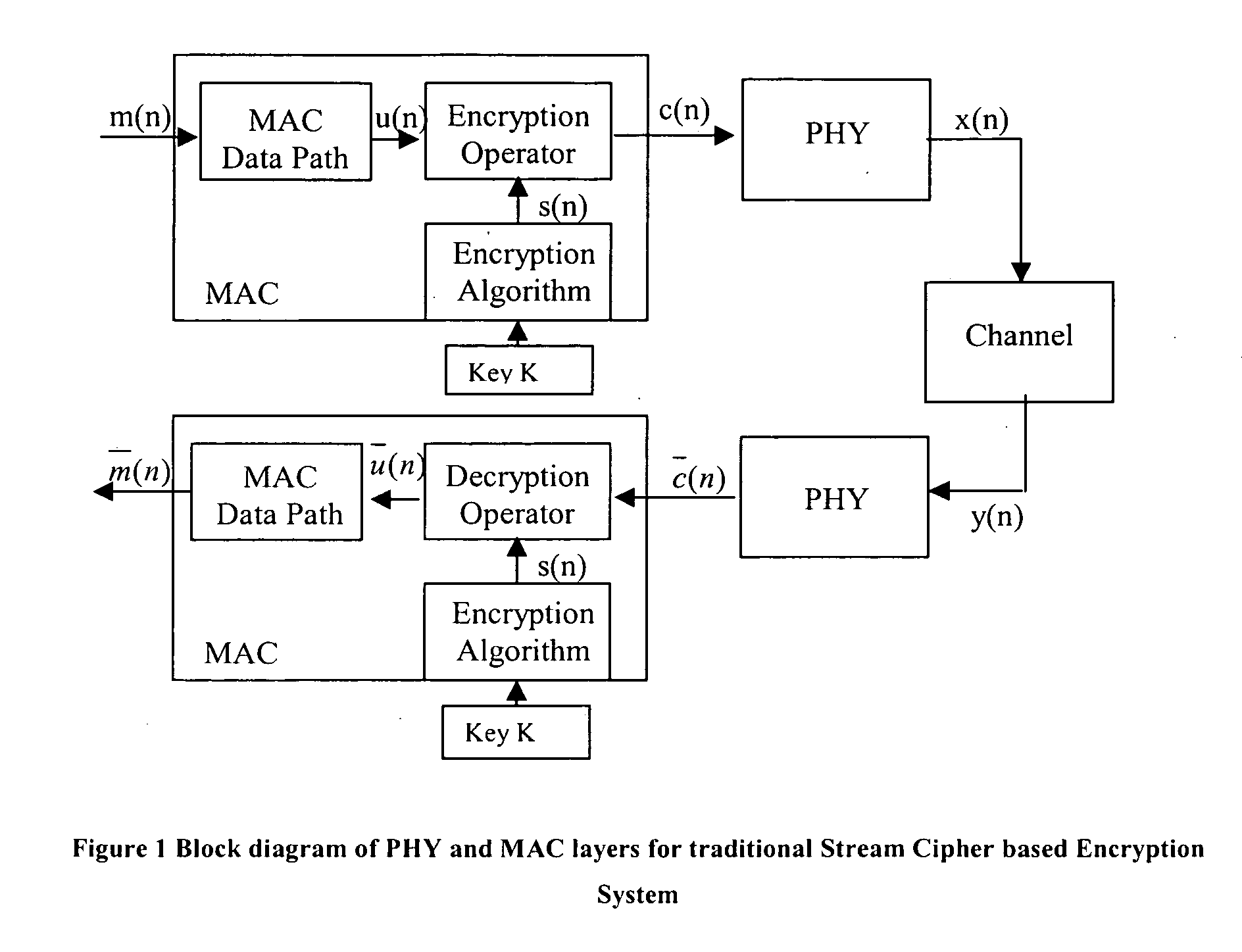

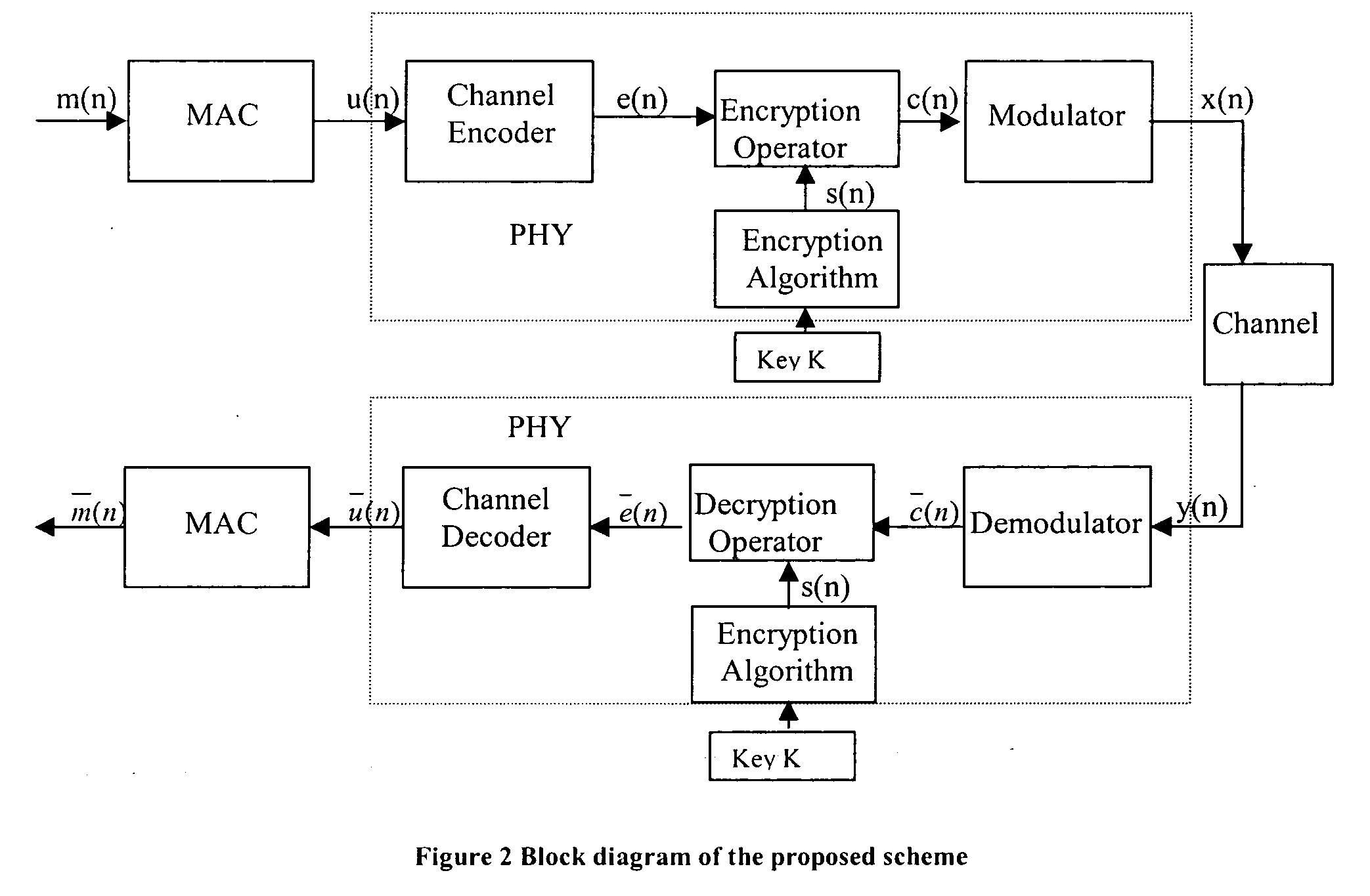

Method and apparatus for a security system for wireless networks

InactiveUS20060126841A1Avoid attackImprove communication performanceData stream serial/continuous modificationSecret communicationViterbi decoderCommunications system

A Method and Apparatus for a Security System for Wireless Networks is described. The technique involves encryption and decryption at the Physical layer. It also develops a criterion for choosing the encryption / decryption methodology for a particular embodiment for communication systems typically using a Viterbi Decoder and describes how the difficult-to-invert property of the Viterbi Decoder can be utilized to provide security against known-plaintext attacks. Some candidate encryption / decryption methodologies satisfying the developed criterion are also discussed.

Owner:TATA CONSULTANCY SERVICES LTD

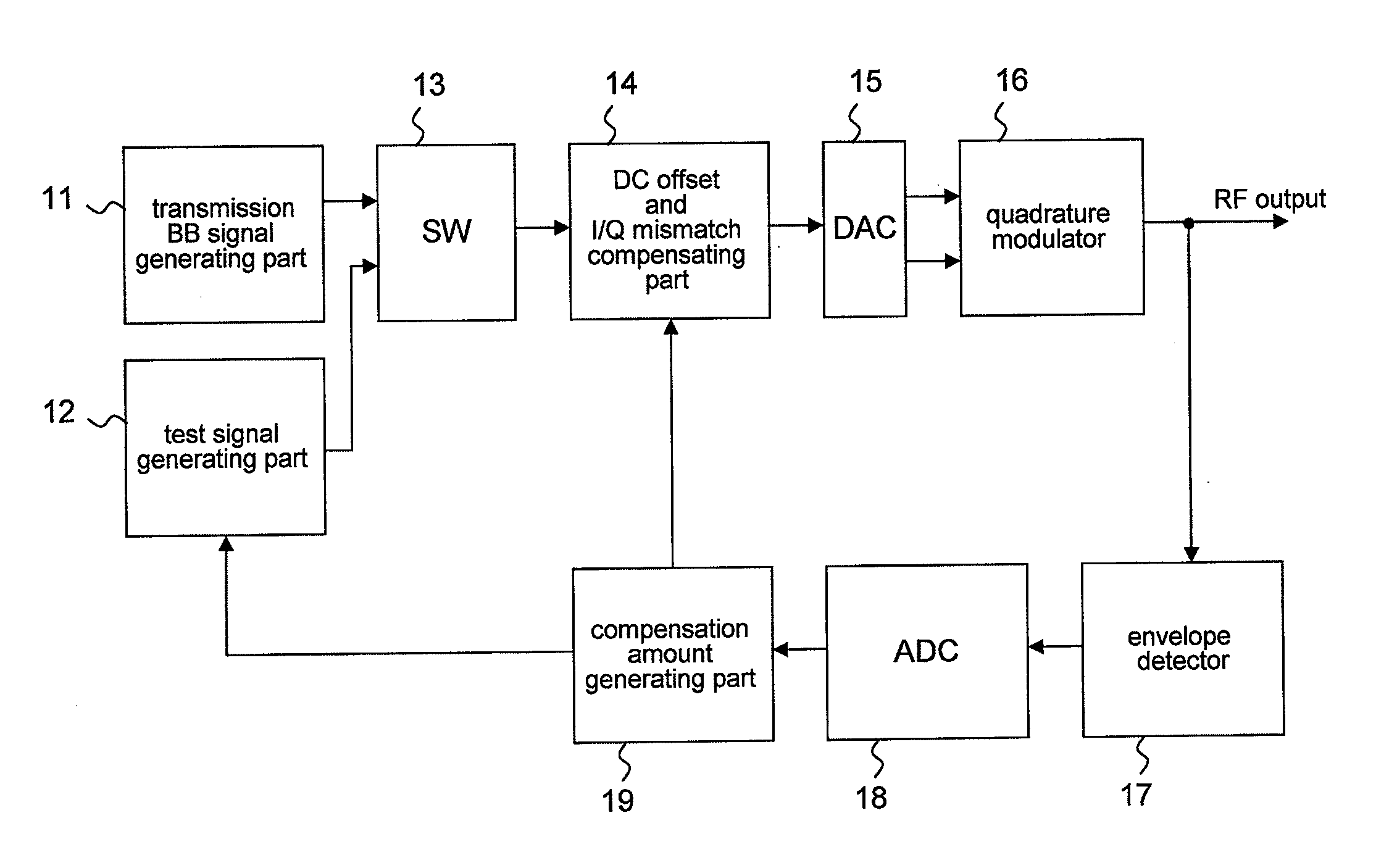

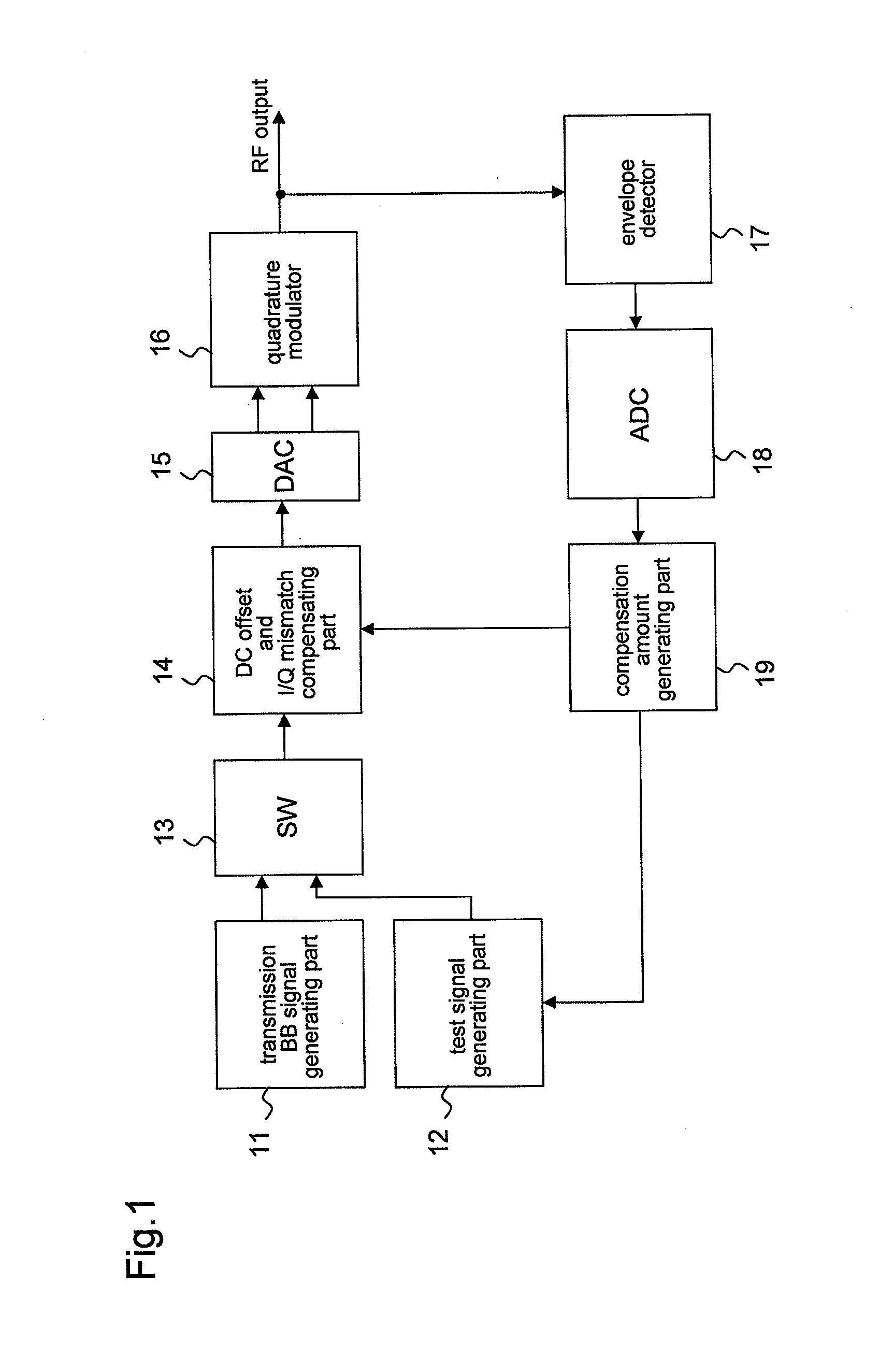

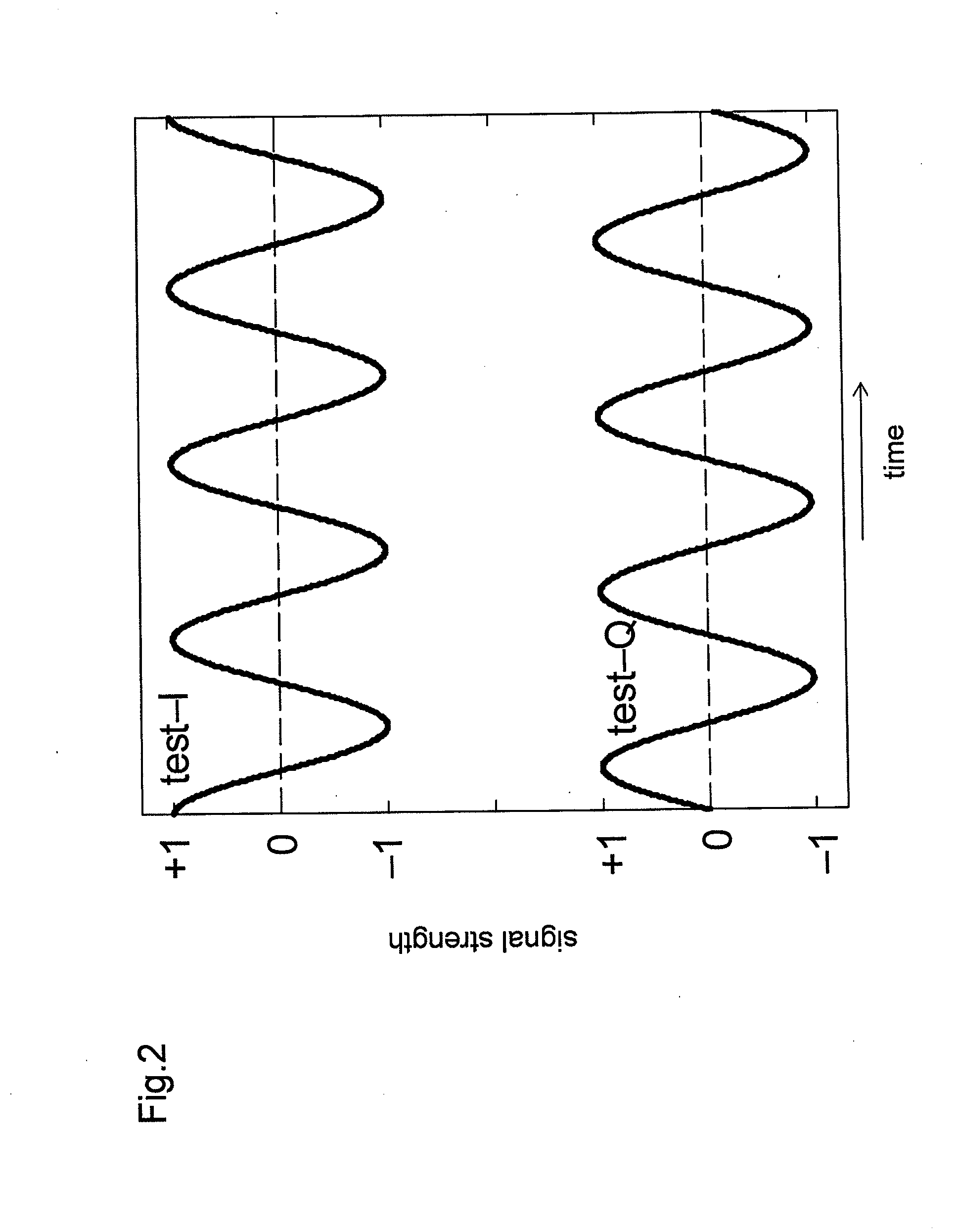

Signal processing circuit and signal processing method

ActiveUS20100195706A1High precision compensationMore complexModulated-carrier systemsTransmission monitoringQuadrature modulatorSignal processing circuits

A signal processing circuit for compensating for an I / Q amplitude mismatch in which the amplitudes of I- and Q-components of output signals of a quadrature modulator are unequal to or for compensating for an I / Q phase mismatch in which the phase difference between the I- and the Q-components of output signals of the quadrature modulator deviates from 90 degrees. The signal processing circuit comprises an I / Q mismatch compensating part that corrects the amplitude or phase of an input signal based on the compensation amount for compensating for an I / Q amplitude mismatch or an I / Q phase mismatch and that inputs the corrected signal into a quadrature modulator; a test signal generating part that sequentially generates and inputs two sets of combined I- and Q-components of a test signal, which is an AC signal, to the I / O mismatch compensating part; a detector that determines an amplitude of the envelope of an output signal of the quadrature modulator; a filter that passes those ones of output signals of the detector which have frequencies equal to or lower than a cutoff frequency; and a control part that derives an amplitude or phase compensation amount of the I / Q mismatch compensating part such that the output values of the filter at the time of generating the two respective sets of test signals are equal to each other, the control part then inputting the derived amplitude or phase compensation amount into the I / Q mismatch compensating part.

Owner:NEC CORP

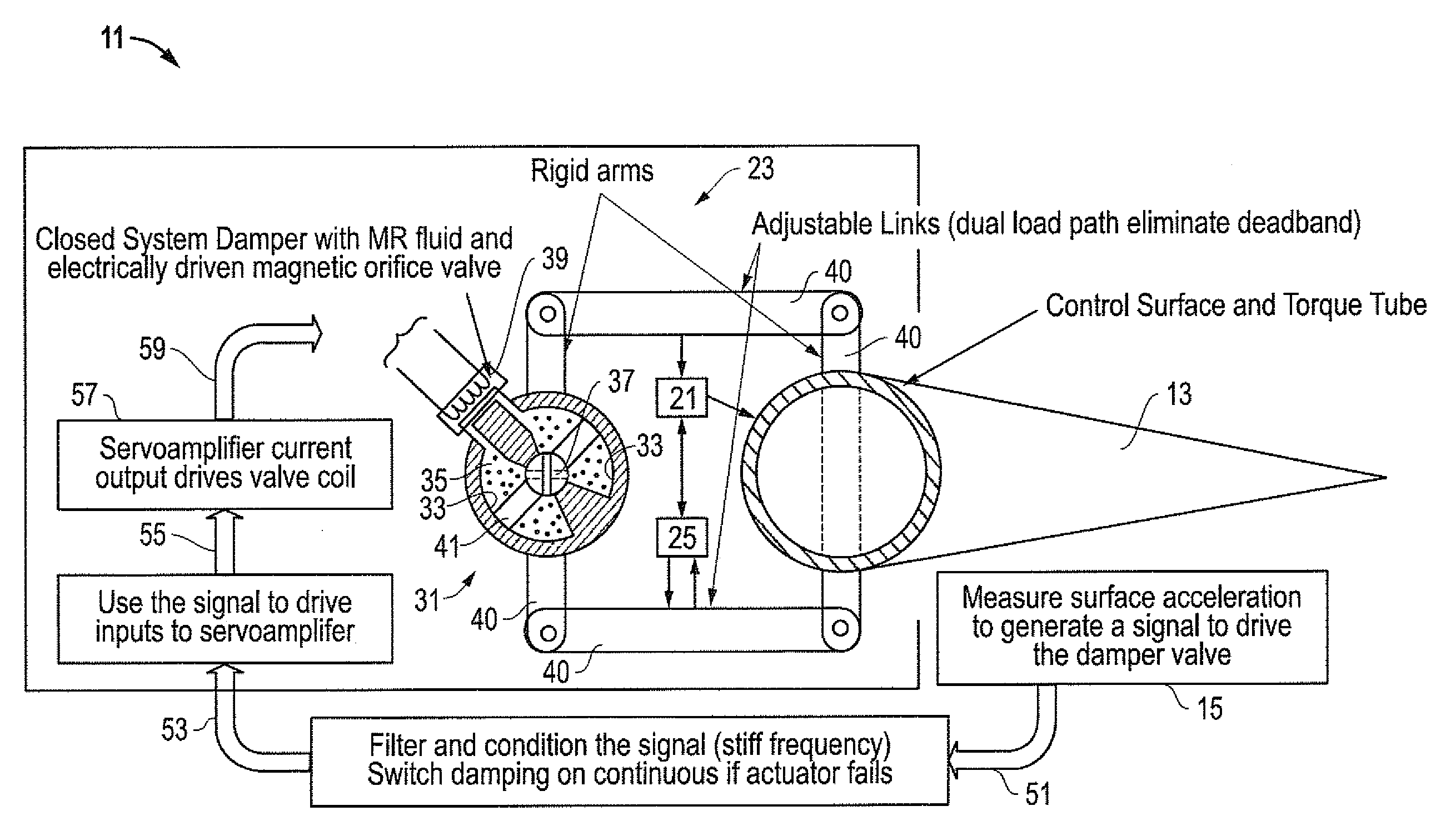

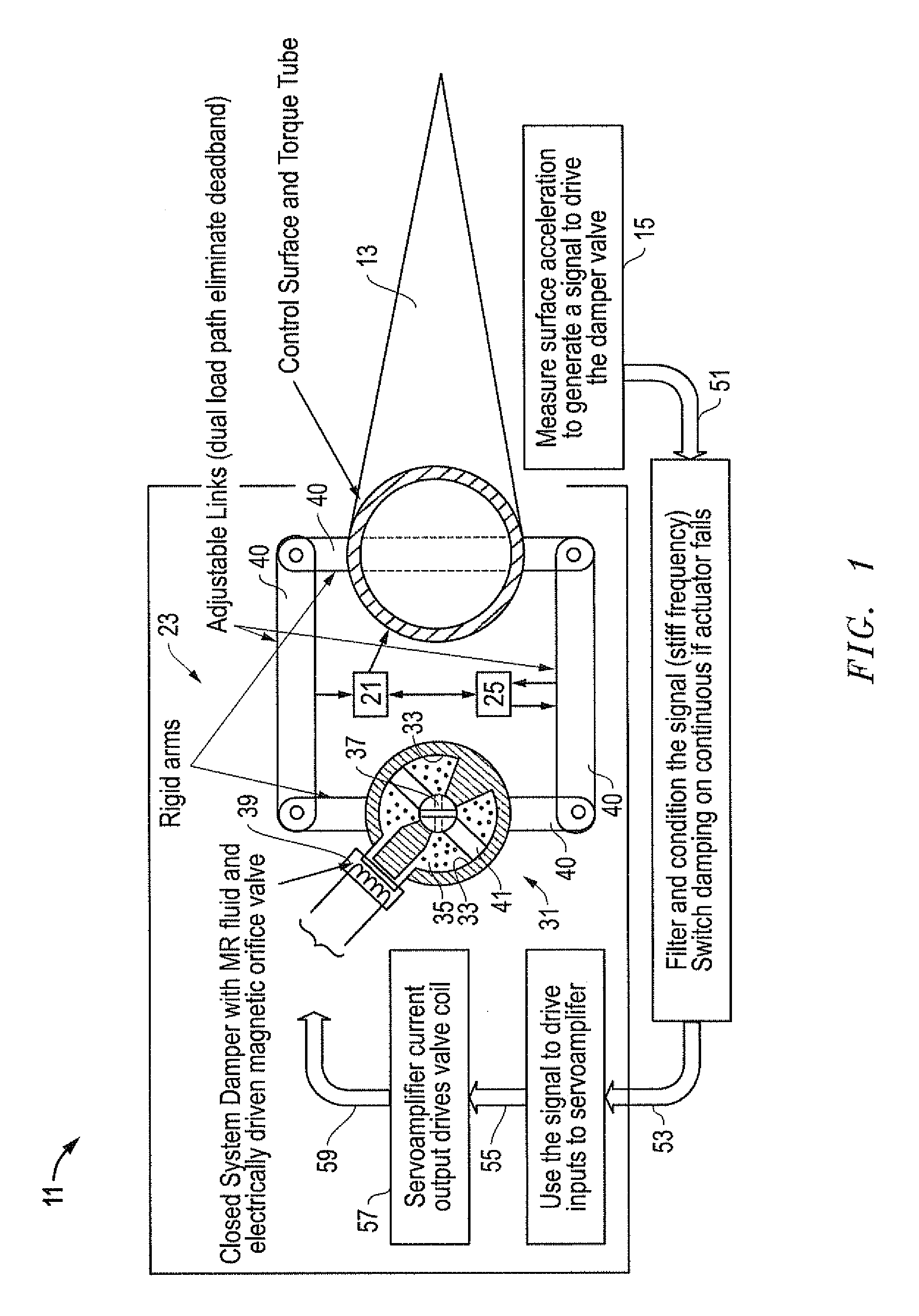

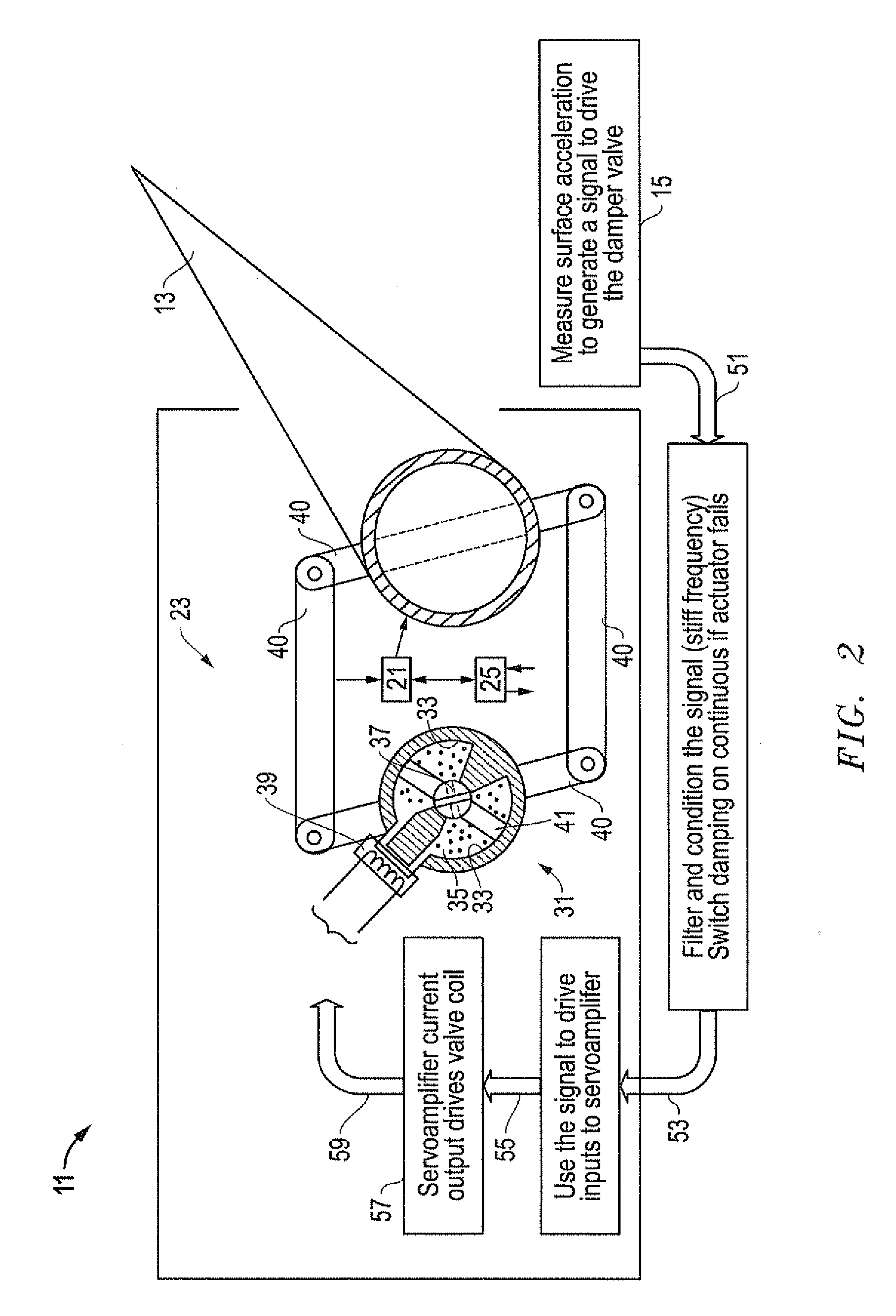

System, method and apparatus for control surface with dynamic compensation

InactiveUS20090302516A1Reduce complexityReduced power capacityNon-rotating vibration suppressionDigital data processing detailsFlight control surfacesFlight vehicle

An aircraft flight control surface has an actuator that employs a magneto-rheological (MR) fluid for dynamically adjusting the responsiveness of the control surface. The MR fluid may be used as a primary or secondary control in the event that a primary control actuator fails. In the event of system failures associated with the primary control, an alternate level of performance may be provided by the secondary control and communicated to the overall flight control system. This permits the control surface actuator to reactively and proactively respond to changes associated with the flight control system. If the design fails, it also permits a safe mode of operation should the ability to dynamically adjust the viscosity of the MR fluid be negatively impacted. The safe mode of operation may involve a reduced level of performance.

Owner:LOCKHEED MARTIN CORP

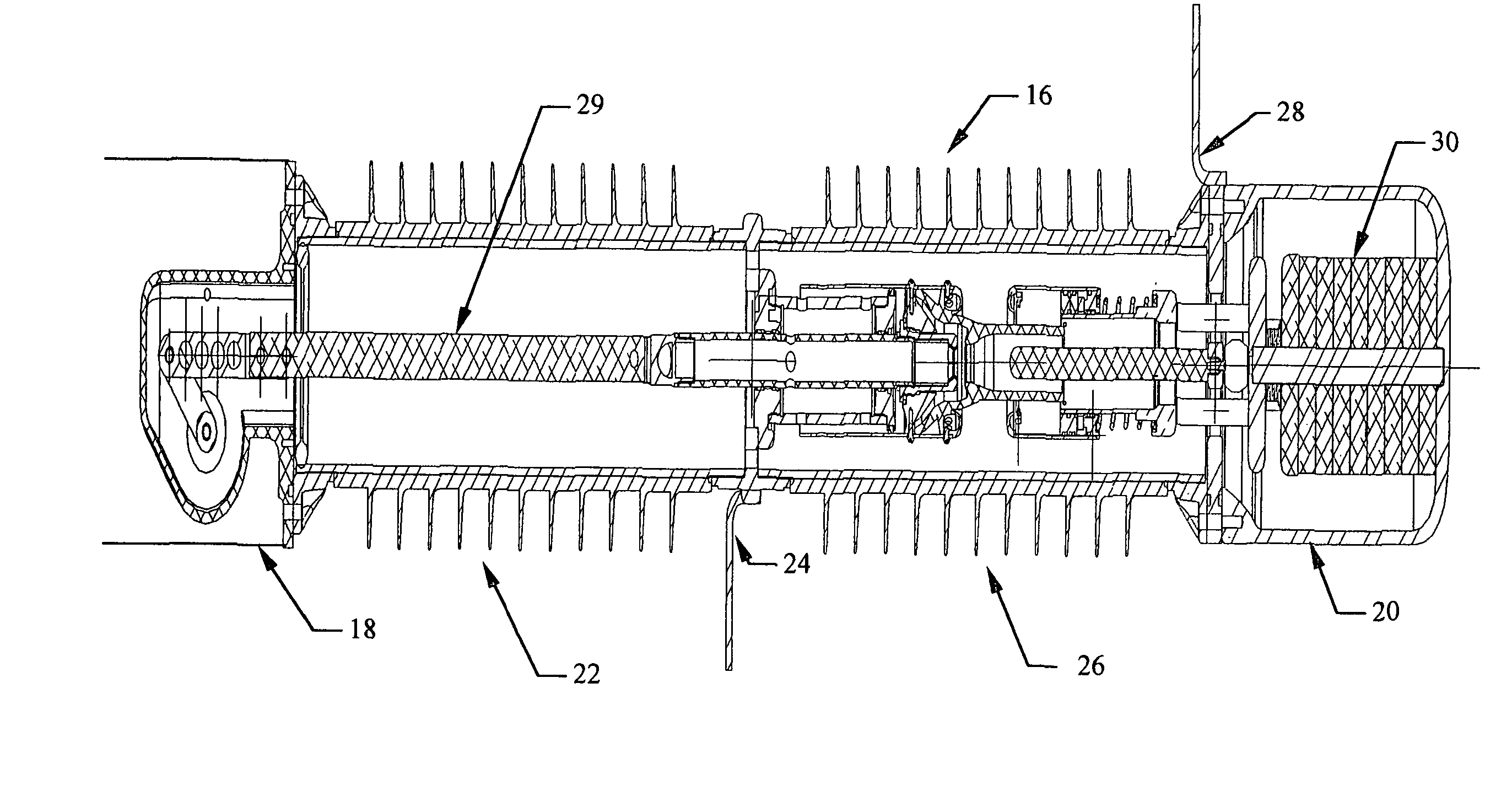

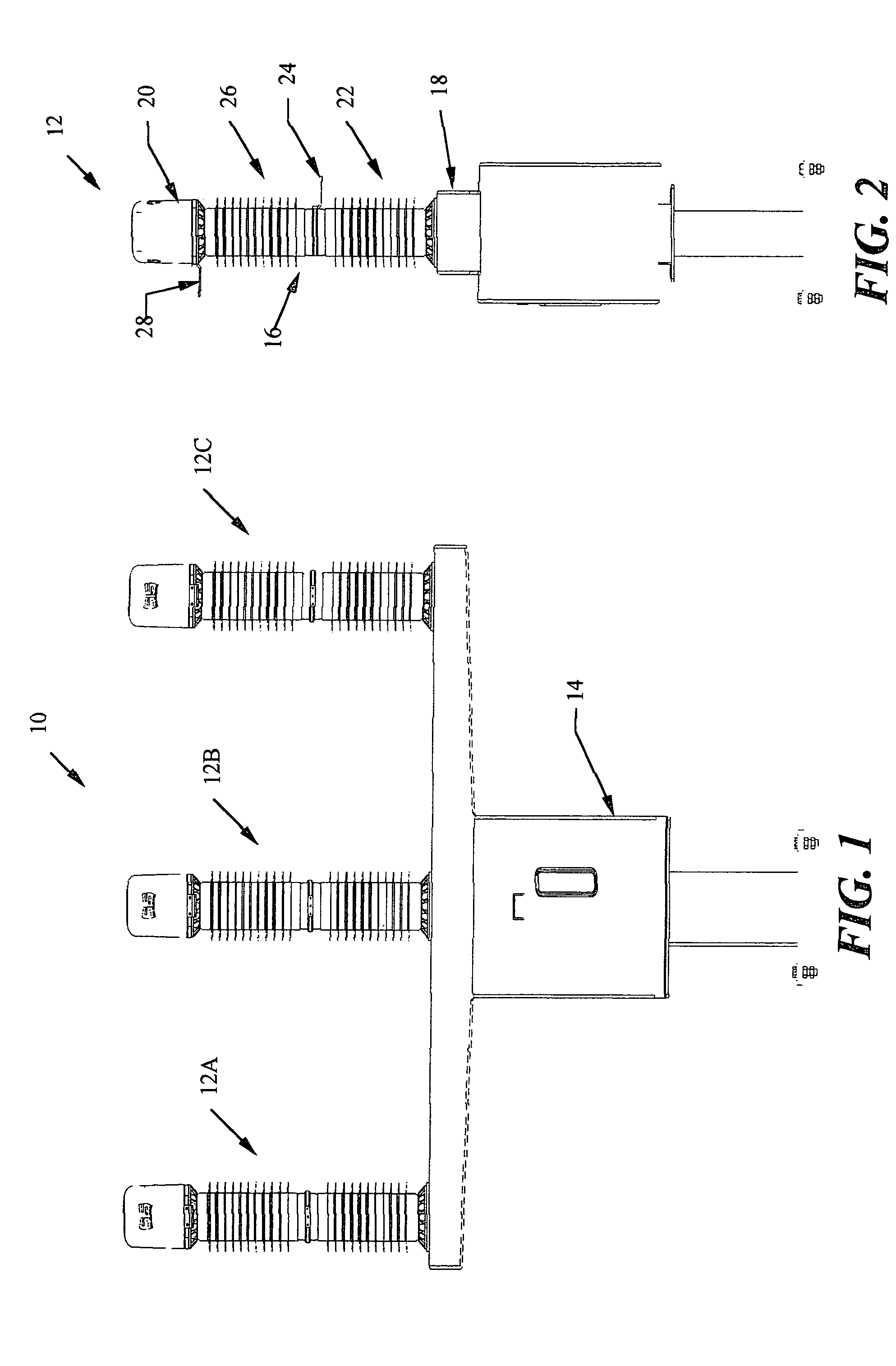

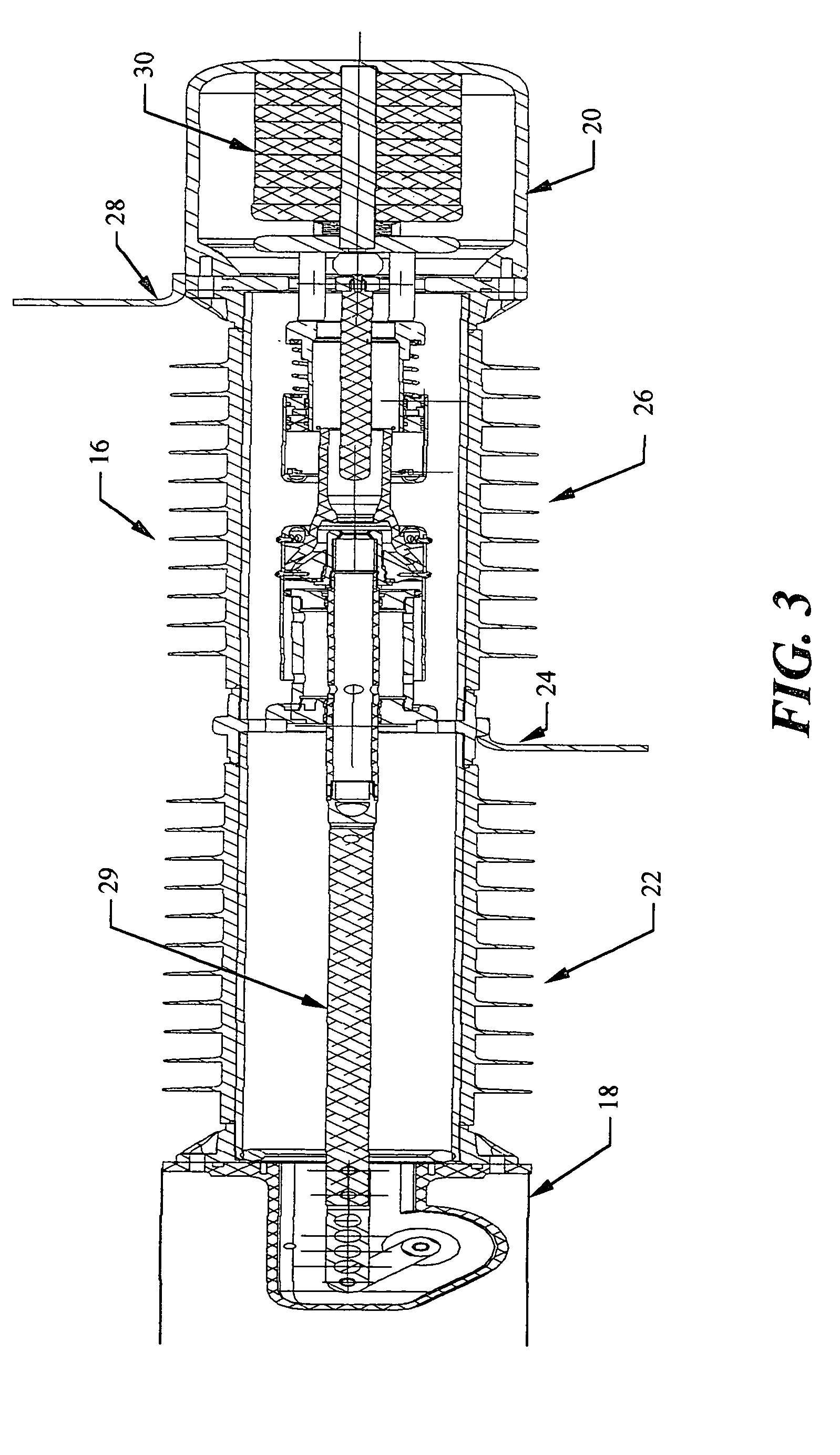

Capacitor switch with internal retracting impedance contactor

ActiveUS7078643B2Easy to removeEasy to replaceHigh-tension/heavy-dress switchesAir-break switchesElectrical impedanceCapacitor

A capacitor switch including a power contactor and an impedance contactor located within a relatively slender container filled with dielectric gas. The container may be a “dead tank” or an insulator. For the insulator configuration, the switch also includes a conductive cap housing a charging impedance located on the end of the insulator. The power contactor includes a relatively fixed probe contact and a linearly moving socket. The impedance contactor is ring-type butt contactor surrounding the penetrating contactor that includes a retracting (but otherwise fixed) contact that surrounds the fixed probe, and a traveling ring contact that surrounds and moves with the moving socket contact. The impedance contactor closes before the power contactor on the closing stroke to introduce the charging impedance into the circuit. A puffer mechanism retards the expansion of the retracting contact on the opening stroke, which causes the impedance contactor to open before the power contactor.

Owner:SOUTHERN STATES

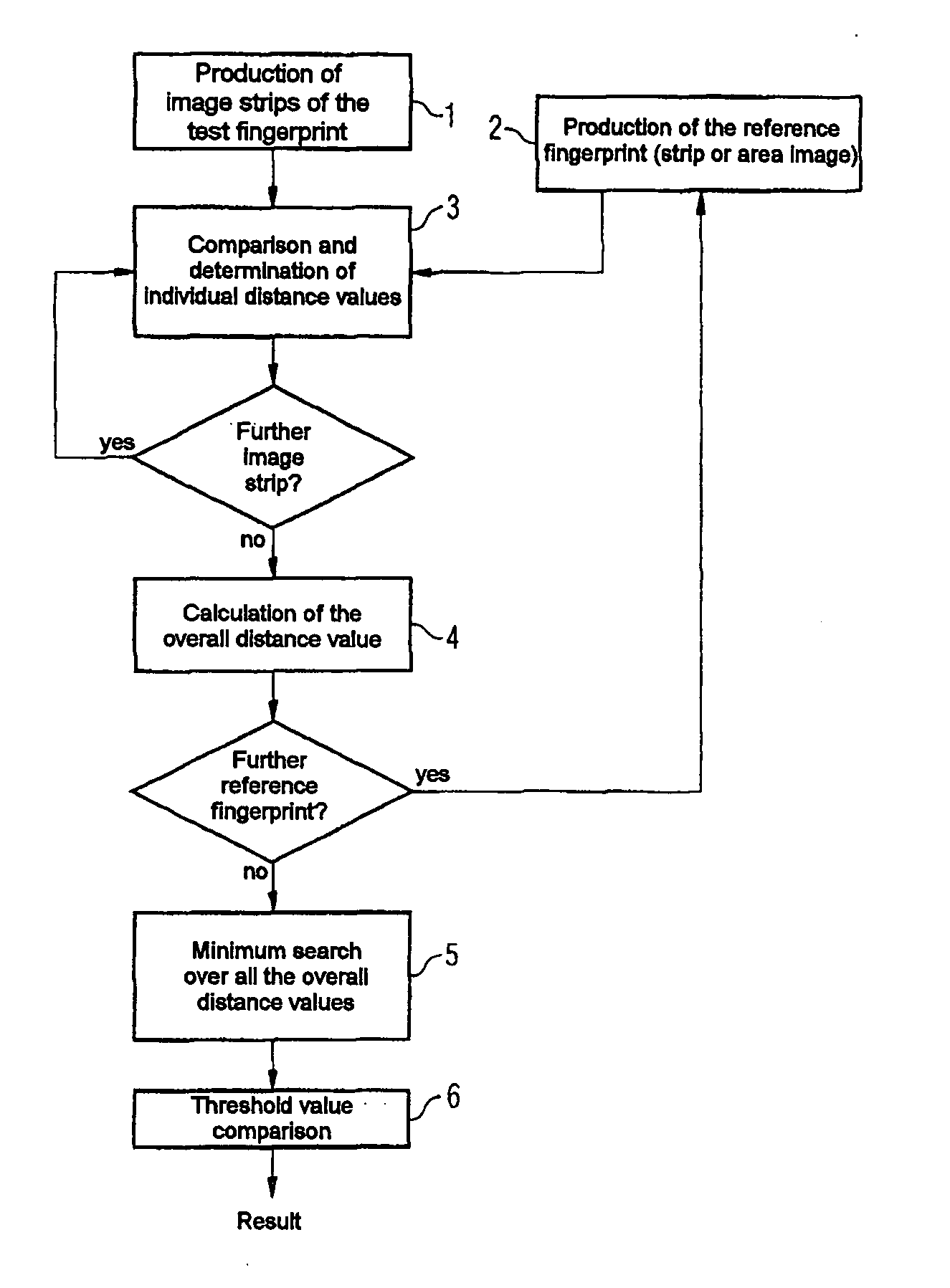

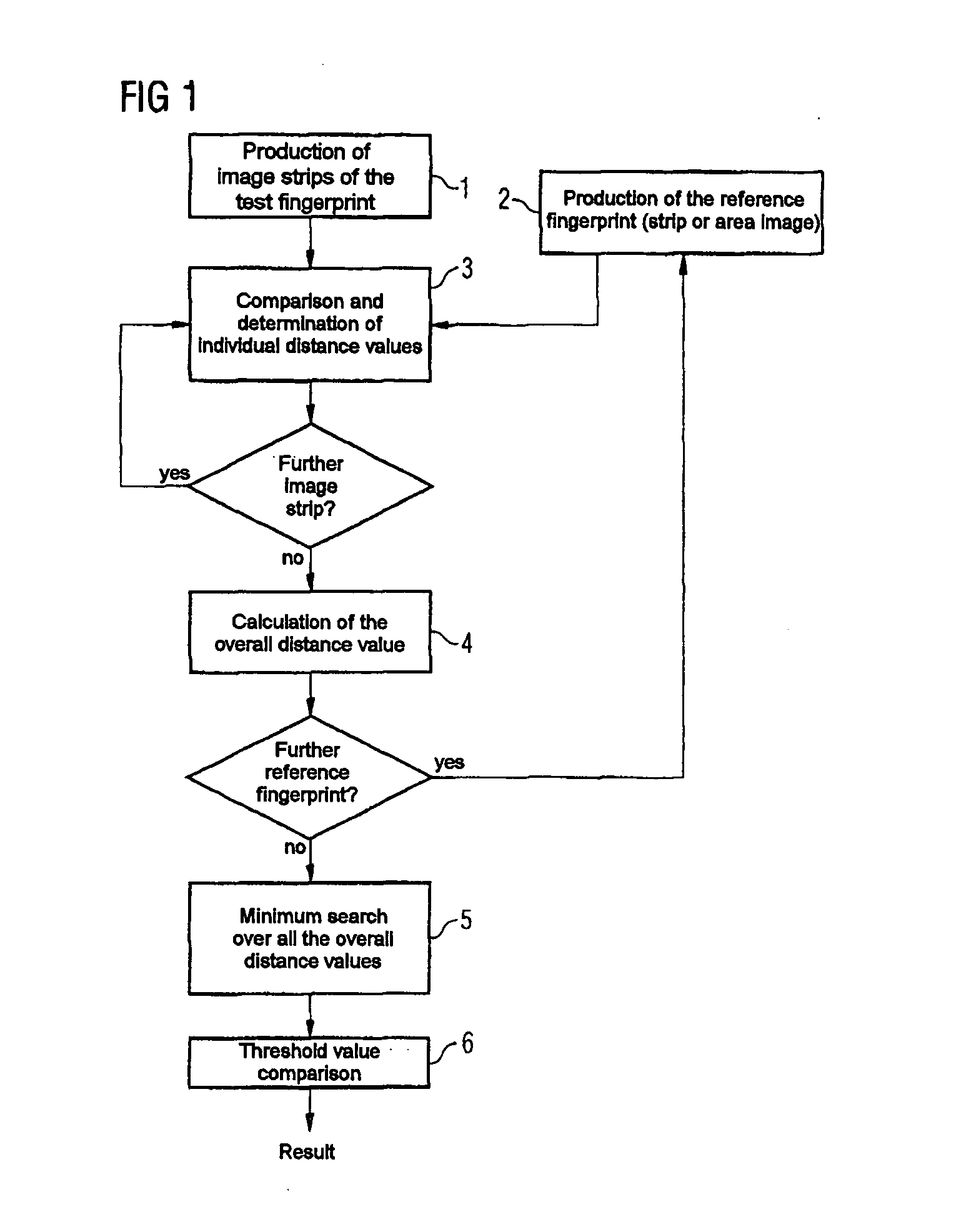

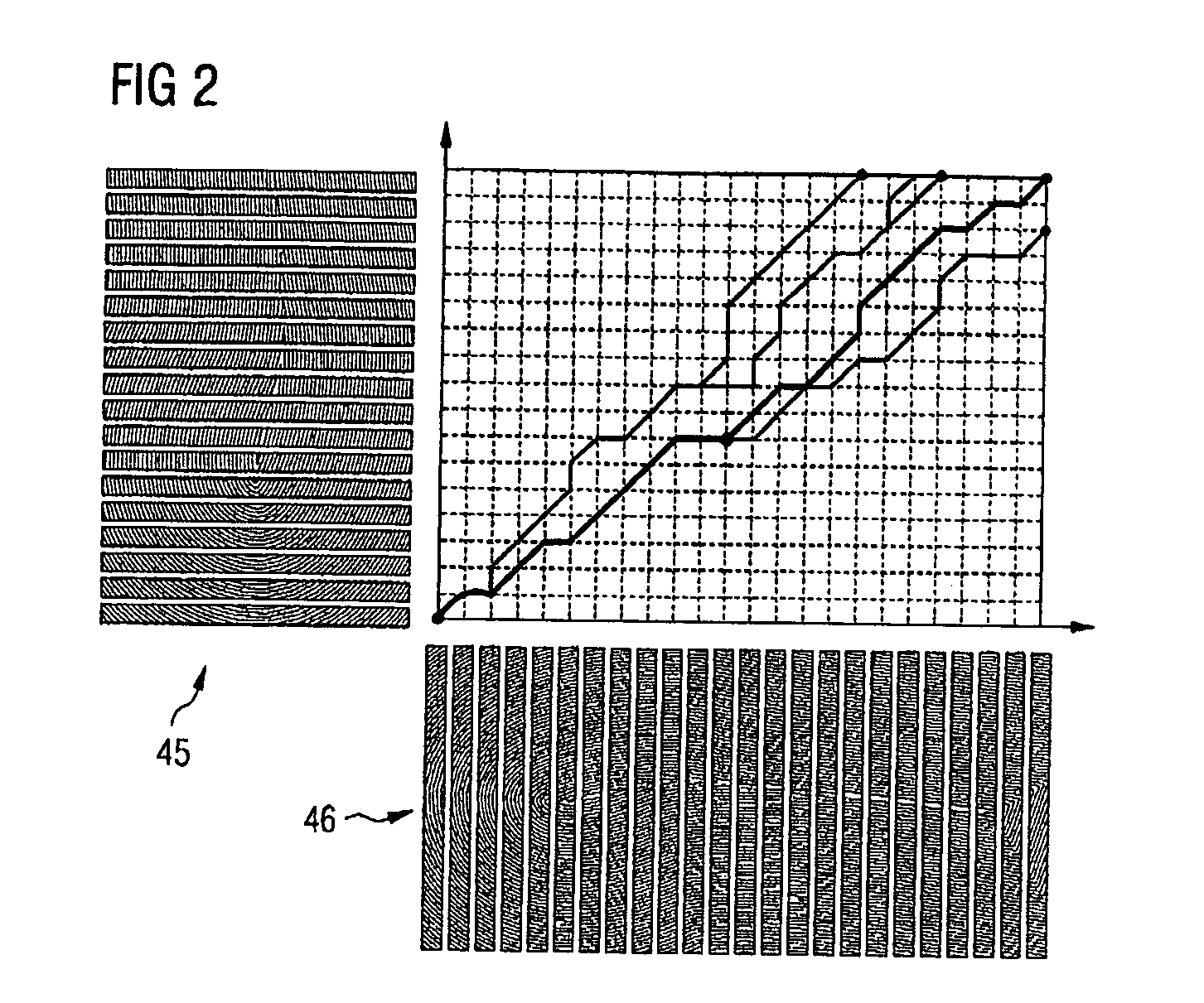

Method for comparison of a test fingerprint, which is in the form of an image strip sequence, with a stored reference fingerprint, and a suitable apparatus for carrying out the method

InactiveUS20050047633A1Improve confidence levelLess influenceMatching and classificationFingerprintPattern recognition

Method of comparing a test fingerprint with a stored reference fingerprint. The stored reference fingerprint and an image strip sequence of the test fingerprint are produced, wherein image strips of the image strip sequence represent different areas of the test fingerprint. Individual distance values between each image strip of the test fingerprint and at least one section of the reference fingerprint using a distance function are determined. An overall distance value from the individual distance values are determined, the overall distance value being a measure of similarity between the test fingerprint and the reference fingerprint.

Owner:INTEL CORP

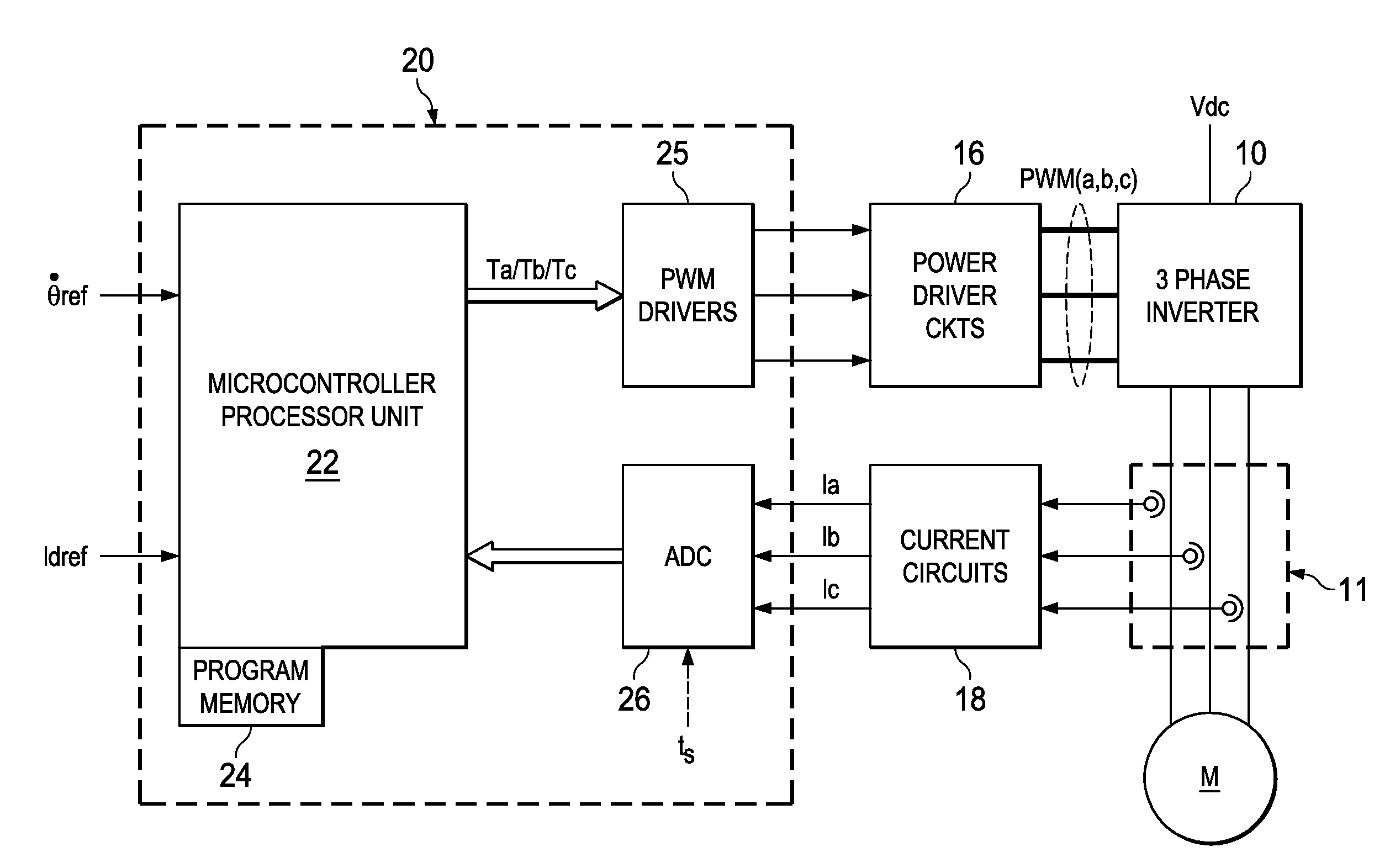

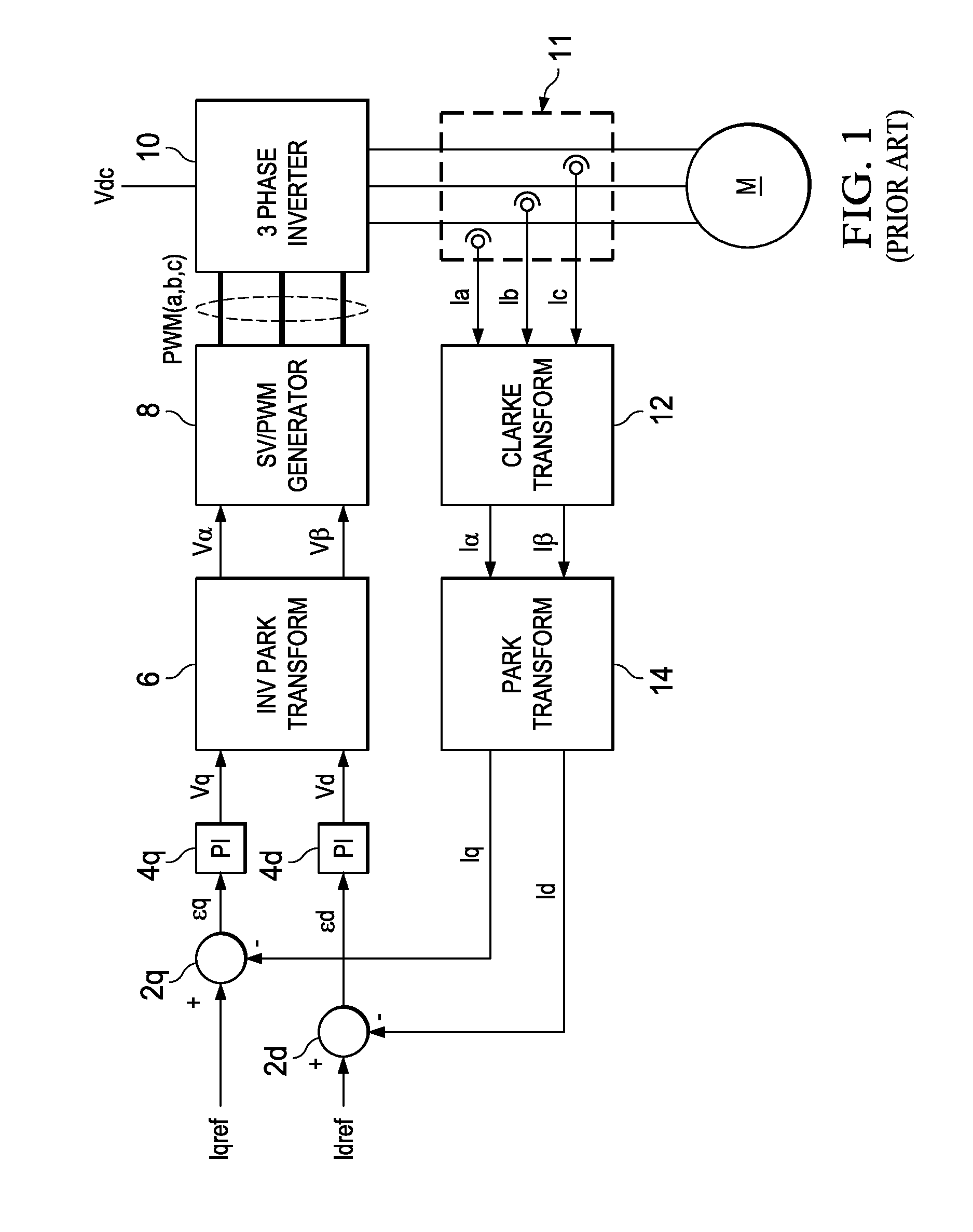

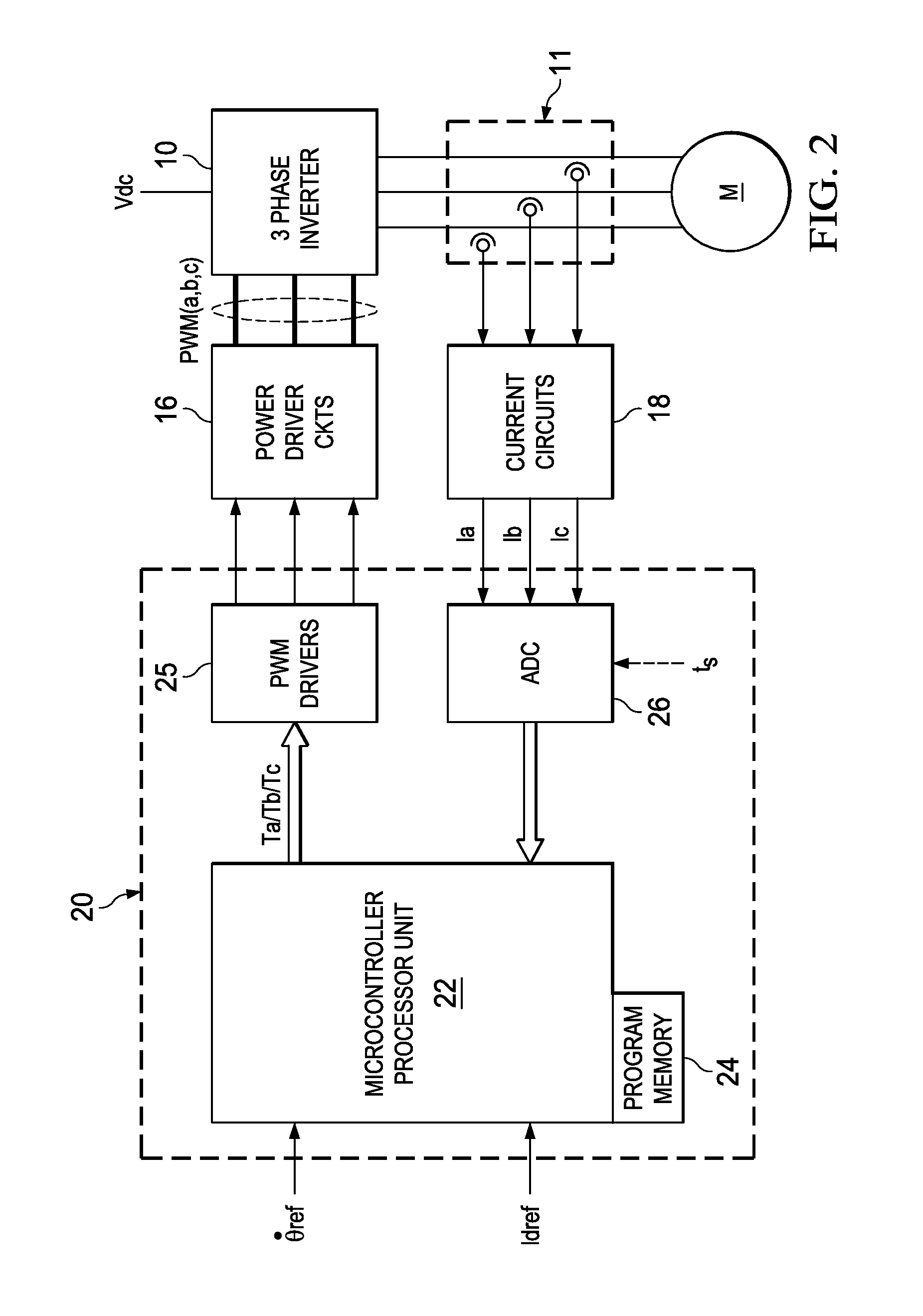

Low Speed and High Speed Controller Architecture for Electric Motors

InactiveUS20150084576A1Accurate low speed controlEfficient implementationElectronic commutation motor controlMotor/generator/converter stoppersPeriodic excitationController architecture

A motor controller architecture and method of operating the same. The motor controller includes a function for estimating the low speed operation of the motor, for example by evaluating the response to a periodic excitation signal injected into the control loop of the controller architecture. A periodic excitation signal in the form of a square wave allows for analysis of the response of the motor without requiring demodulation, which allows the frequency of the excitation signal to be above the audible range. Control logic for controlling the motor at transitional speeds between low speed control and high speed (back emf) control is provided in some embodiments.

Owner:TEXAS INSTR INC

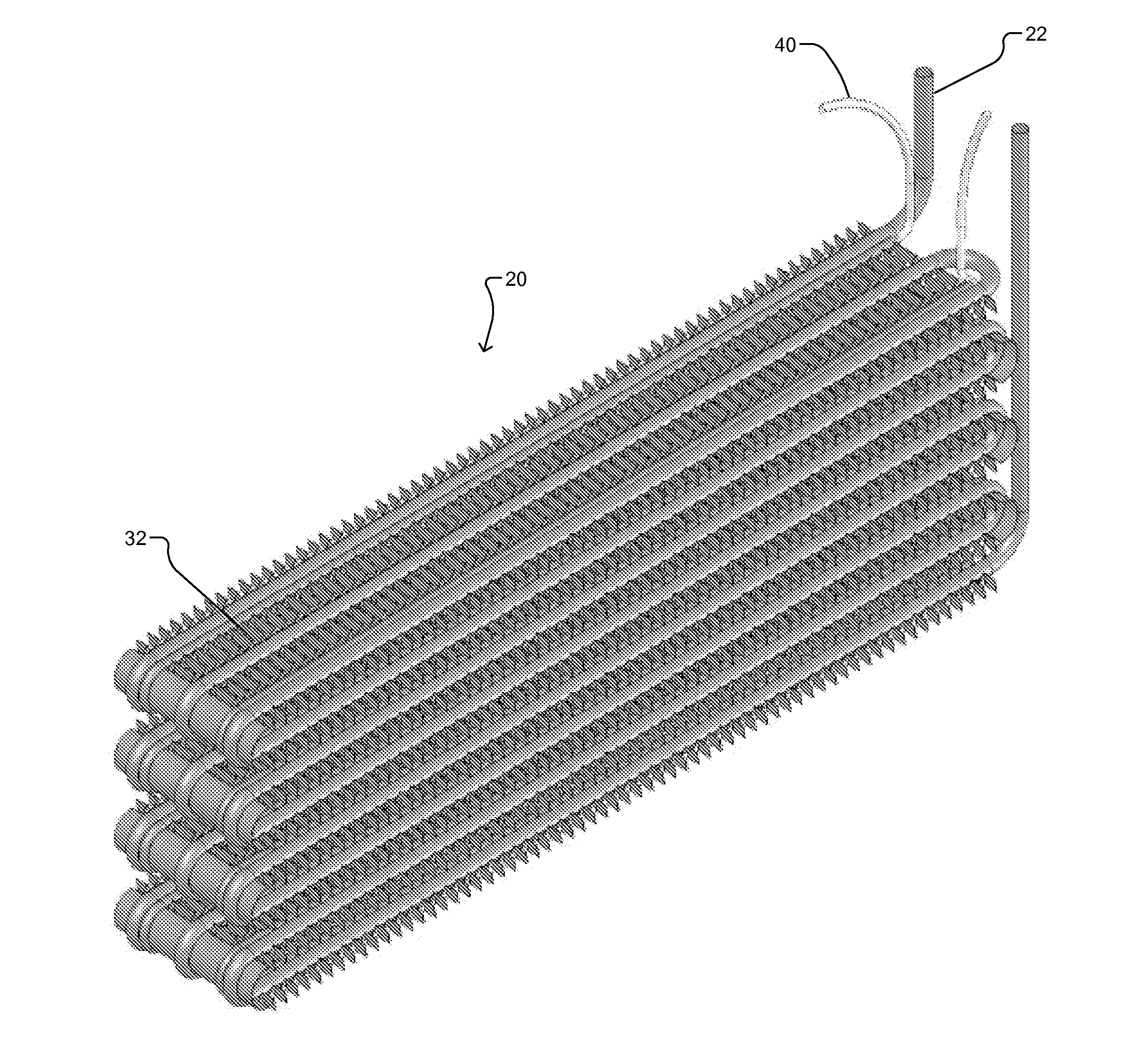

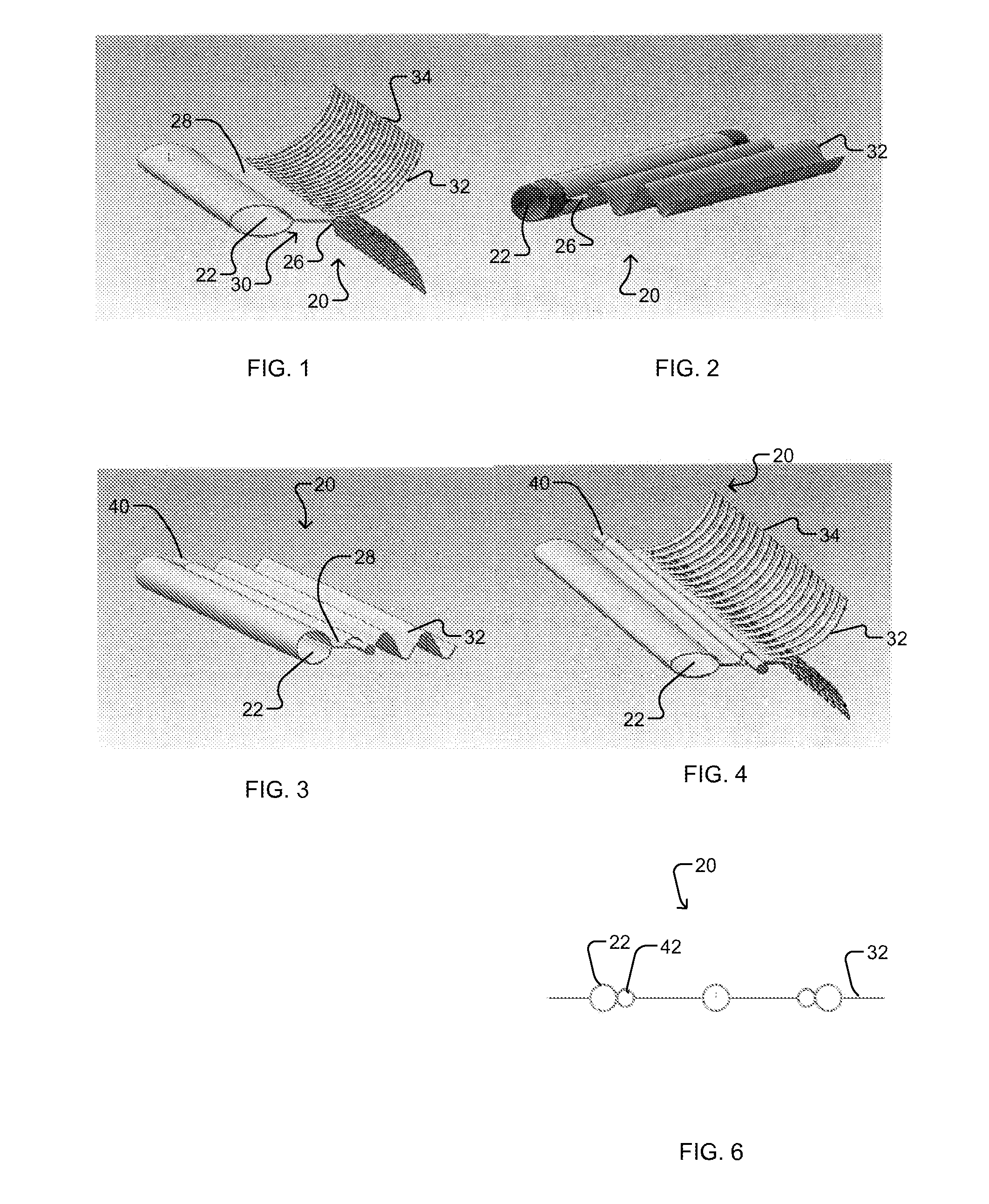

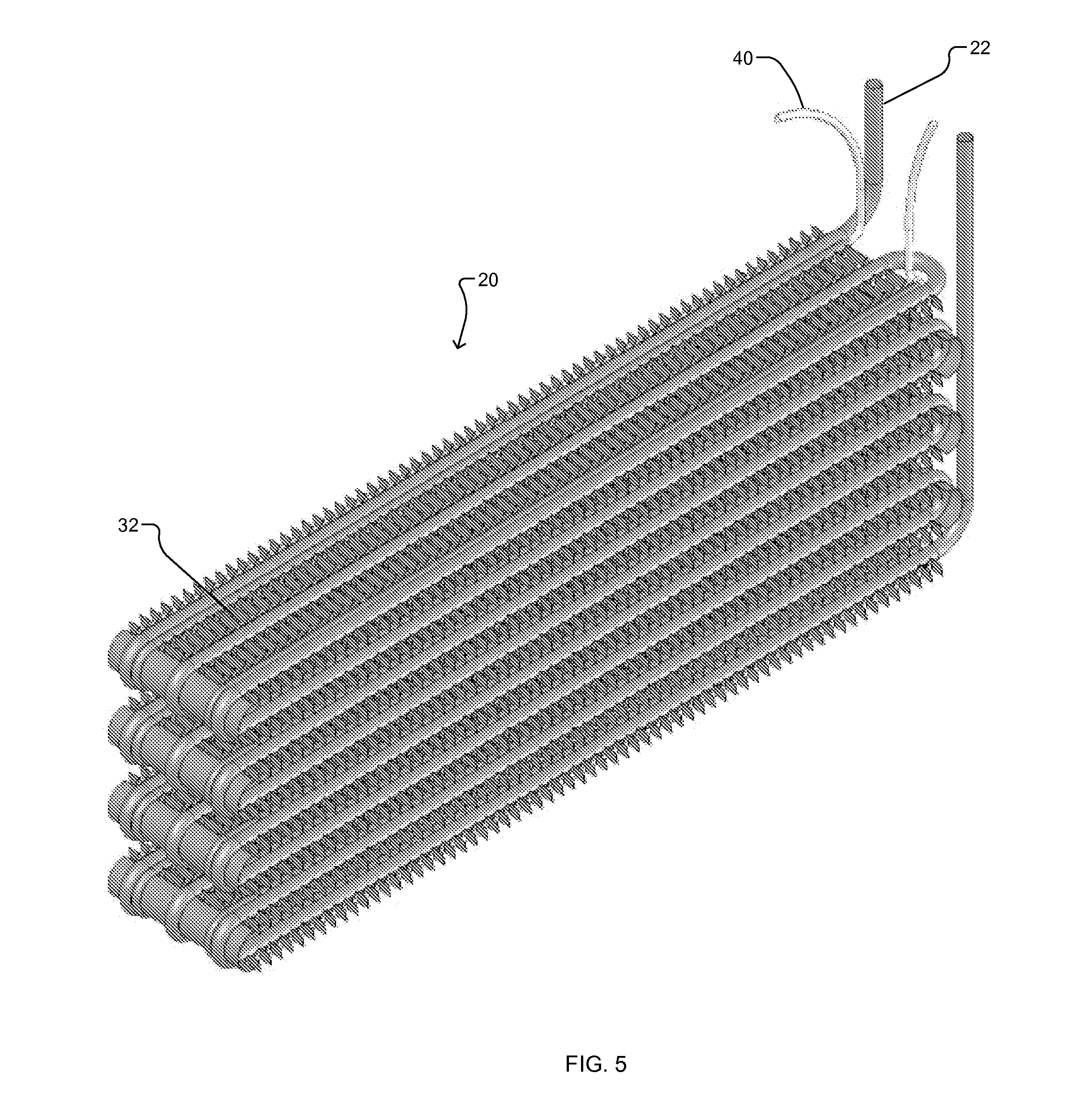

Integral evaporator and defrost heater system

InactiveUS20110036553A1More complexHigh performanceCorrosion preventionStationary conduit assembliesEvaporatorEngineering

A heat exchanger system having a fluid passage operable to fluidly communicate a first fluid and a heat transfer surface extending from the fluid passage for transferring heat between the first fluid and a second fluid. The system can further include a heating element operably coupled to and selectively applying thermal energy to at least one of the fluid passage and the heat transfer surface.

Owner:BRAZEWAY

A data processing apparatus and method for executing a stream of instructions out of order with respect to original program order

ActiveUS20170109172A1Reduce energy consumptionEffective instructionRegister arrangementsConcurrent instruction executionData processingImproved performance

A data processing apparatus and method are provided for executing a stream of instructions out-of-order with respect to original program order. At least some of the instructions in the stream identify one or more architectural registers from a set of architectural registers. The apparatus comprises a plurality of out-of-order components configured to manage execution of a first subset of instructions out-of-order, the plurality of out-of-order components being configured to remove false dependencies between instructions in the first subset. The plurality of out-of-order components include a first issue queue into which the instructions in the first subset are buffered prior to execution. A second issue queue is used to buffer a second subset of instructions prior to execution, the second subset of instructions being constrained to execute in order. Issue control circuitry is configured to reference both issue queues in order to determine an order of execution of instructions, and is configured to constrain the order of execution of the first subset of instructions by true dependencies between the instructions in both the first and second issue queues, and to constrain the order of execution of the second subset of instructions by both the true dependencies and the false dependencies between the instructions in both the first and second issue queues. This approach provides improved performance and / or reduced energy consumption.

Owner:THE RGT OF THE UNIV OF MICHIGAN

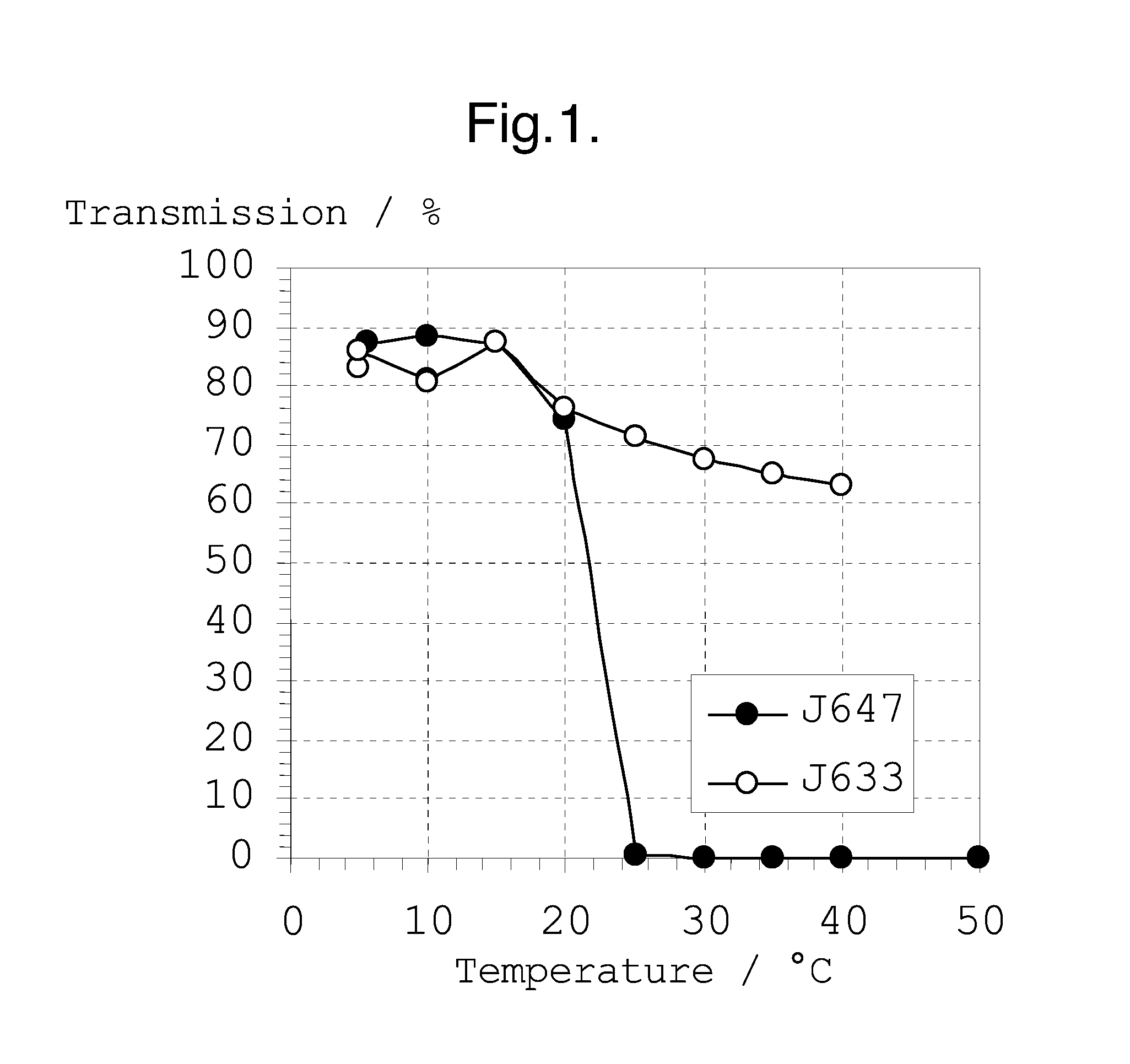

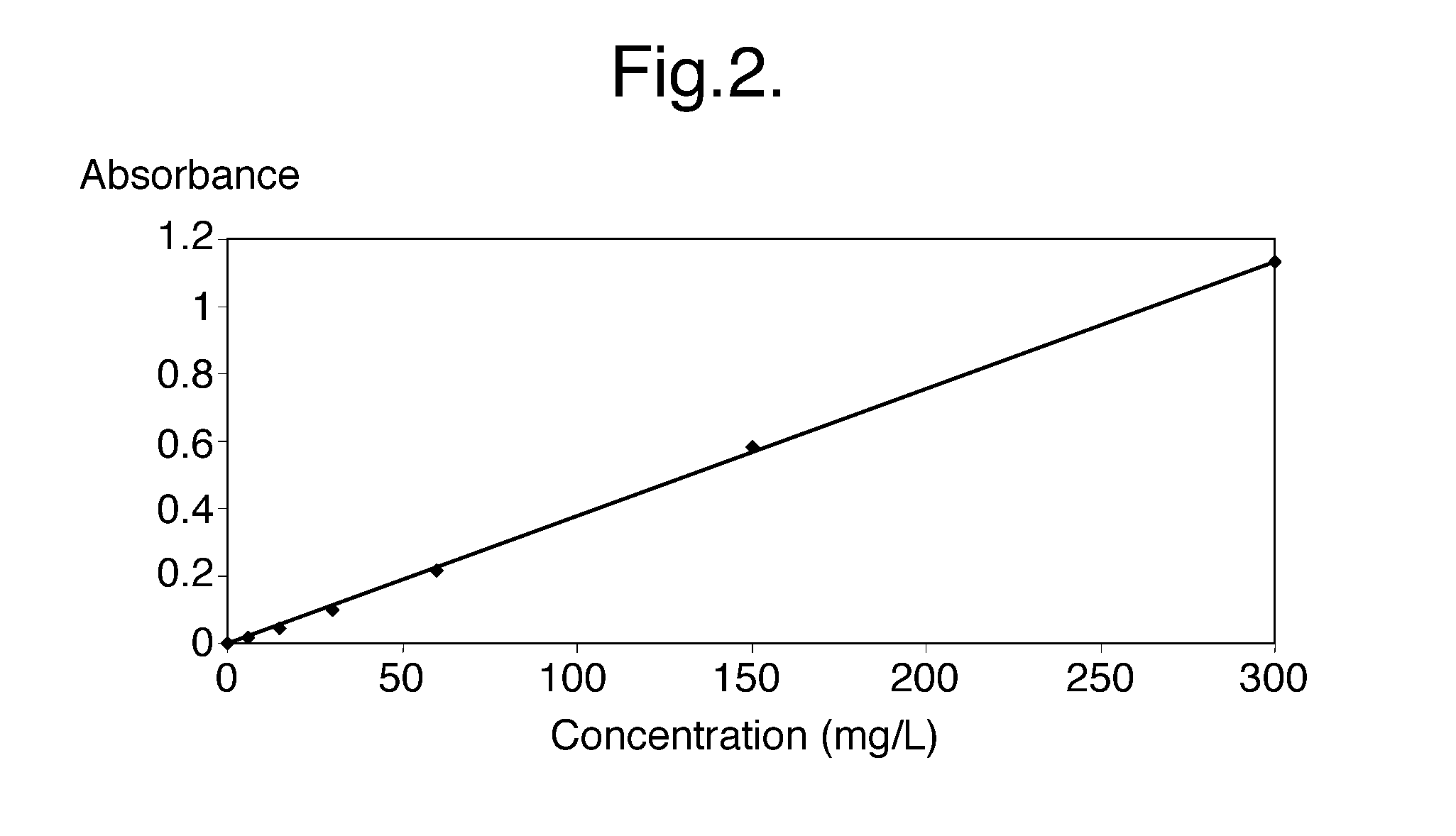

Method for producing a foaming agent

A method for producing a foaming agent is provided, the method comprising cultivating a host cell in a fermentation medium wherein the host cell extra-cellularly secretes a foaming agent and wherein the fermentation medium contains an antifoam which has a cloud point; and then removing the antifoam5 while the temperature of the fermentation medium is above the cloud point.

Owner:CONOPCO INC D B A UNILEVER

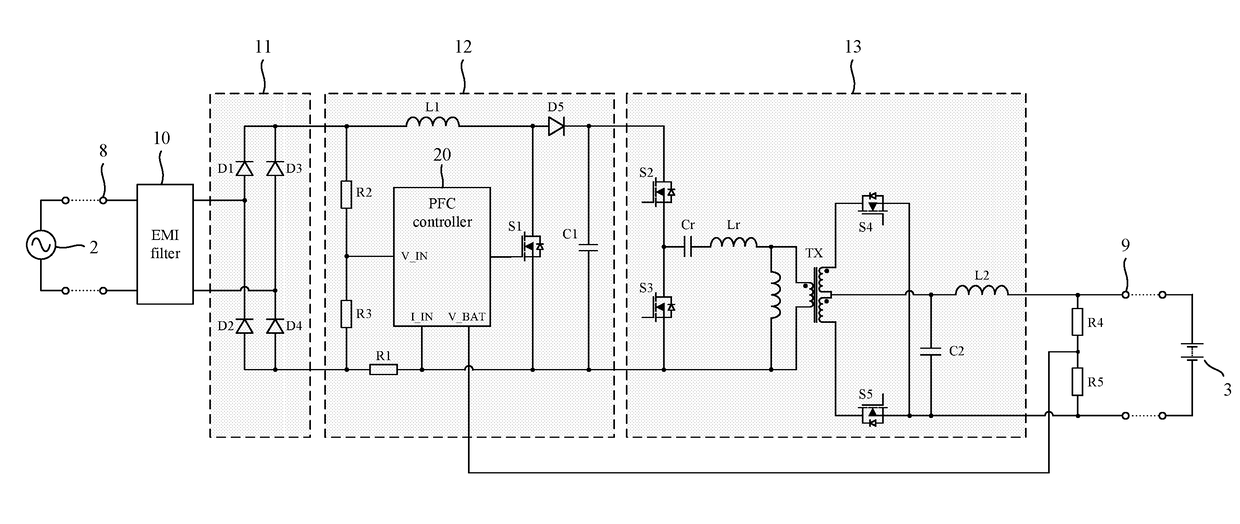

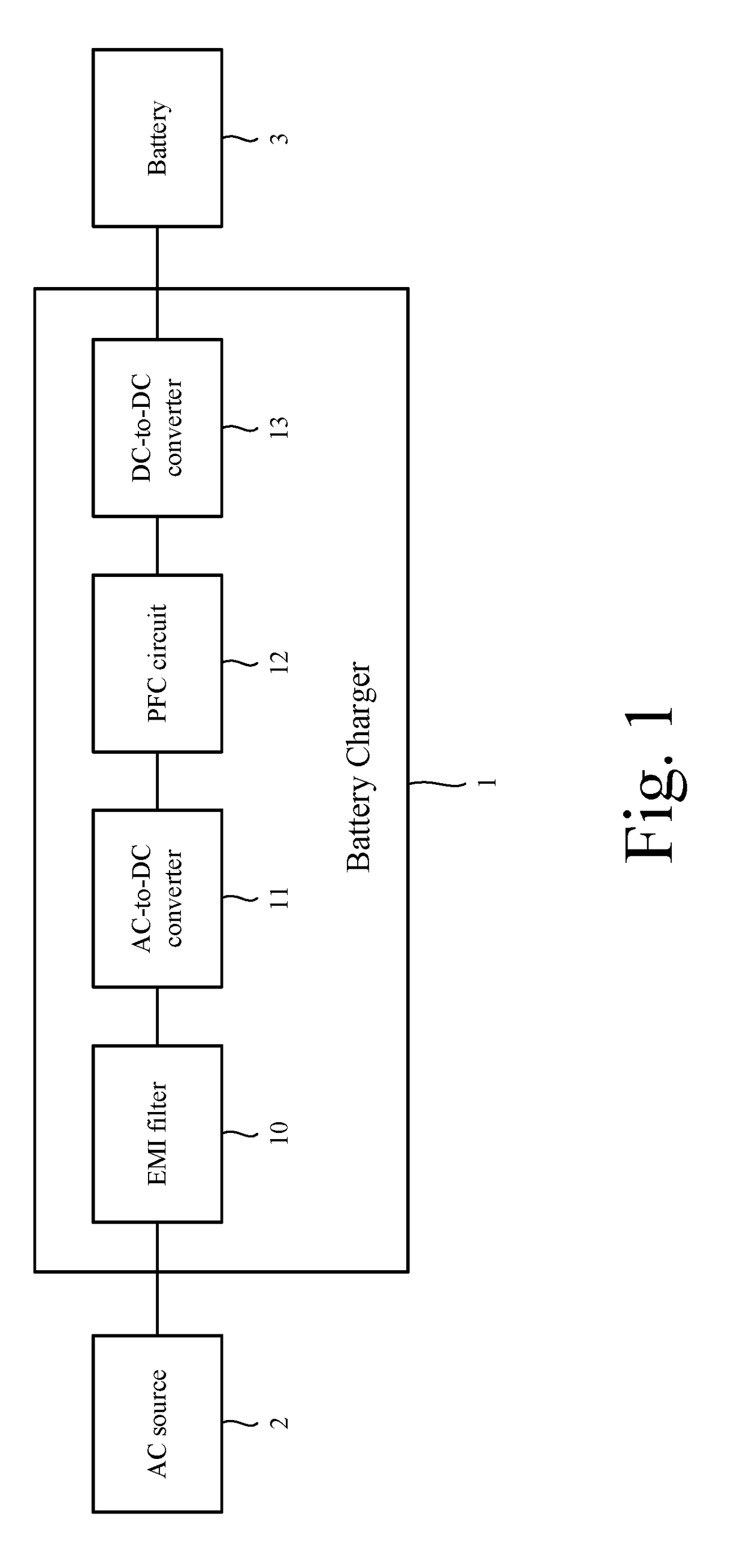

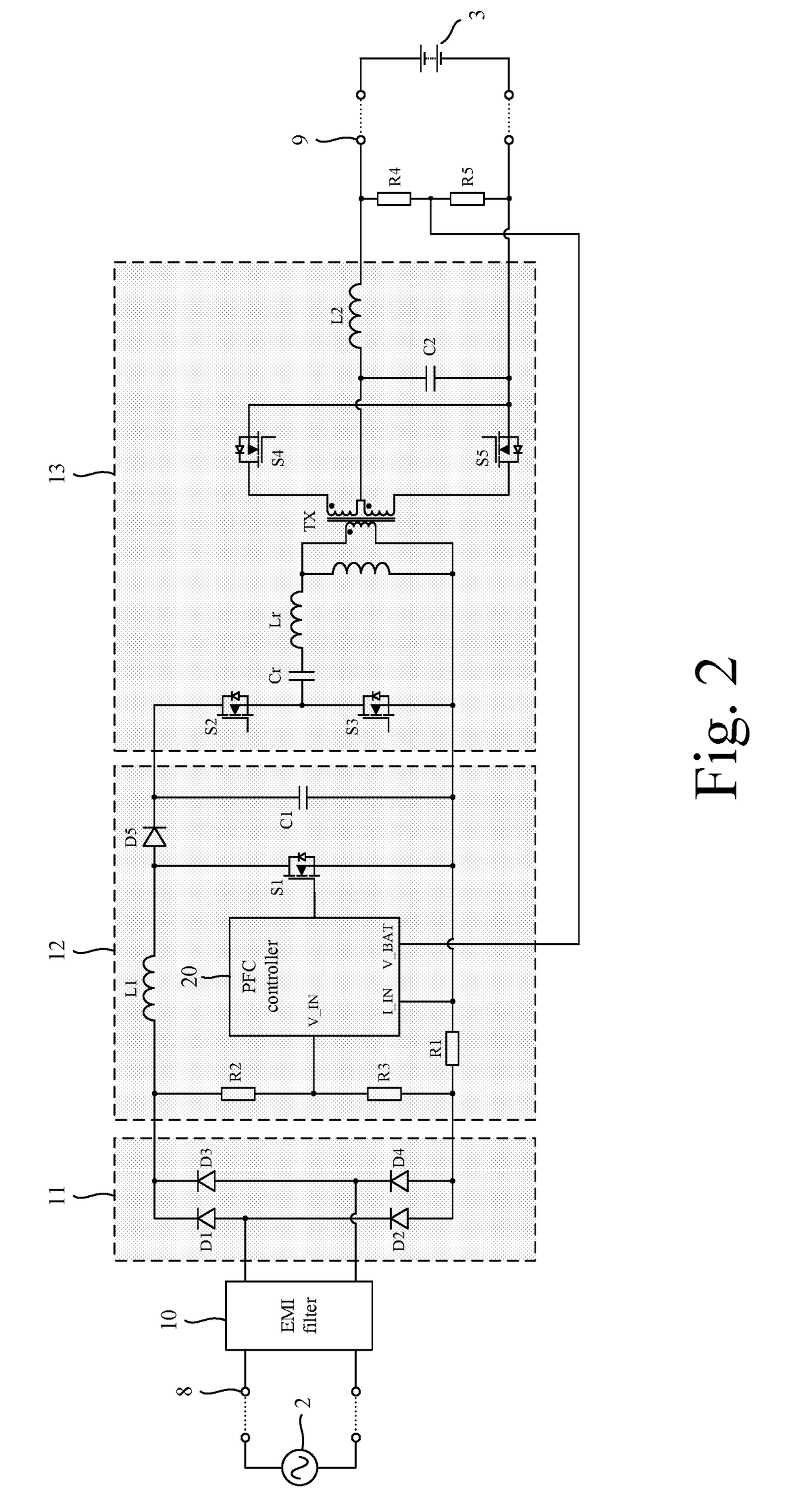

Battery charger

InactiveUS20180219474A1Low costSmall sizeBatteries circuit arrangementsEfficient power electronics conversionBattery chargeCell voltage

A battery charger comprising input terminals for connection to an AC source, output terminals for connection to a battery to be charged, and a power factor correction (PFC) circuit connected between the input terminals and the output terminals. The PFC circuit comprises a current control loop for regulating an input current drawn from the AC source. The voltage at the output of the PFC circuit is regulated by the voltage of the battery which is reflected back to the PFC circuit. As a result, the battery charger acts as a current source that outputs an output current at the output terminals, and the waveform of the output current is periodic with a frequency twice that of the input current and a ripple of at least 50%.

Owner:DYSON TECH LTD

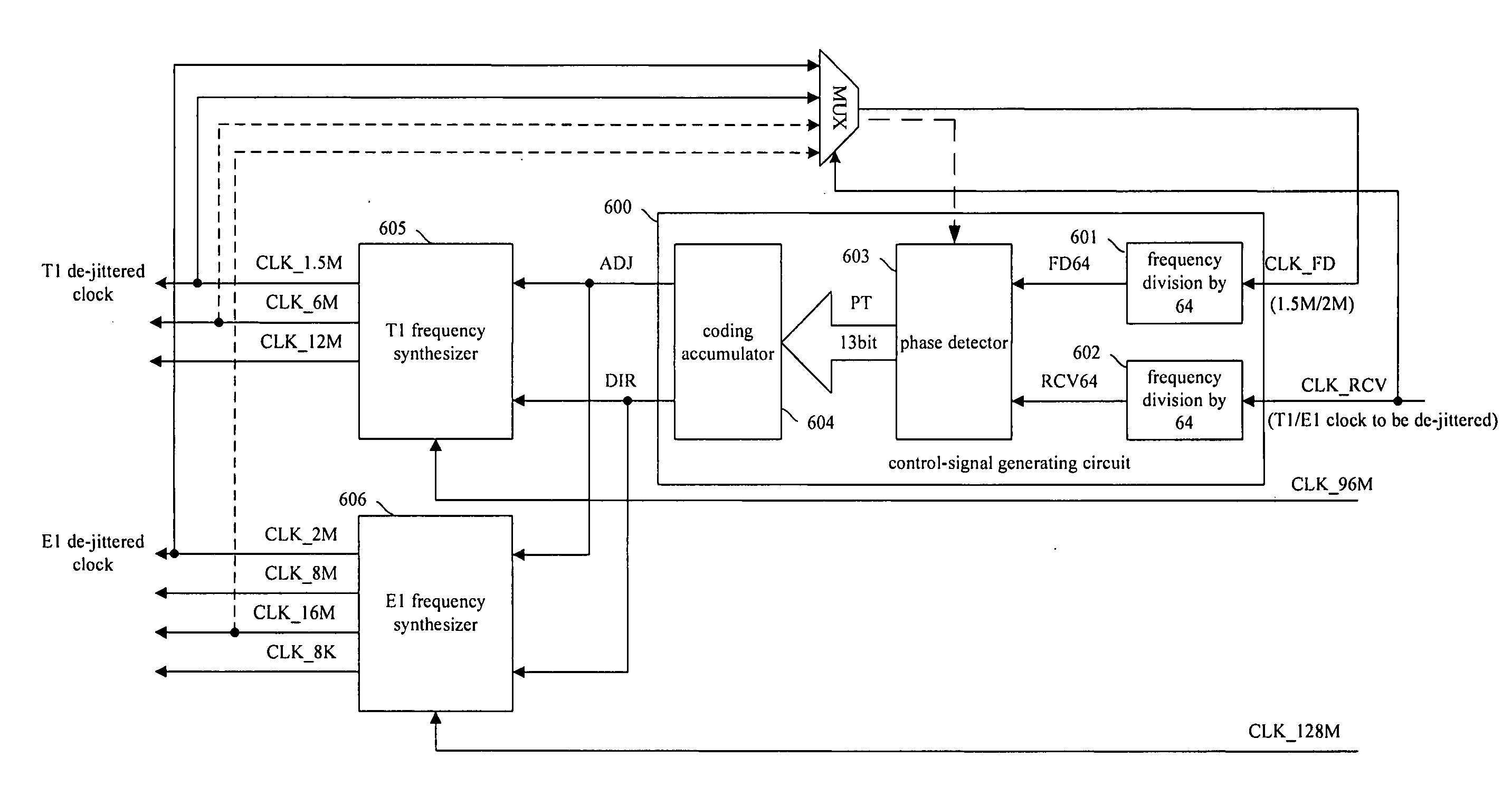

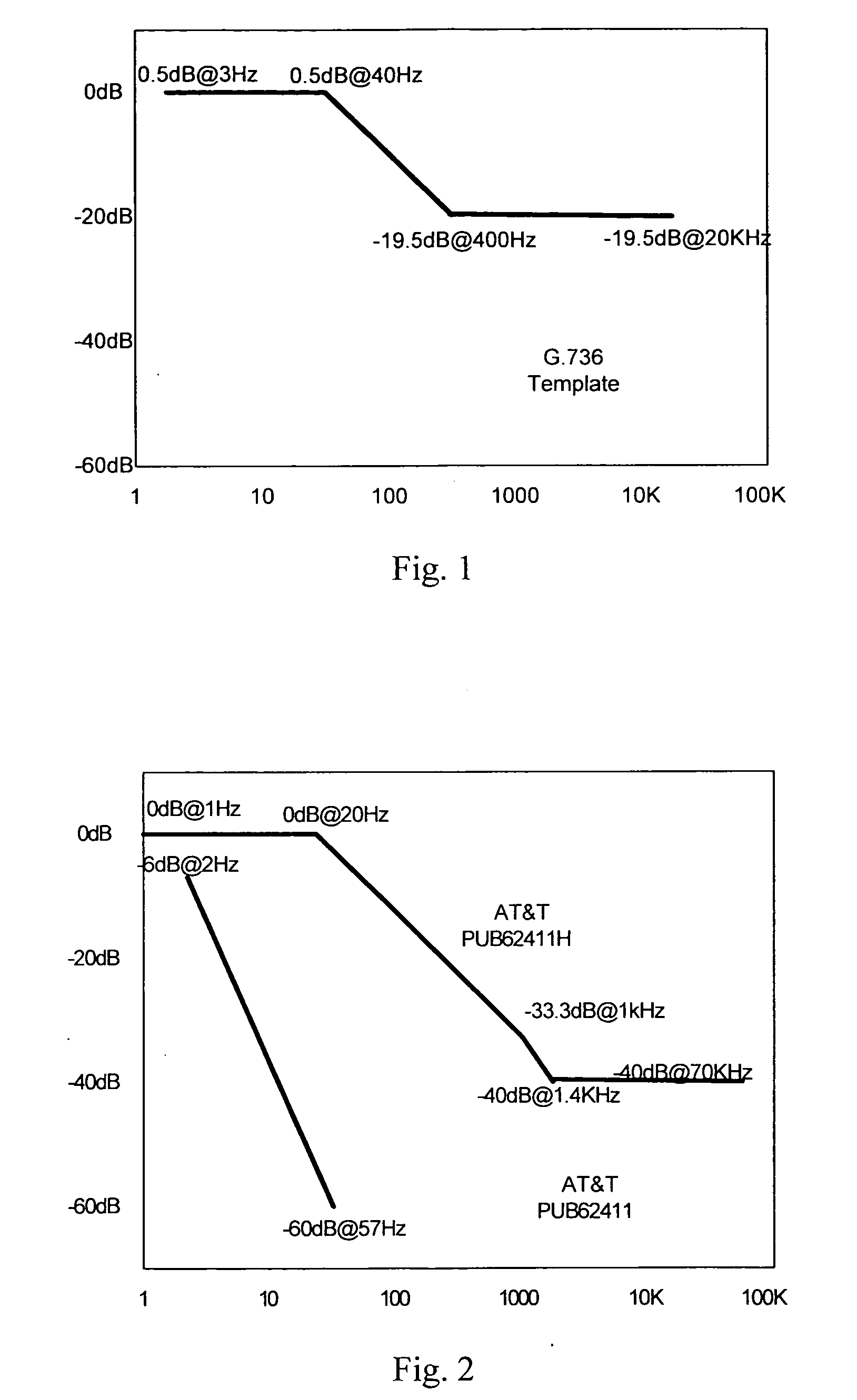

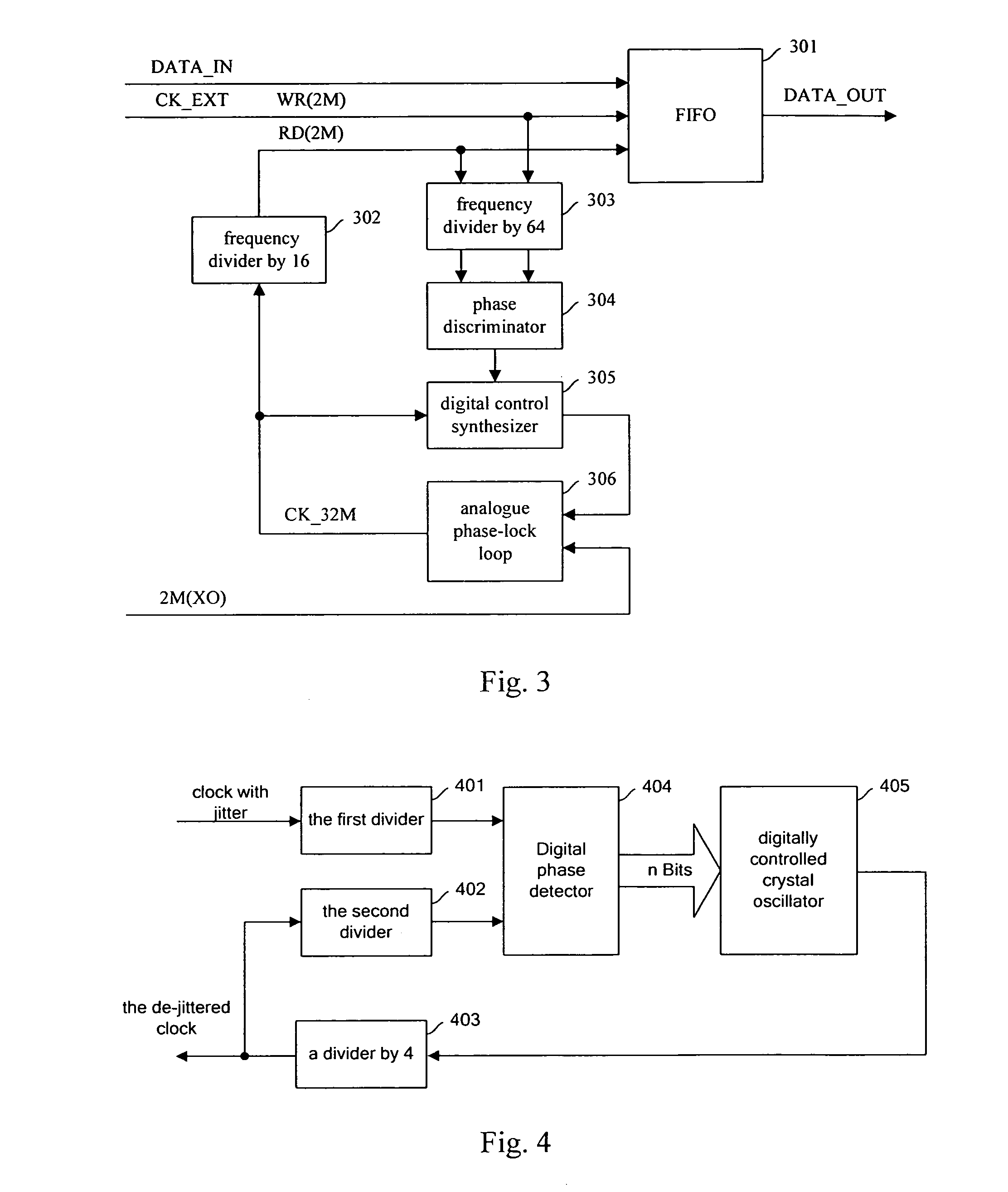

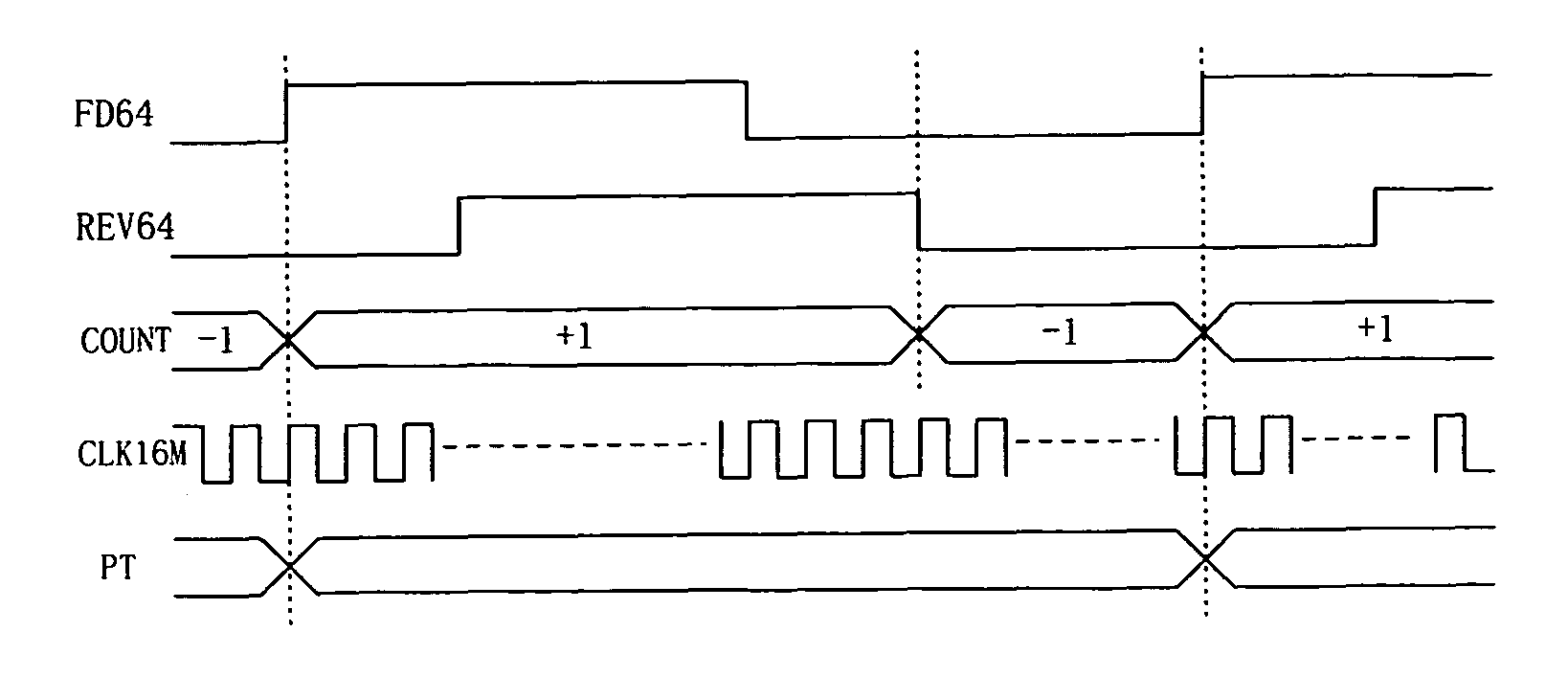

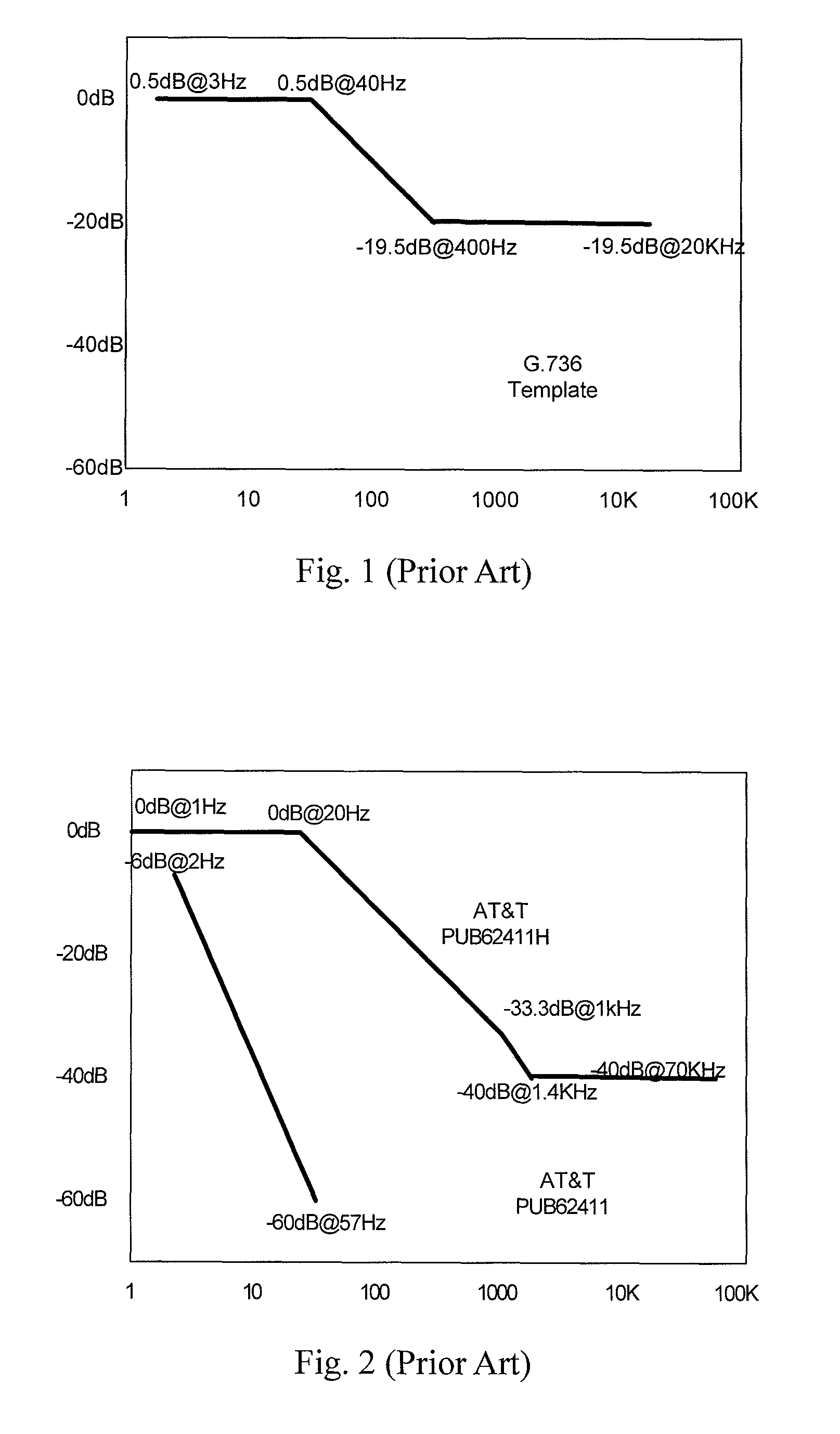

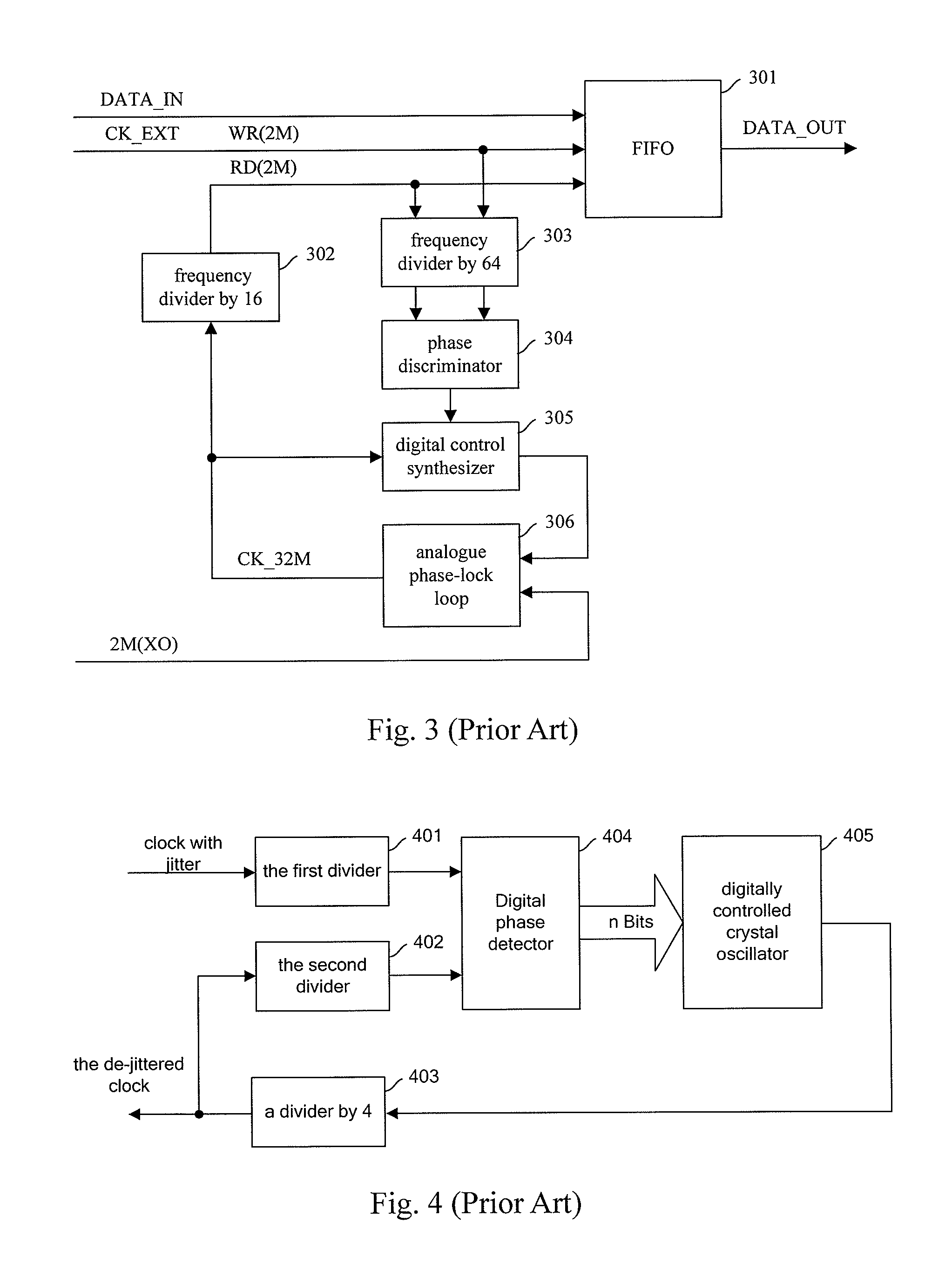

Method and apparatus for removing the otter on clock signal

ActiveUS20080143397A1Easy to implementLow costPulse automatic controlModulated-carrier systemsControl signalEngineering

The present invention discloses a de-jittering method for a clock signal, which is implemented by adopting a controllable frequency divider and includes: taking the clock signal to be de-jittered as a reference signal, and comparing a feedback clock signal outputted by the controllable frequency divider with the reference signal; generating the control signal that is then transmitted to the controllable frequency divider; the controllable frequency divider performs frequency division upon the input high-frequency signal to generate a stable clock, and the stable clock is outputted as the feedback clock signal which has been de-jittered. The present invention also discloses a de-jittering apparatus for implementing the above-mentioned method, which includes: a circuit for generating a control signal and a controllable frequency divider. By applying the present invention, the de-jittering circuit for clock signal can be simple. What's more, transition between T1 clock frequency and E1 clock frequency can also be implemented to meet practical requirements better.

Owner:HUAWEI TECH CO LTD

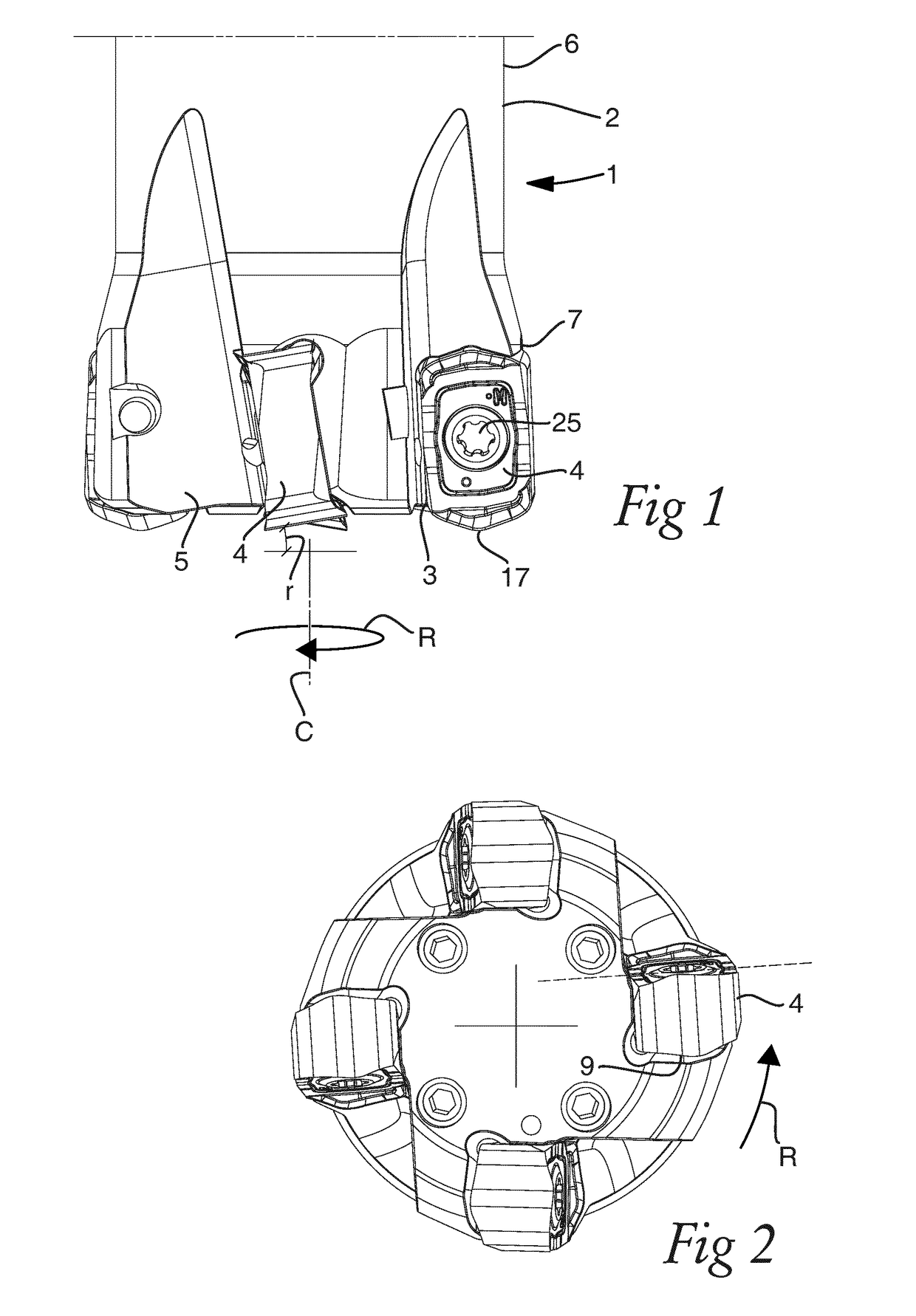

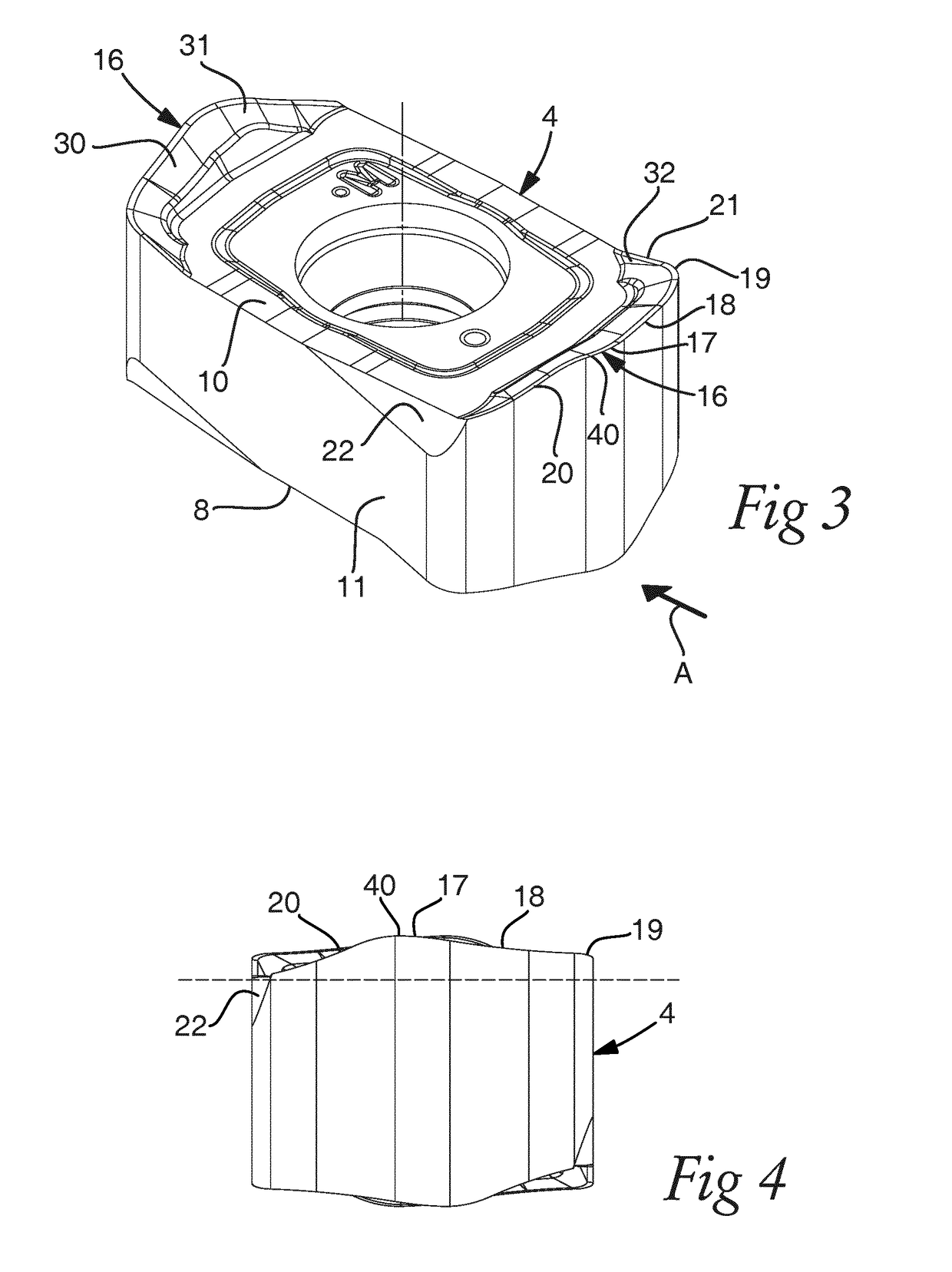

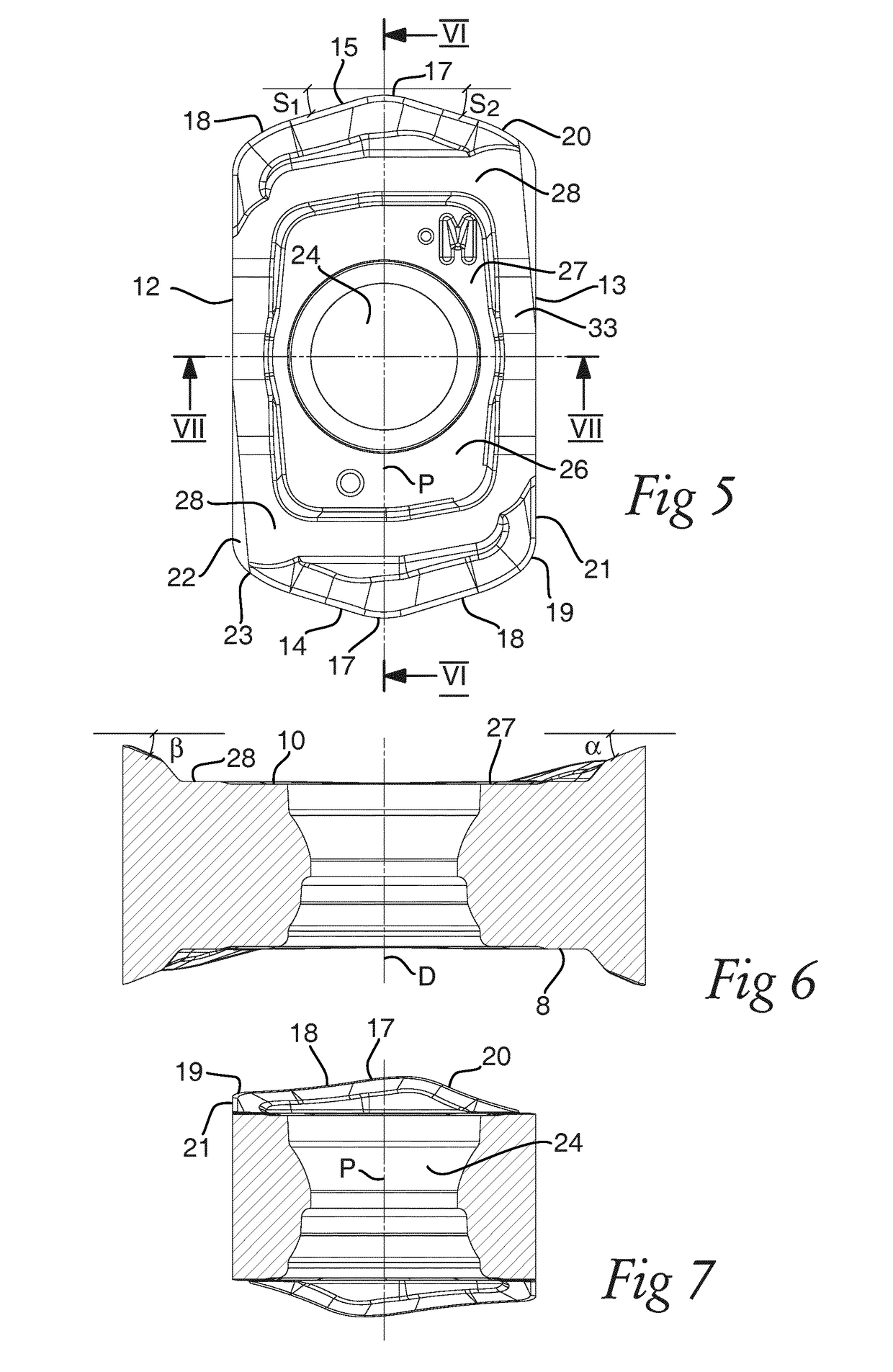

Indexable cutting insert for an end mill tool and an end mill tool provided with such an insert

ActiveUS20190030629A1Reduce loadReduce the risk of fracturesMilling cuttersMilling cutting insertsMilling cutterMechanical engineering

An indexable cutting insert has a first corner edge forming a front tip of a cutting edge portion configured to project furthest in the direction of an axis of rotation of an end mill tool receiving the insert. A major cutting edge is descending to come closer to the lower surface of the insert along its extension away from the first corner edge. The minor cutting edge extends from the first corner edge while descending from a point of the cutting edge portion most distant to the lower surface all the way to an inner corner of the insert and has a length of 80%-95% of the length of the major cutting edge including a second corner edge in a side elevation view of the cutting insert.

Owner:PRAMET TOOLS

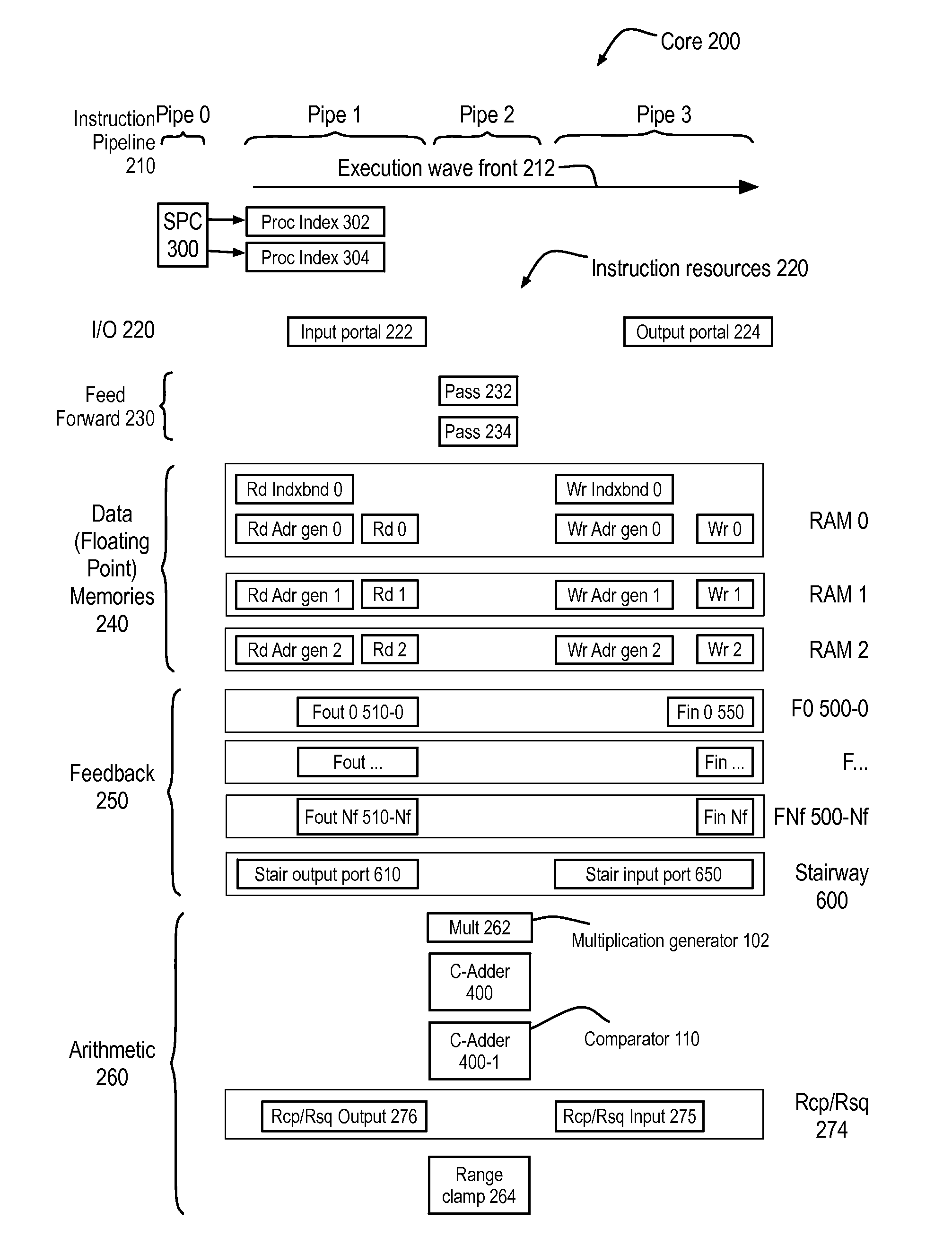

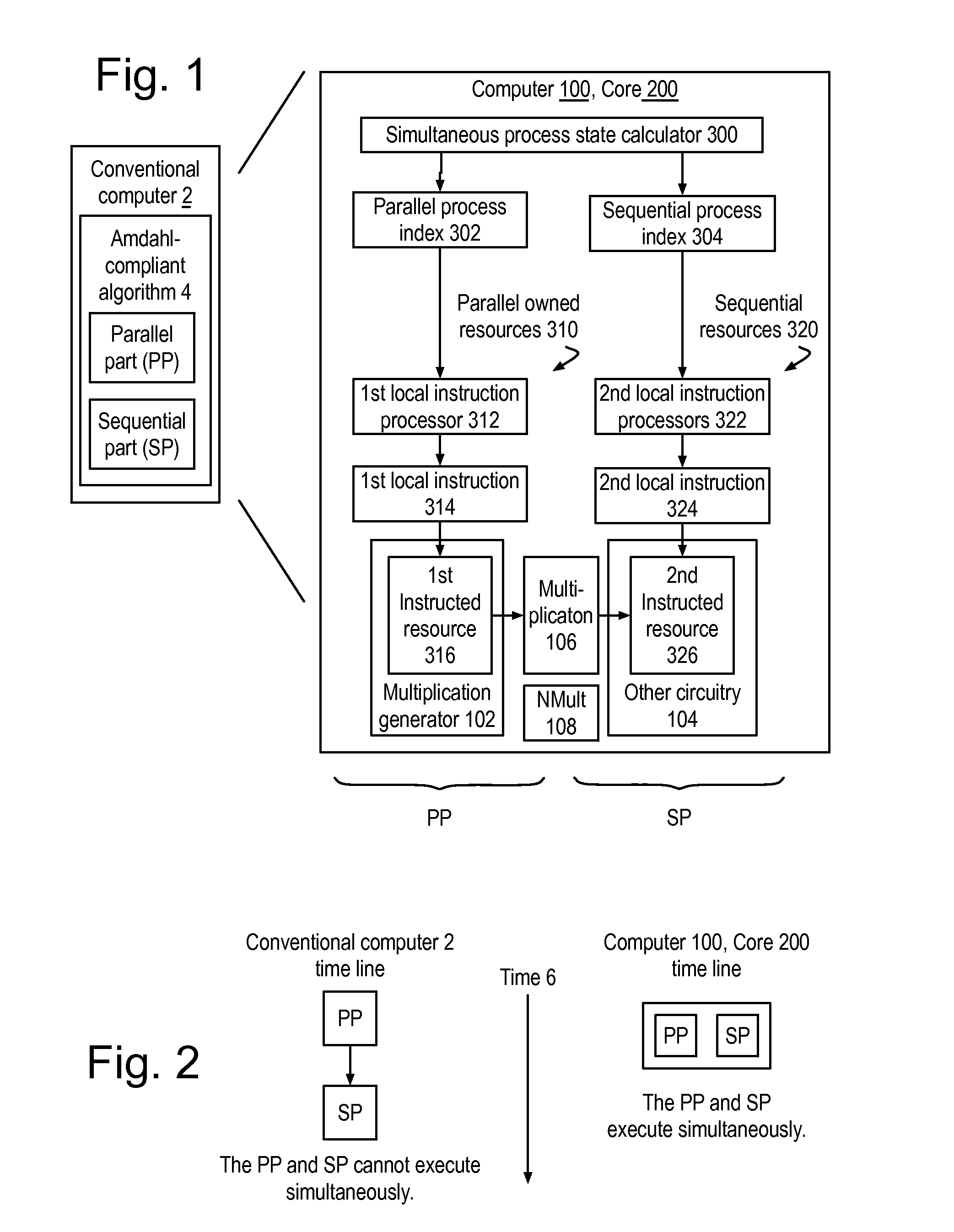

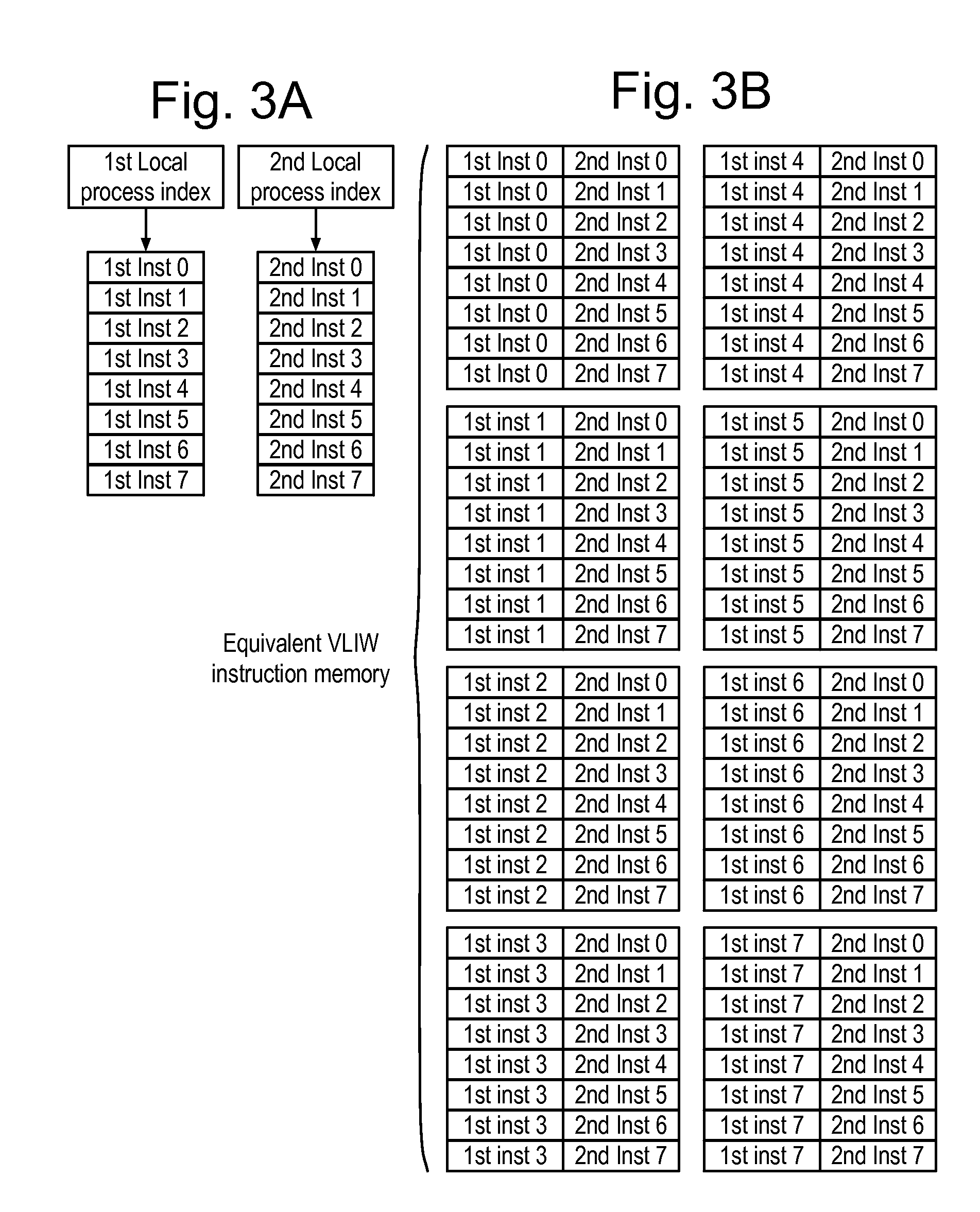

Computer for amdahl-compliant algorithms like matrix inversion

ActiveUS20120203814A1More complexMaximum performanceComputation using non-contact making devicesDigital computer detailsComputational scienceFloating point

A family of computers is disclosed and claimed that supports simultaneous processes from the single core up to multi-chip Program Execution Systems (PES). The instruction processing of the instructed resources is local, dispensing with the need for large VLIW memories. The cores through the PES have maximum performance for Amdahl-compliant algorithms like matrix inversion, because the multiplications do not stall and the other circuitry keeps up. Cores with log based multiplication generators improve this performance by a factor of two for sine and cosine calculations in single precision floating point and have even greater performance for loge and ex calculations. Apparatus specifying, simulating, and / or layouts of the computer (components) are disclosed. Apparatus the computer and / or its components are disclosed.

Owner:QSIGMA

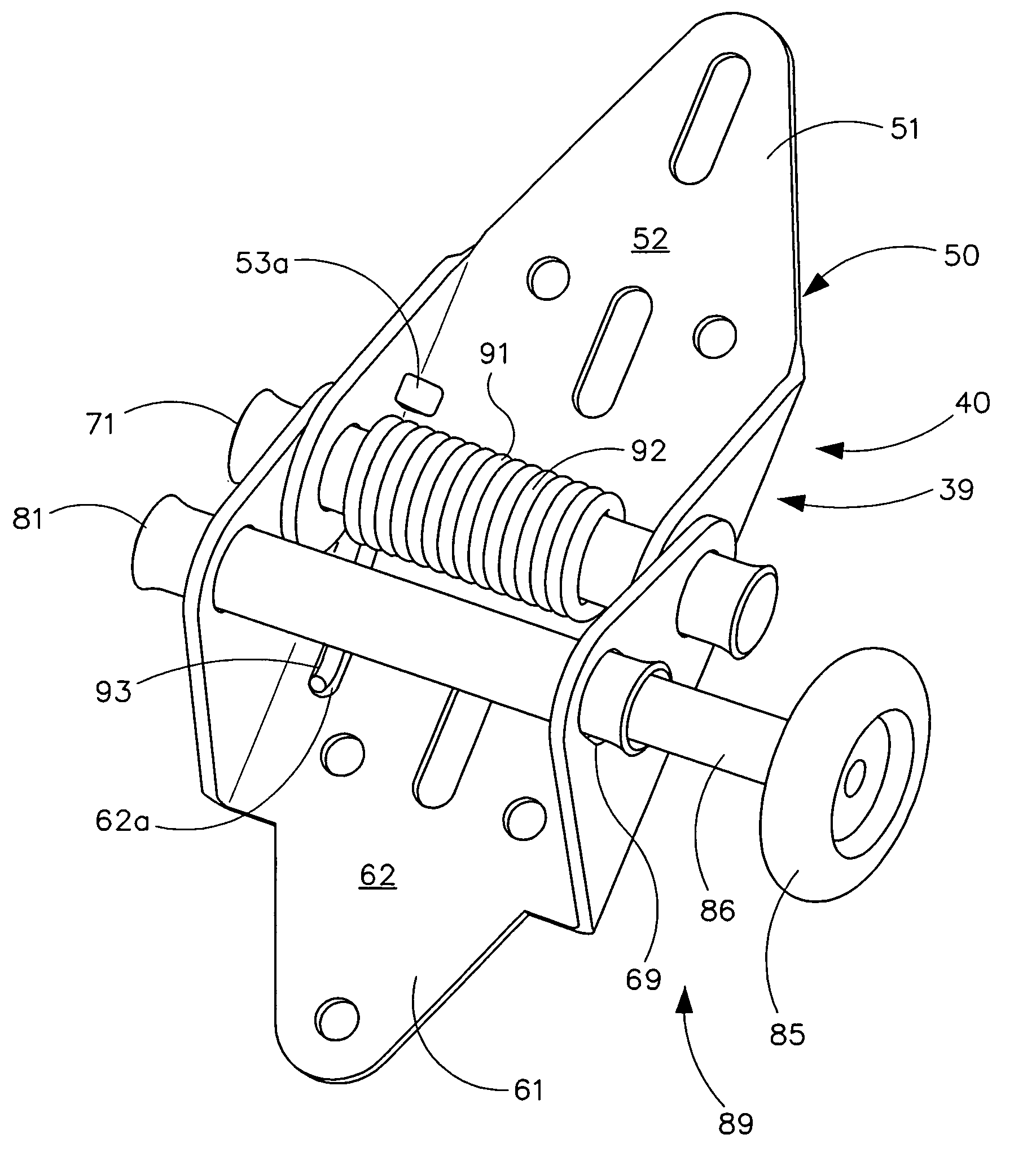

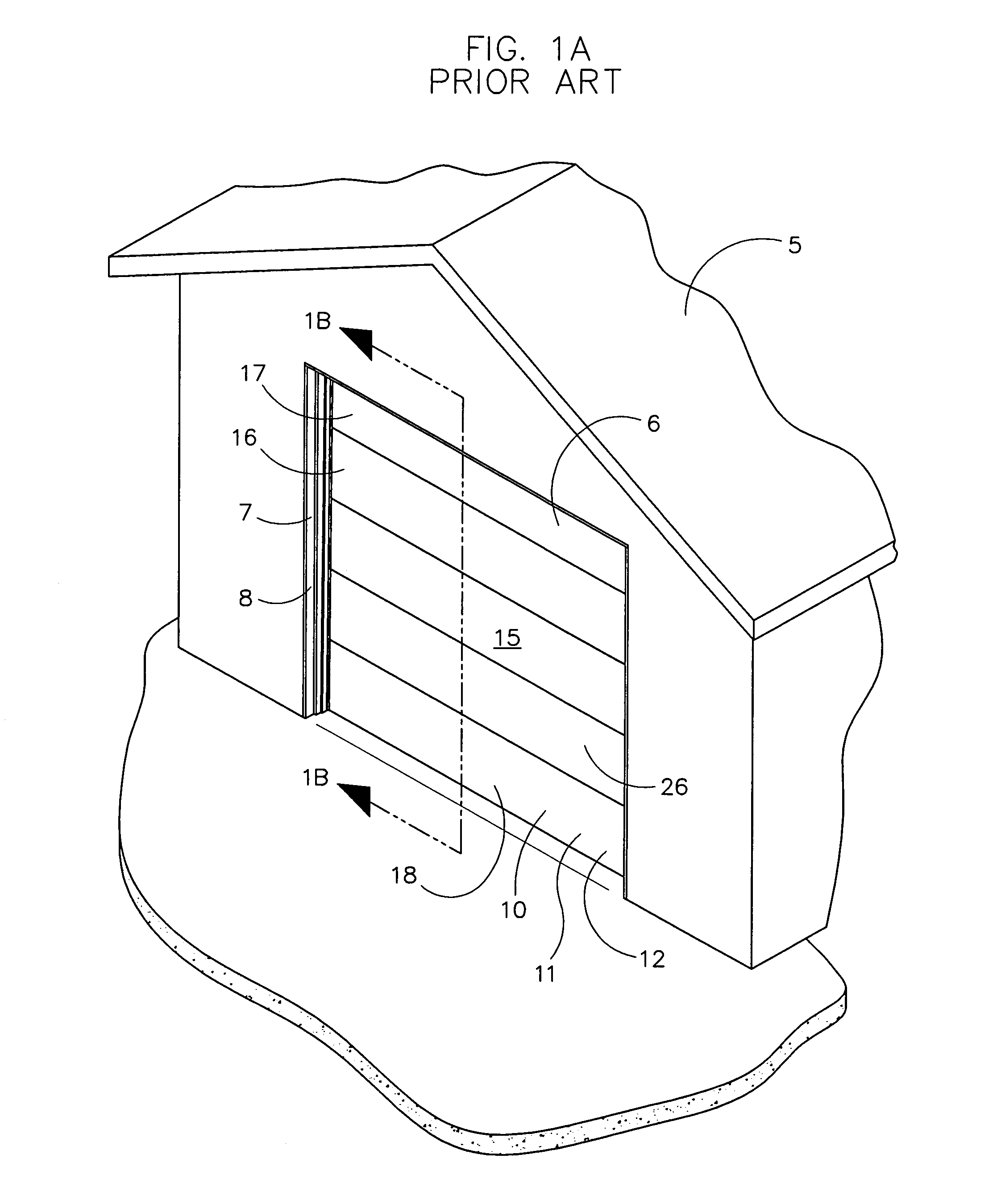

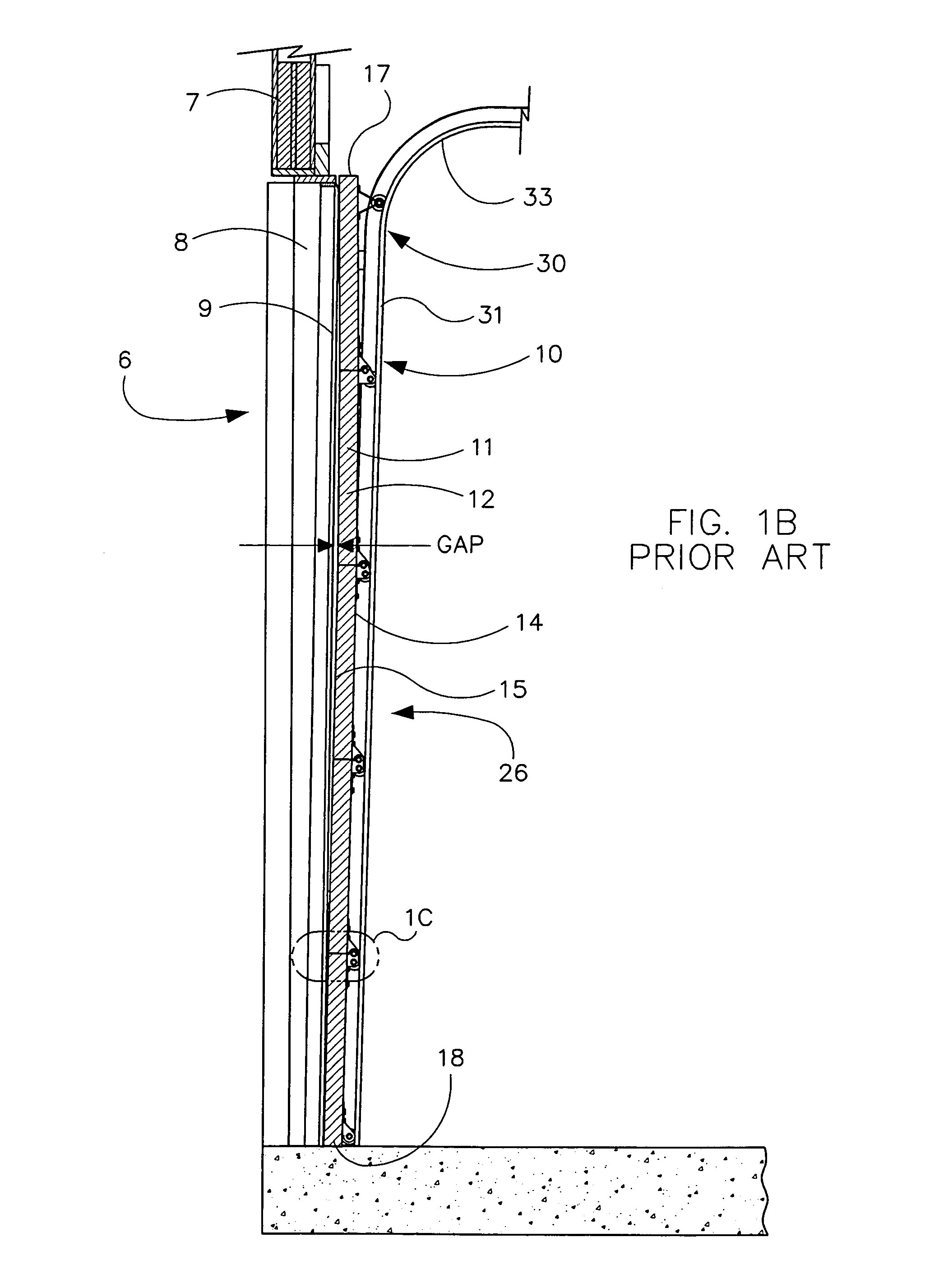

Overhead door with spring-loaded roller hinges

An overhead door with spring-loaded roller hinges that push the door against its frame or weather stripping to provide an effective weather and thermal seal when the door is closed. The spring-loaded roller hinges are readily retrofit to overhead doors with conventional roller hinges. Each hinge spaces and pivotally secures a roller hub from the base of the hinge. The roller hub is pivotally secured to an inside flange and movably held by an elongated slot in an outer flange. The roller hub supportingly receives the axle of a wheel that rollingly engages a track fixed to the vertical sides of the door frame. Each roller hinge has a spring that biases its roller hub and wheel rearwardly against the fixed track, which pushes the door panels forward and into sealing engagement with the door frame or its weather stripping.

Owner:MORTIER LESTER L

Method and apparatus for de-jittering a clock signal

ActiveUS7724812B2Quality improvementMore complexPulse automatic controlModulated-carrier systemsControl signalEngineering

Owner:HUAWEI TECH CO LTD