Patents

Literature

56results about How to "More costly" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

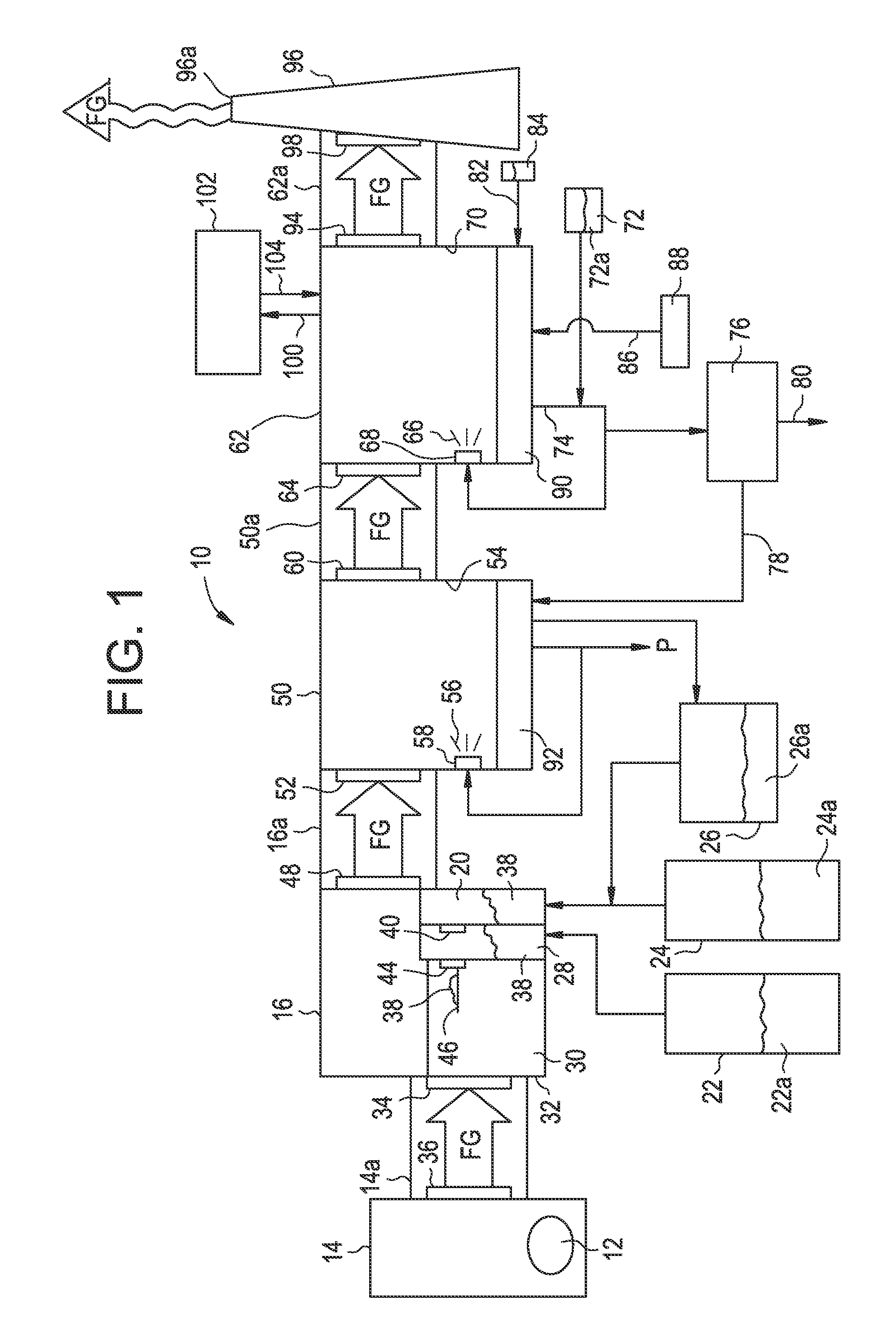

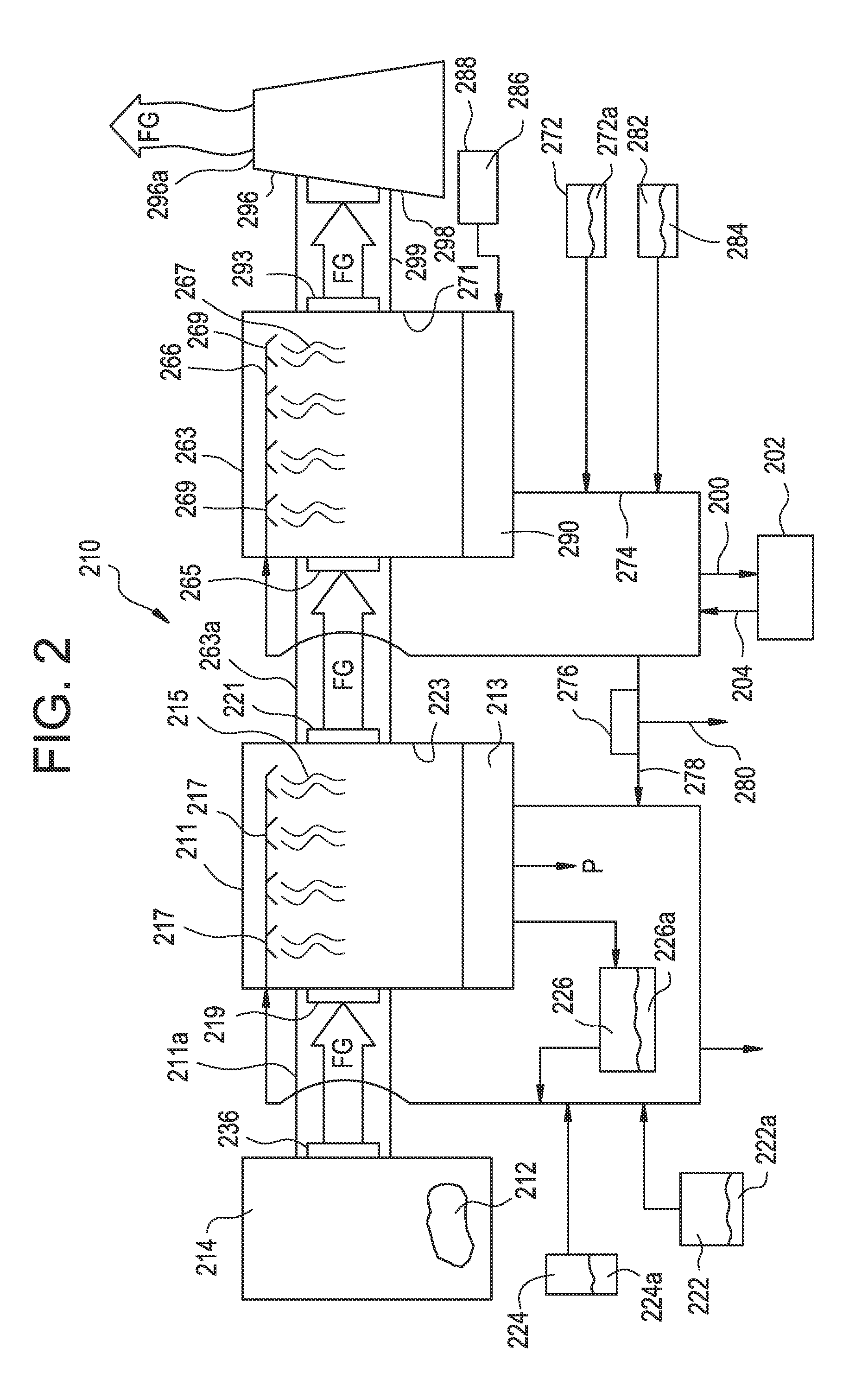

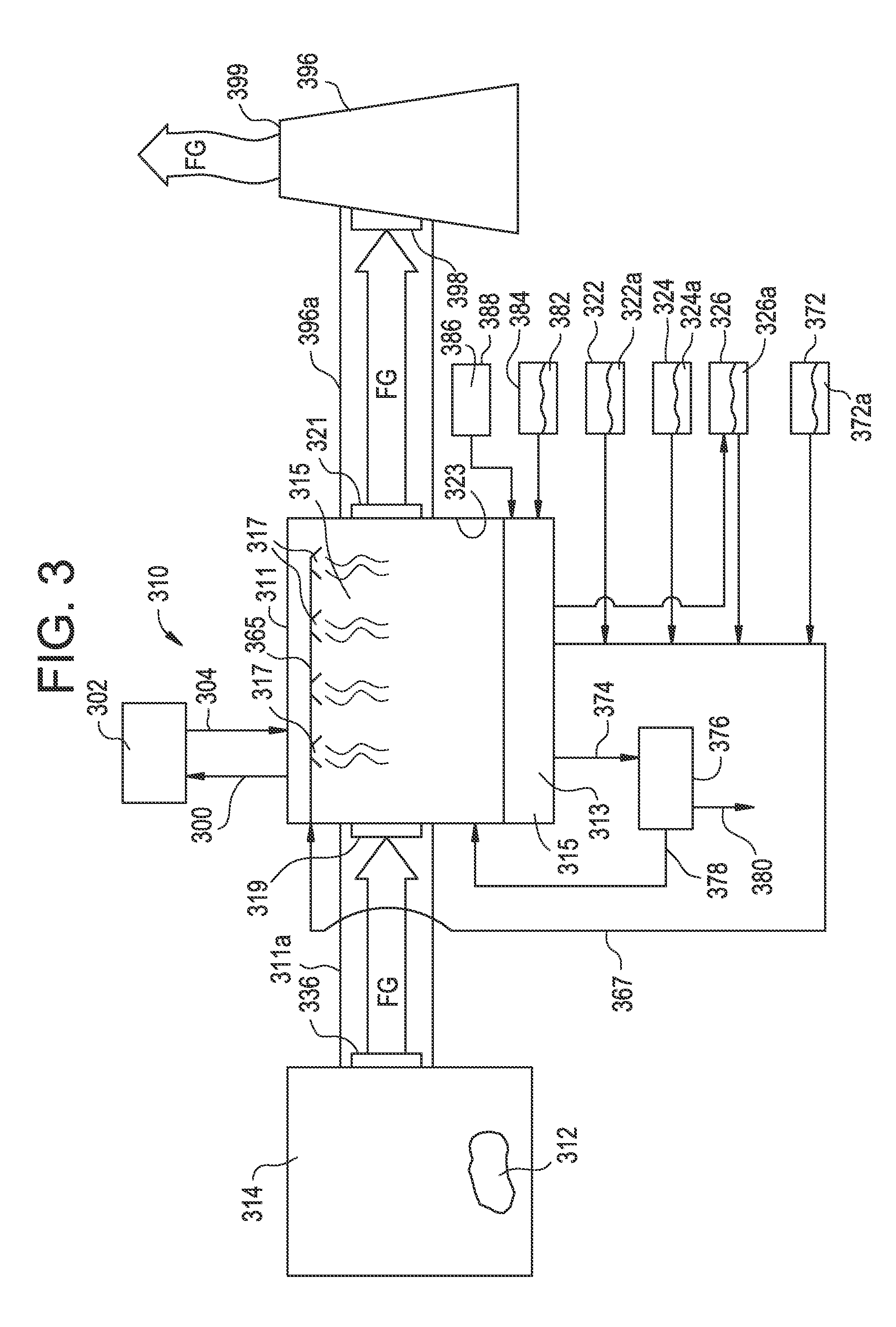

Production of hydrogen and removal and sequestration of carbon dioxide from coal-fired furnaces and boilers

InactiveUS7282189B2Increase ratingsValue maximizationOrganic chemistryNitrogen compoundsHydrogenProcess engineering

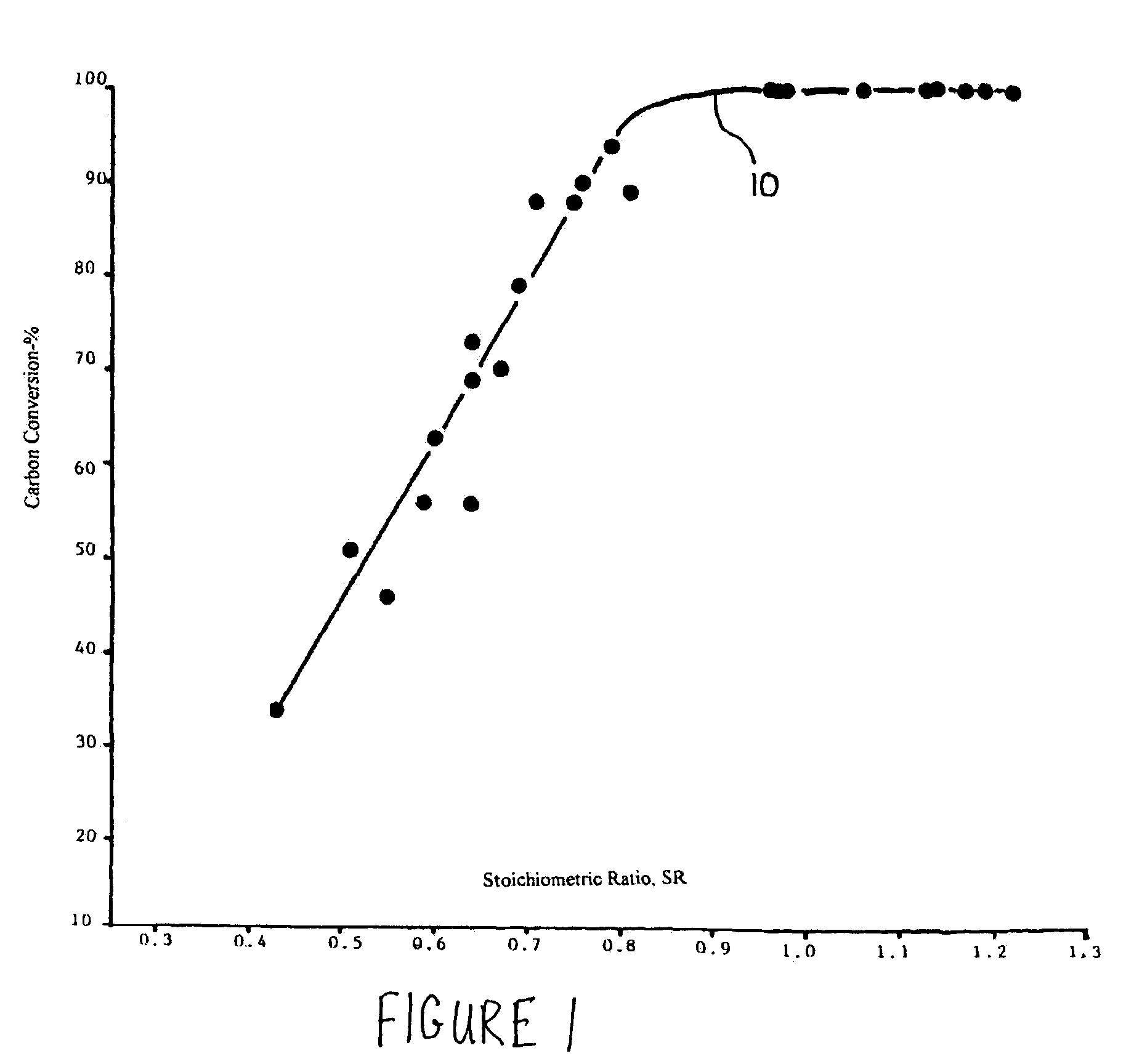

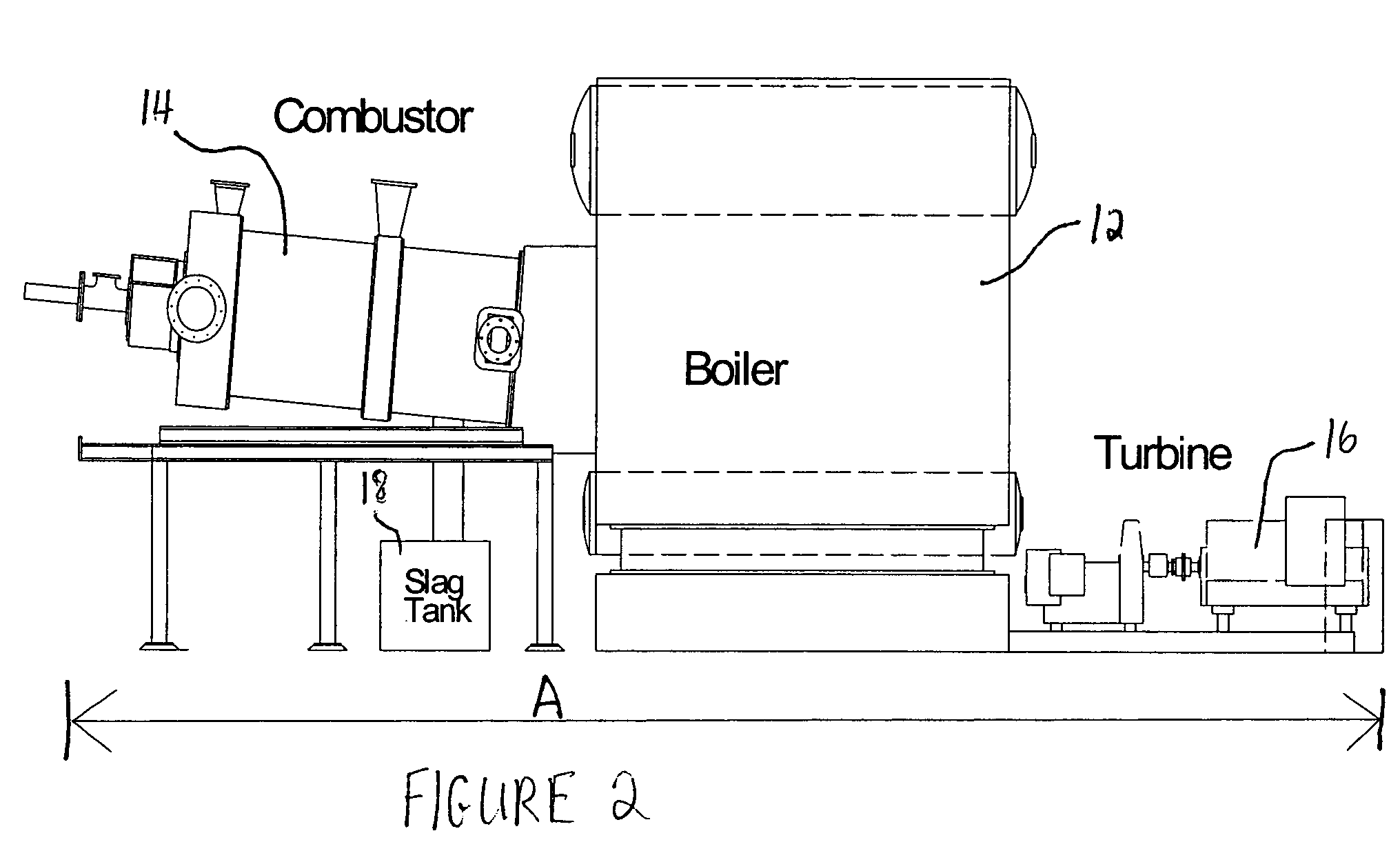

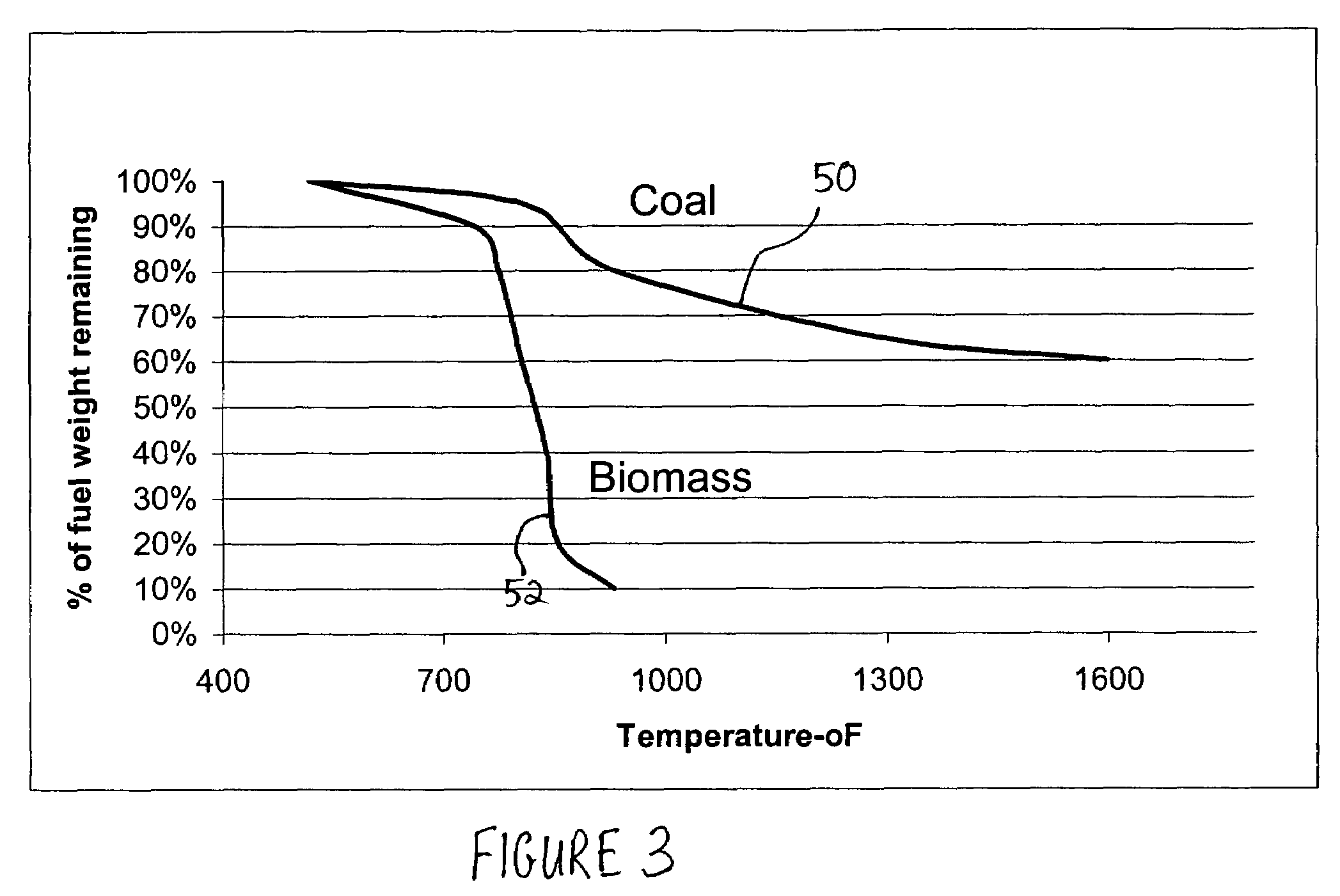

Methods for reducing and eliminating carbon dioxide from the emissions of solid fuel fired power plants, particularly coal fired power plants, and to sequester the carbon dioxide, typically by using existing equipment. In some embodiments, the methods involve pyrolyzing the solid fuel to remove volatile matter and using the volatile matter to produce hydrogen. Additionally, the methods may involve burning the solid fuel or pyrolized solid fuel at very fuel rich stoichiometric conditions. Sequestration may include the production of a carbon dioxide-containing solution and the pumping of the solution into the ground, particularly in areas high in limestone.

Owner:ZAUDERER BERT

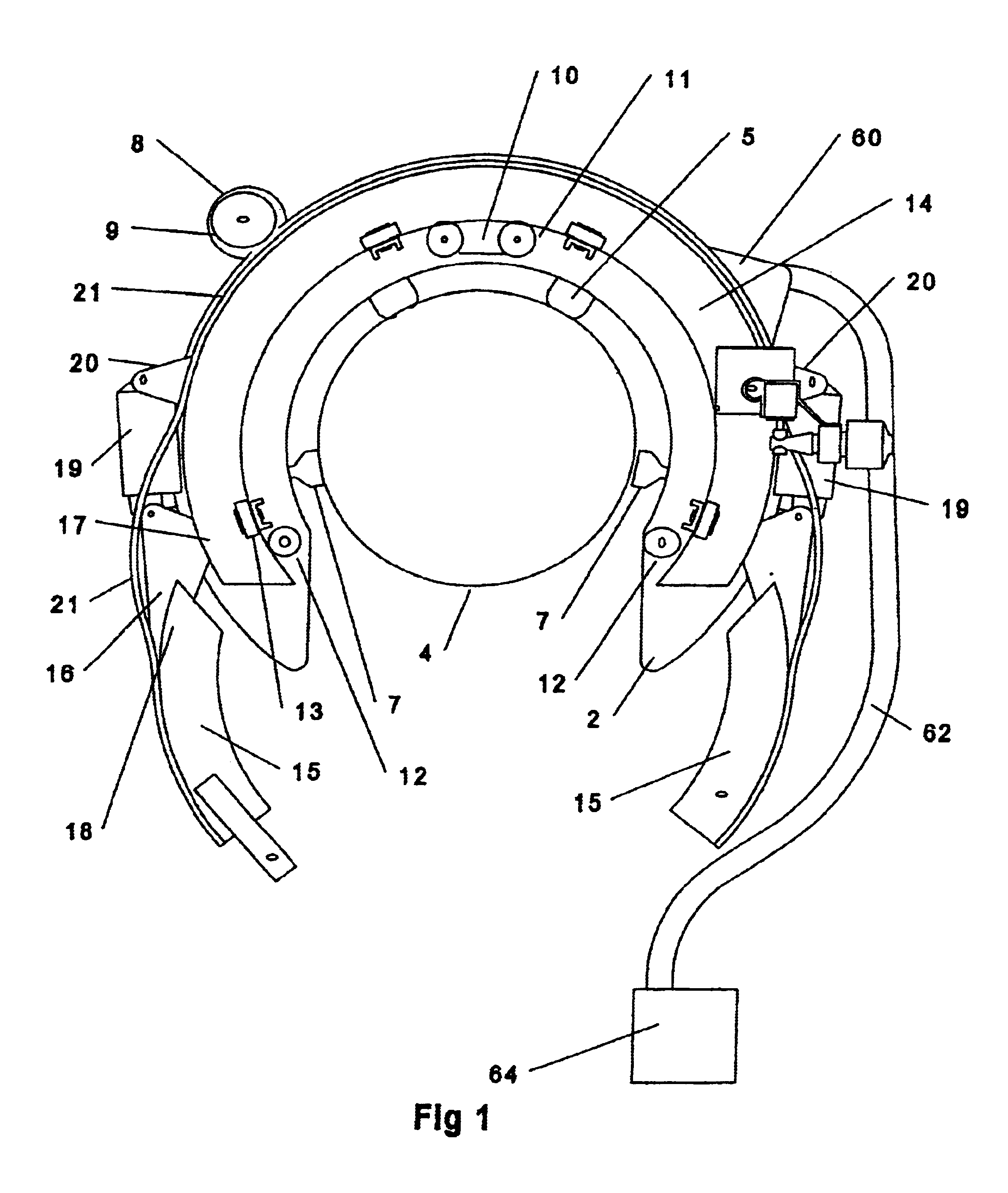

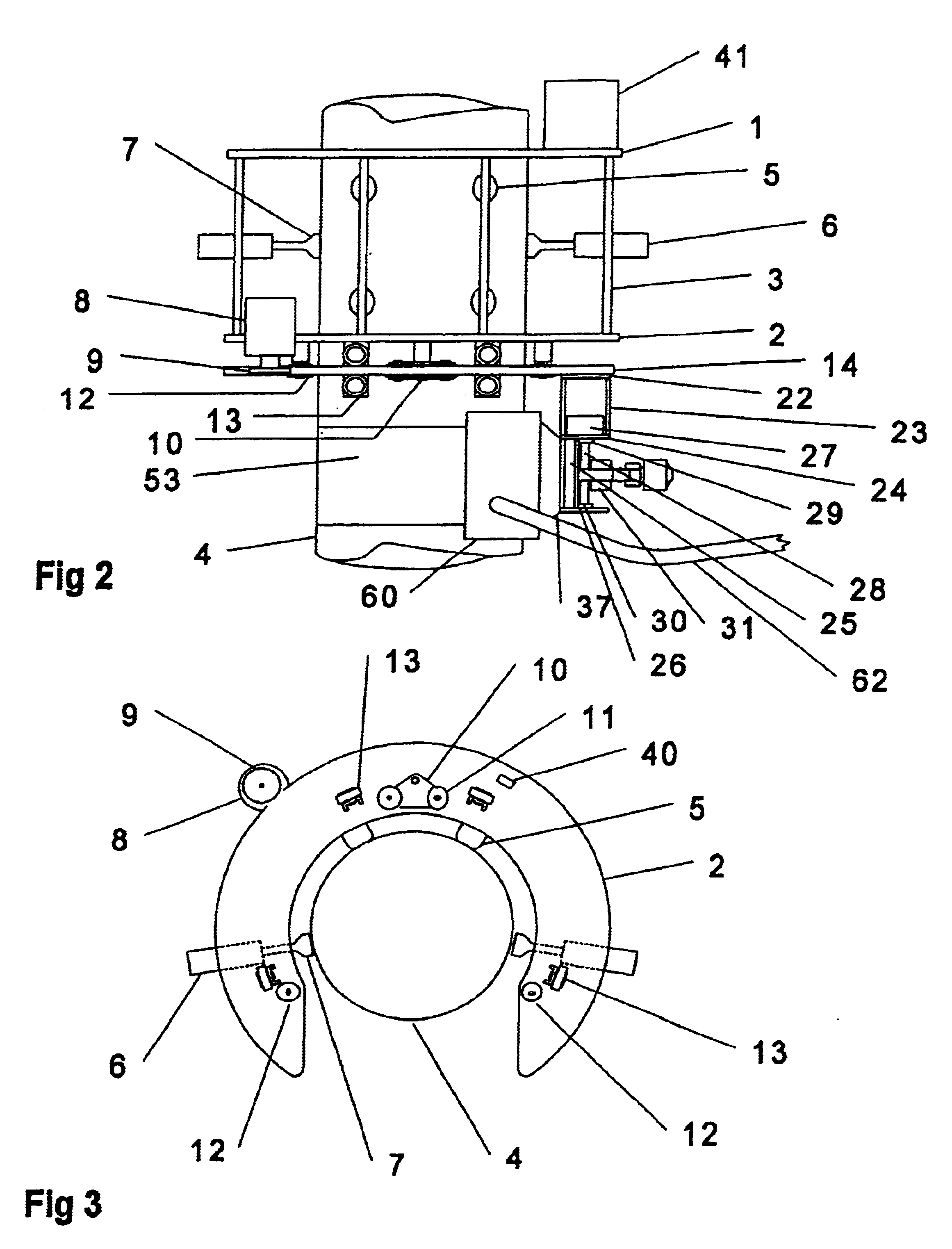

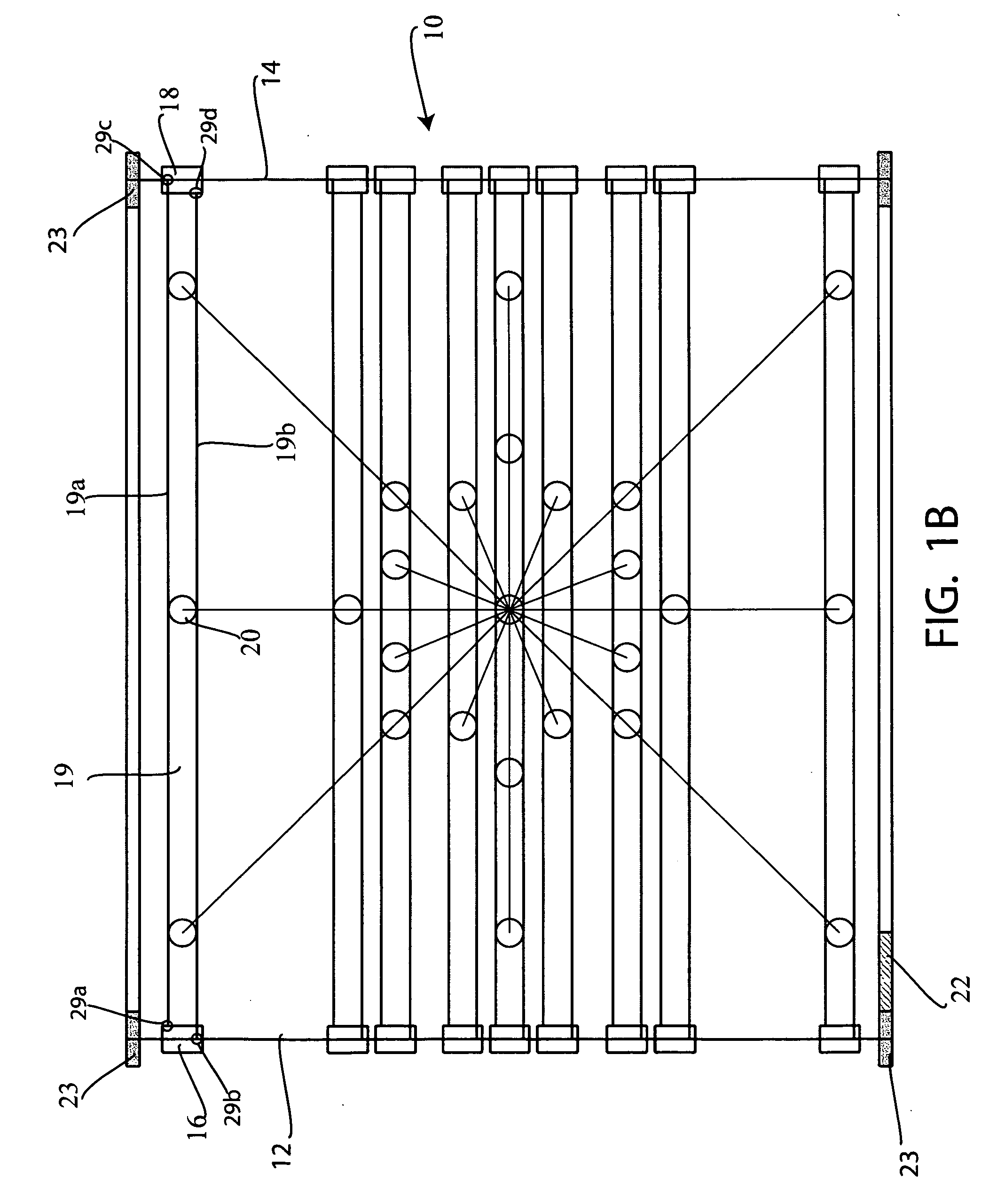

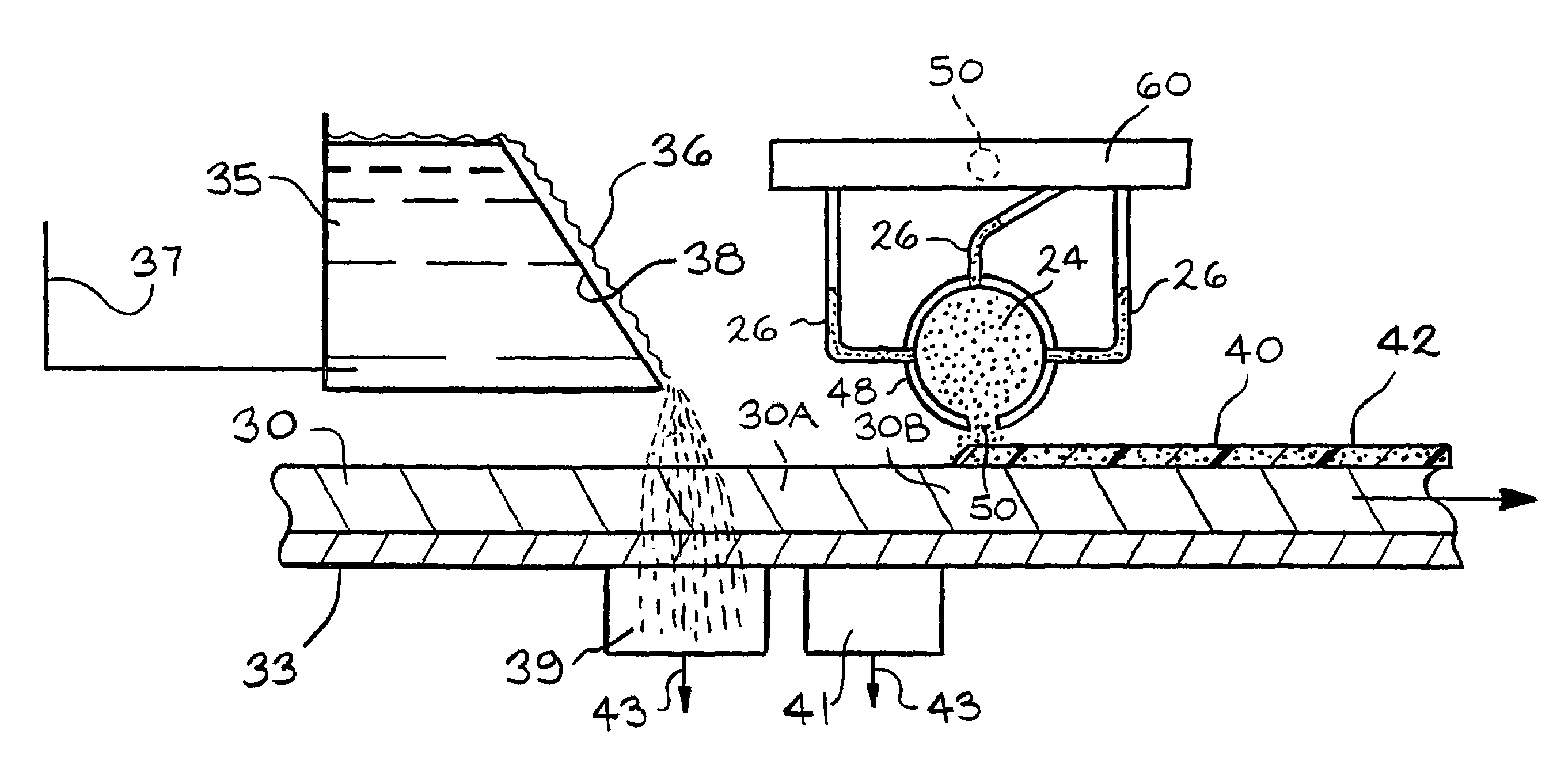

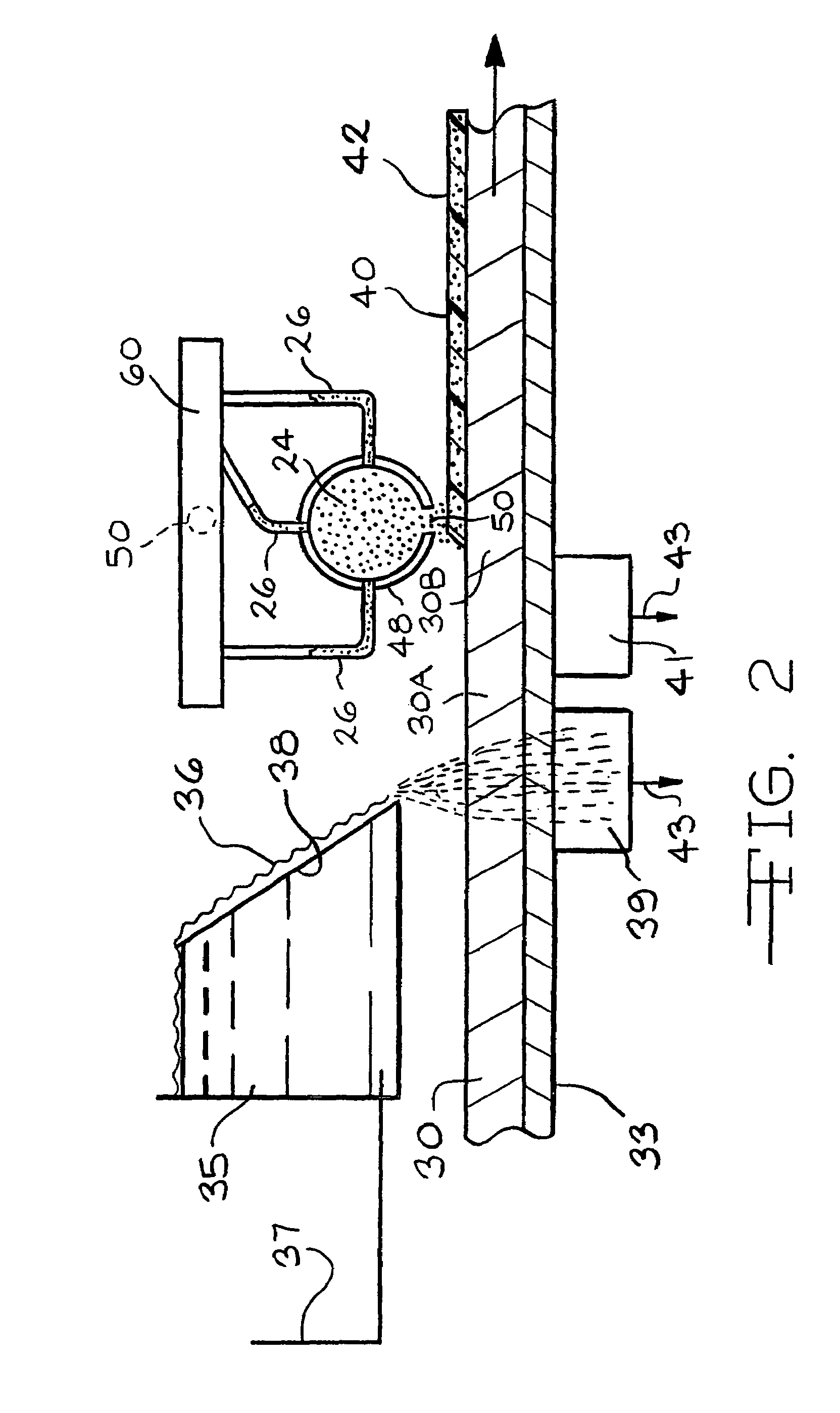

Apparatus and method for coating pipes

InactiveUS6881266B1Minimizes amount of wasteReduce riskMovable spraying apparatusVacuum evaporation coatingRange of motionSpray coating

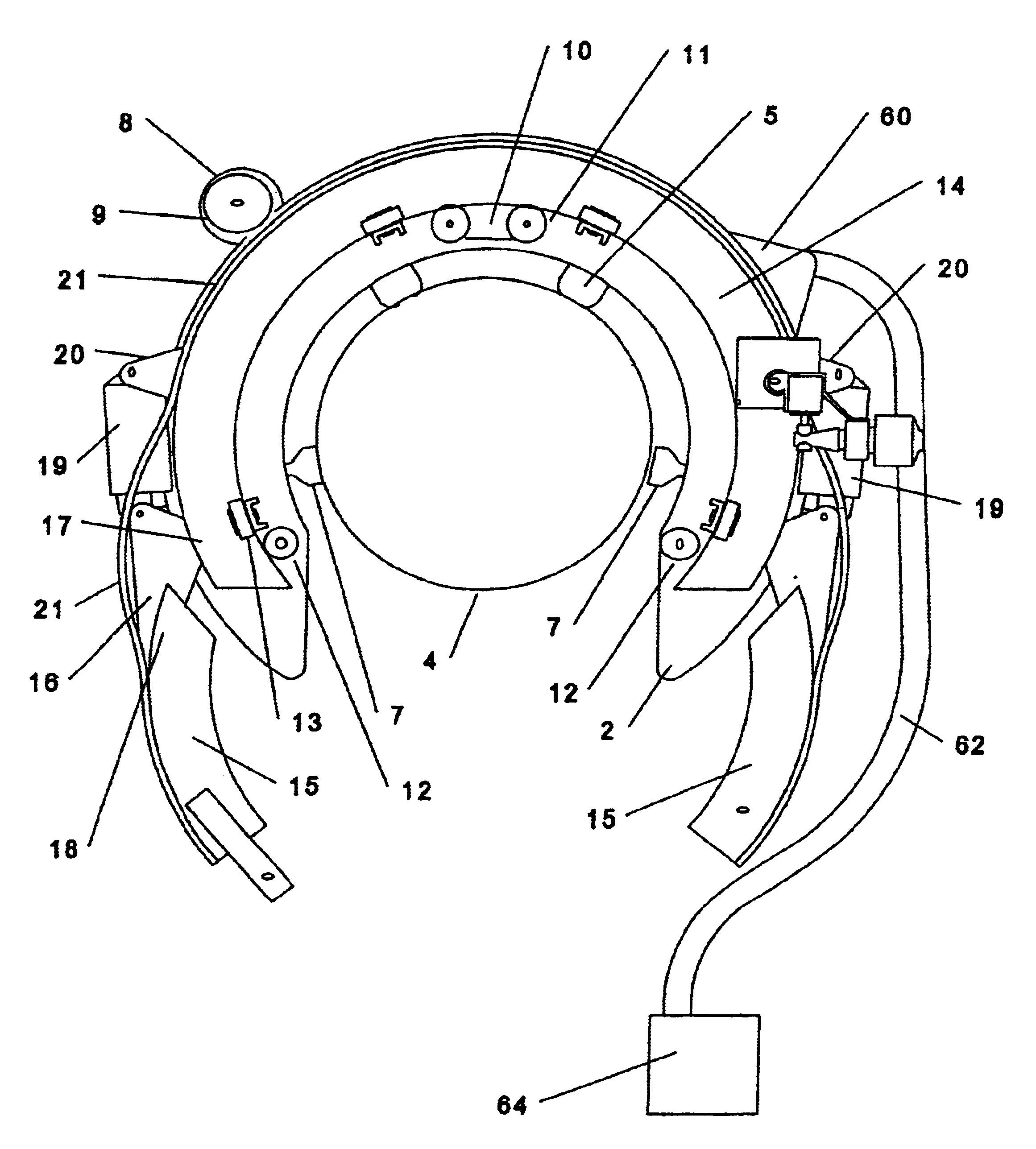

Apparatus for spraying a coating onto the outside of a pipe includes a body for mounting on a pipe to be coated. A spray gun is mounted on the body such that it can move relative to the body to spray coating completely around the periphery of the pipe. The apparatus may include only a single spray gun which is able to travel in a 360 degree range of motion around the periphery of the pipe. The apparatus is particularty suited to coating girth welds of a pipeline.

Owner:PIPELINE INDUCTION HEAT

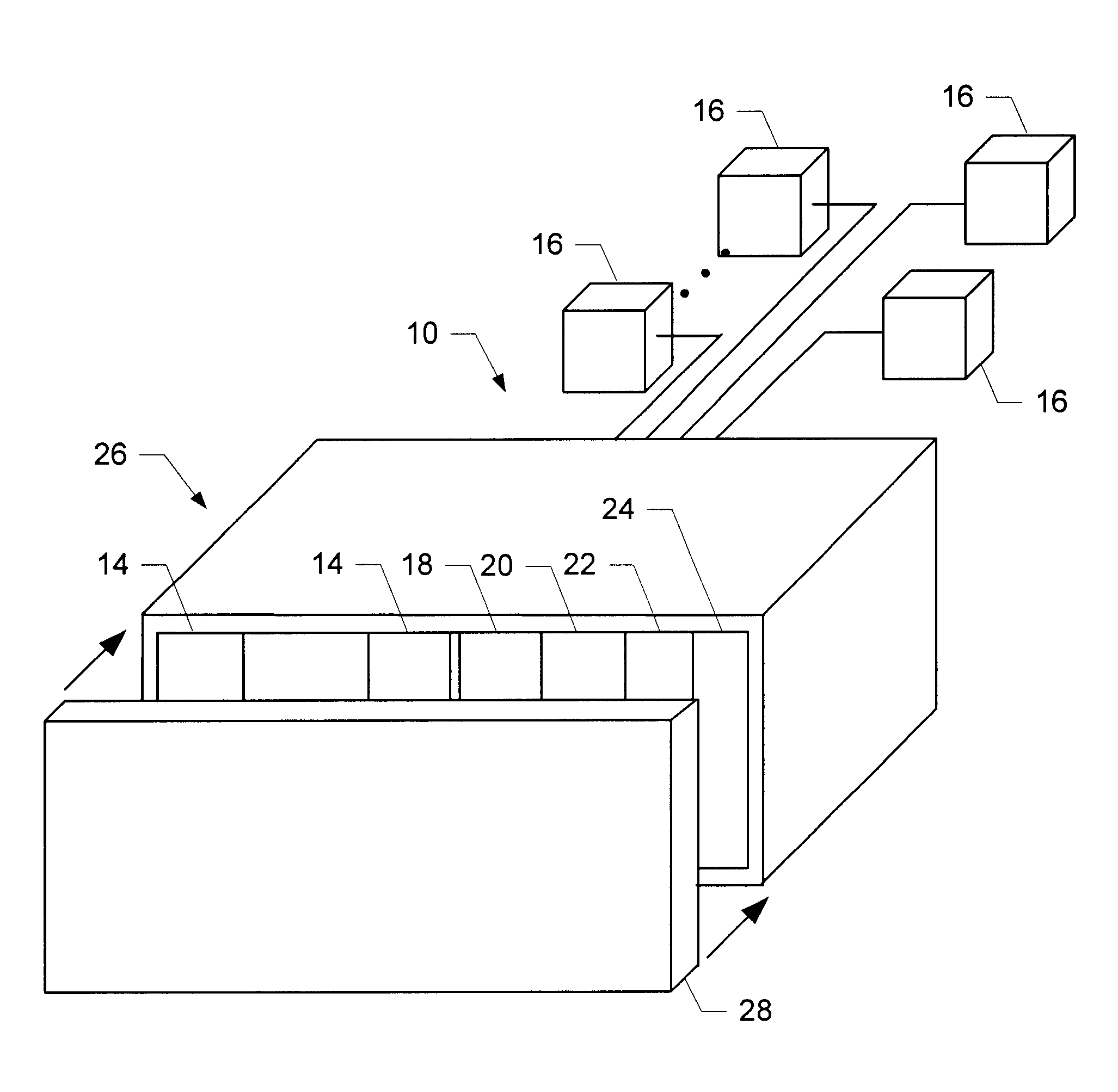

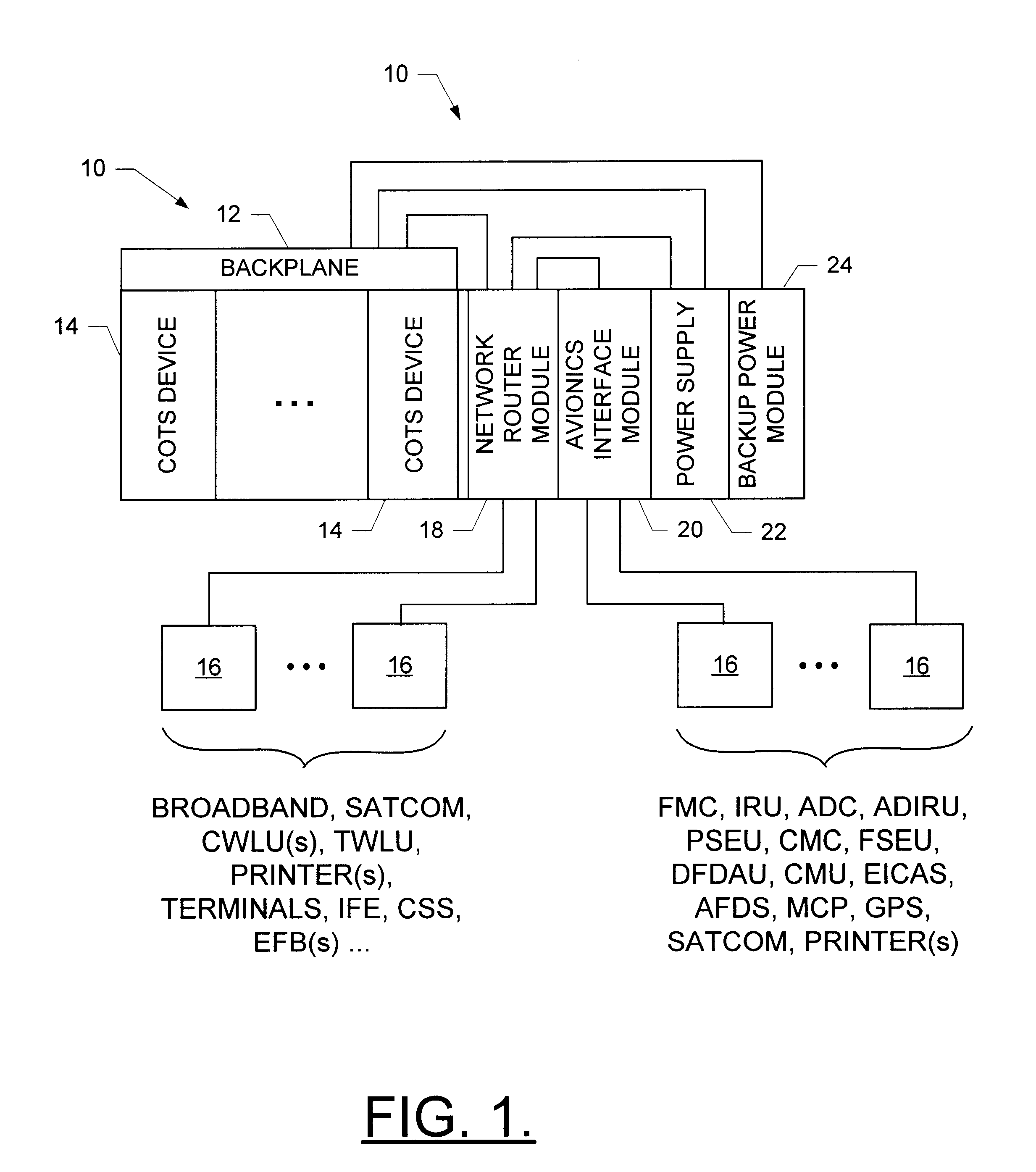

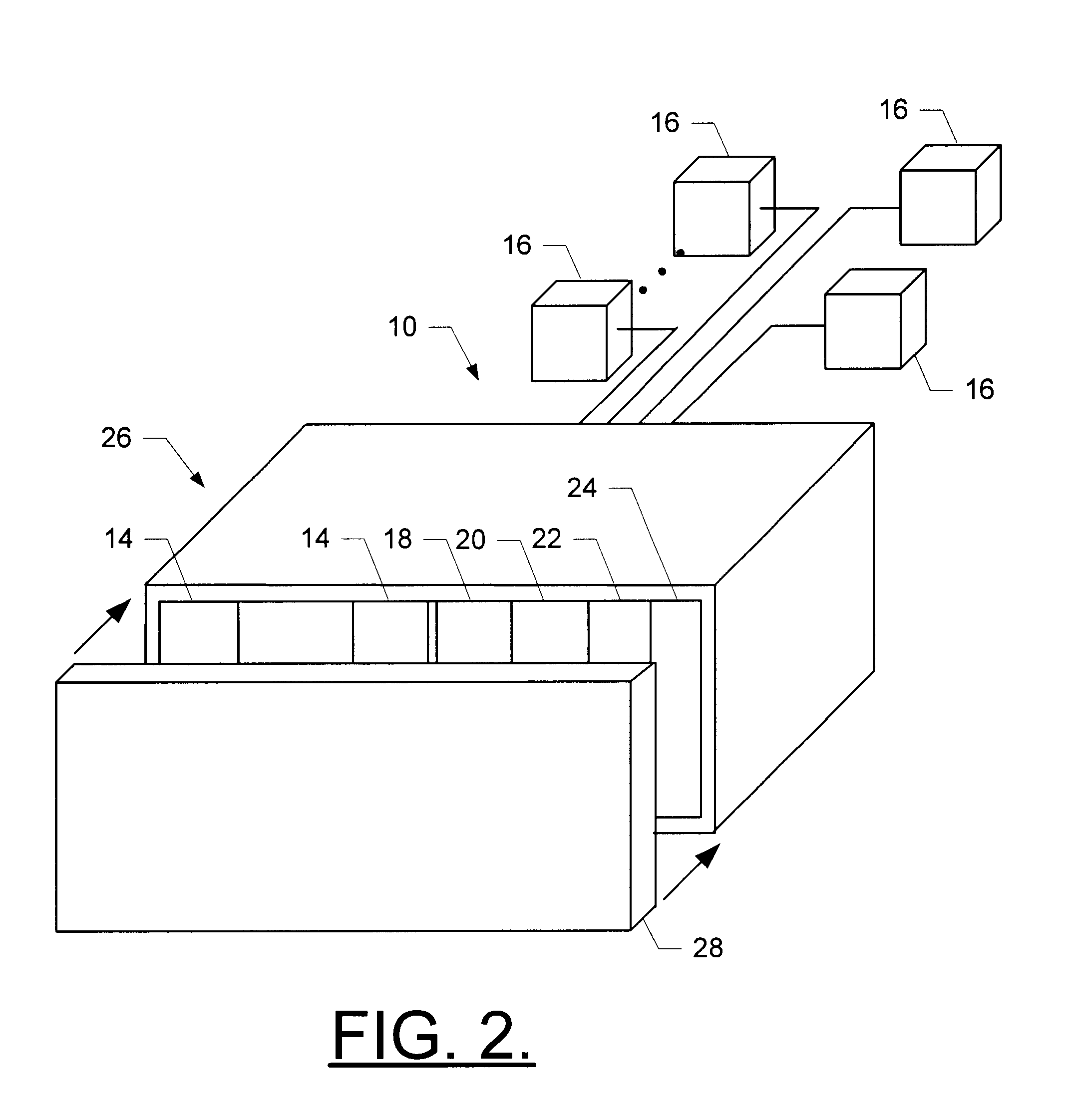

Modular aircraft information network system and an associated method of packaging the same

InactiveUS6801769B1Low costGood removal effectAircraft componentsRadio/inductive link selection arrangementsAviationElectricity

A modular aircraft information system is provided for communicating information onboard an aircraft. The modular aircraft information system includes a backplane and a network router module, and may include an avionics interface module. The backplane is capable of receiving at least one COTS device such that the COTS devices can be electrically coupled and / or decoupled to the backplane. The network router module can interface with at least one avionics device. The network router module is in electrical communication with the backplane and the avionics interface module such that the network router module is capable of passing communications between the COTS devices and the avionics devices when the COTS devices are electrically coupled to the backplane. The network router is also capable of isolating the backplane from the avionics devices such that the COTS devices, when electrically coupled to the backplane, are at least partially isolated from the avionics devices.

Owner:THE BOEING CO

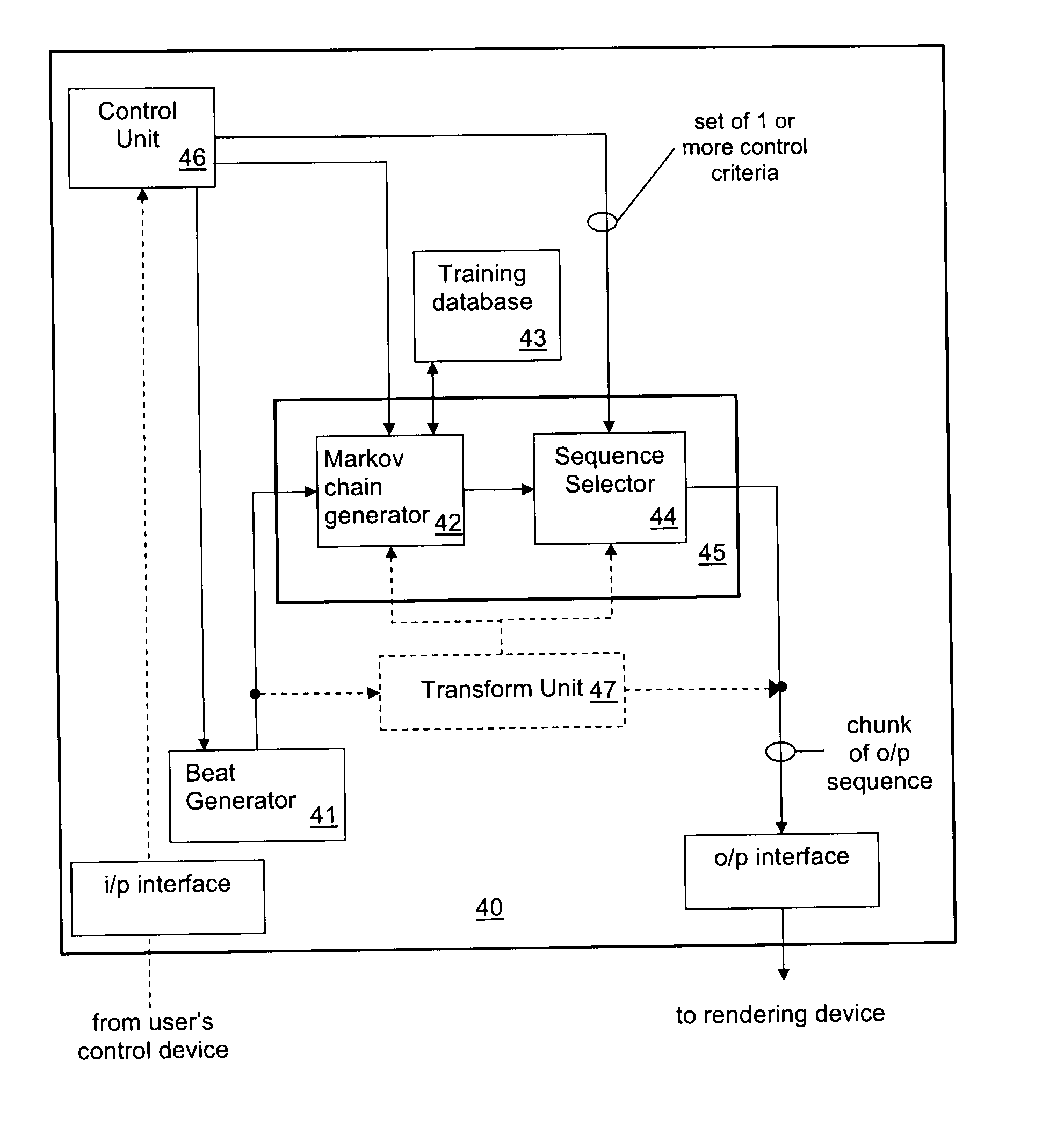

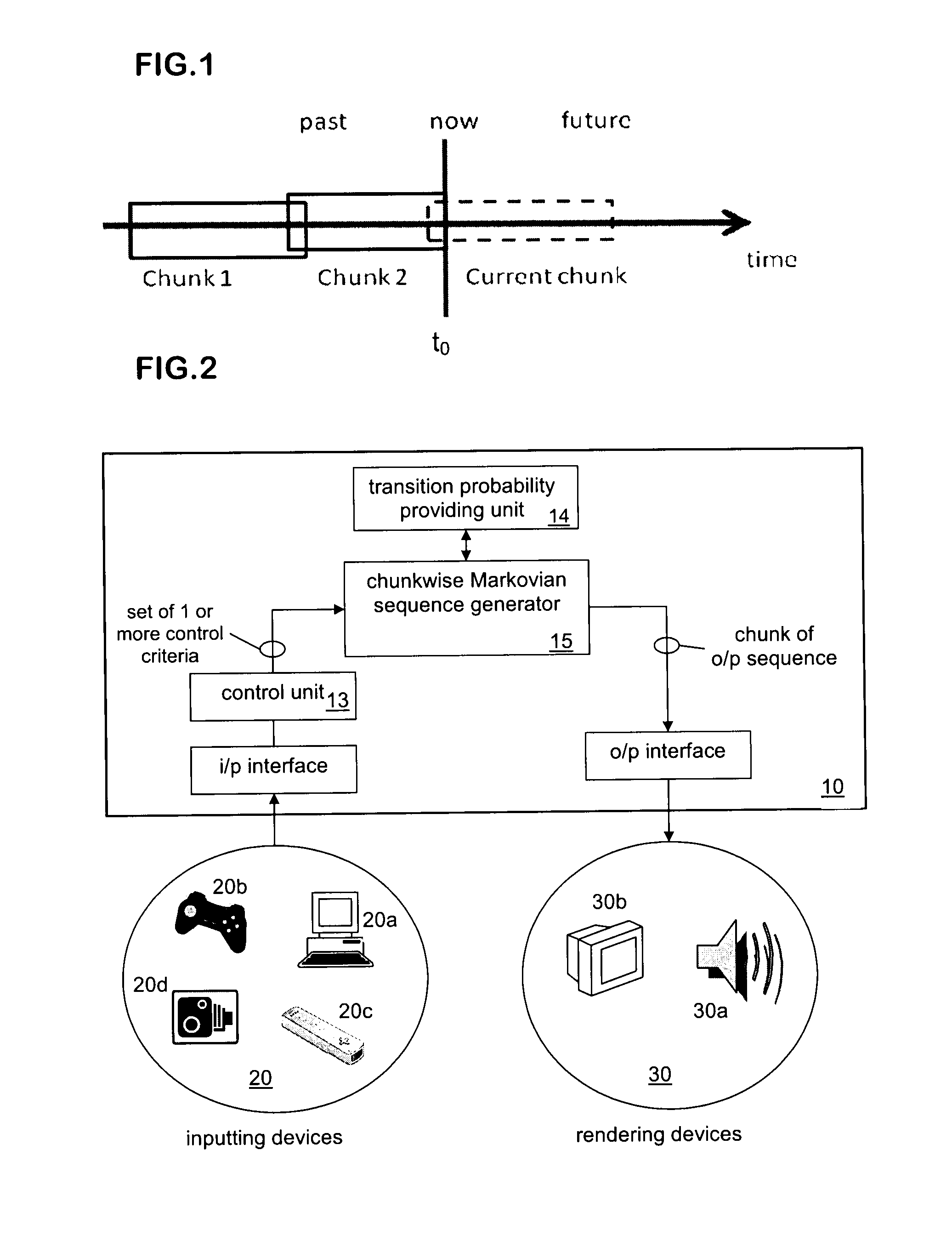

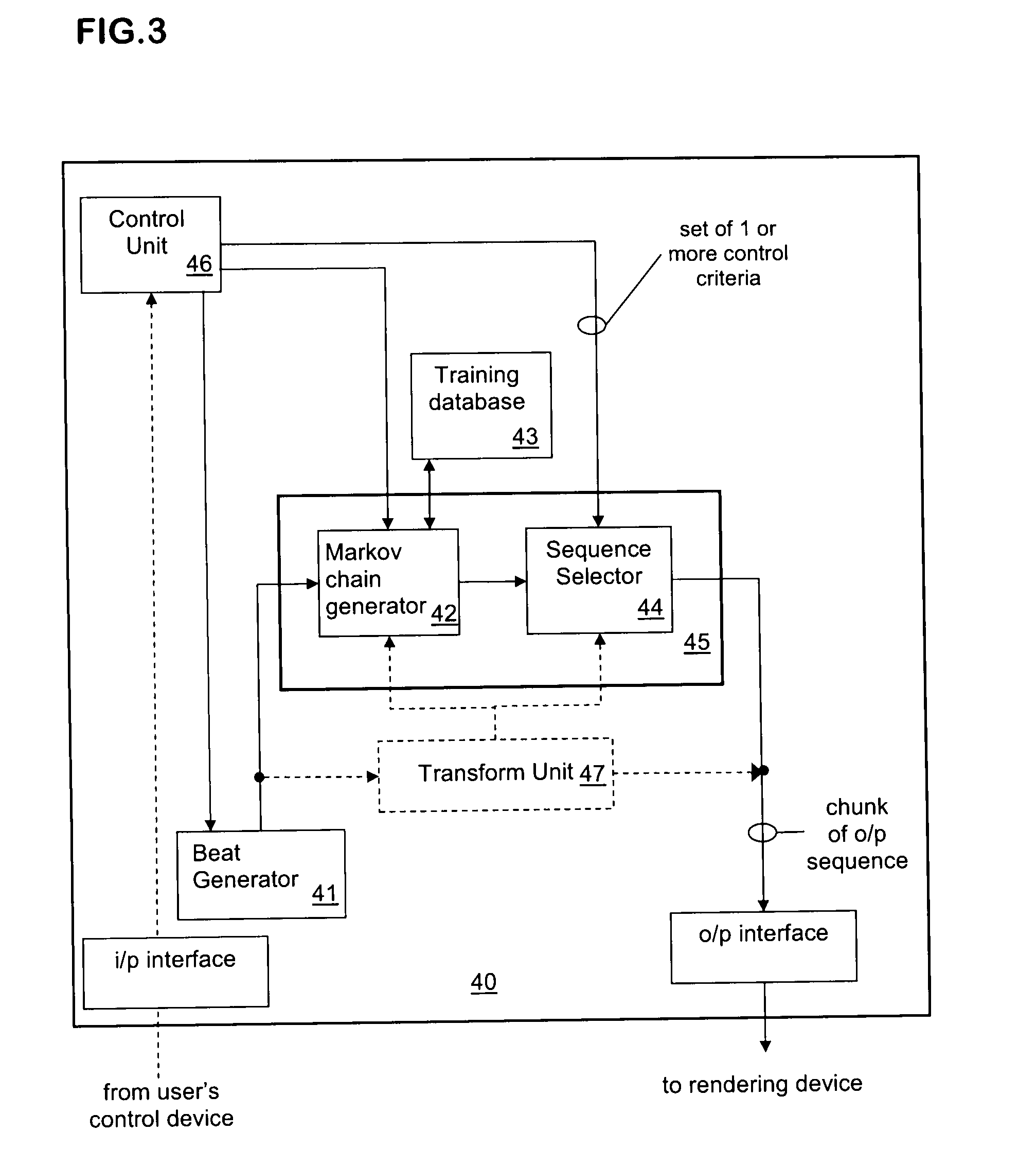

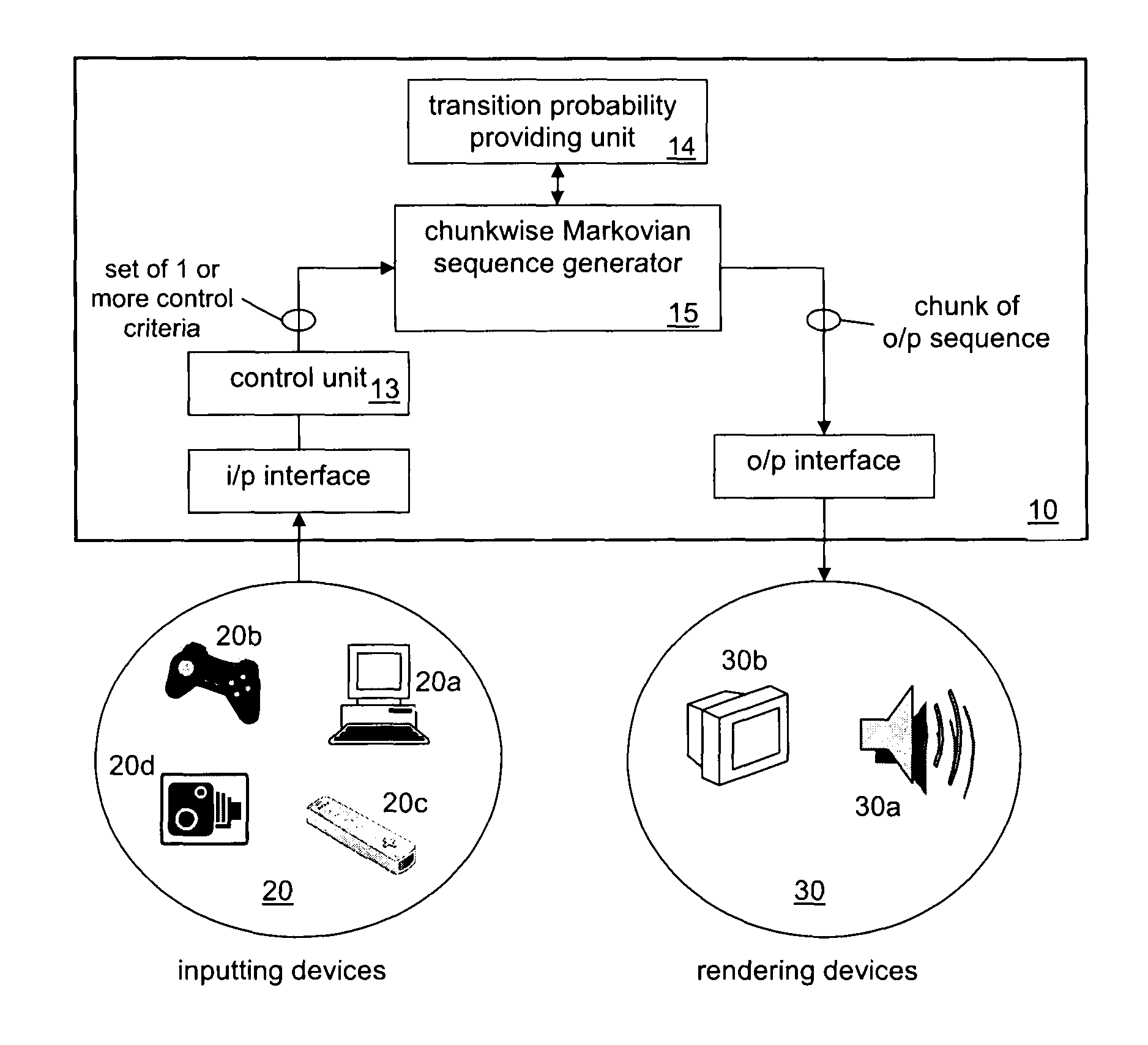

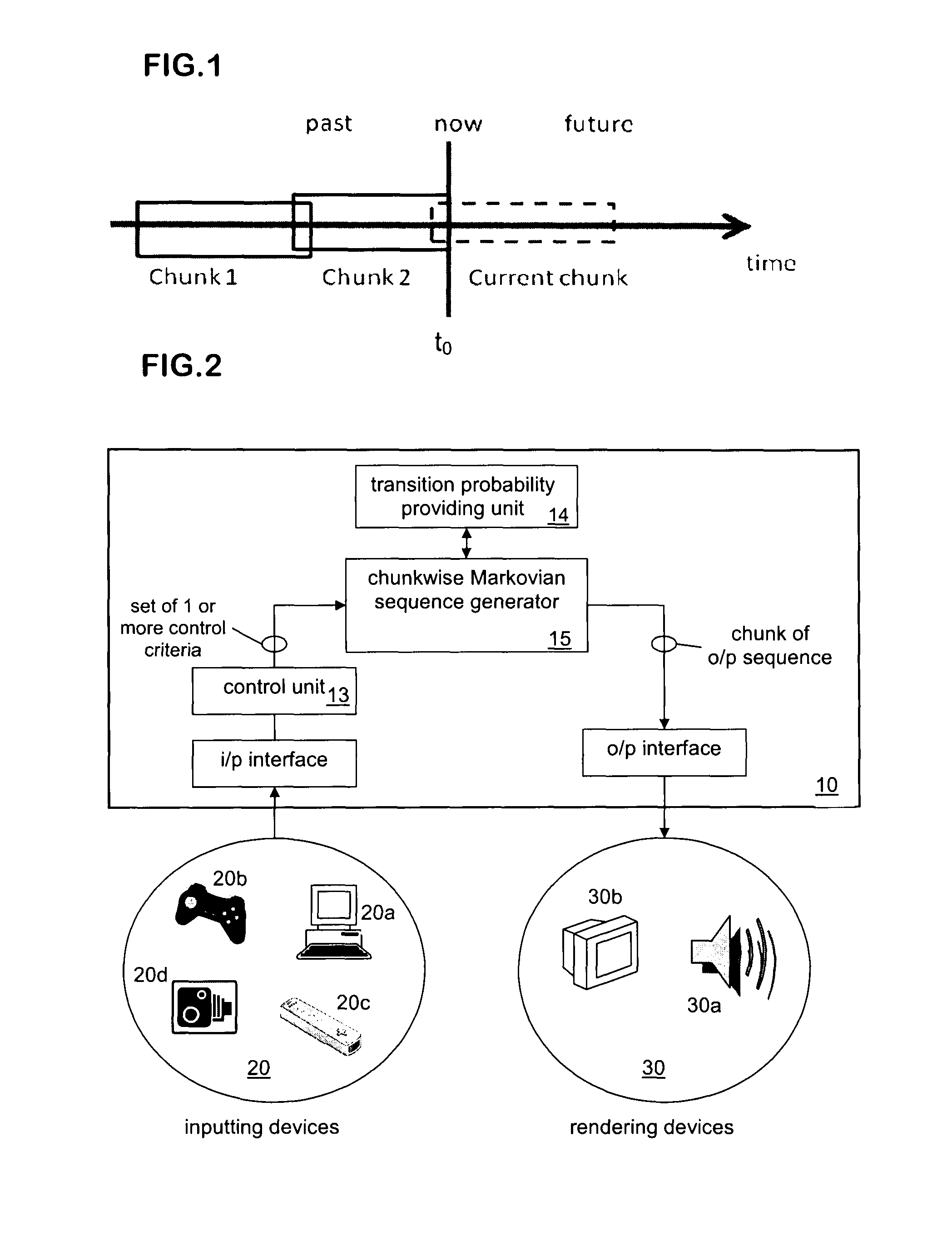

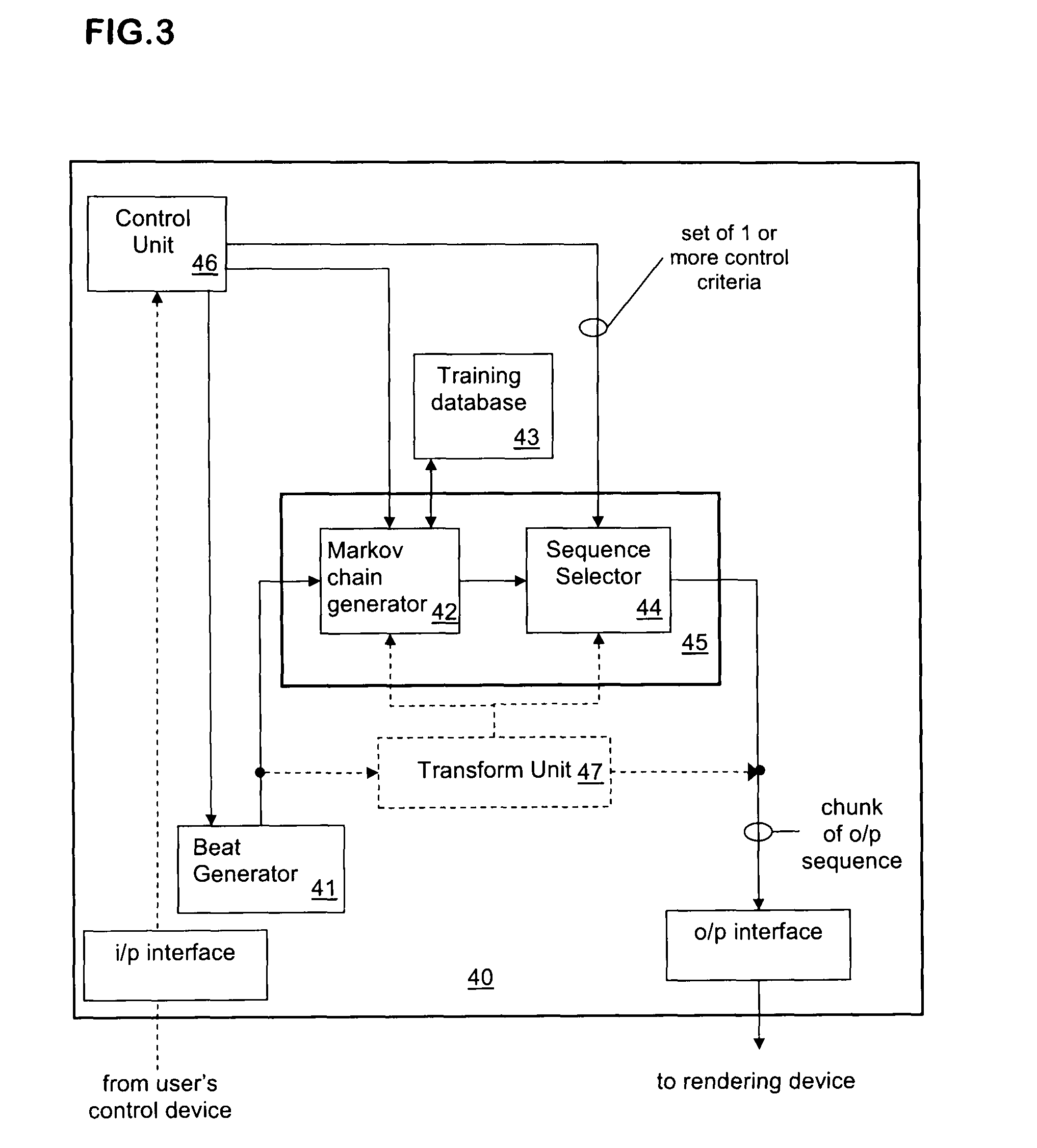

Markovian-sequence generator and new methods of generating markovian sequences

ActiveUS20110010321A1Extensive controlMore “costly”Mathematical modelsElectrophonic musical instrumentsConstraint satisfaction problemExecution control

A new type of Markovian sequence generator and generation method generates a Markovian sequence having controllable properties, notably properties that satisfy at least one control criterion which is a computable requirement holding on items in the sequence. The Markovian sequence is generated chunkwise, each chunk containing a plurality of items in the sequence. During generation of each chunk a search is performed in the space of Markovian sequences to find a chunk-sized series of items which enables the control criterion to be satisfied. The search can be performed using a generate and test approach in which chunk-sized Markovian sequences are generated then tested for compliance with the requirement(s) of the control criteria. Alternatively, the search can be performed by formulating the sequence-generation task as a constraint satisfaction problem, with one or more constraints ensuring that the generated sequence is Markovian and one or more constraints enforcing the requirement(s) of the control criteria. The sequence generator can be used in an interactive system where a user specifies the control criterion via an inputting device (20).

Owner:SONY CORP

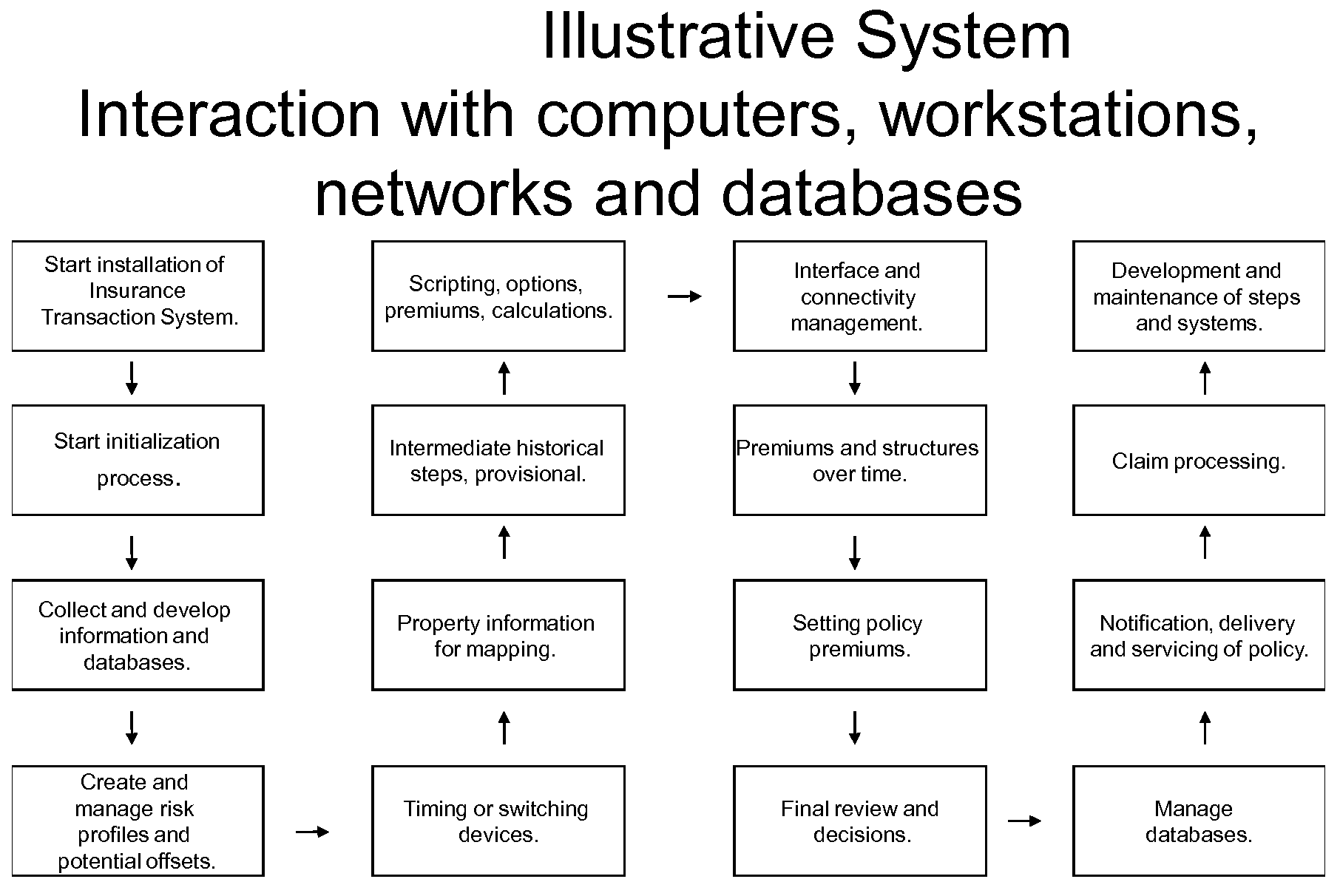

Insurance Transaction System and Method

The present invention is a system and method of creating insurance with a switching device that limits the liability of the insurer and the potential loss of the insured.

Owner:KOZIOL JOSEPH D

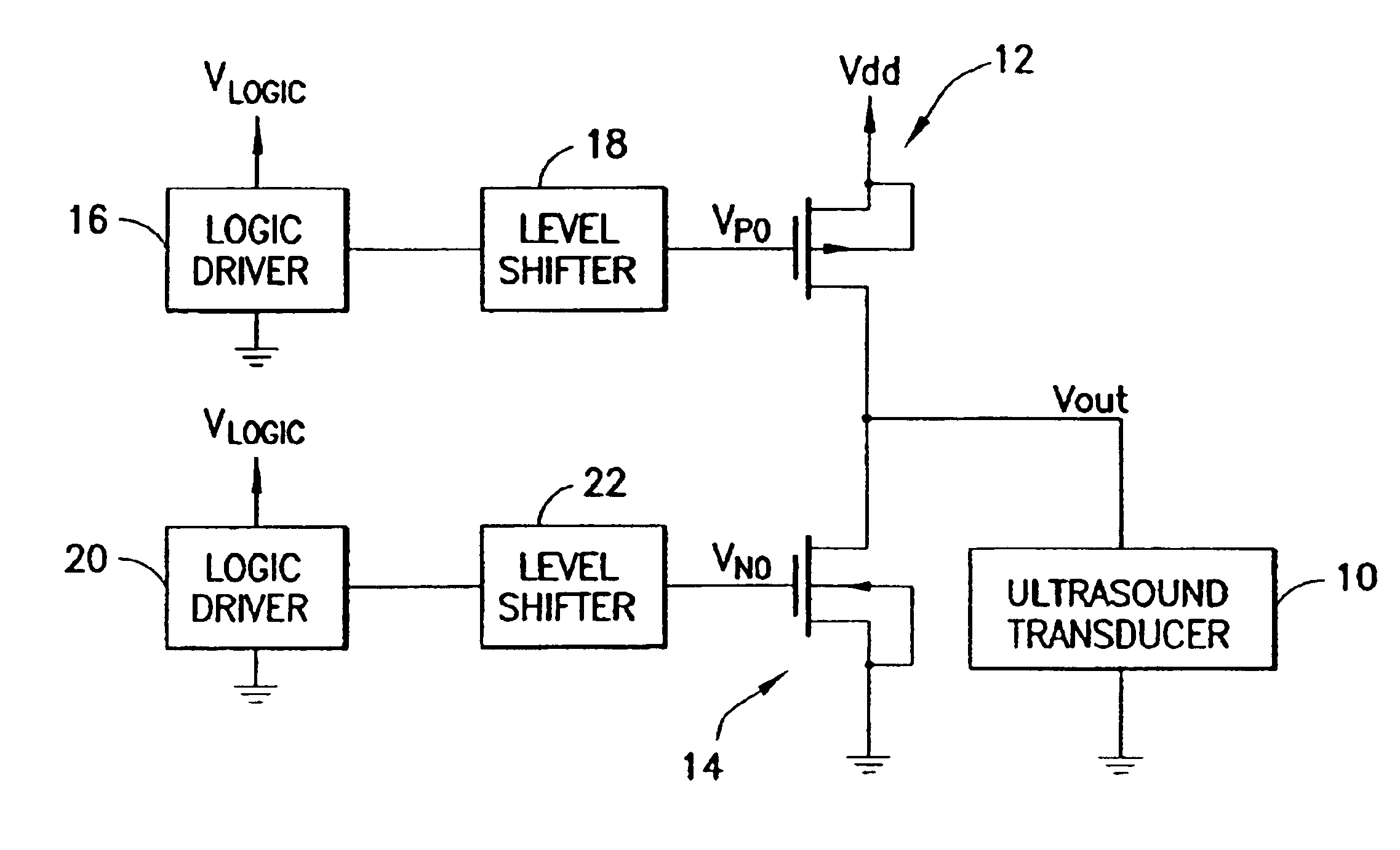

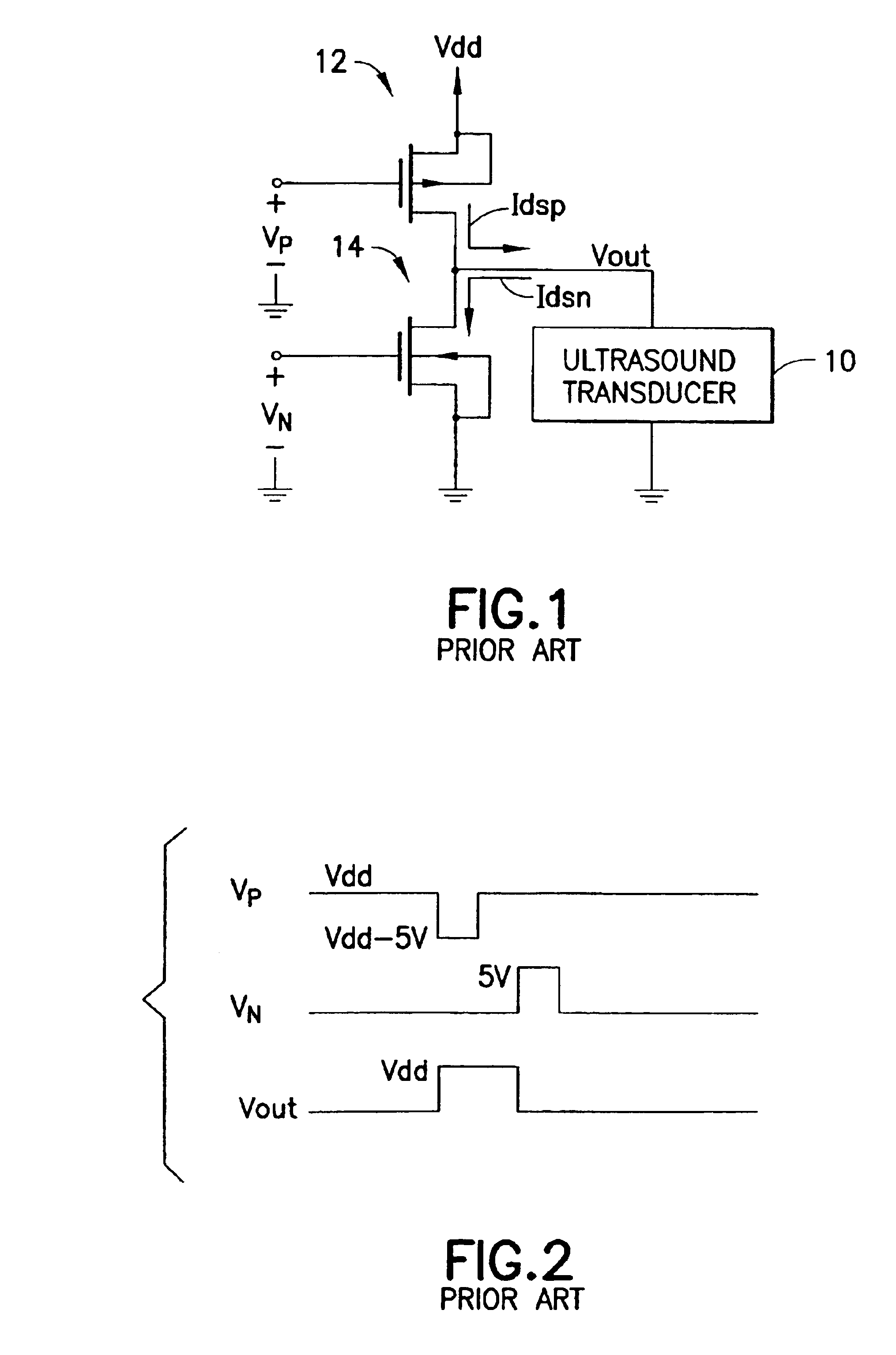

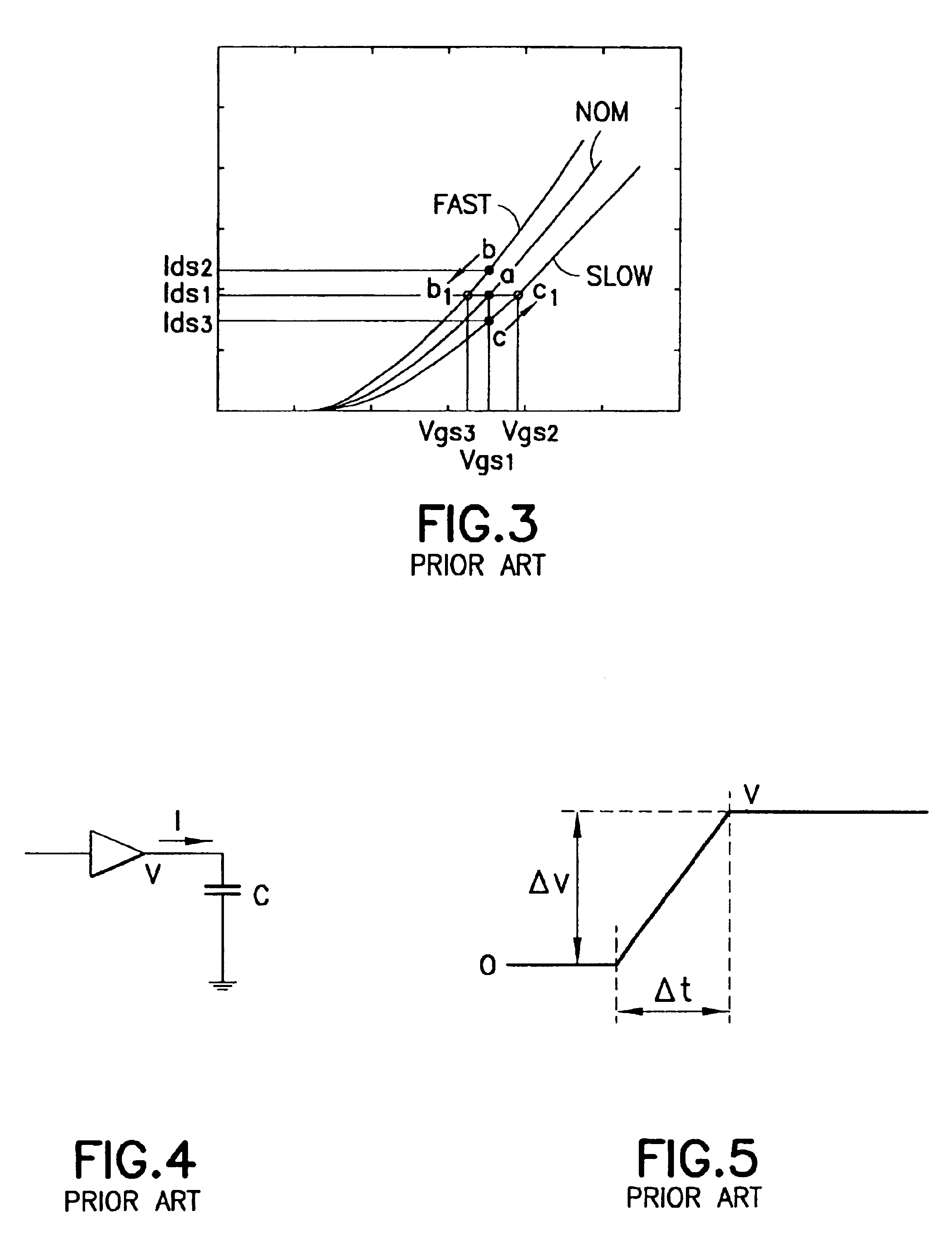

Ultrasound transmitter with voltage-controlled rise/fall time variation

InactiveUS6856175B2Shorten the timeReduce variationContinuous to patterned pulse manipulationElectronic switchingEngineeringUltrasound

In an ultrasound transmit ASIC, the rise and fall times of the output pulse can be controlled by varying the gate-source voltage used to drive the output-stage transistors. Control of the rise / fall times can be effected either by trimming on-chip during fabrication or by changing the gate-source voltage that drives the output-stage transistors, either on-chip or off-chip. In all cases it will be necessary to first test the manufactured device to determine how much calibration voltage needs to be applied.

Owner:GENERAL ELECTRIC CO

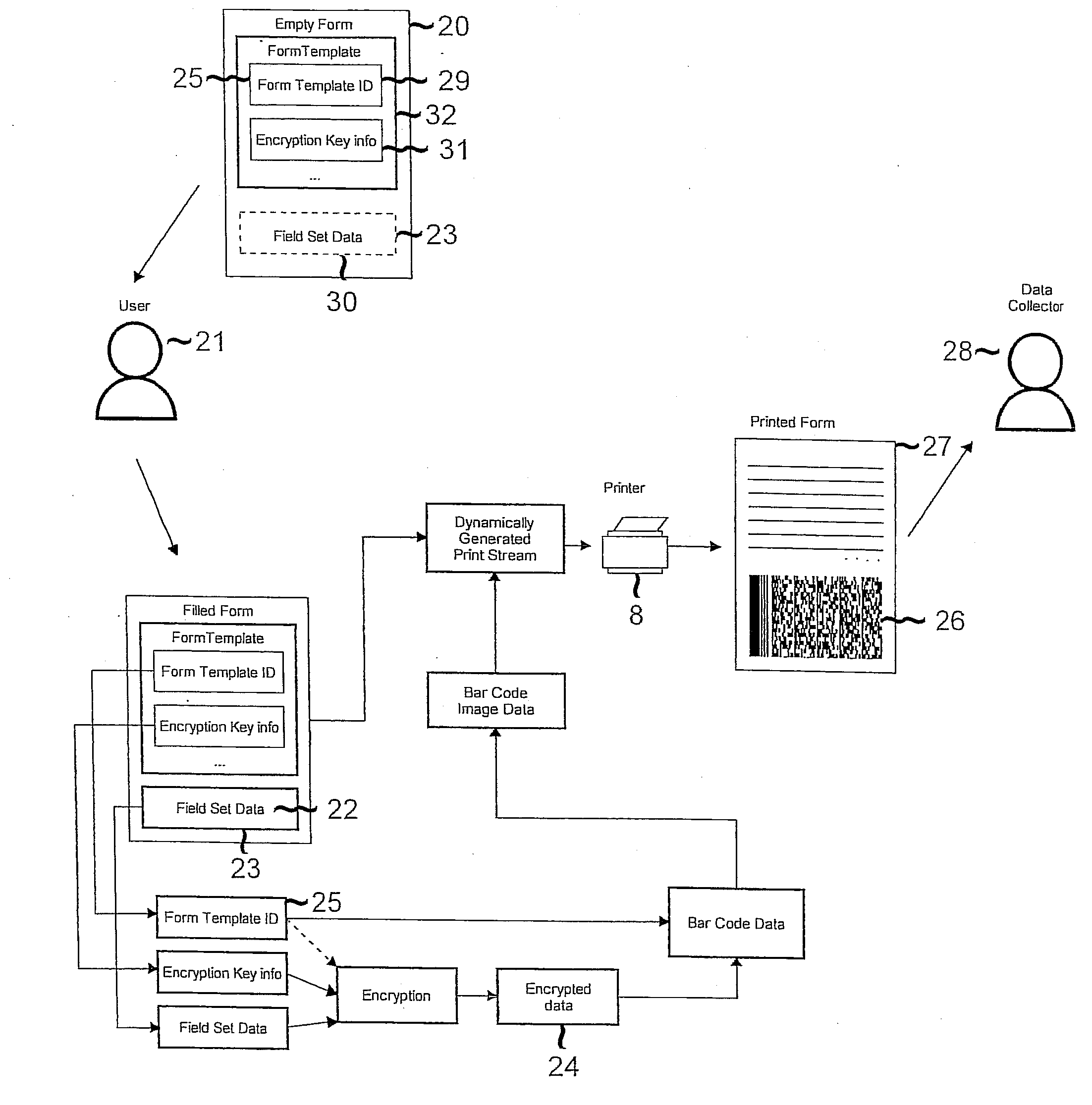

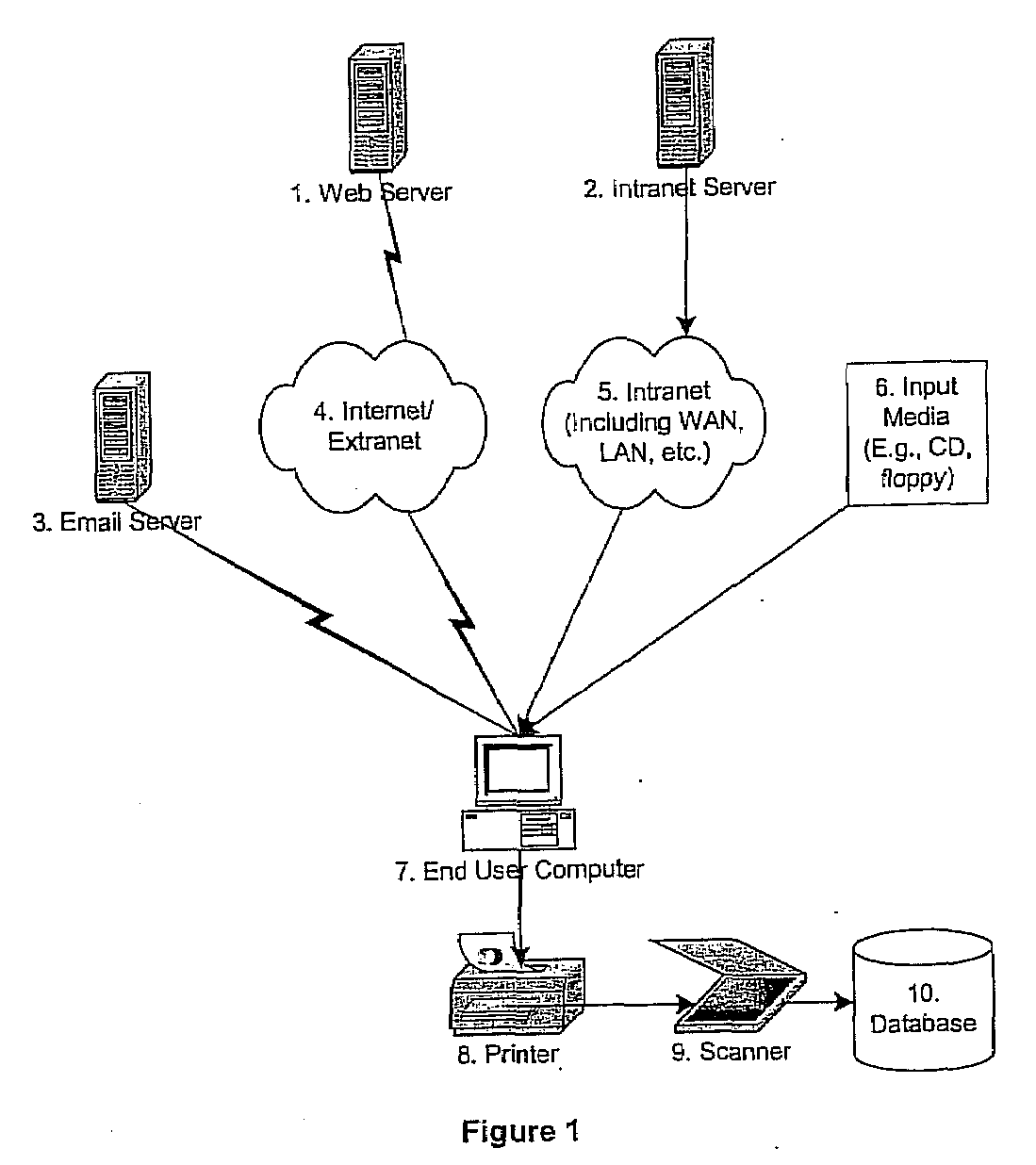

Method and system for increasing the accuracy and security of data capture from a paper form

InactiveUS20080130896A1Improve accuracyImprove securityCoding/ciphering apparatusSecuring communicationBarcodeAuthentication

A method and system is provided for increasing the accuracy and security of data capture from a paper form where the form was completed electronically and printed out prior to submission. The invention utilizes two-dimensional barcode technology to dynamically capture data entered electronically into the form. The data contained in this two-dimensional barcode is then encrypted for security and authentication purposes and printed on the form when the user prints the form. When the printed form is received by the Data Collector at a central processing site, the two-dimensional barcode is scanned and decrypted, the form is authenticated, and the data is extracted virtually error-free

Owner:FORMATTA

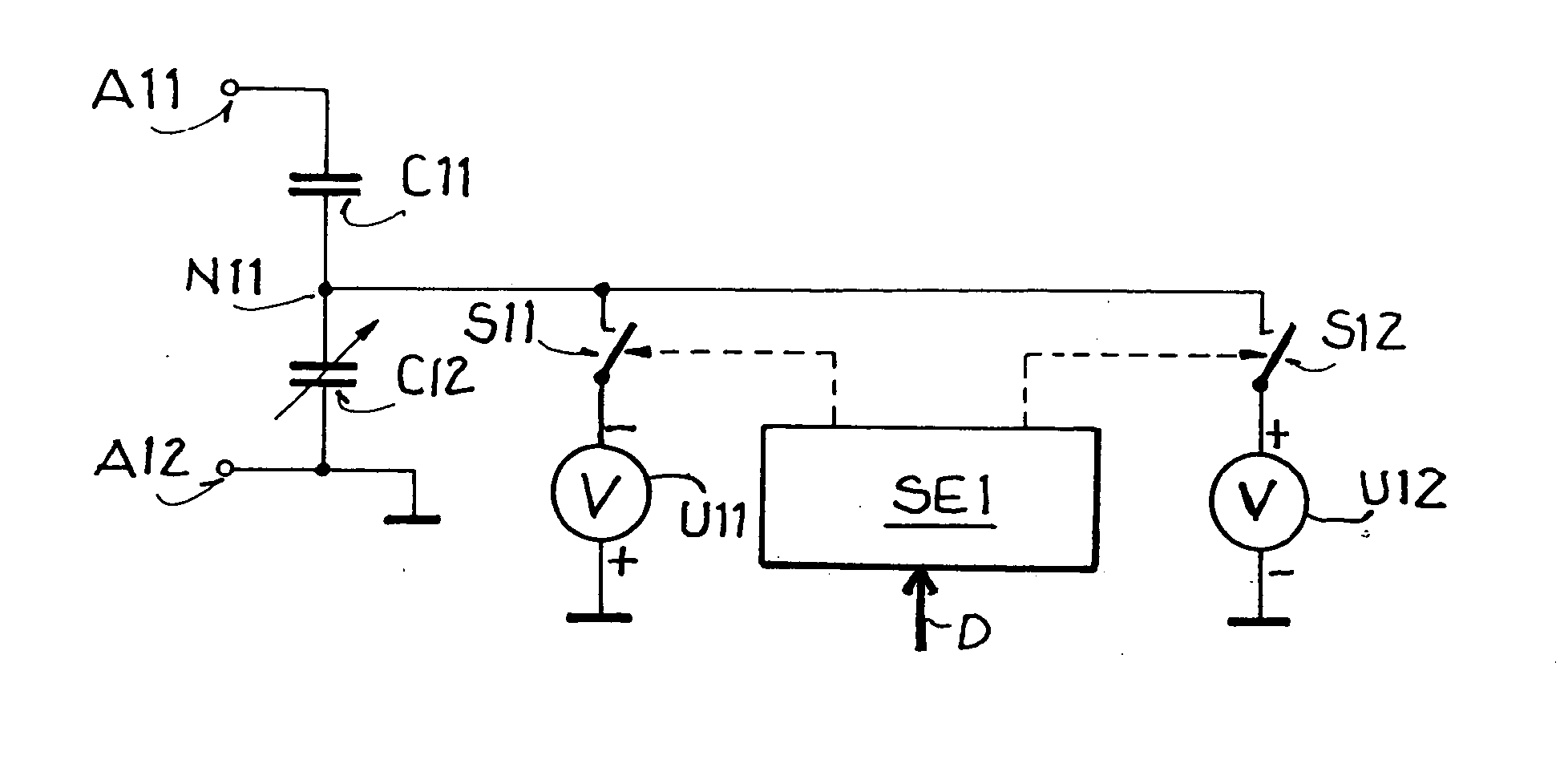

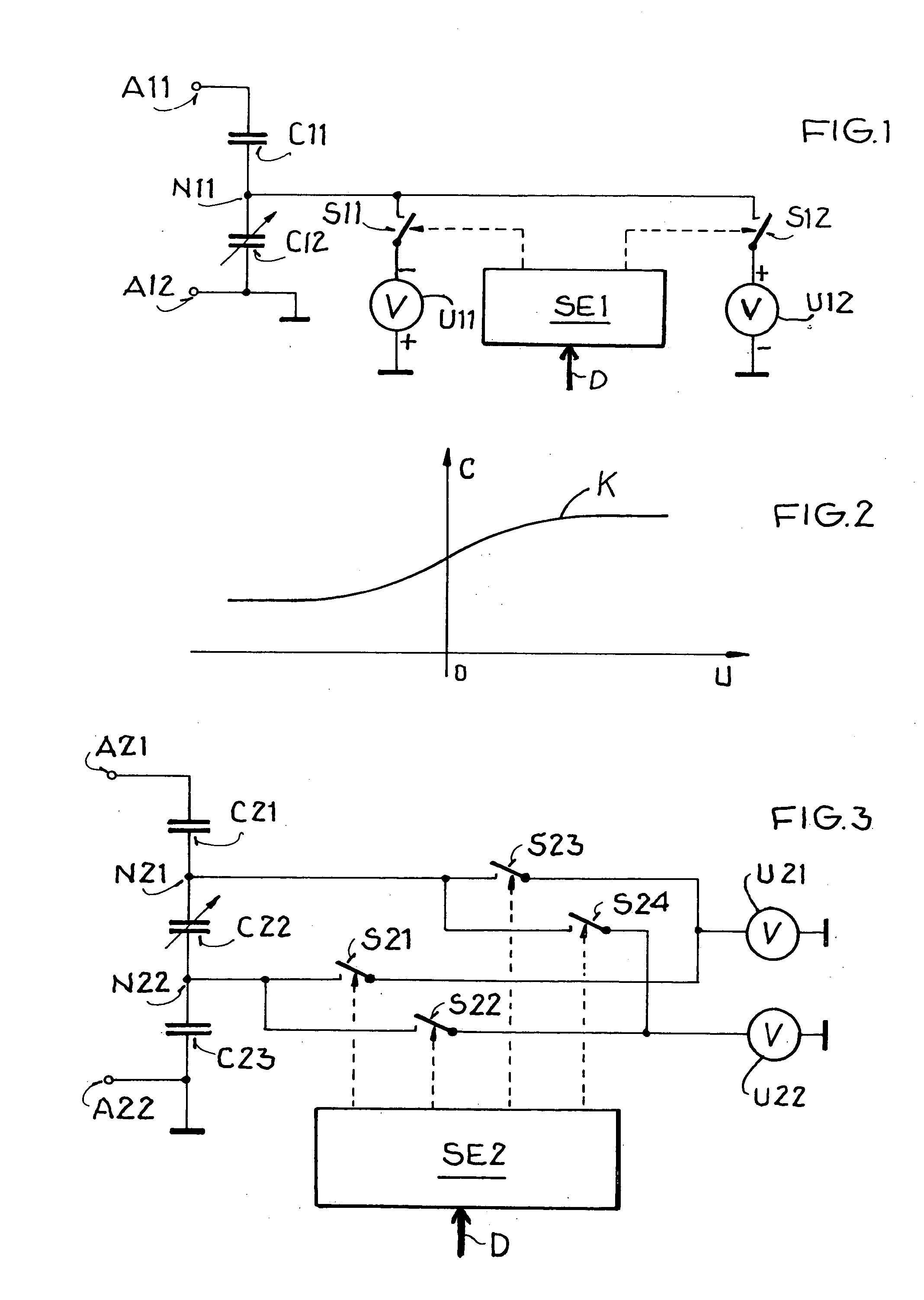

Circuit arrangement and method for phase modulation in a backscattering transponder

ActiveUS20040257220A1More complexMore costlyAngle modulation by variable impedenceFrequency-division multiplex detailsInput impedanceVoltage source

A circuit arrangement for phase modulation in an input circuit of a backscattering transponder includes a varactor and at least one capacitor connected in series between two antenna terminals, and at least two voltage sources selectively connected through at least two switches to at least one terminal of the varactor. A control unit selectively opens and closes the switches in response to the data to be phase-modulated onto the backscattered signal. By selectively connecting the different voltage values of the respective voltage sources to the varactor terminal(s) through the switches, the capacitance of the varactor and correspondingly the input impedance of the input circuit are thereby varied, so as to provide respective different phase positions of the phase modulation.

Owner:ATMEL CORP +1

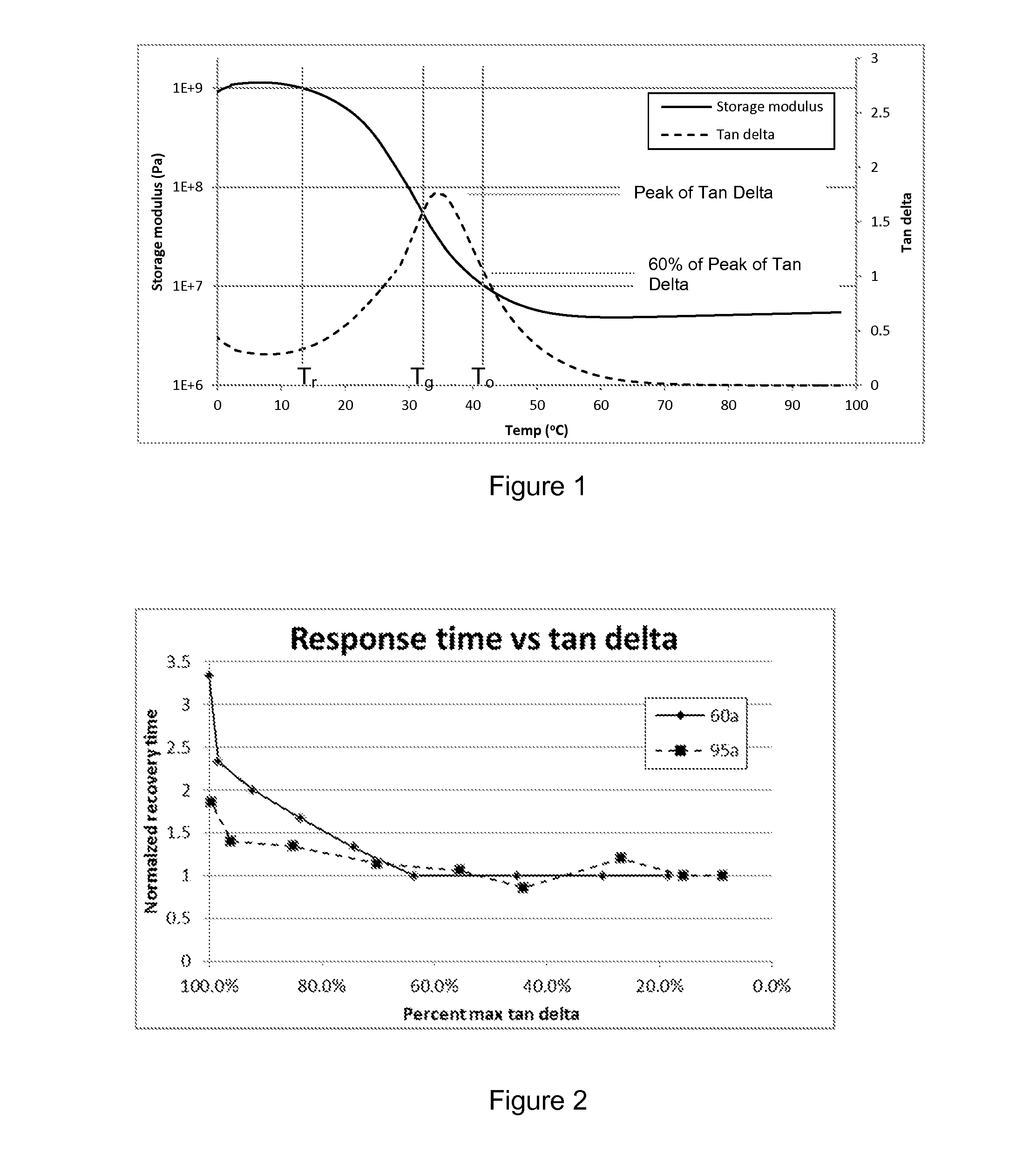

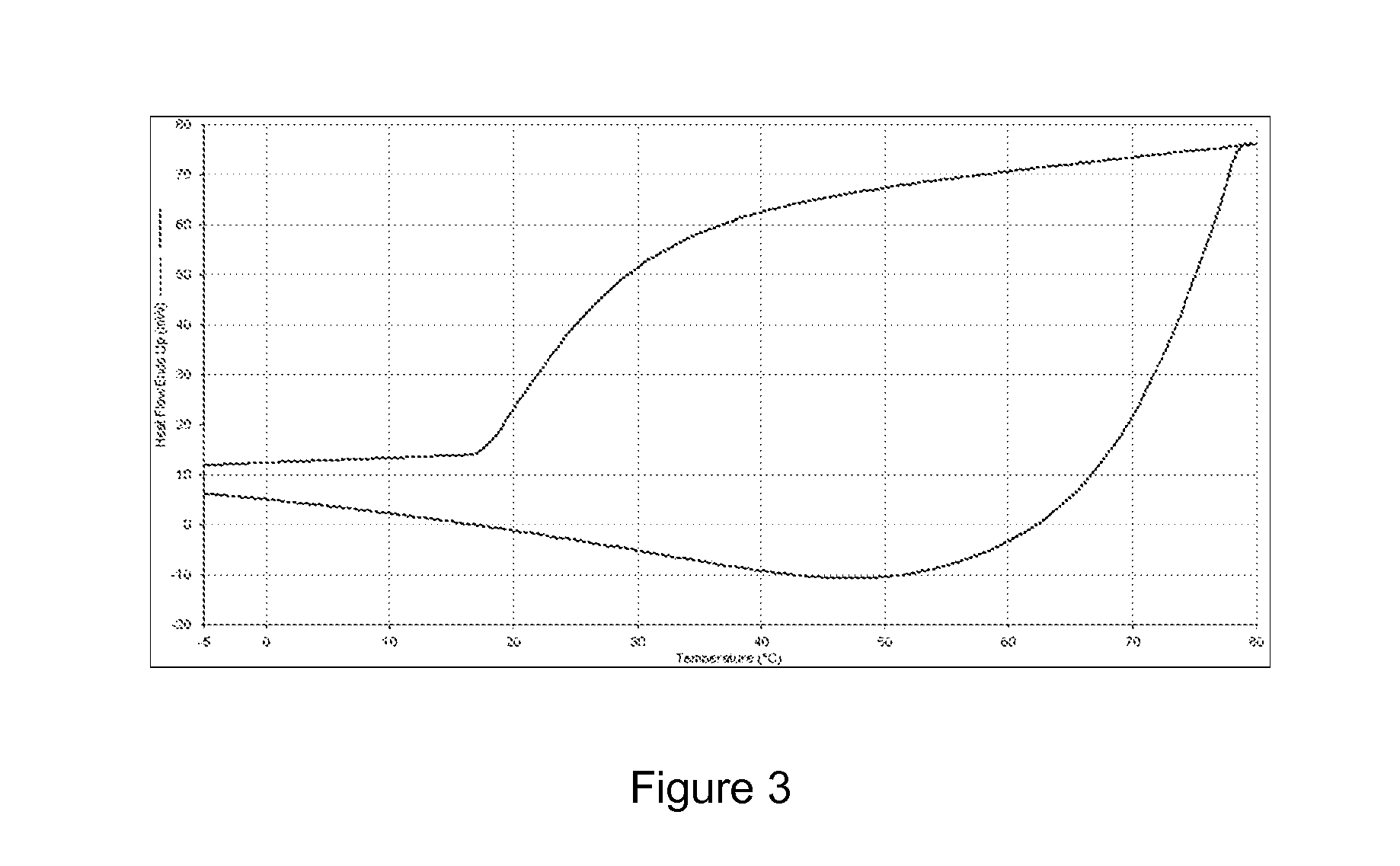

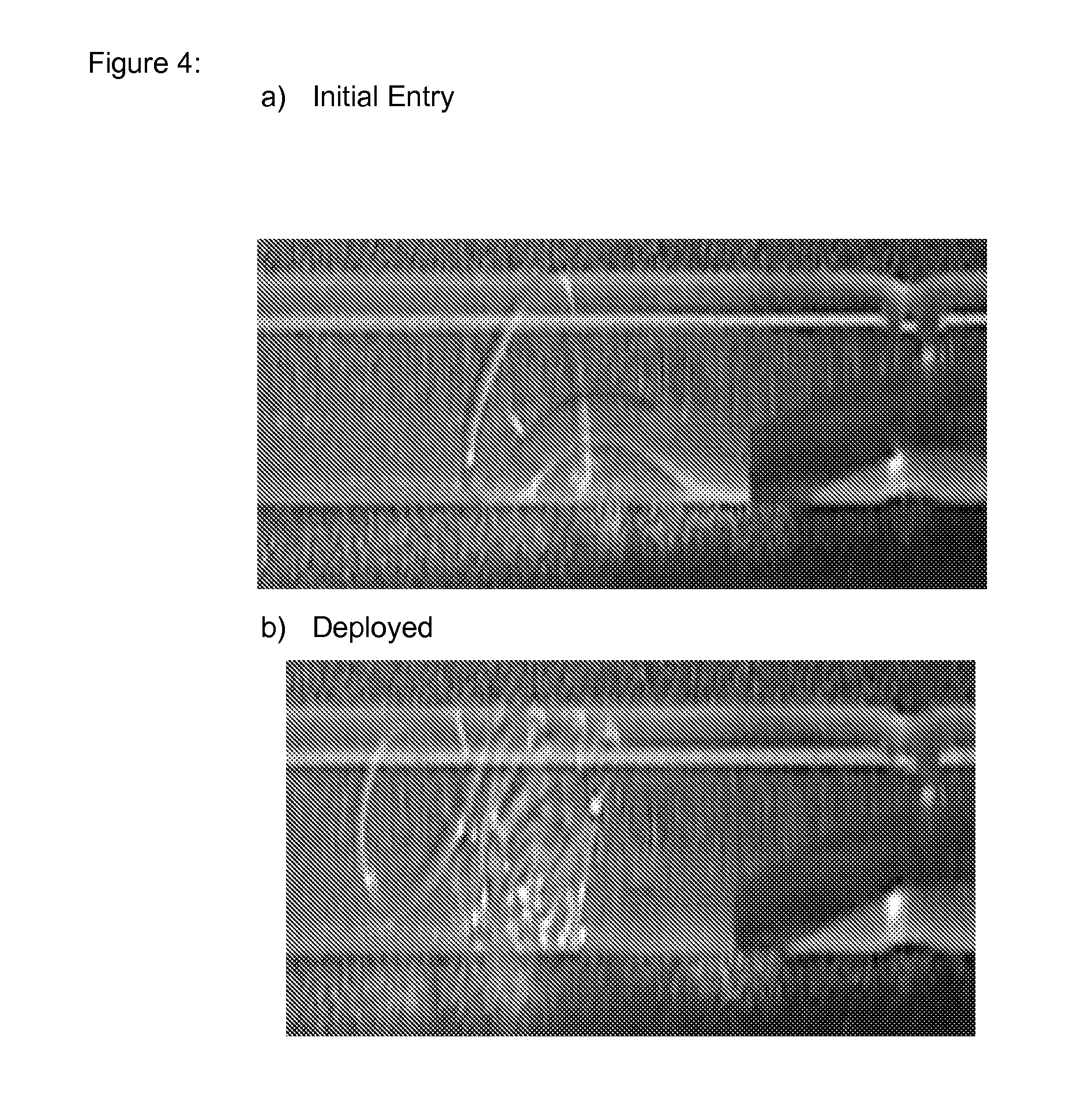

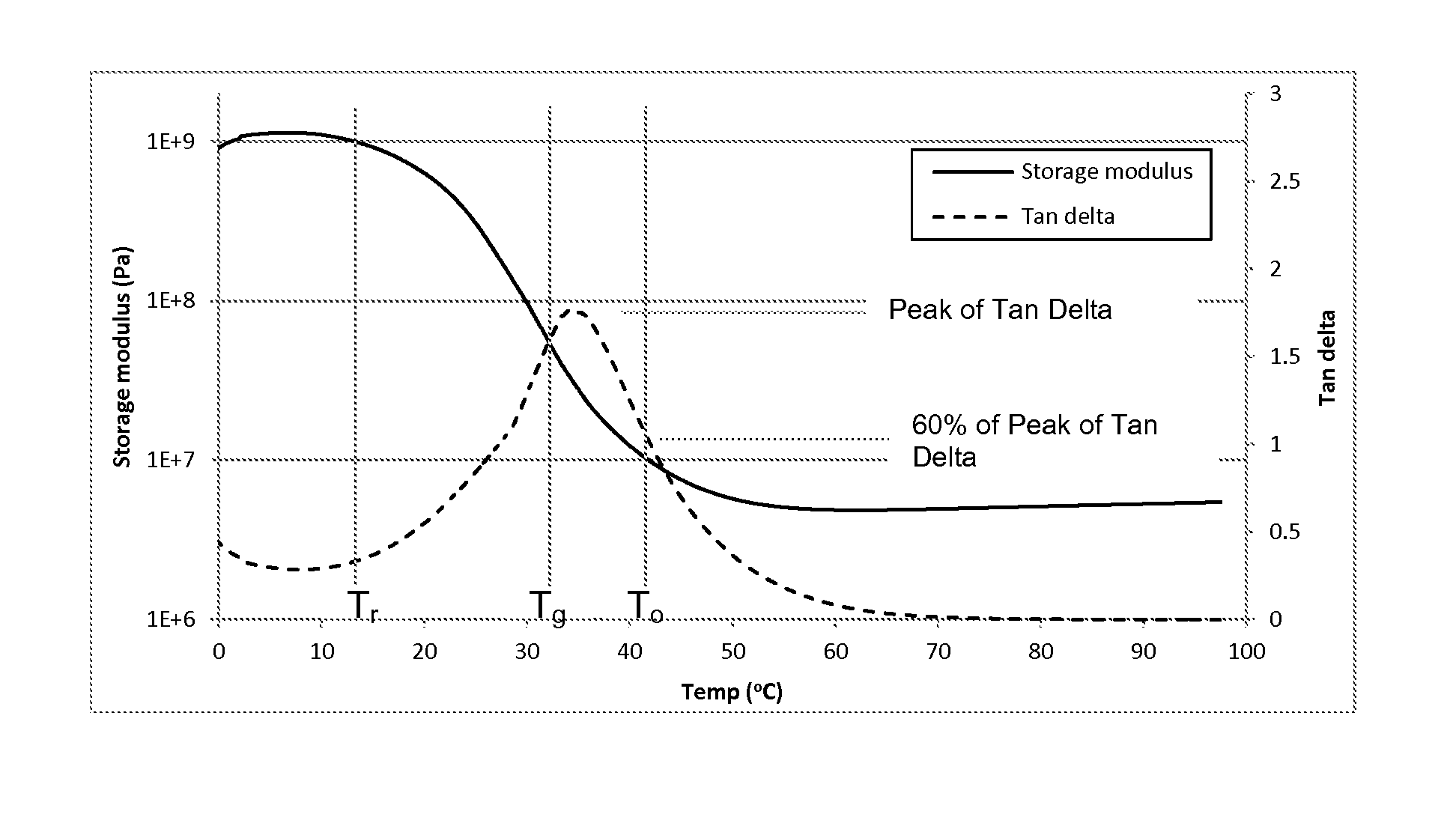

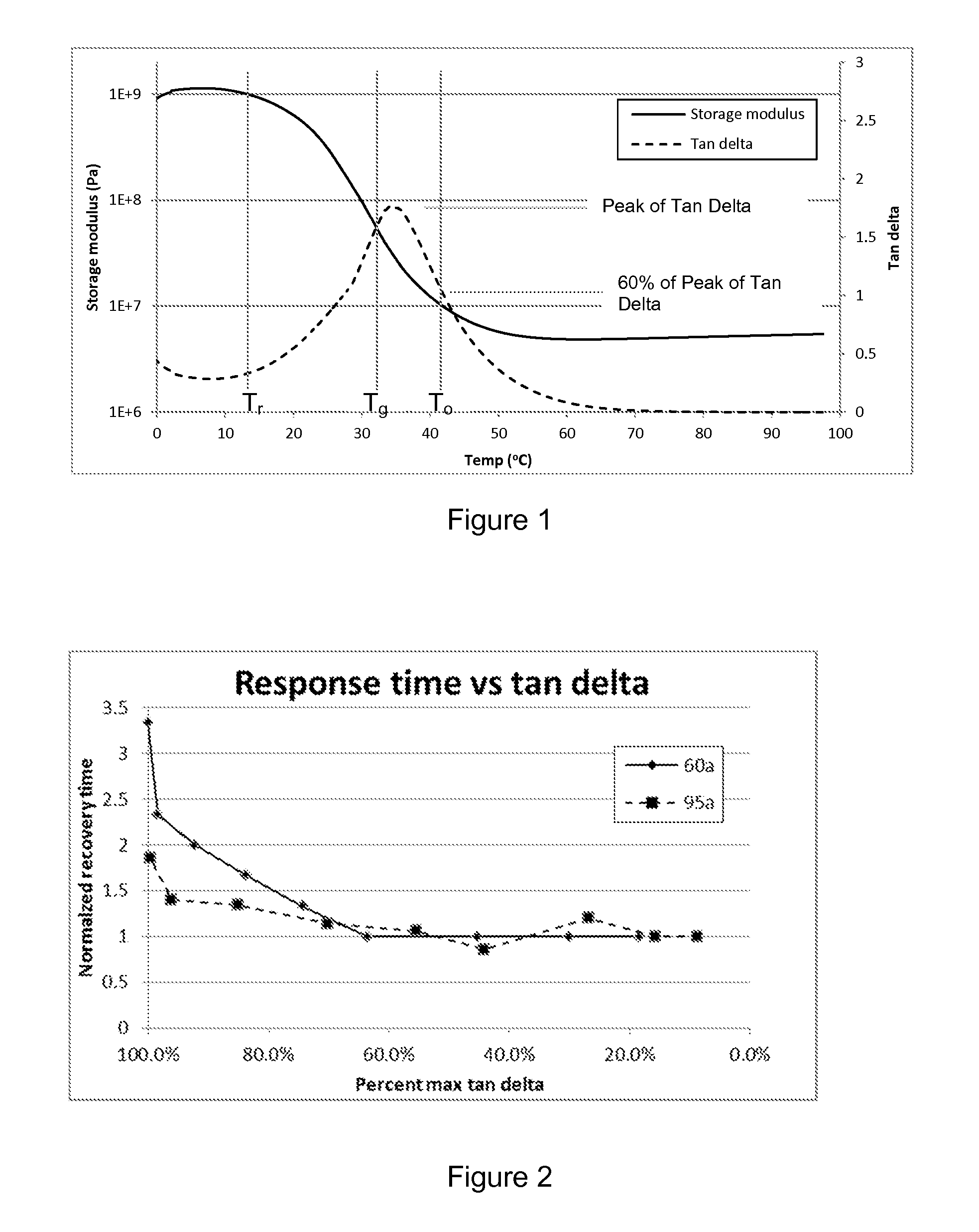

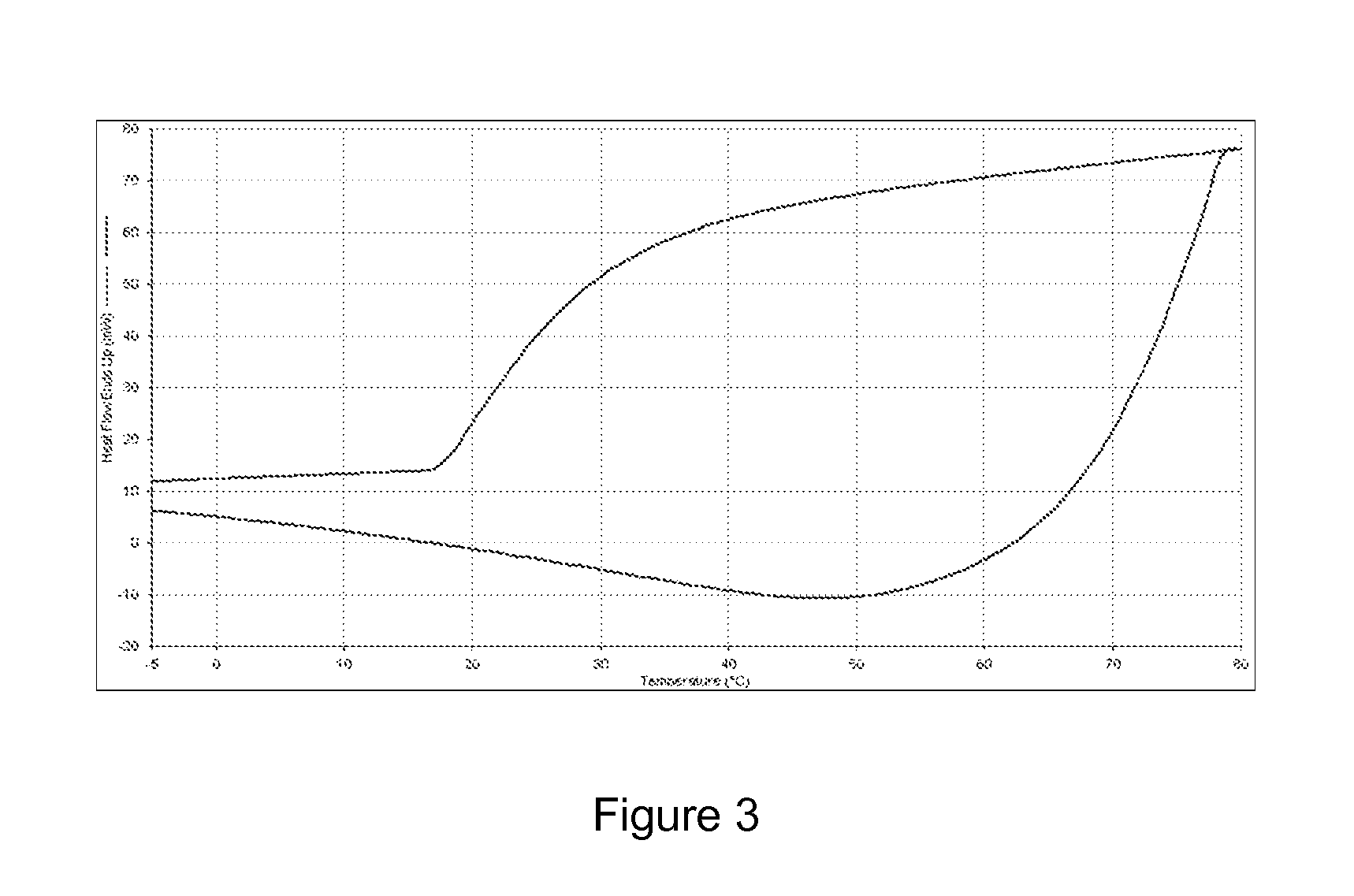

Radiopaque shape memory polymers for medical devices

InactiveUS20130225778A1Inhibit ability to clinically imageMore costlyIn-vivo testing preparationsPolymer scienceDevice form

Radiopaque polymer compositions and methods for making the compositions are provided. These radiopaque polymer compositions include shape memory polymer compositions comprising a crosslinked polymer network, the network comprising a first repeating unit derived from a monofunctional iodinated monomer and a second repeating unit derived from a multifunctional non-iodinated monomer wherein neither of the two monomers is fluorinated. Devices formed from radiopaque polymer compositions are also provided.

Owner:ENDOSHAPE INC

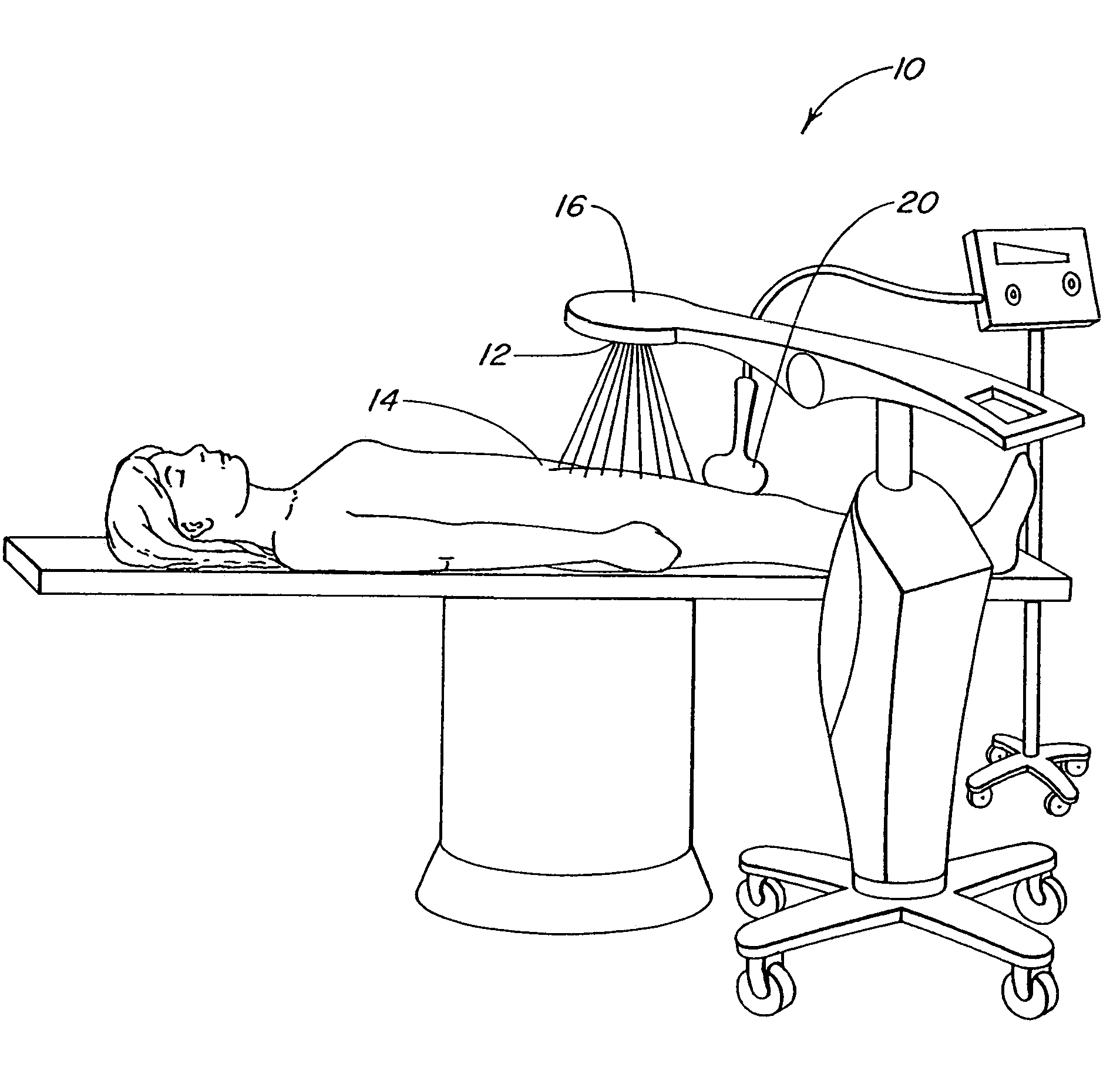

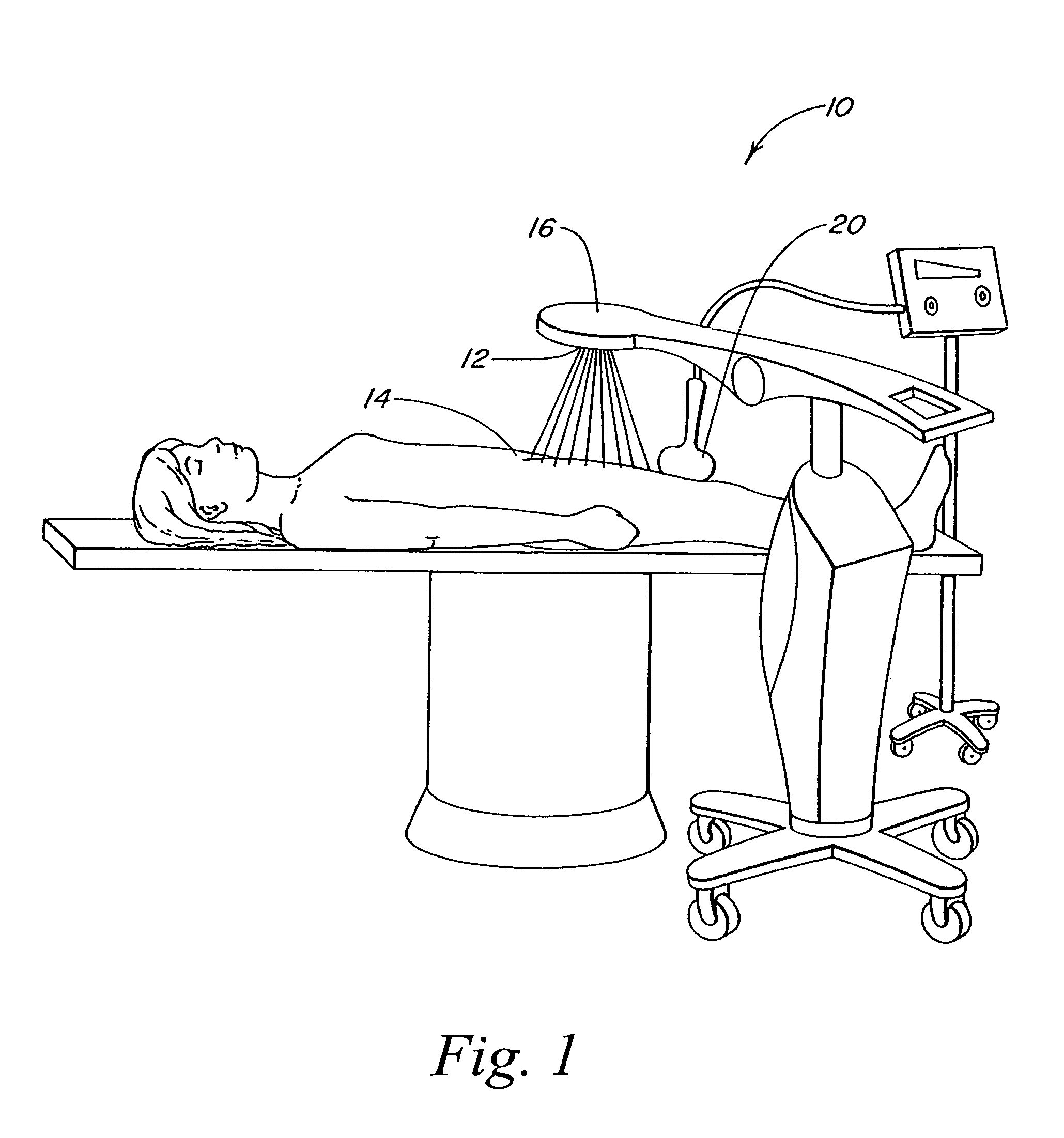

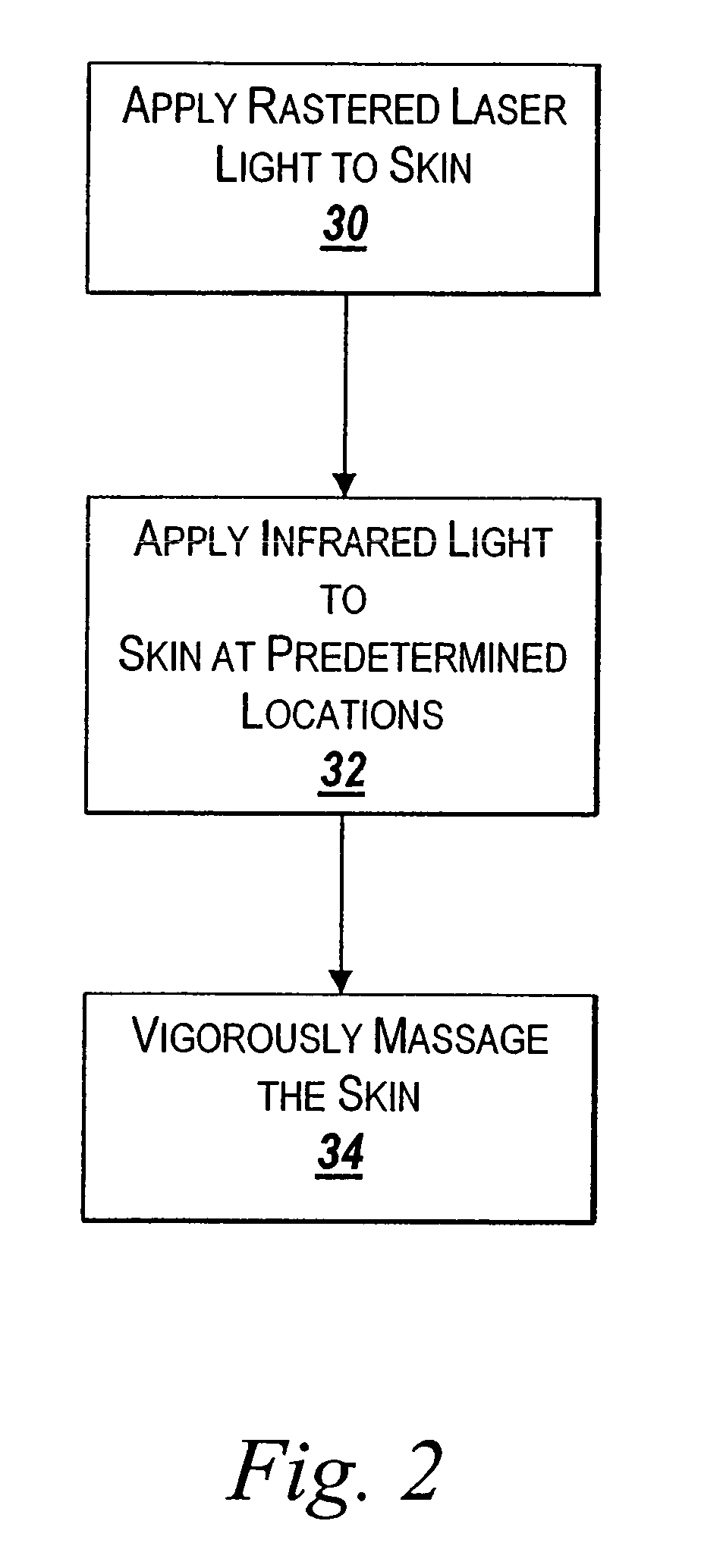

System and method for tissue treatment

InactiveUS7033382B2Lower Level RequirementsIncreased down timeDiagnosticsSurgerySkin surfaceMedicine

A system and method for the treatment of body tissue is provided that includes a radiation-emitting device and a massaging mechanism. In accordance with one embodiment, the radiation-emitting device is a laser and the massaging mechanism is an automated mechanical massaging mechanism. The radiation-emitting device can emit radiation in one or both of the visible and infrared wavelengths. The radiation-emitting device can emit radiation in a concentric combination of infrared and visible laser light. The method of using the tissue treatment system includes exposing a skin surface of a patient to radiation emitted from the radiation-emitting device at predetermined wavelengths for predetermined periods of time. The method further provides for massaging the exposed skin surface of the patient with the massaging mechanism. The tissue treatment system can be utilized to effect the reduction of excess cellulite.

Owner:CYNOSURE

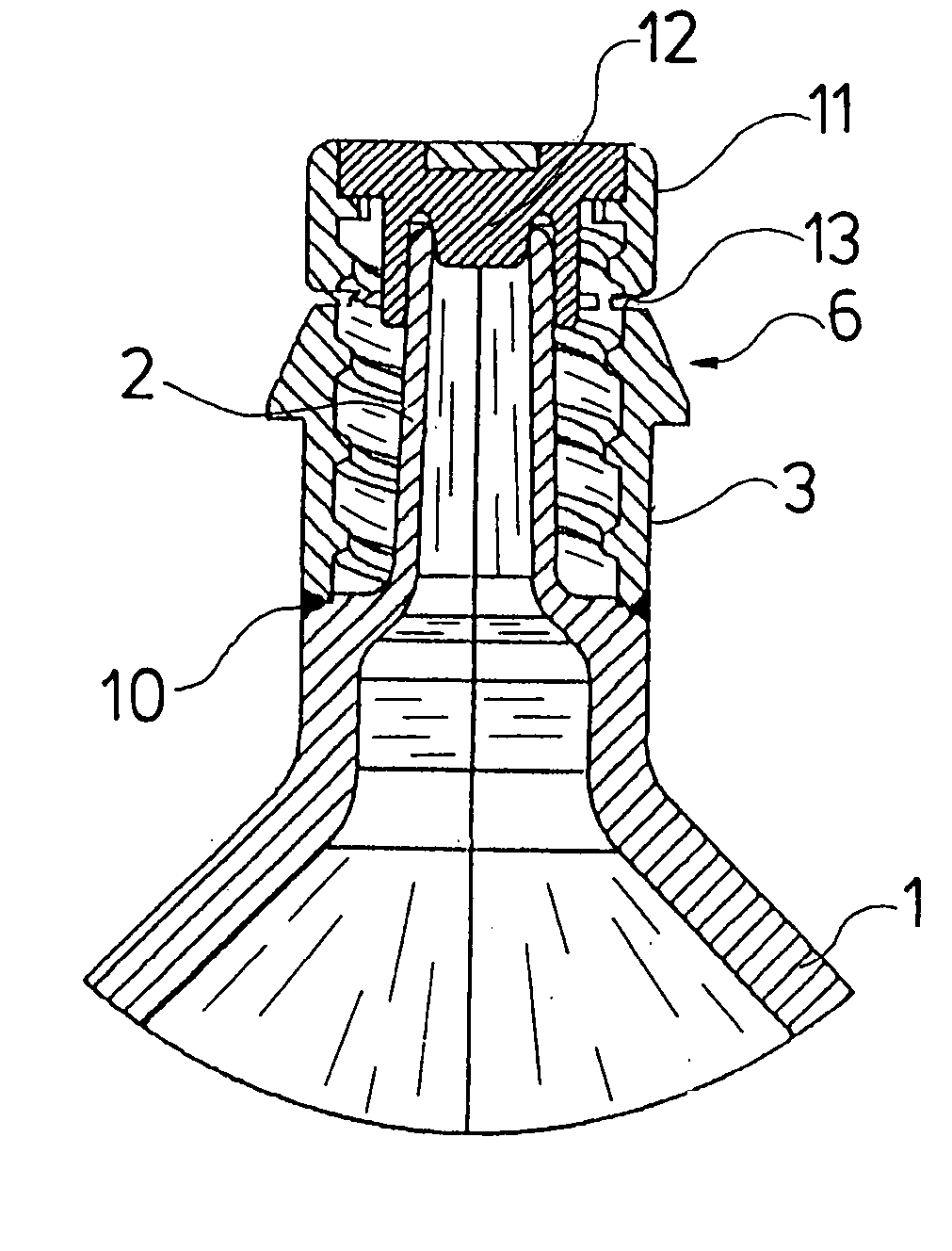

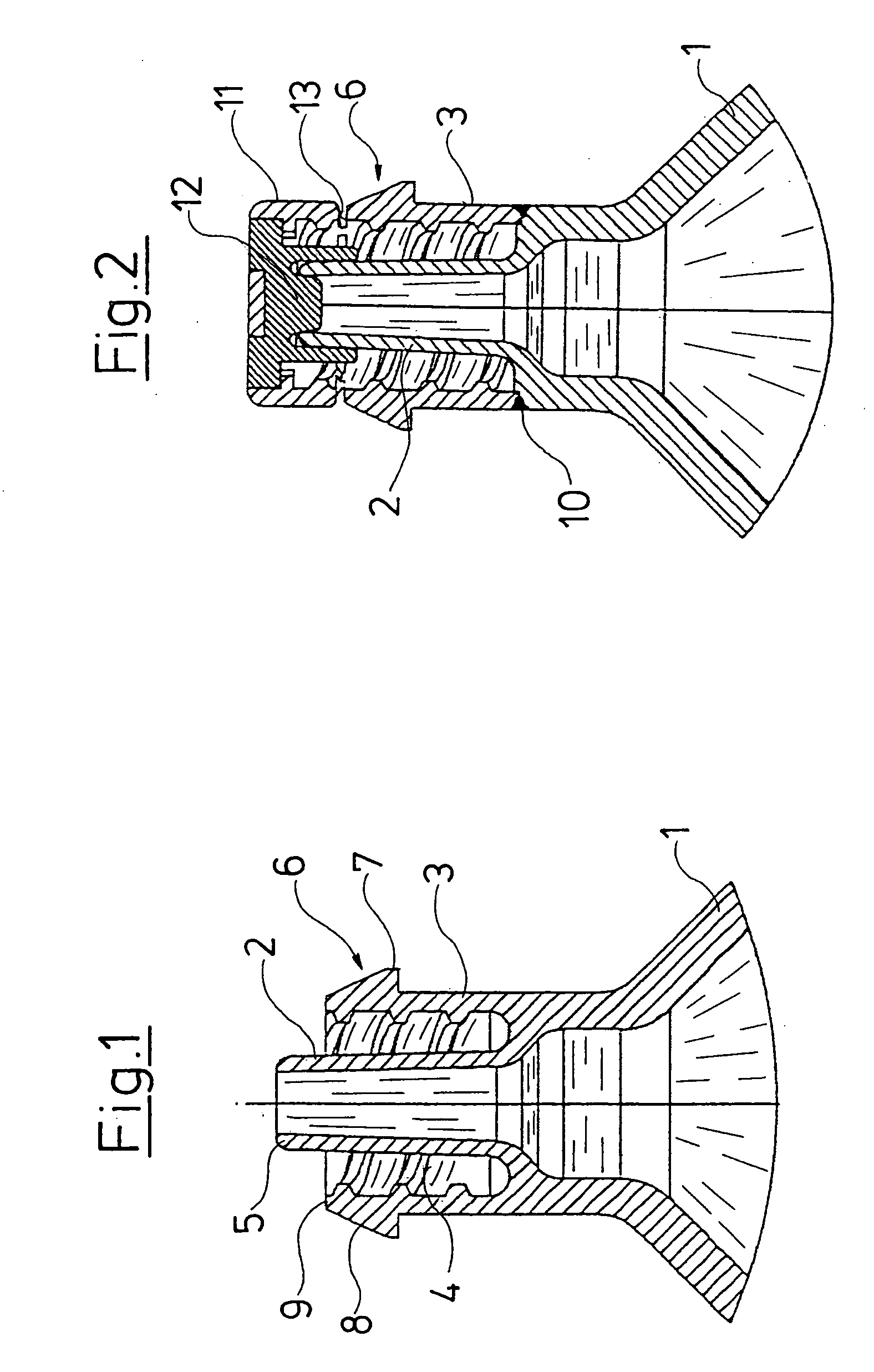

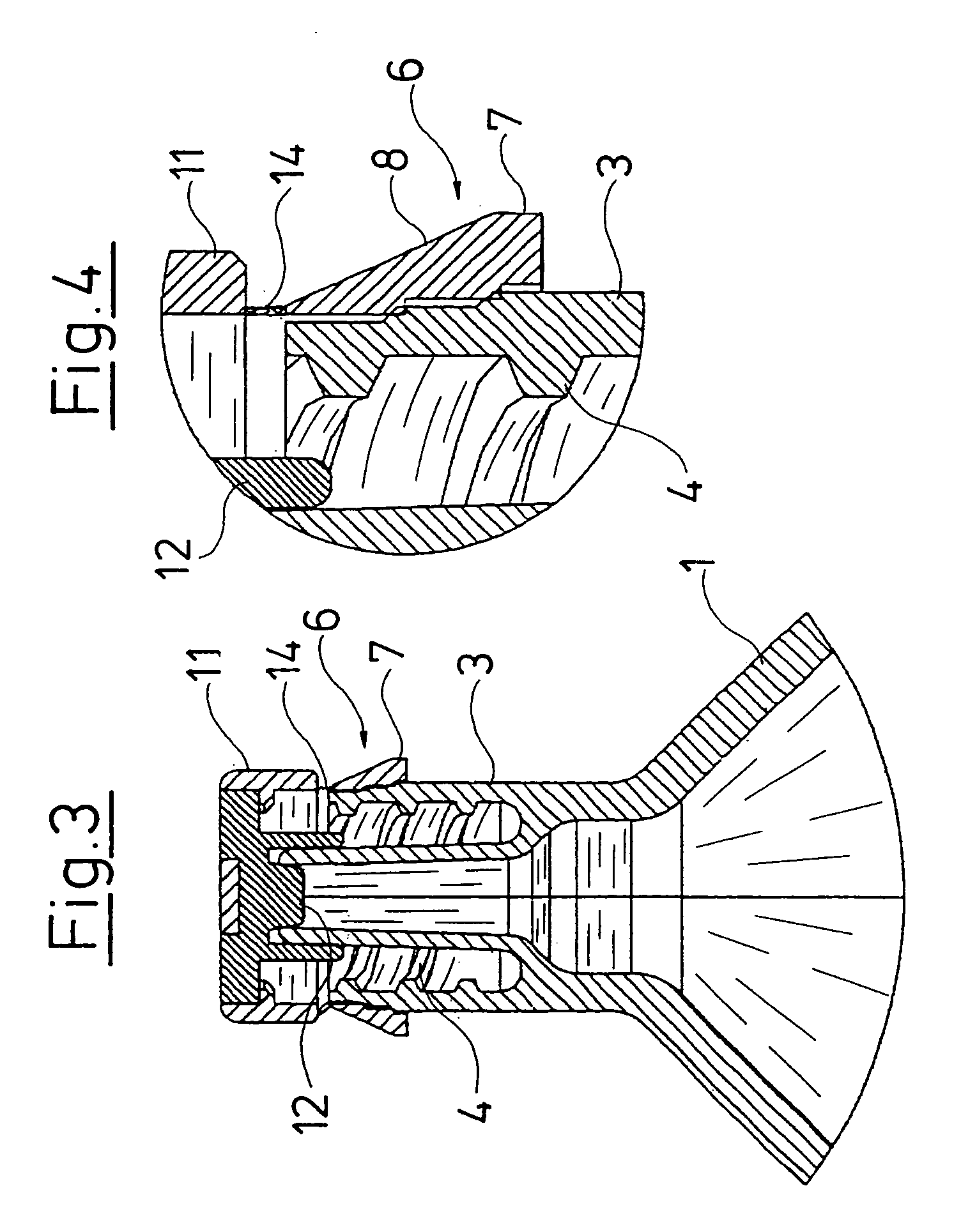

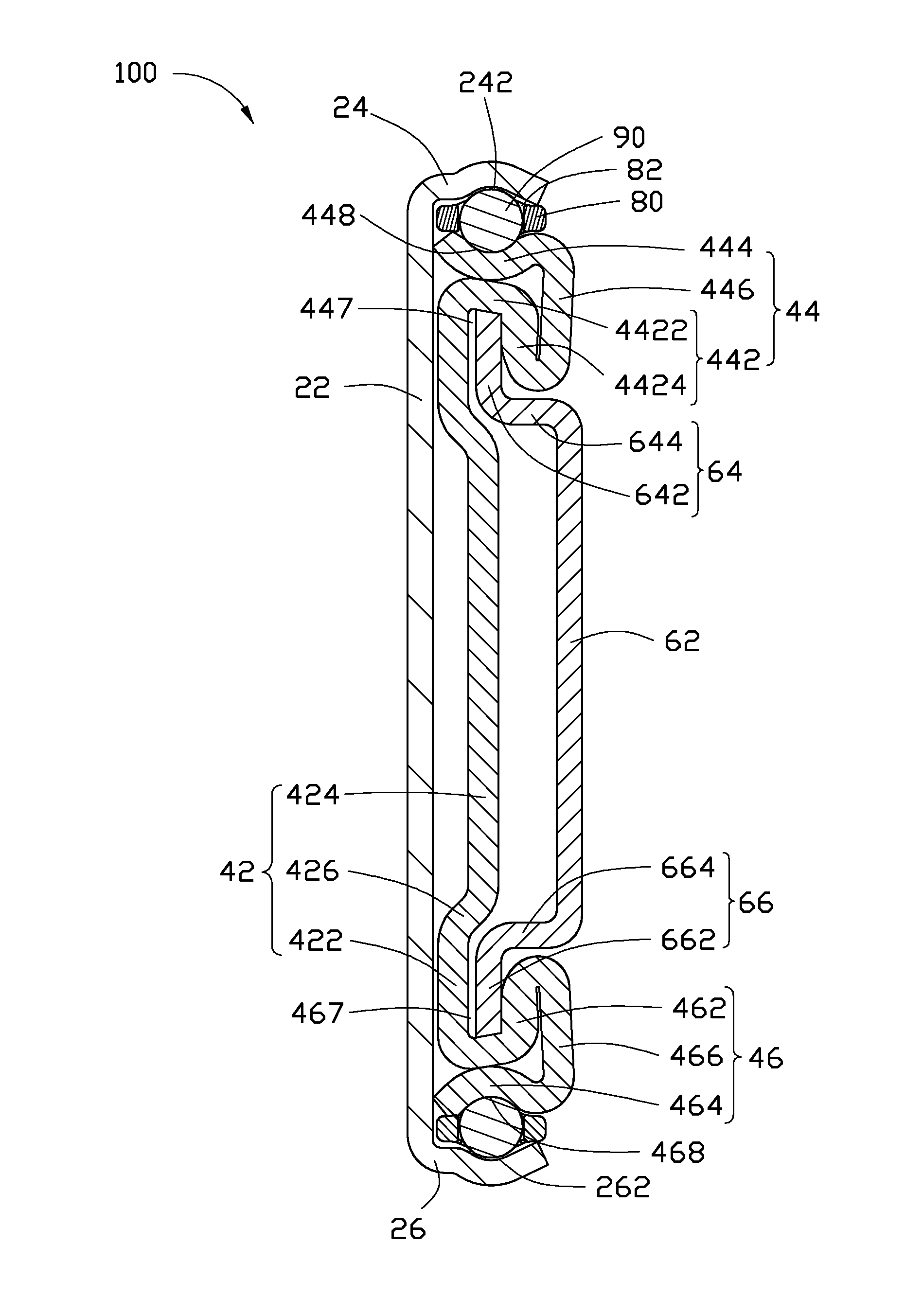

Syringe cylinder

InactiveUS20040133169A1Simplifies sliding-onImprove sealingInfusion syringesTube connectorsSyringePlunger

A syringe cylinder is open to one side for accommodating a plunger and at the other side comprises a syringe connection in the form of a Luer lock connection. The Luer lock connection is formed by a Luer connection and a cylinder section with an inner thread, the cylinder section surrounding the Luer connection. On the outer circumference of the cylinder section there is arranged a ring tapering towards the connection-side end.

Owner:TRANSCOJECT GES FUR MEDIZINISCHE GERATE

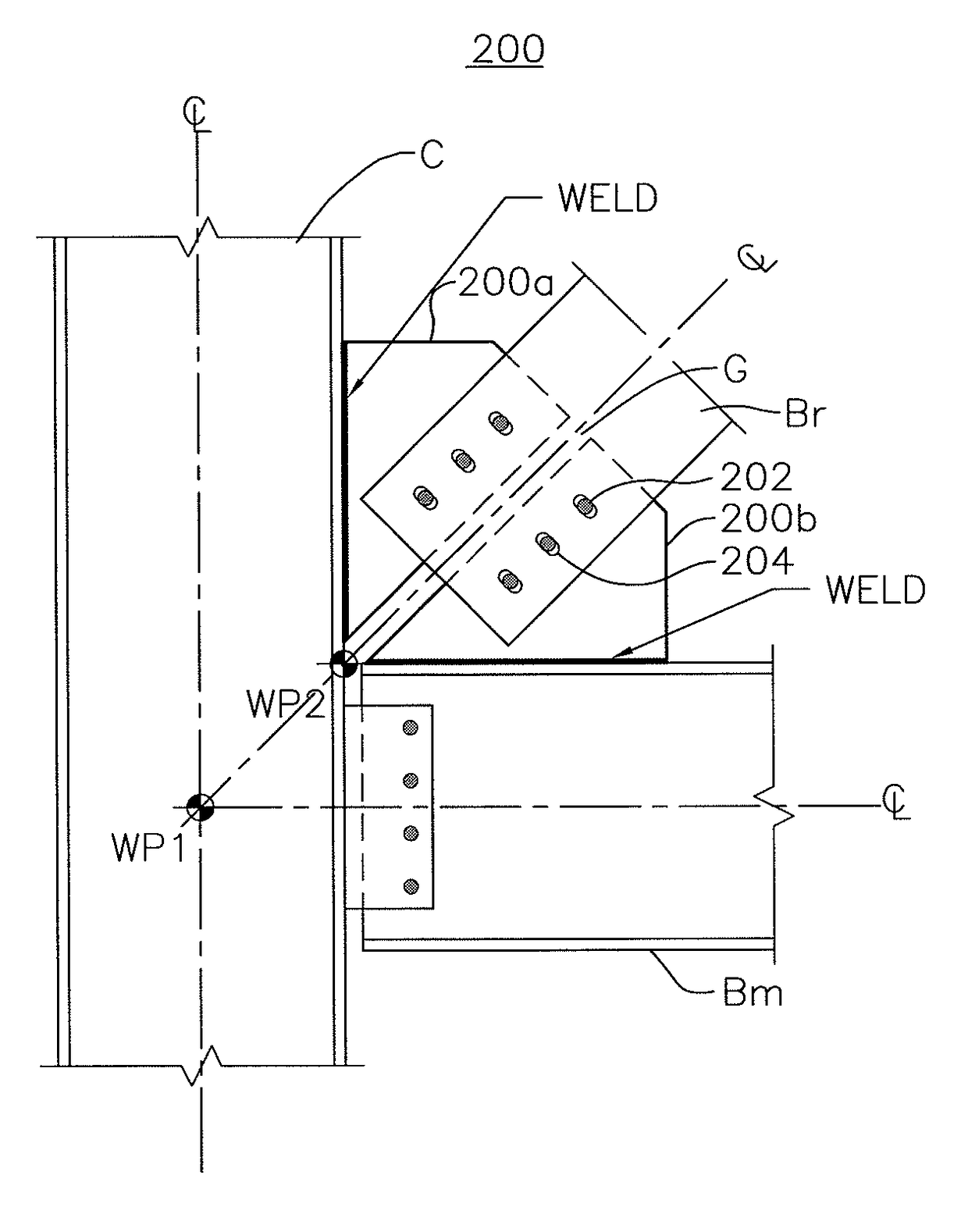

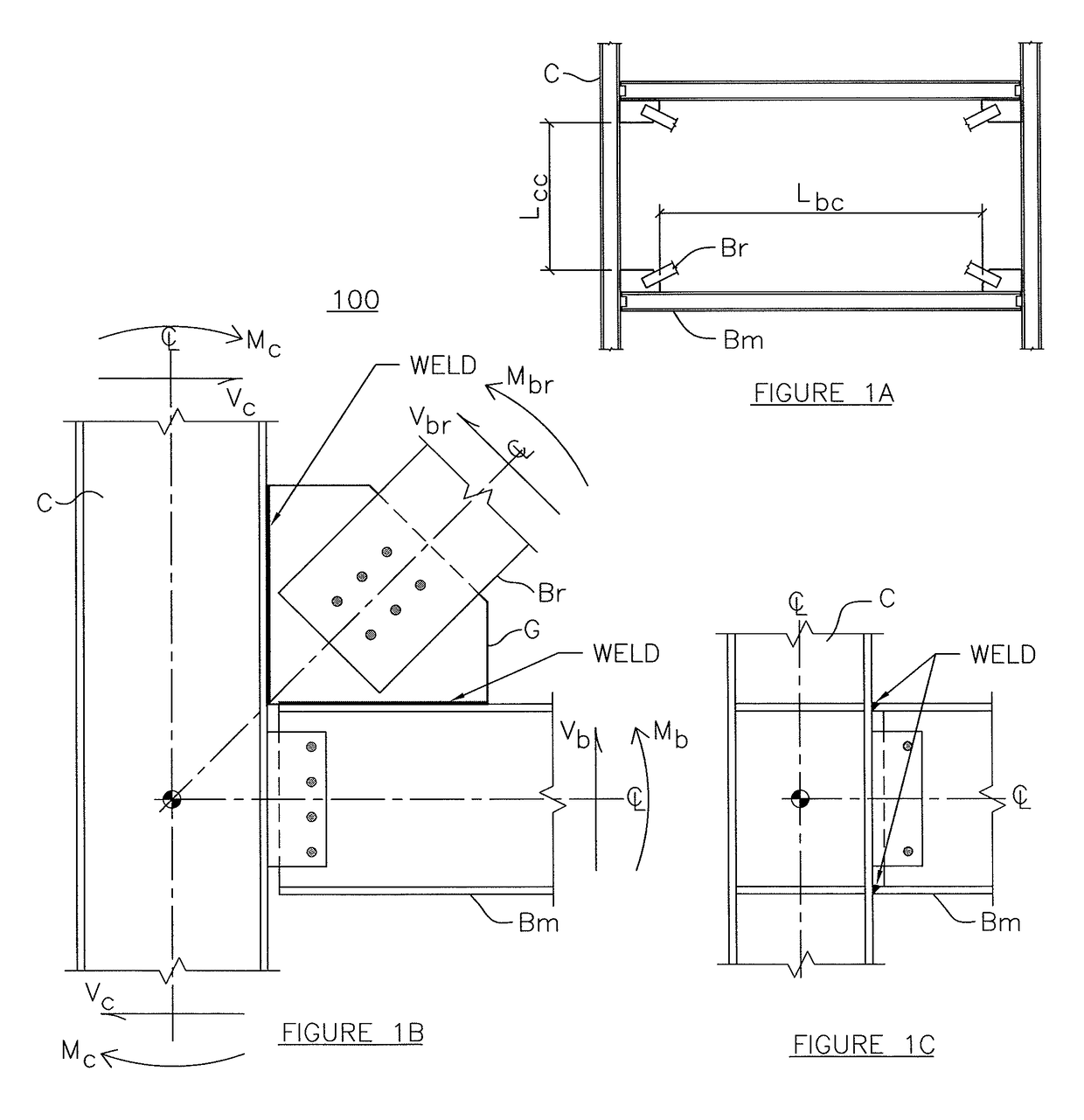

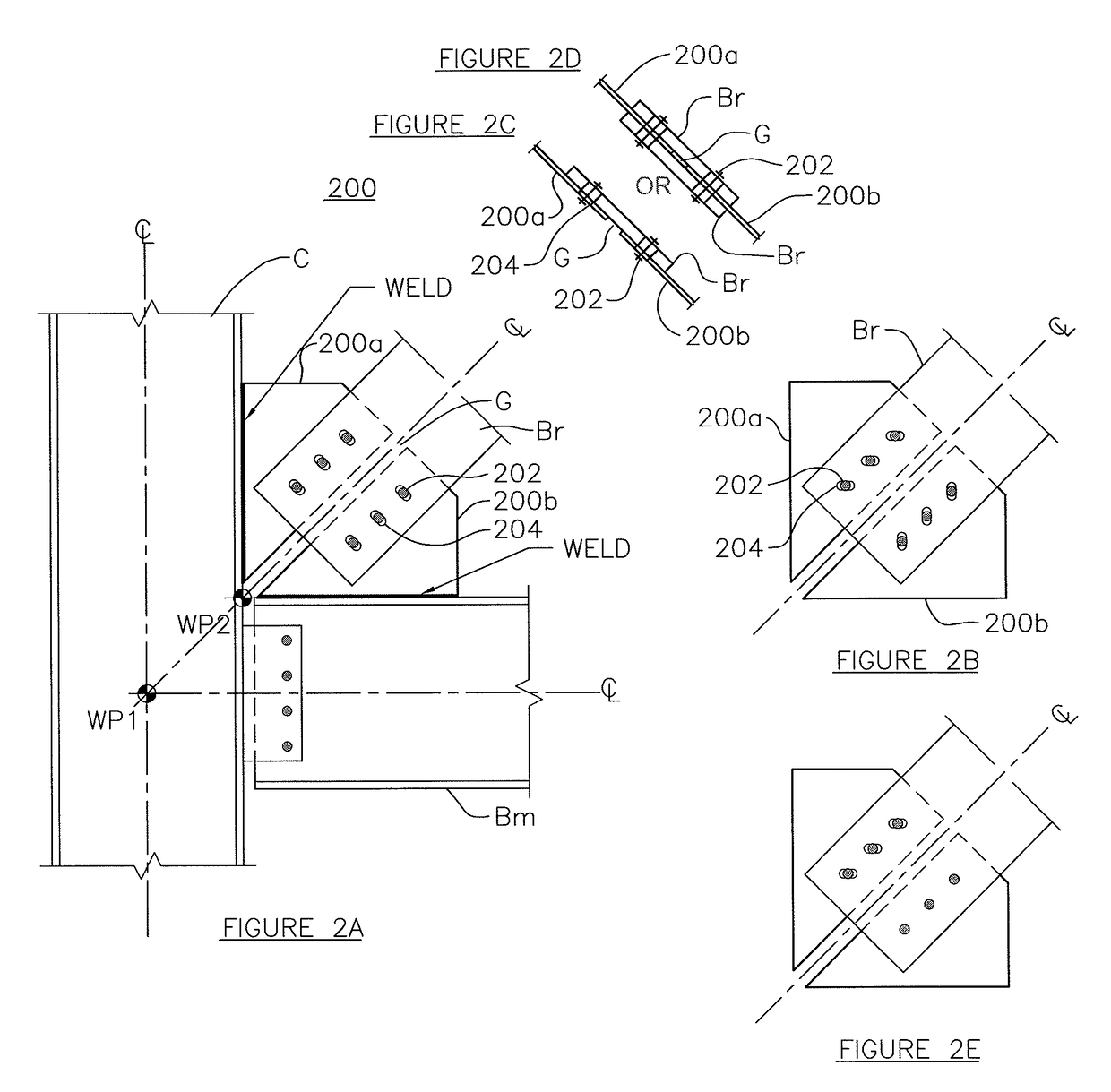

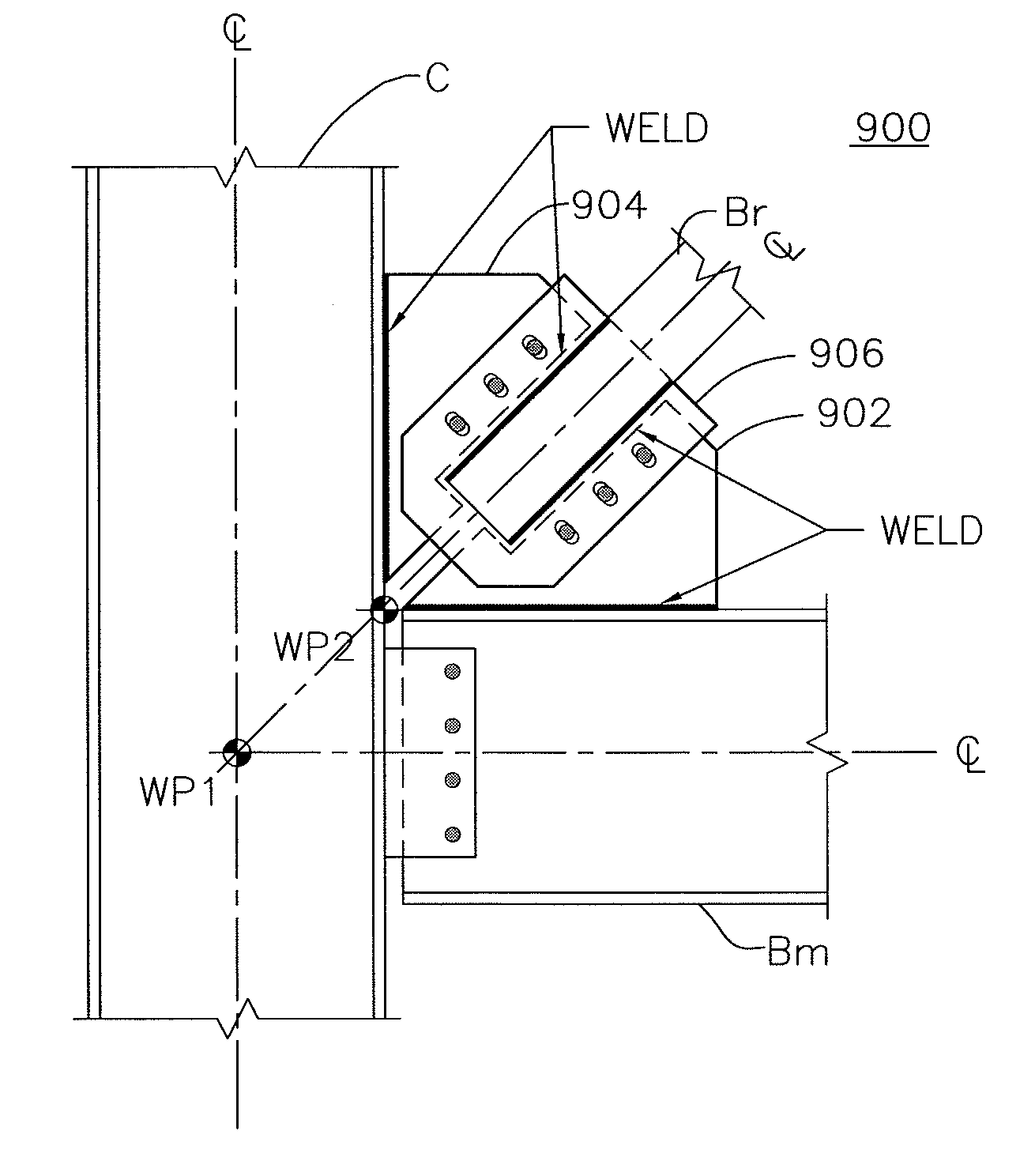

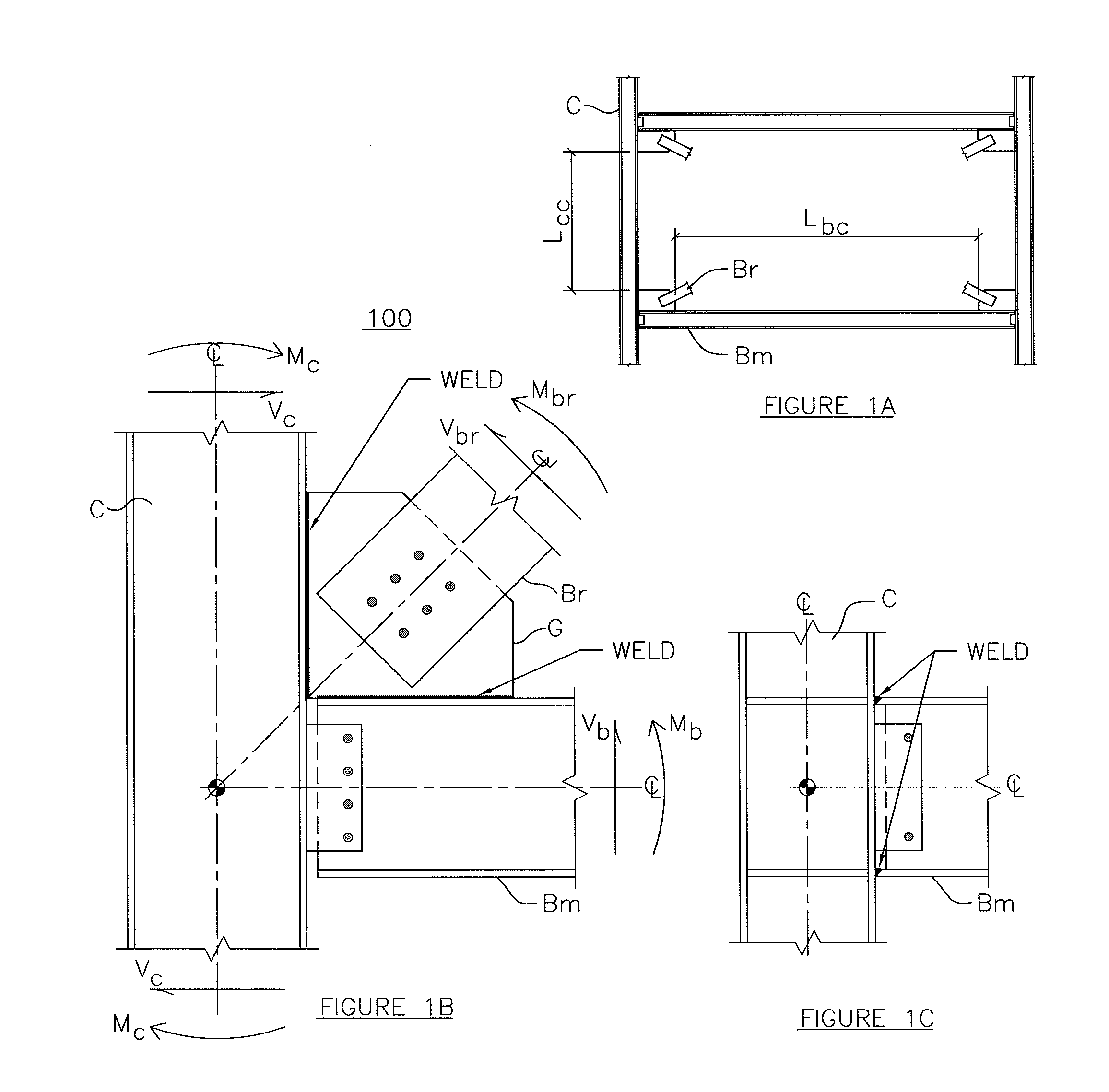

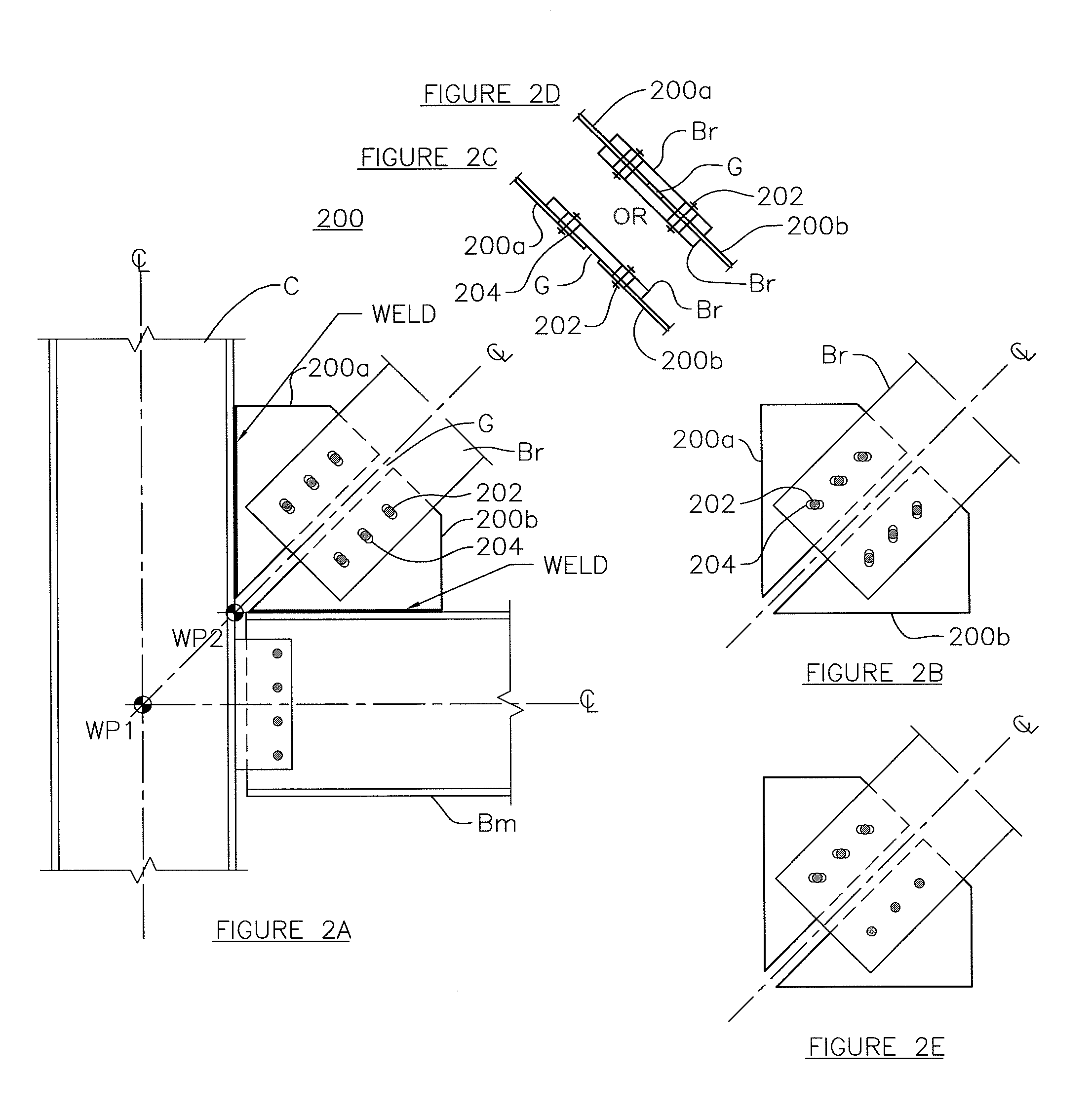

Split gusset connection

ActiveUS9856640B2Less-reliable and accurateAvoid excessive controlGirdersProtective buildings/sheltersEngineeringGreat Relative

A gusset connection that allows greater relative movement between connected structural members and simplifies erection in the field. The gusset connection can be a first gusset portion moveably or fixedly connected to a vertical column and a second gusset connection moveably or fixedly connected to a horizontal beam. A diagonal brace is moveably or fixedly connected to the gusset connection. The first and second gusset portions are not directly connected to each other to allow relative movement between the column, beam, and diagonal brace.

Owner:SHUHAIBAR CONSTANTINE

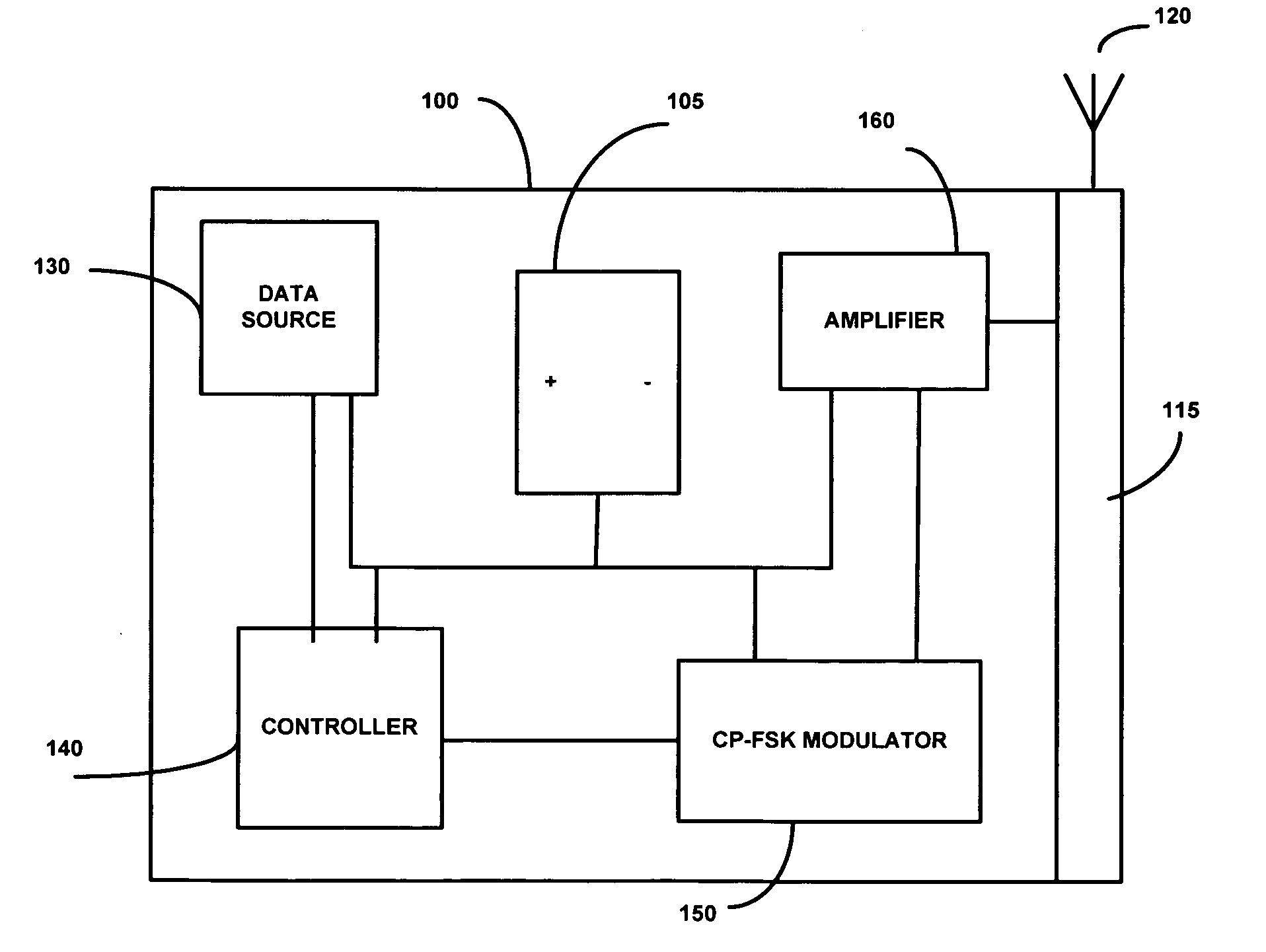

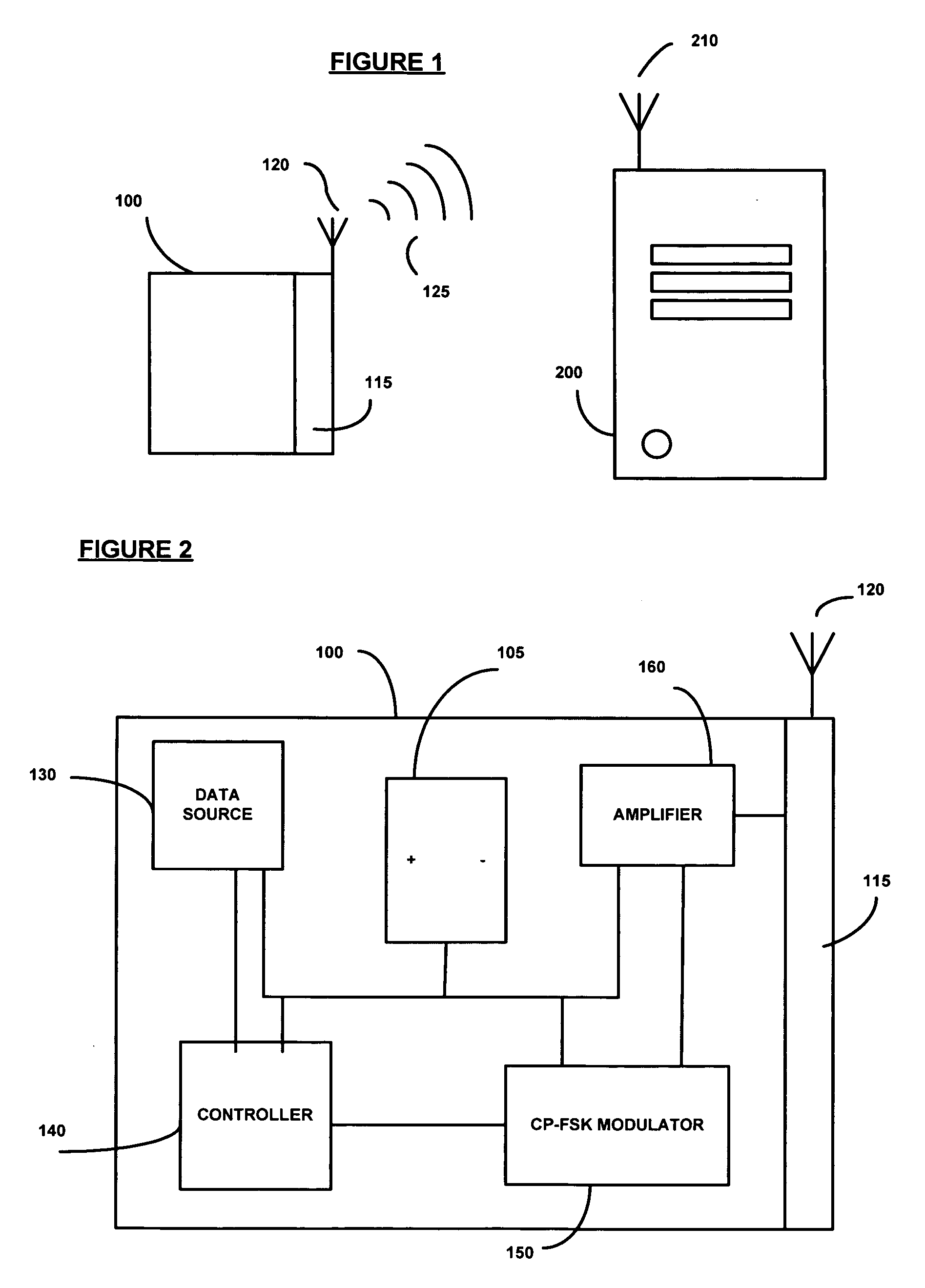

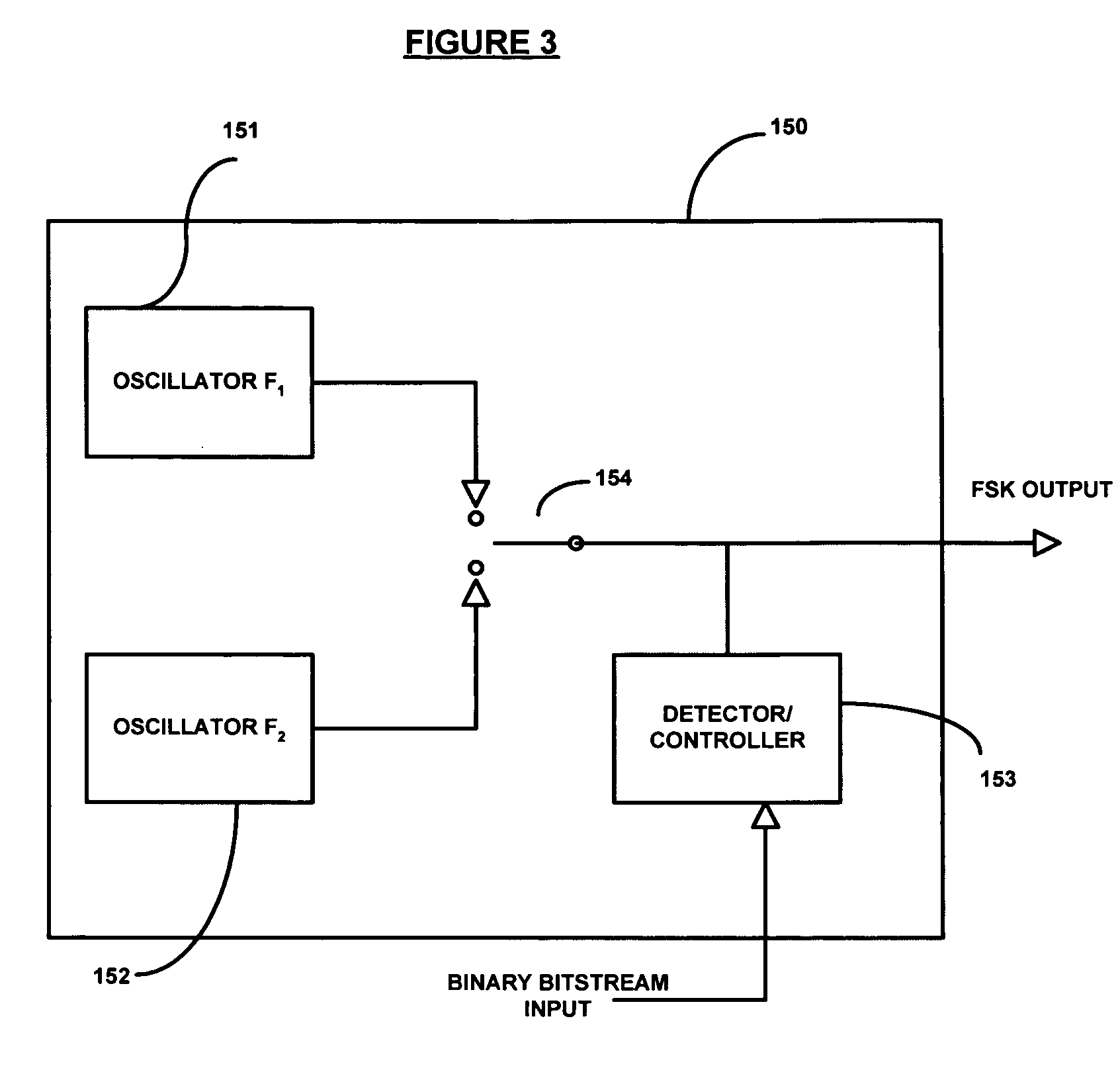

Methods and systems for frequency shift keyed modulation for broadband ultra wideband communication

InactiveUS20050220173A1Reduce power consumptionLow costPhase-modulated carrier systemsUltra-widebandCarrier signal

A system and method for transmitting a UWB or WB signal over a wireless network using a CP-FSK modulated carrier waveform. The system and method comprises selecting a wireless communication channel that is free of at least one of interference and multipath distortion and transmitting a CP-FSK modulated signal over the selected channel having a modulation index of ≦0.707, a bandwidth of at least 500 MHz, a power spectral density of ≦−41.3 dBm / MHz, and a frequency range of 3.1 GHz to 10.6 GHz.

Owner:CONEXANT SYST INC

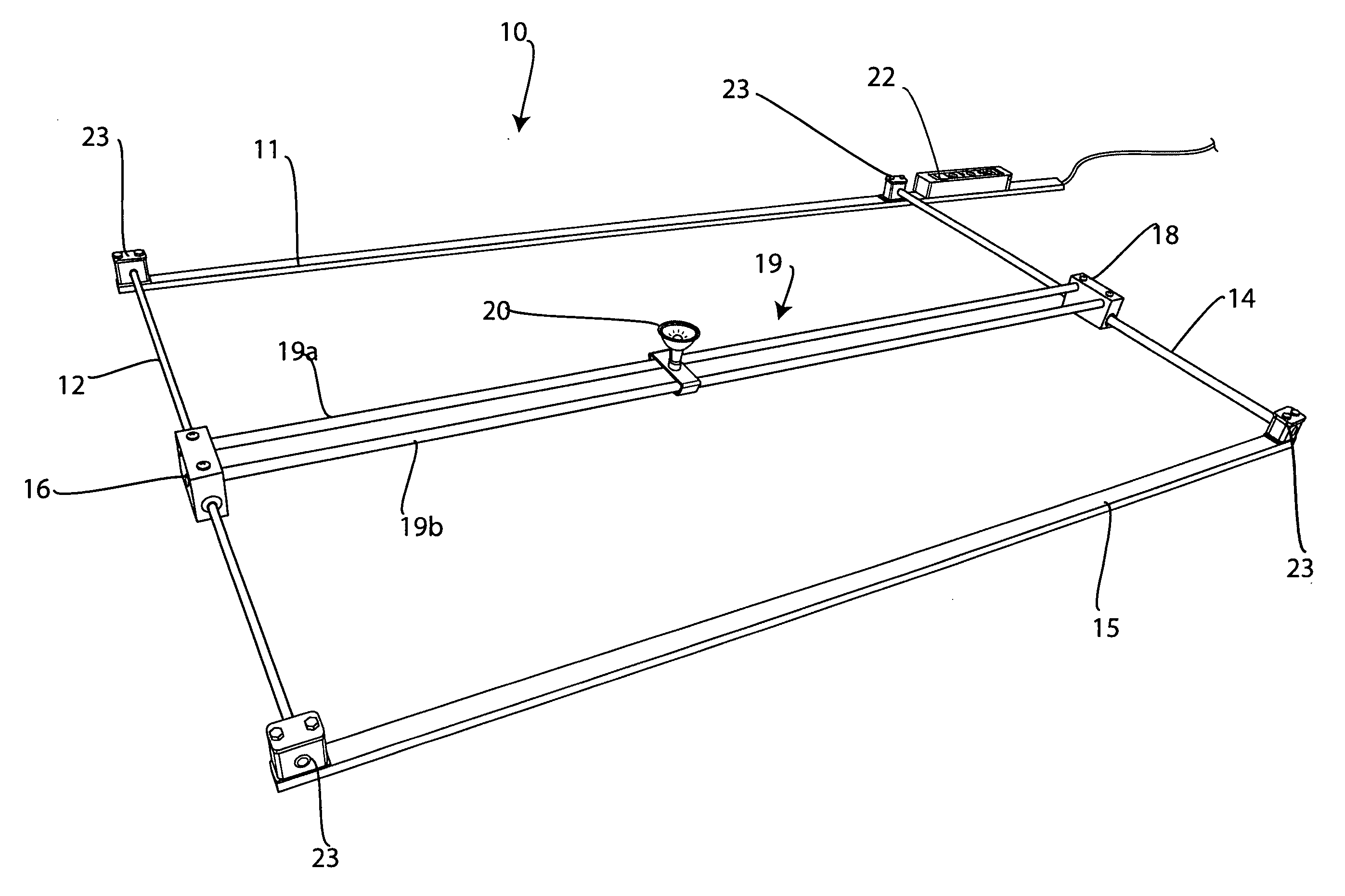

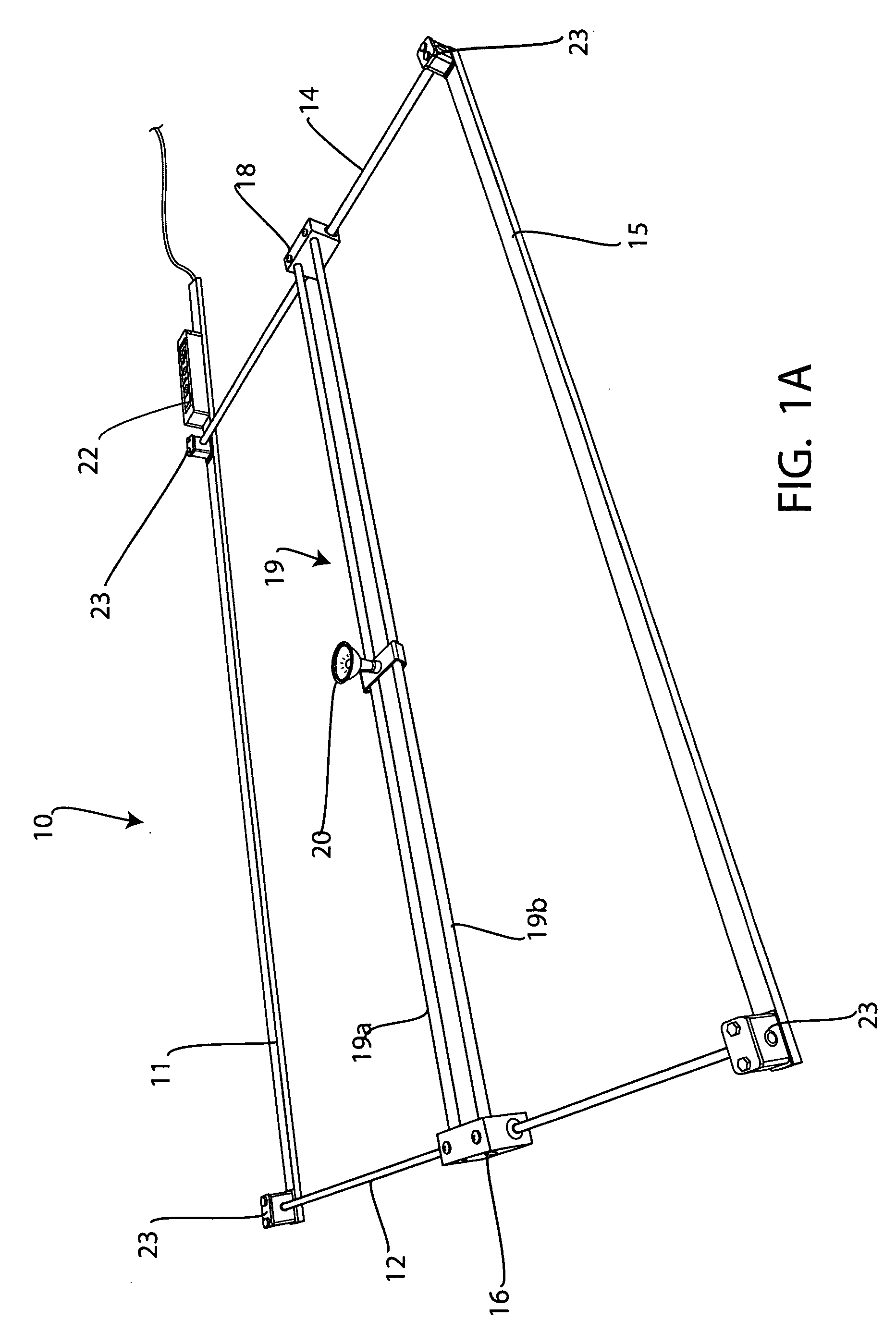

Multi-positional track lighting device

InactiveUS20070002558A1Increased complexityMore costlyCoupling device connectionsLighting support devicesTrack lightingLow voltage

A lighting system that can be a track lighting system that allows lights to move in different directions such as in both a “x” direction and in a “y” direction. This lighting system can include a set of parallel tracks wherein at least one track is also slidable on this set of parallel spaced tracks. On that track is at least one light that can be electrically and mechanically coupled to that track. The device relies on a low voltage system which allows current to flow through the tracks.

Owner:PRYOR JAE WON KIM

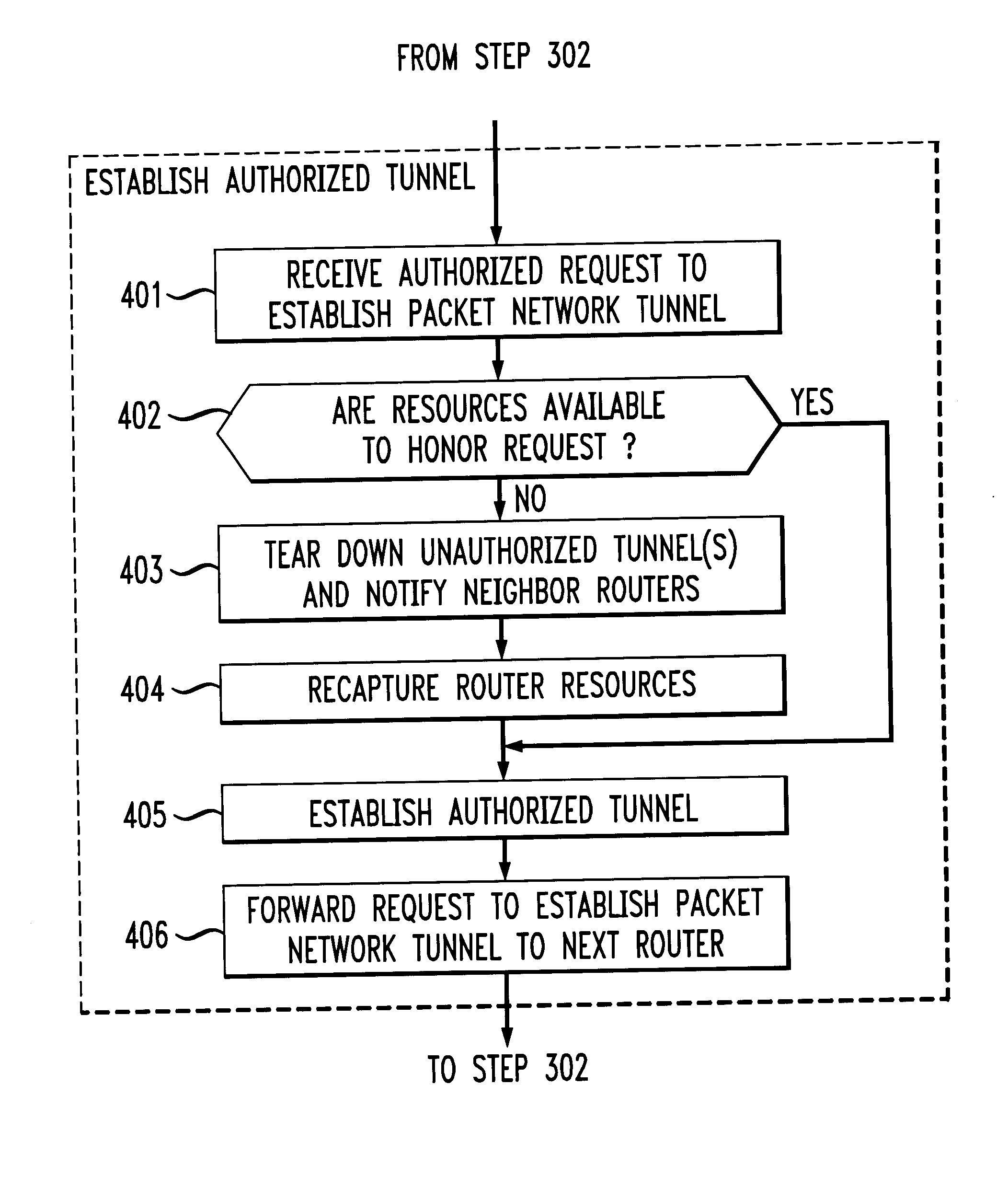

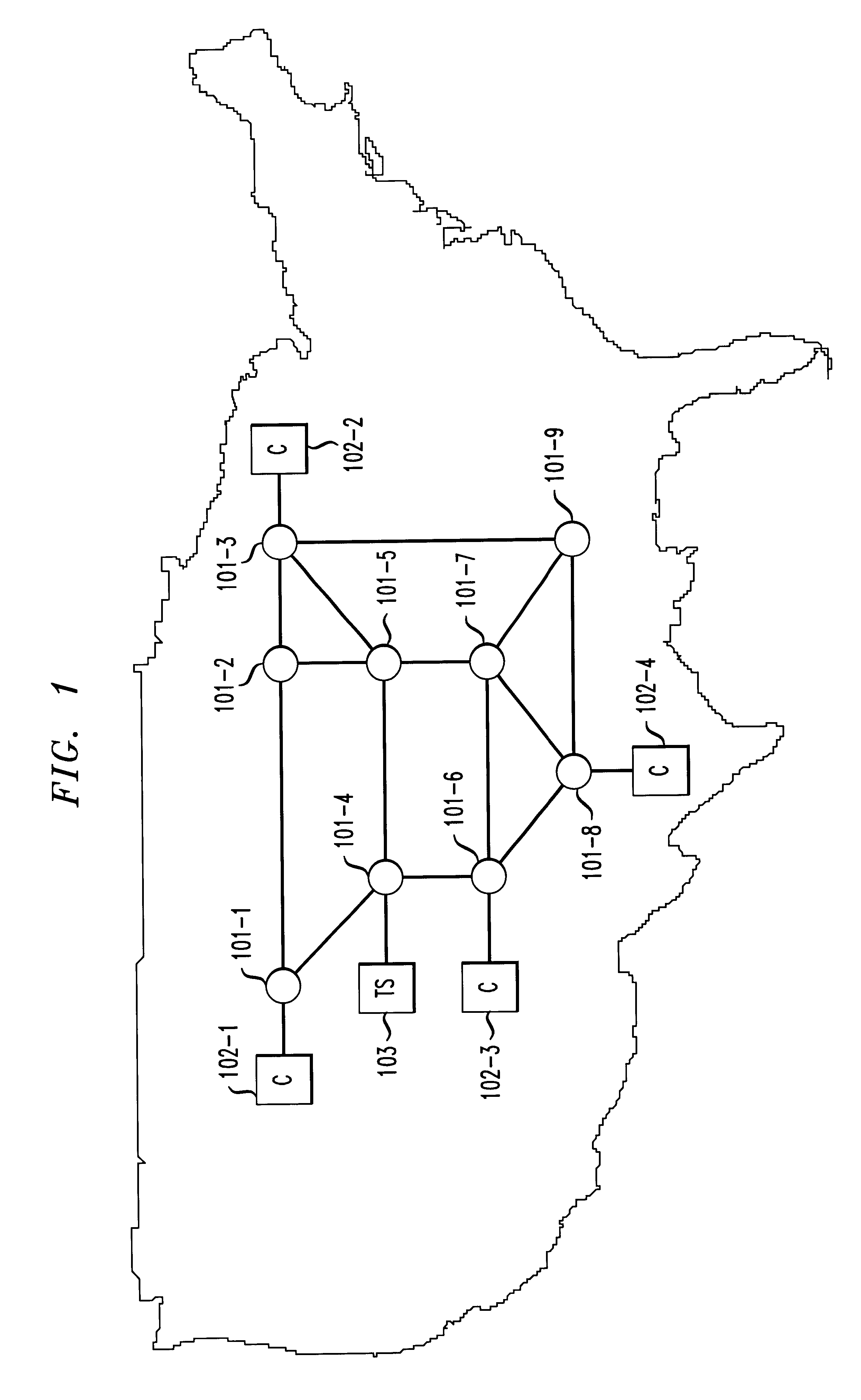

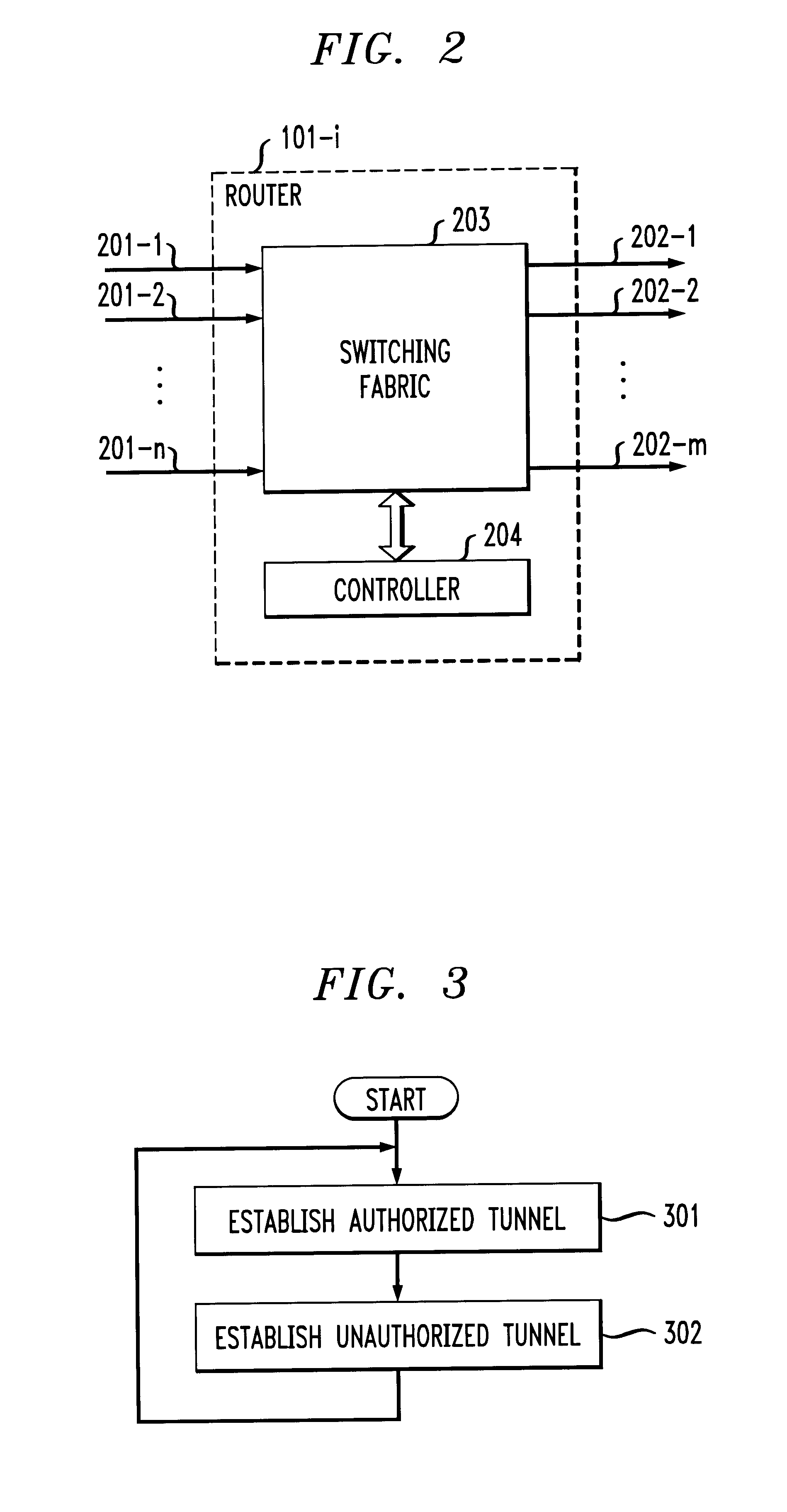

Method and apparatus for packet network tunnel management

InactiveUS6839353B1Addressing failureConsumes network resourceNetworks interconnectionNetwork packetTime sensitive

Systems and techniques for enabling packet networks to carry time-sensitive data in an efficient manner are described. A packet traverses a packet network through the creation of a packet network tunnel. Each router can propose, and establish if possible, a detour tunnel around the failure without the knowledge or consent of a tunnel manager. Establishment and maintenance of packet network tunnels is also prioritized so any packet network tunnel authorized by the tunnel manager has precedence over any packet network tunnel initiated by a router without the authorization of the tunnel manager.

Owner:CIENA +1

Radiopaque shape memory polymers for medical devices

InactiveUS9062141B2Inhibit ability to clinically imageMore costlyX-ray constrast preparationsPolymer scienceDevice form

Radiopaque polymer compositions and methods for making the compositions are provided. These radiopaque polymer compositions include shape memory polymer compositions comprising a crosslinked polymer network, the network comprising a first repeating unit derived from a monofunctional iodinated monomer and a second repeating unit derived from a multifunctional non-iodinated monomer wherein neither of the two monomers is fluorinated. Devices formed from radiopaque polymer compositions are also provided.

Owner:ENDOSHAPE INC

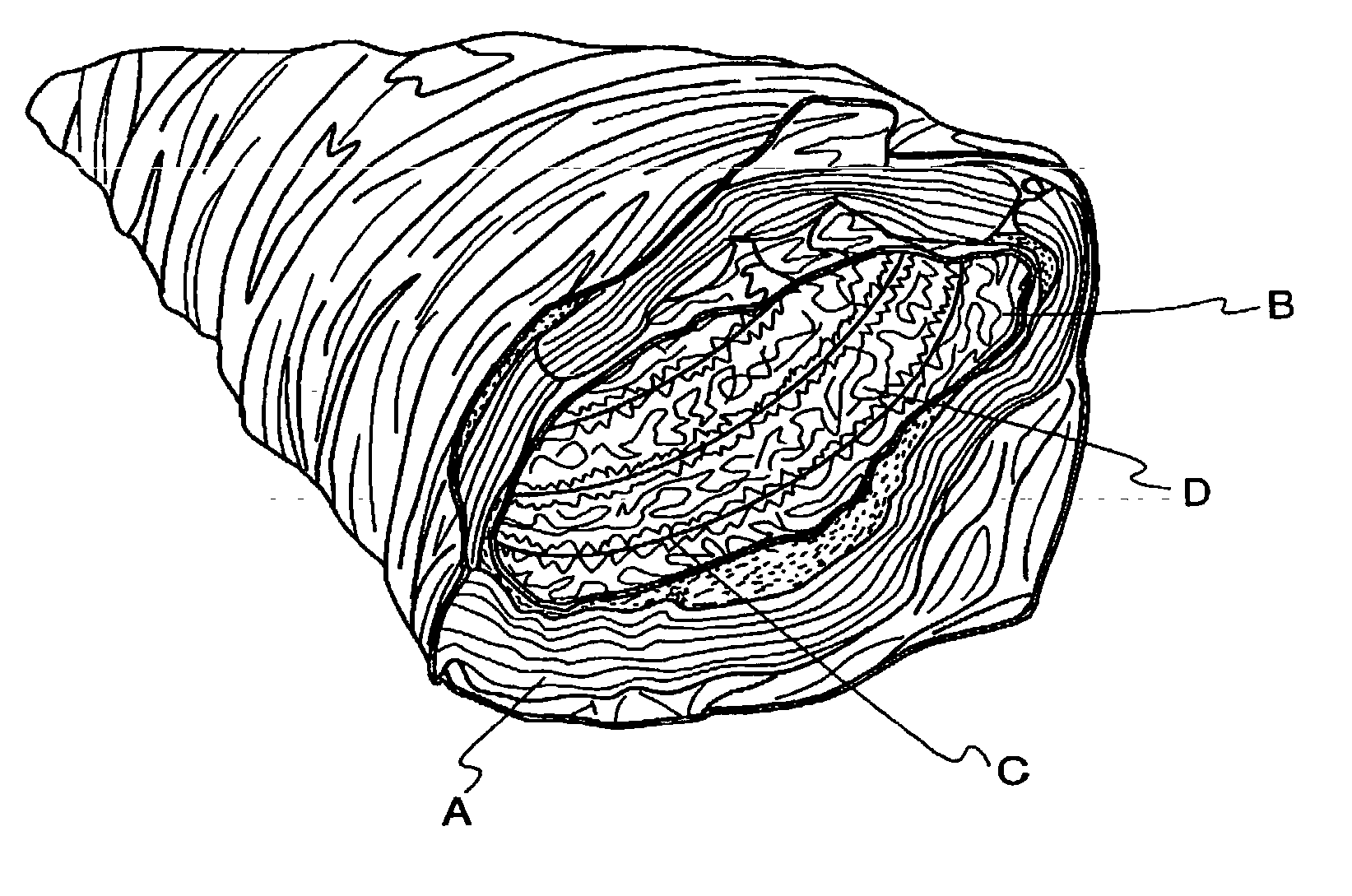

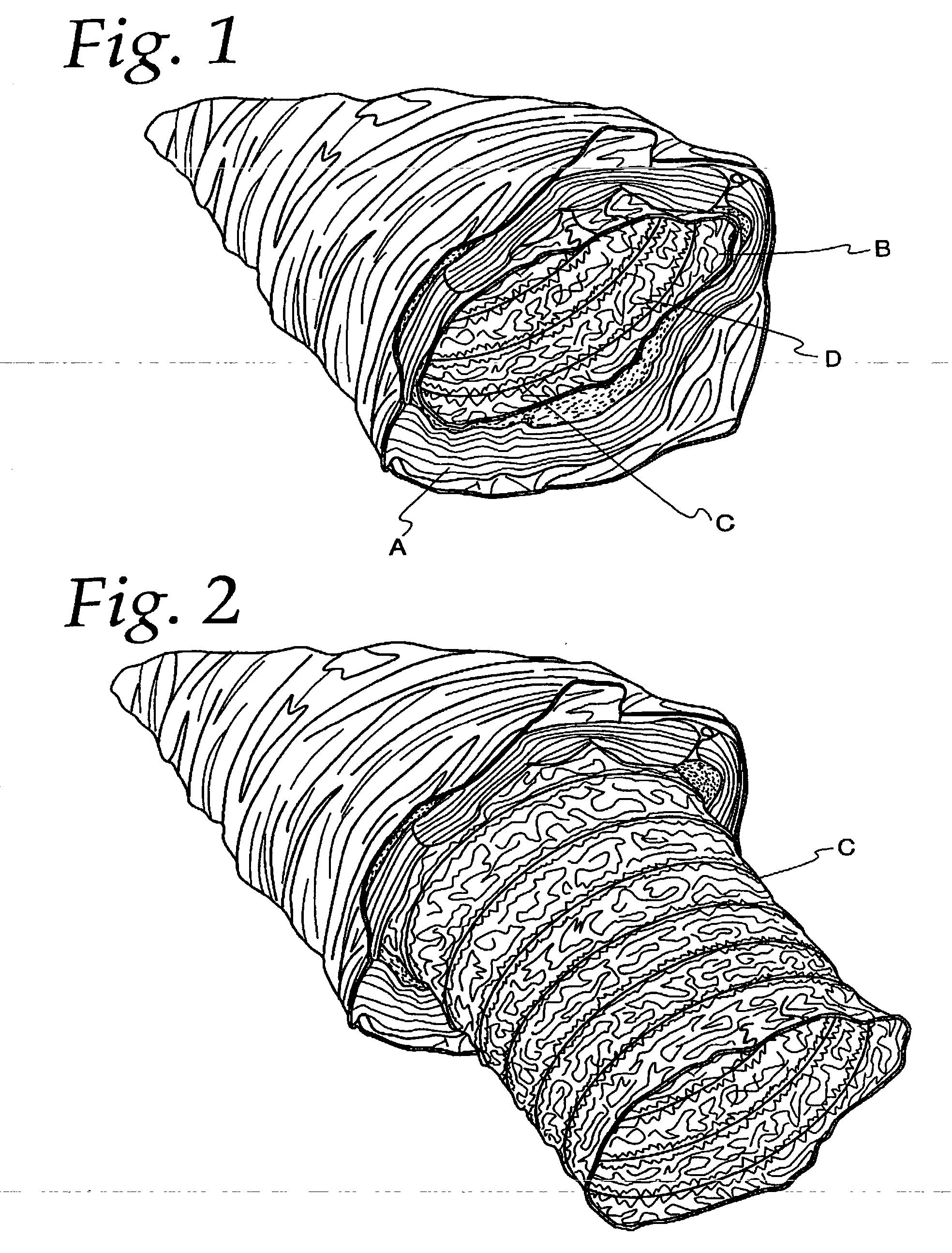

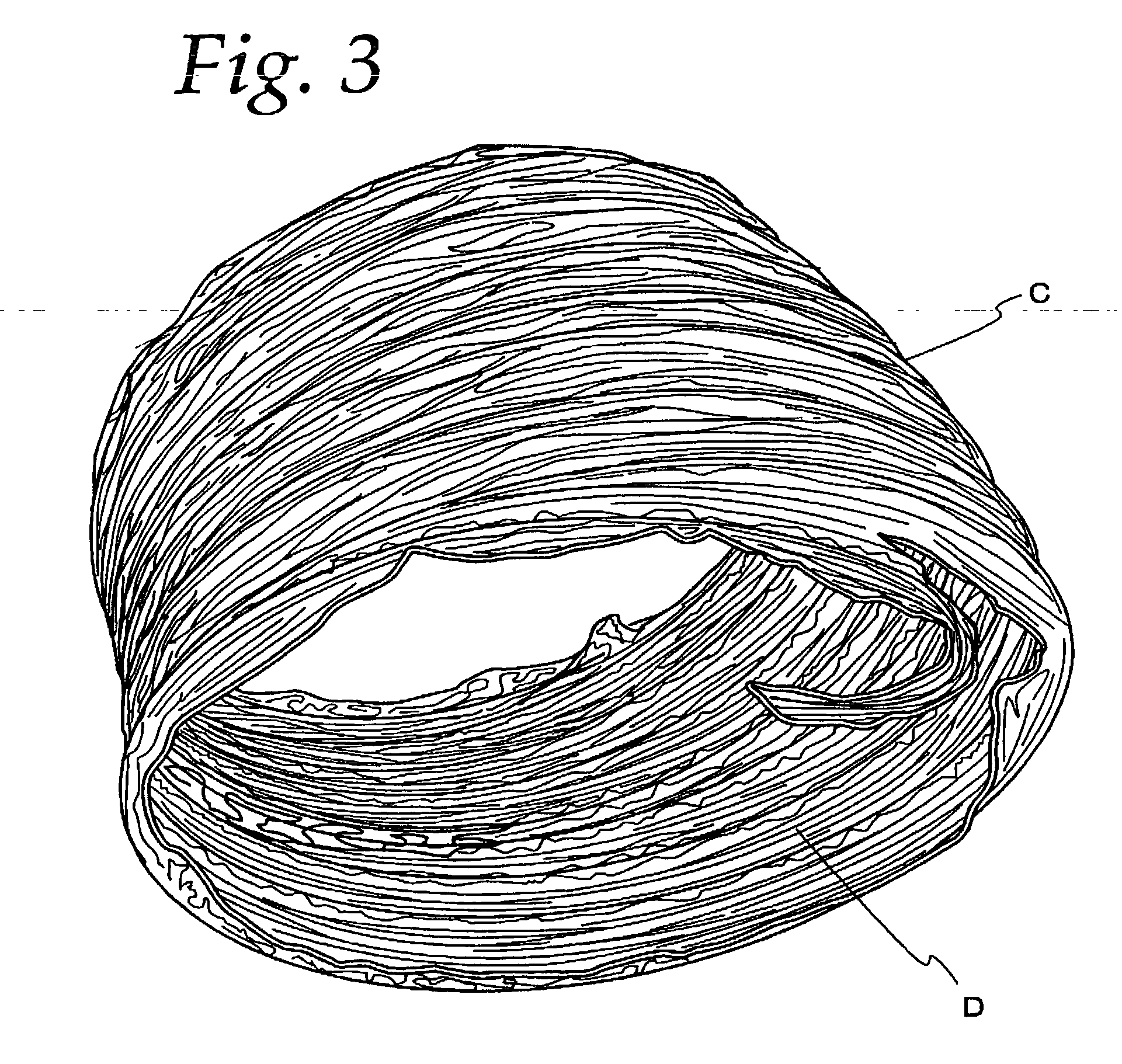

Making foam coated mats on-line

InactiveUS7285183B2High strengthIncreased durabilityNatural cellulose pulp/paperSpecial paperFiberProduction line

A new foam coated nonwoven fibrous mat having properties particularly suited for a facer on gypsum wallboard, laminates made therefrom and the method of making the mat is disclosed. The mat preferably contains a major portion of glass fibers and a minor portion of a resinous binder. The foam coating is permeable and reduces fiber dust and abrasion experienced in the past with relatively coarse, relatively inexpensive glass fibers in the mat. Contrary to previous methods, the foam coated fibrous mat is made in-line on a wet mat forming production line by applying a wet foam binder onto a wet, fibrous web followed by drying and curing in-line.

Owner:JOHNS MANVILLE CORP

Antimicrobial film structures for use in HVAC

InactiveUS20030215589A1Stable efficacyGood adhesionBiocideLighting and heating apparatusPolymer resinEngineering

The present invention relates to flexible film structures which can be affixed to flexible air duct and methods of making the film. More specifically, the present invention relates to film structures having at least one layer comprising an antimicrobial agent inorporated in a polymer resin or resin blend. The film structures of the present invention can be single layer polymer films comprising a layer of antimicrobial agent incorporated in a polymer resin or a multiple layer film wherein at least one layer comprises antimicrobial agent incorporated in a polymer resin. The film structures of the present invention can be affixed to the wiremold core of a flexible air duct to retard, reduce, inhibit, or eliminate microbial growth which can occur in the duct.

Owner:PECHINEY EMBALLAGE FLEXIBLE EURO

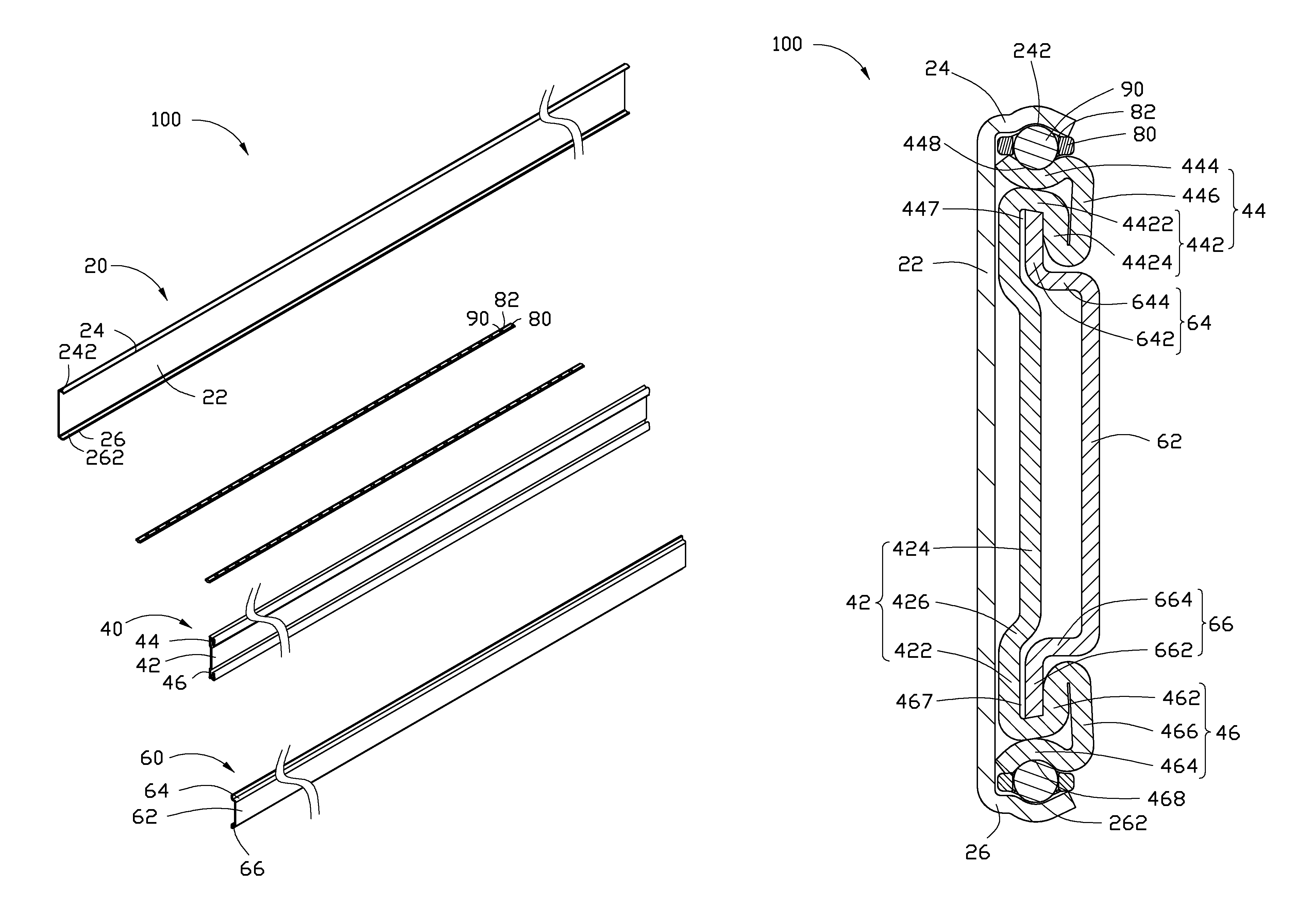

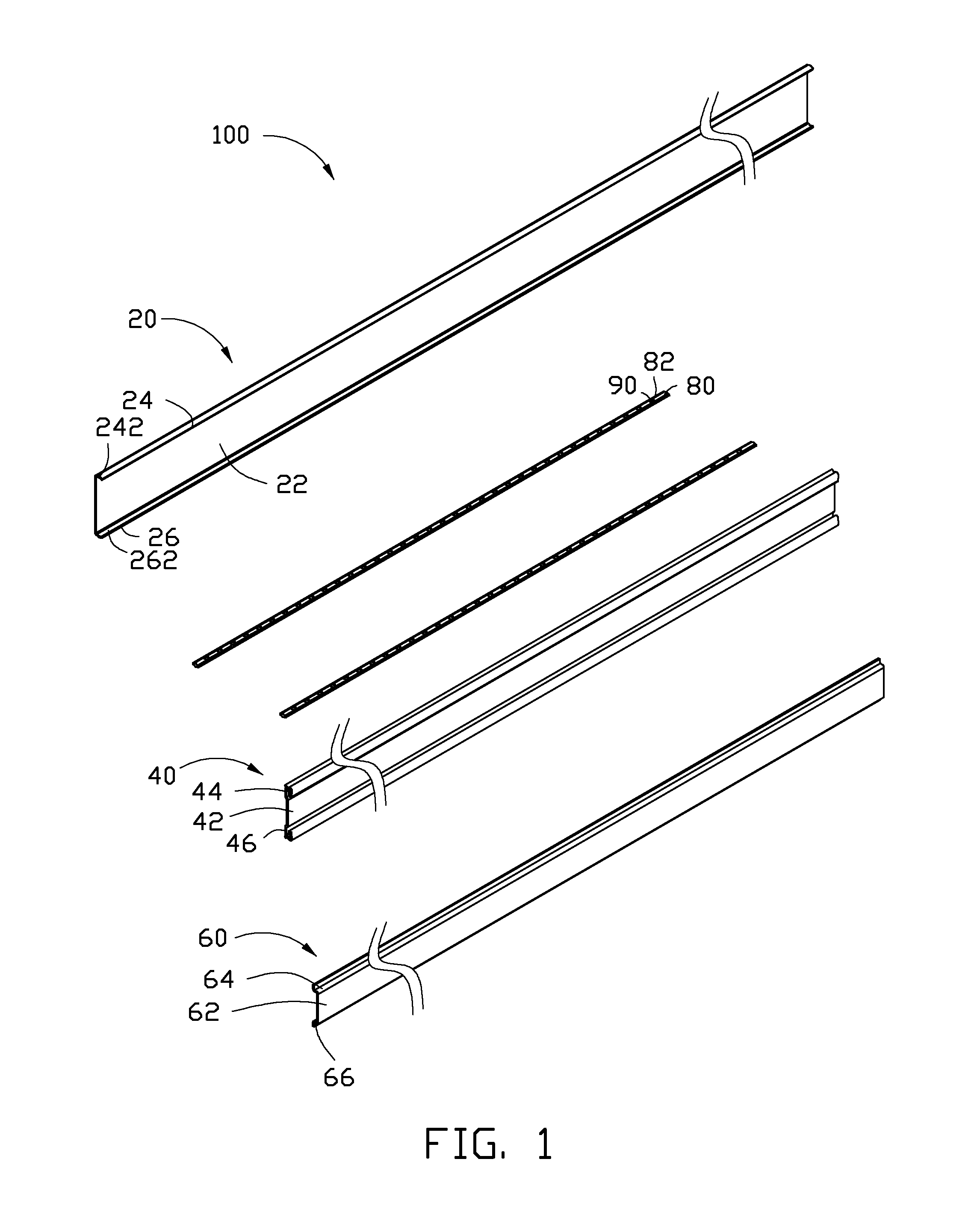

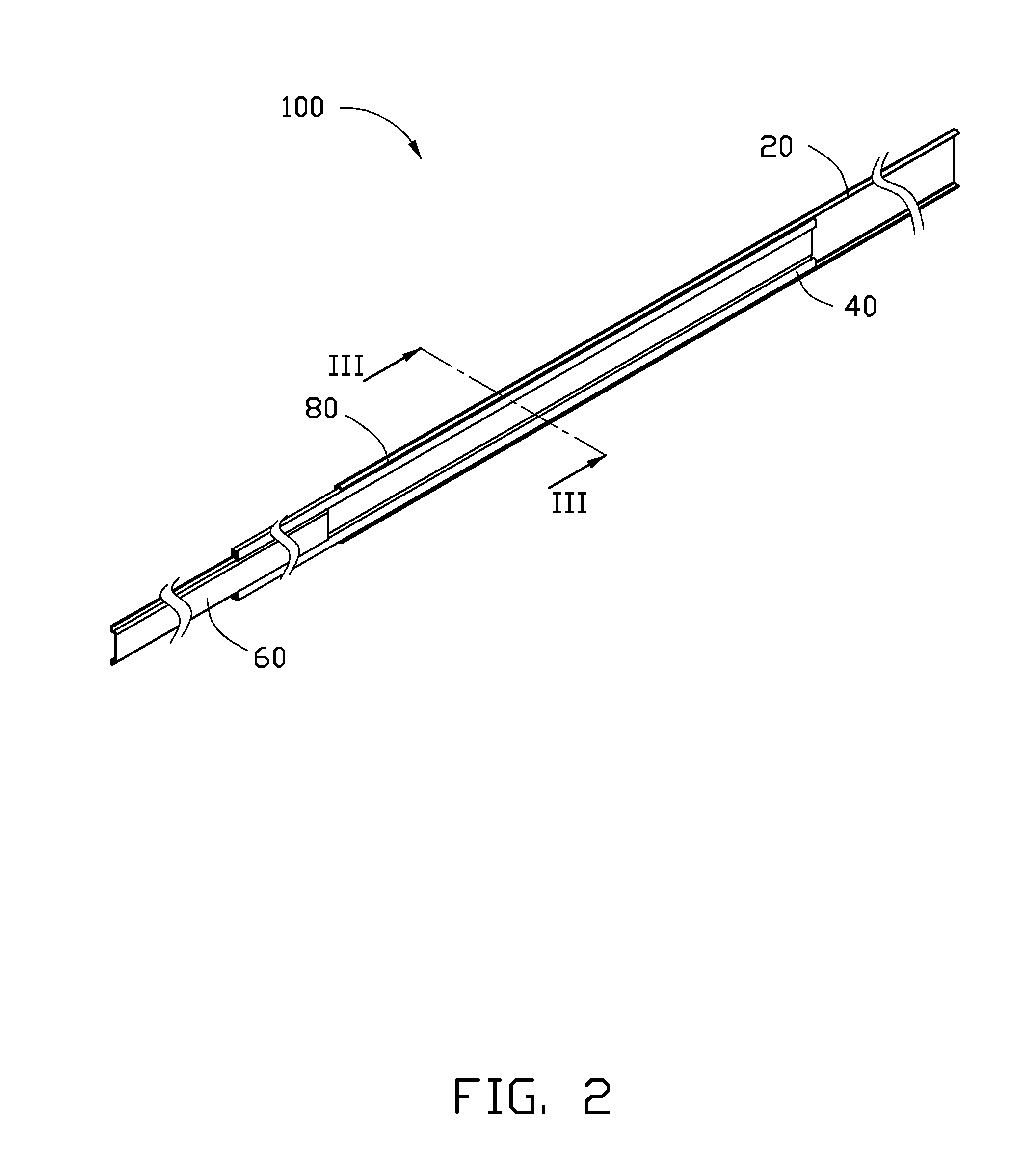

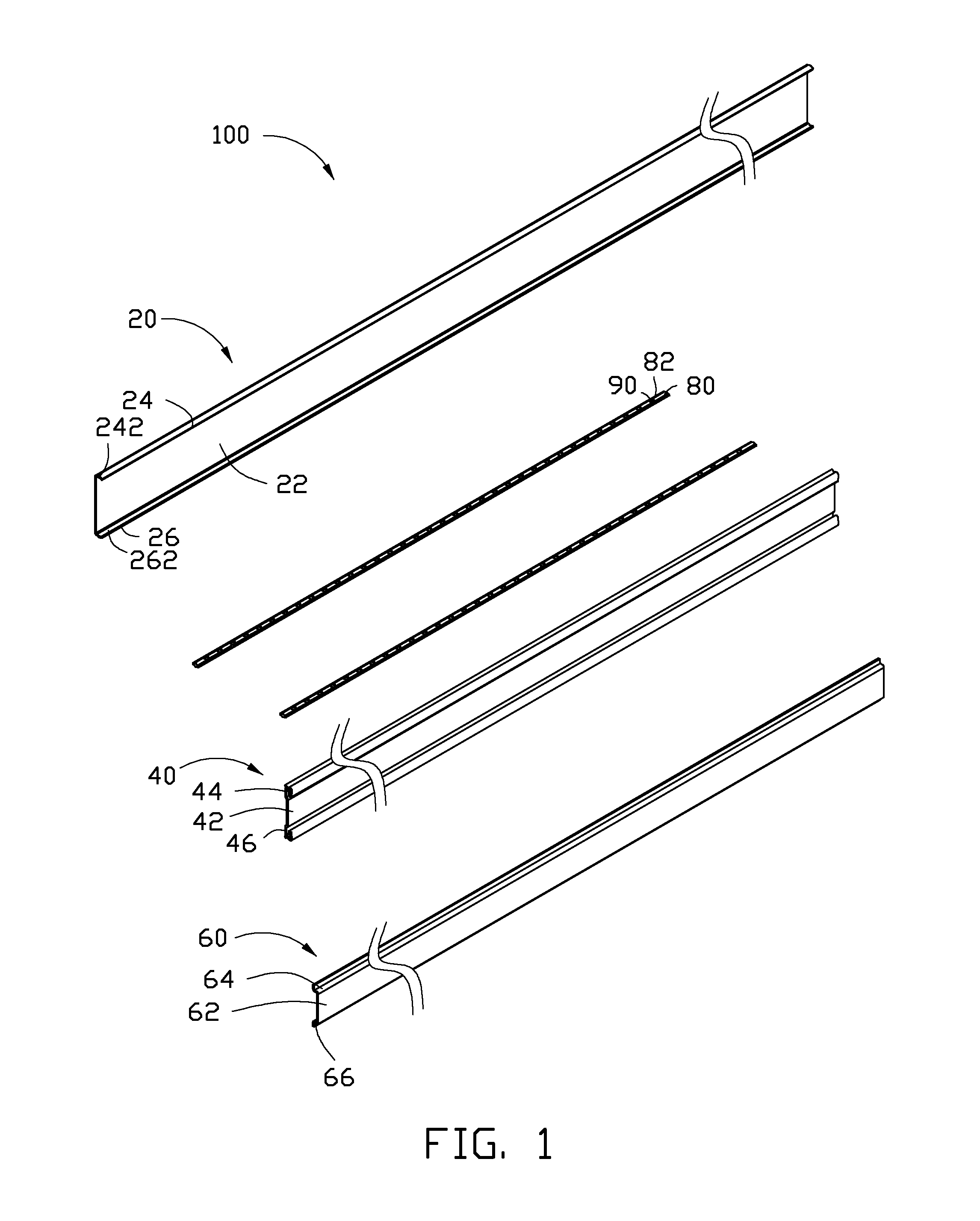

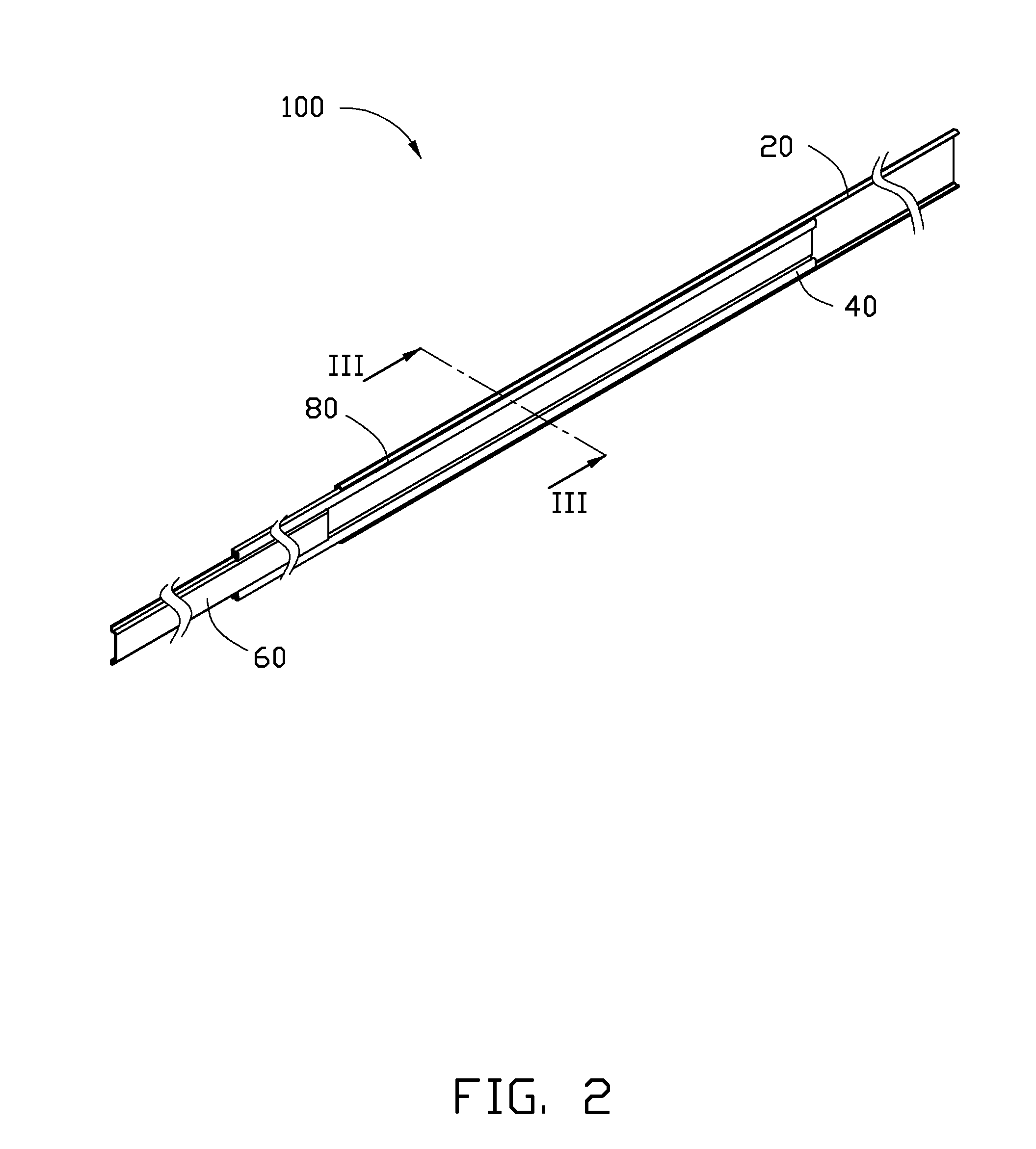

Slide rail structure

ActiveUS8251465B2Smooth slidingLow costServersSliding contact bearingsEngineeringMechanical engineering

Owner:FULIAN PRECISION ELECTRONICS (TIANJIN) CO LTD

Oxidation system and method for cleaning waste combustion flue gas

InactiveUS20140241971A1Efficient and cost-effective captureRemoval in wet scrubbers and condensers is facilitatedCombination devicesGas treatmentFlue gasEnvironmental engineering

Methods and systems for the removal of SO2 from waste combustion flue gas are described herein. The subject methods and systems entail one step, two steps or three steps to produce cleaned flue gas for release to the atmosphere.

Owner:GENERAL ELECTRIC TECH GMBH

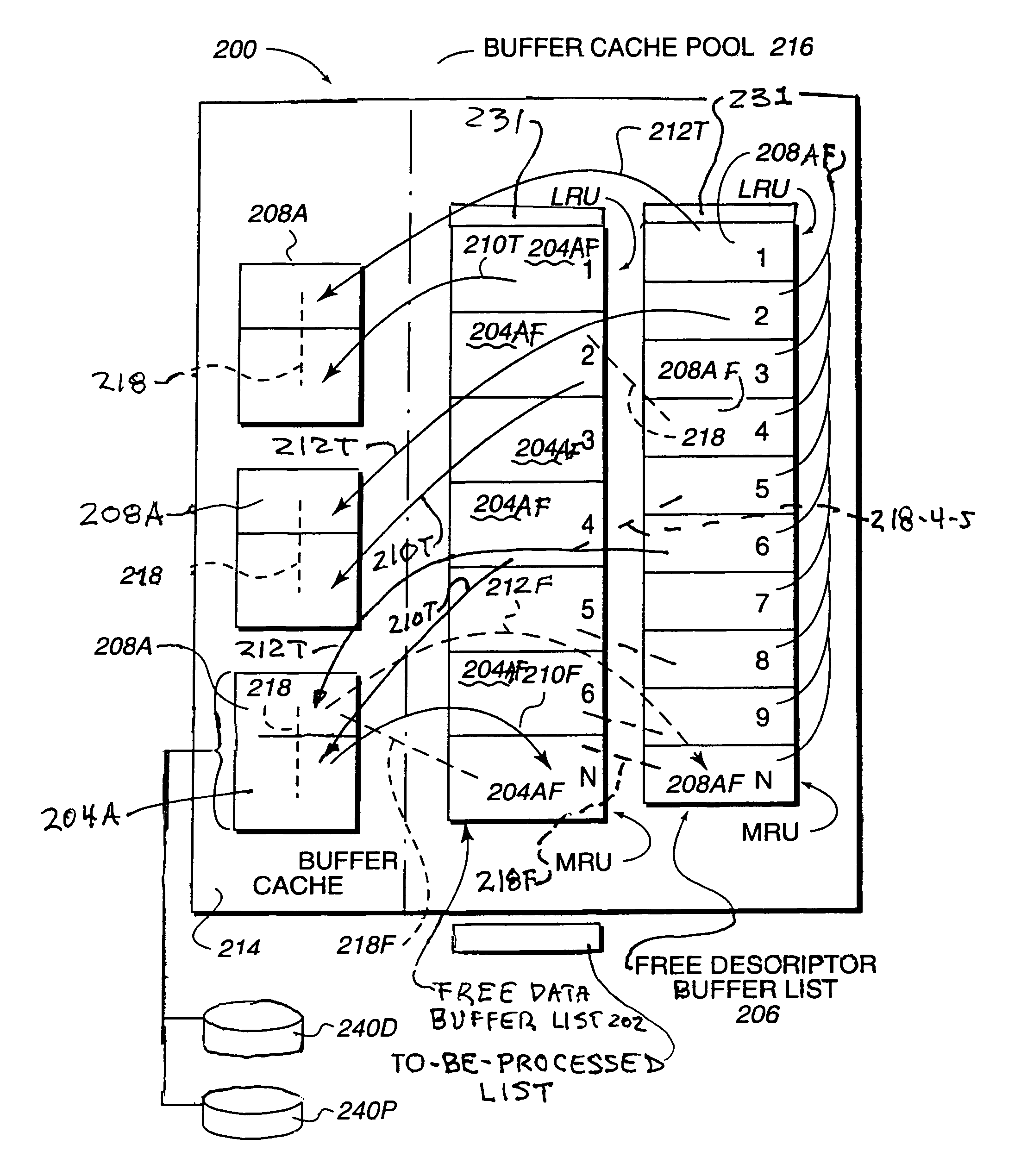

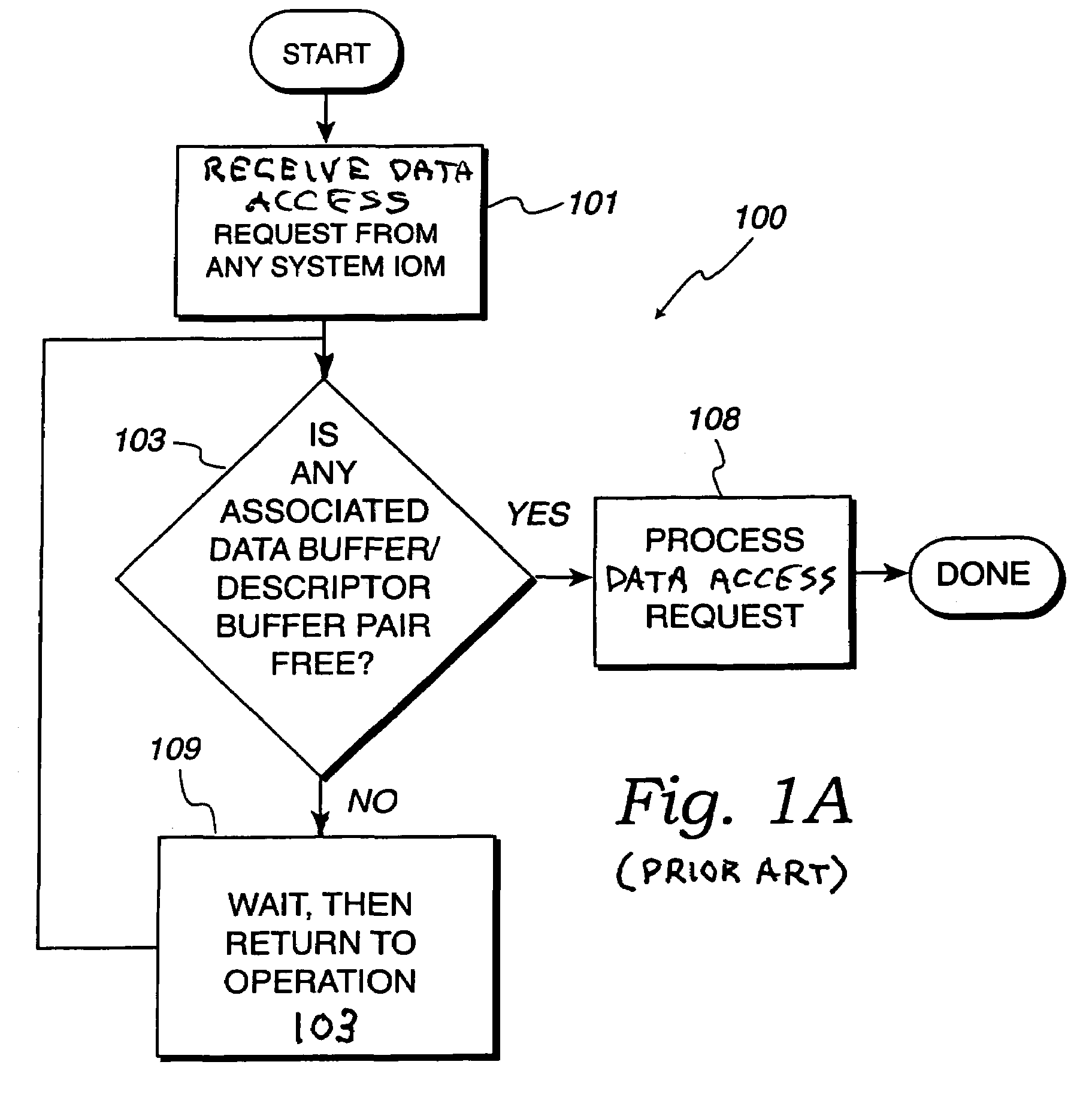

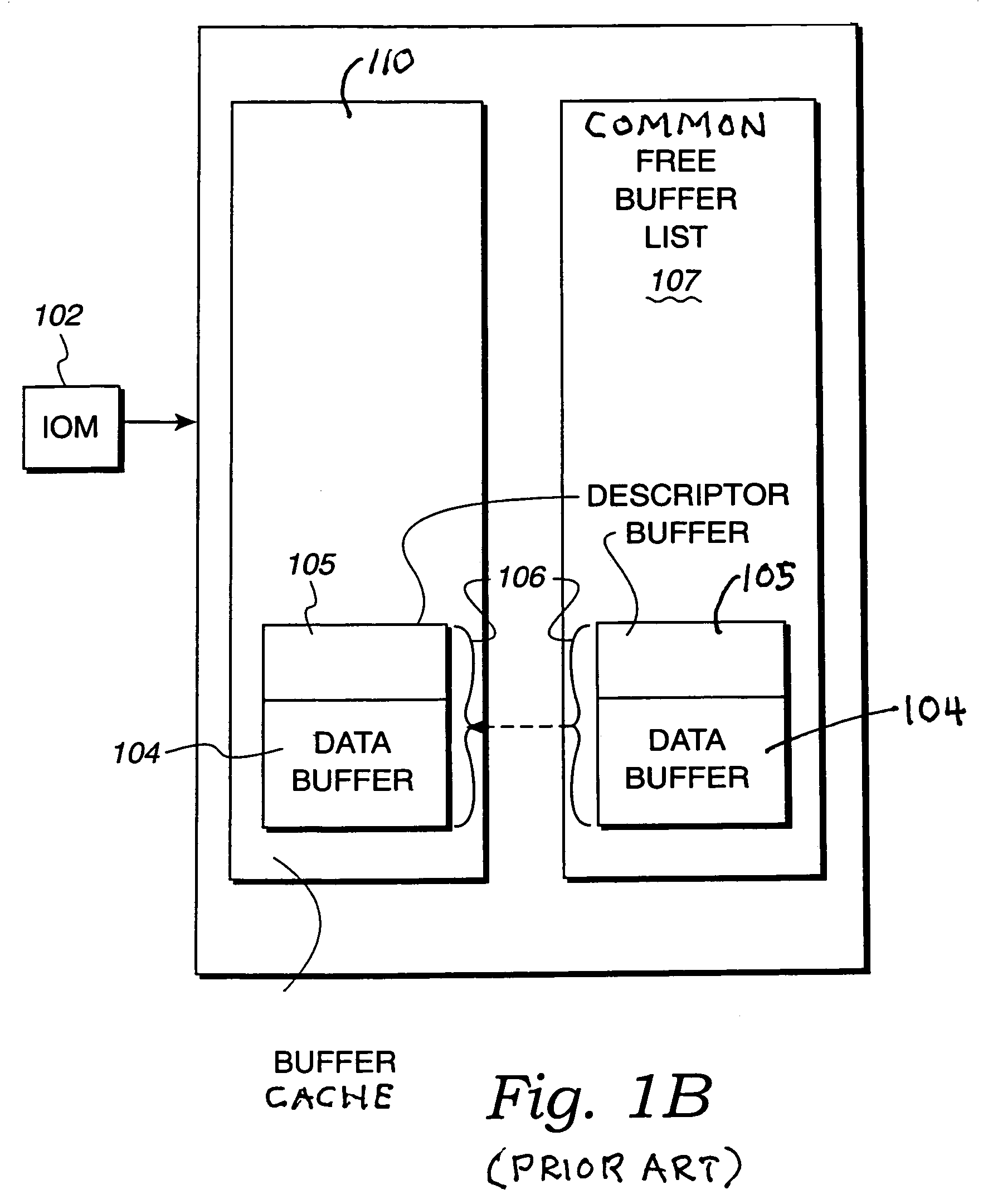

Methods of and apparatus for efficient buffer cache utilization

InactiveUS7210001B2Reduce storage sizeRapid processingRedundant data error correctionMemory systemsData bufferFrequent use

Efficient buffer cache utilization frees a data buffer as soon as data buffer processing is completed, and without losing association of the freed data buffer and a descriptor buffer. Separate free buffer link lists identify the freed data buffer and any freed descriptor buffer. The data buffer is rapidly processed then freed generally before completion of processing of the descriptor buffer, freeing the processed associated data buffer before the associated descriptor buffer is freed. The association of the processed free data buffer and the descriptor buffer may be ended to enable the more frequent use of the large capacity data buffer for other update requests.

Owner:PMC-SIERRA

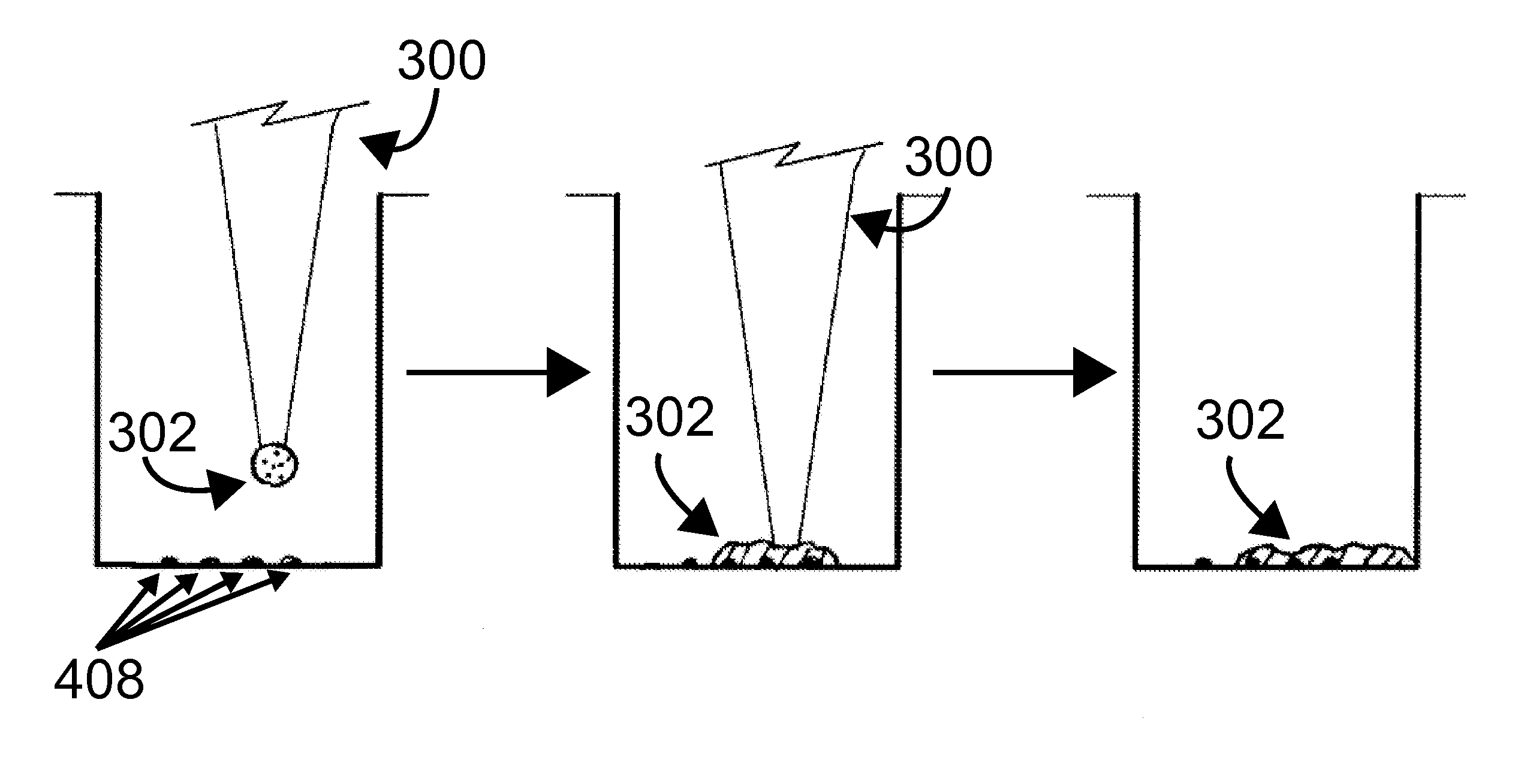

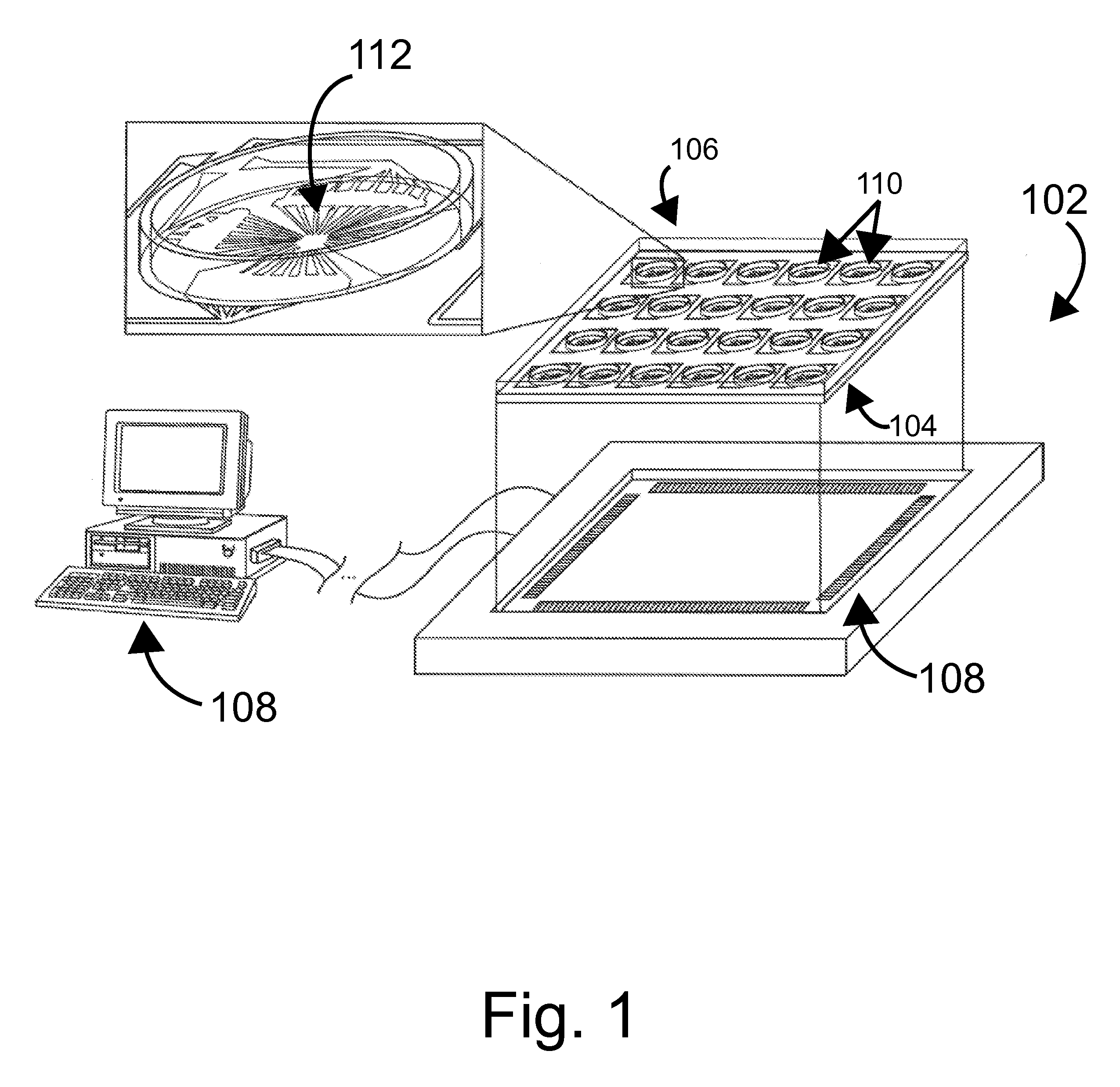

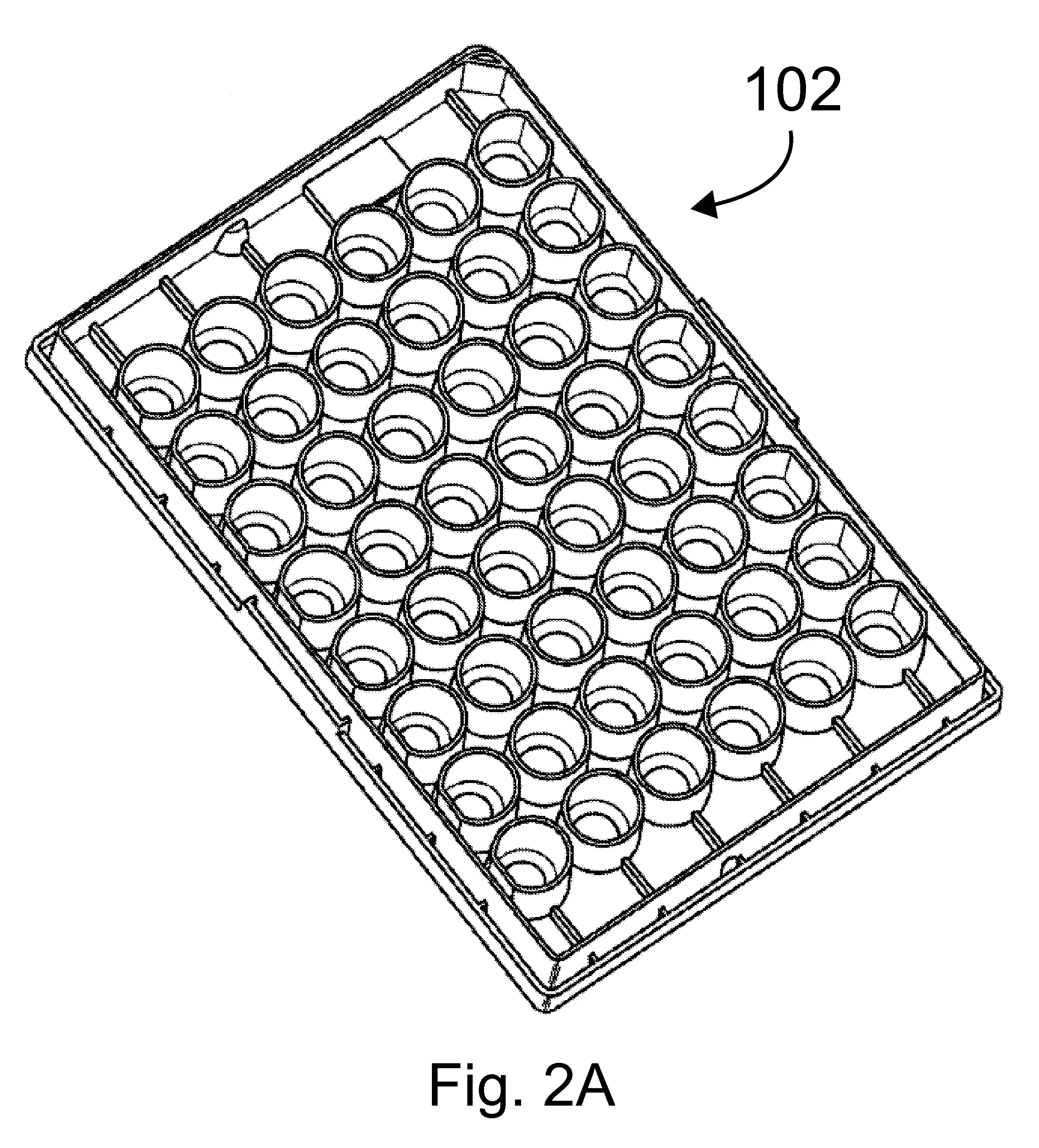

Devices, systems, and methods for targeted plating of materials in high-throughput culture plates

ActiveUS20150125942A1Automated platingSave timeBioreactor/fermenter combinationsBiological substance pretreatmentsElectroplatingCulture plates

Devices, systems, and methods for facilitating placement of cells and materials in culture plates configured for high-throughput applications are provided. A culture system is provided with a culture plate having a lid for guiding placement of cells and materials in each individual culture well of a culture plate. The lid may provide for coupling to an electrophysiology culture plate comprising a biosensor plate and a biologic culture plate, where the biosensor plate underlies and is coupled to the culture well plate such that each biosensor is operatively coupled to one culture well of the plurality of culture wells. A containment device that physically influences the positioning of fluid received in the culture plate is also provided herein.

Owner:AXION BIOSYST

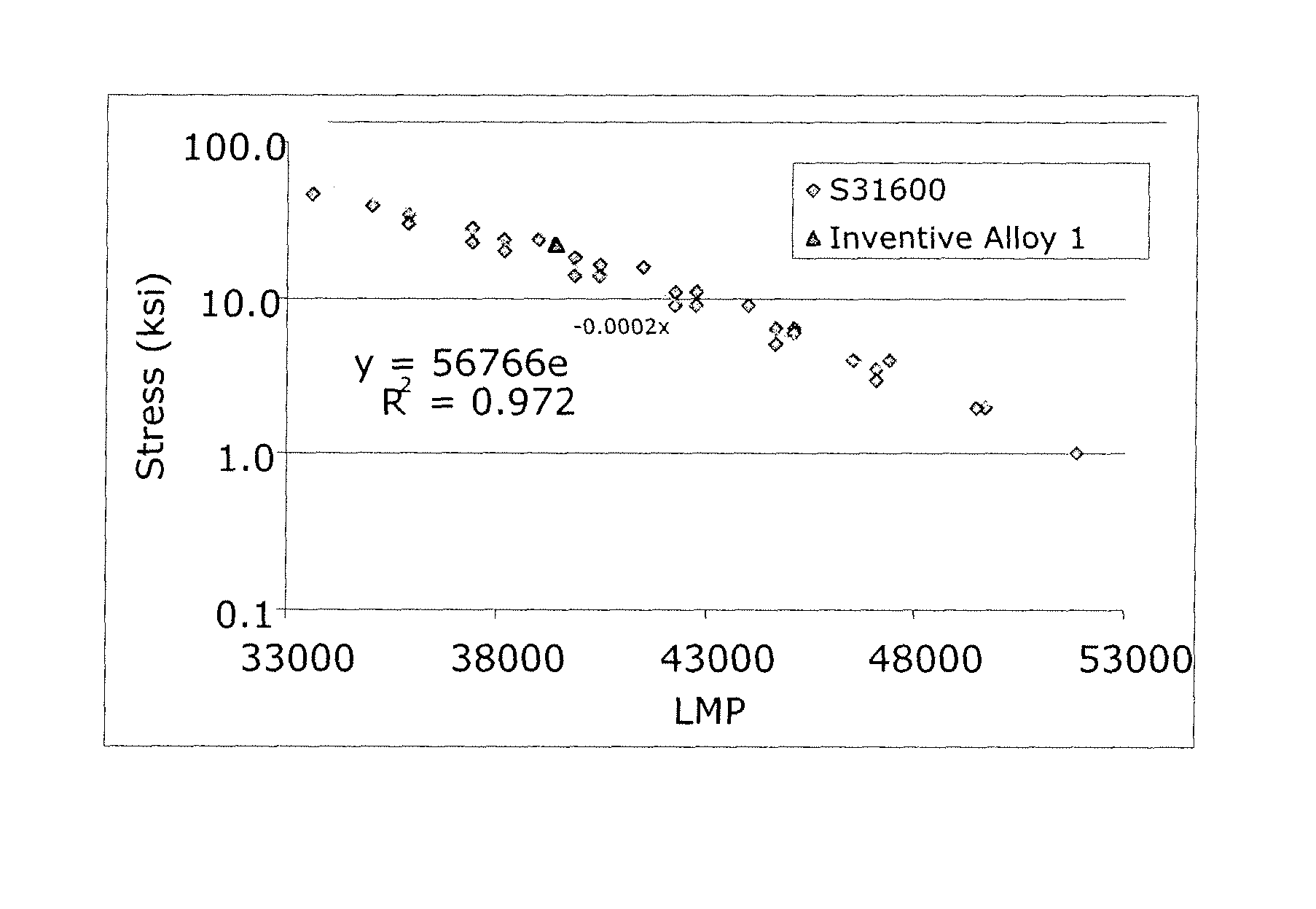

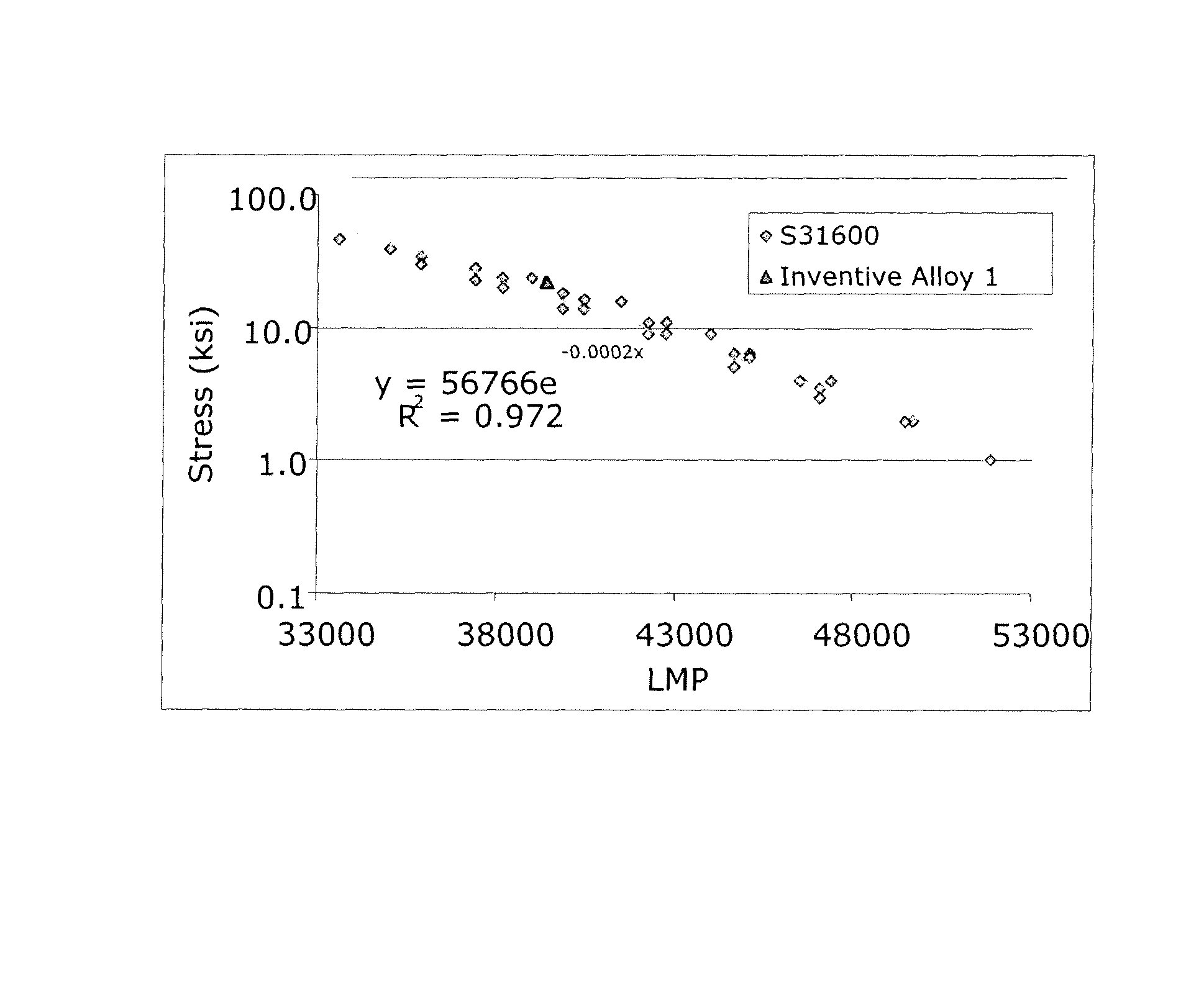

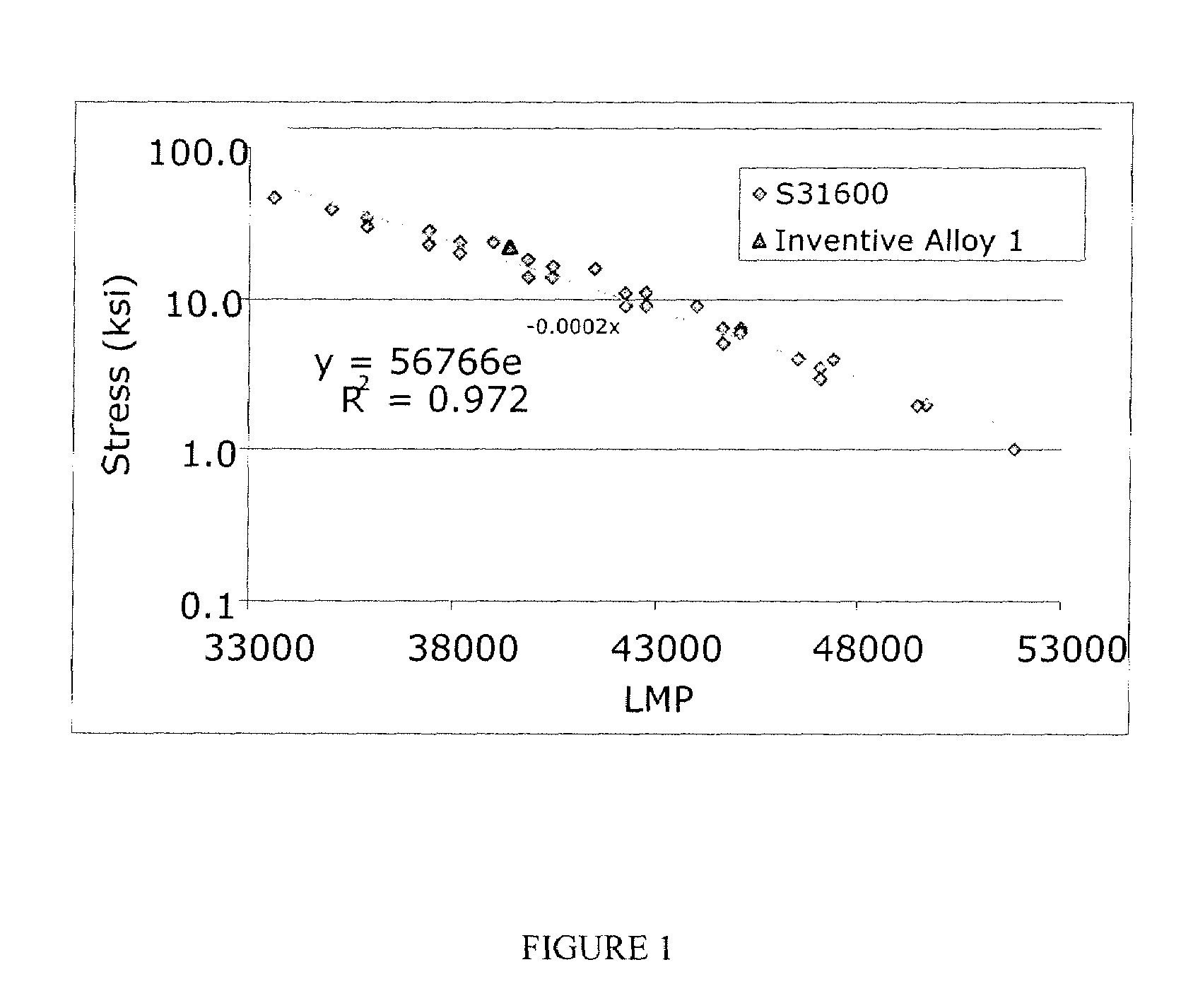

Lean austenitic stainless steel

ActiveUS8313691B2Low costComparable corrosion resistance and formability propertyAusteniteAustenitic stainless steel

An austenitic stainless steel having low nickel and molybdenum and exhibiting comparable corrosion resistance and formability properties to higher nickel and molybdenum alloys comprises, in weight %, up to 0.20 C, 2.0-9.0 Mn, up to 2.0 Si, 16.0-23.0 Cr, 1.0-5.0 Ni, up to 3.0 Mo, up to 3.0 Cu, 0.1-0.35 N, up to 4.0 W, up to 0.01 B, up to 1.0 Co, iron and impurities, the steel having a ferrite number of less than 10 and a MD30 value of less than 20° C.

Owner:ATI PROPERTIES LLC

Lean austenitic stainless steel

An austenitic stainless steel having low nickel and molybdenum and exhibiting comparable corrosion resistance and formability properties to higher nickel and molybdenum alloys comprises, in weight %, up to 0.20 C, 2.0-9.0 Mn, up to 2.0 Si, 16.0-23.0 Cr, 1.0-5.0 Ni, up to 3.0 Mo, up to 3.0 Cu, 0.1-0.35 N, up to 4.0 W, up to 0.01 B, up to 1.0 Co, iron and impurities, the steel having a ferrite number of less than 10 and a MD30 value of less than 20° C.

Owner:ATI PROPERTIES LLC

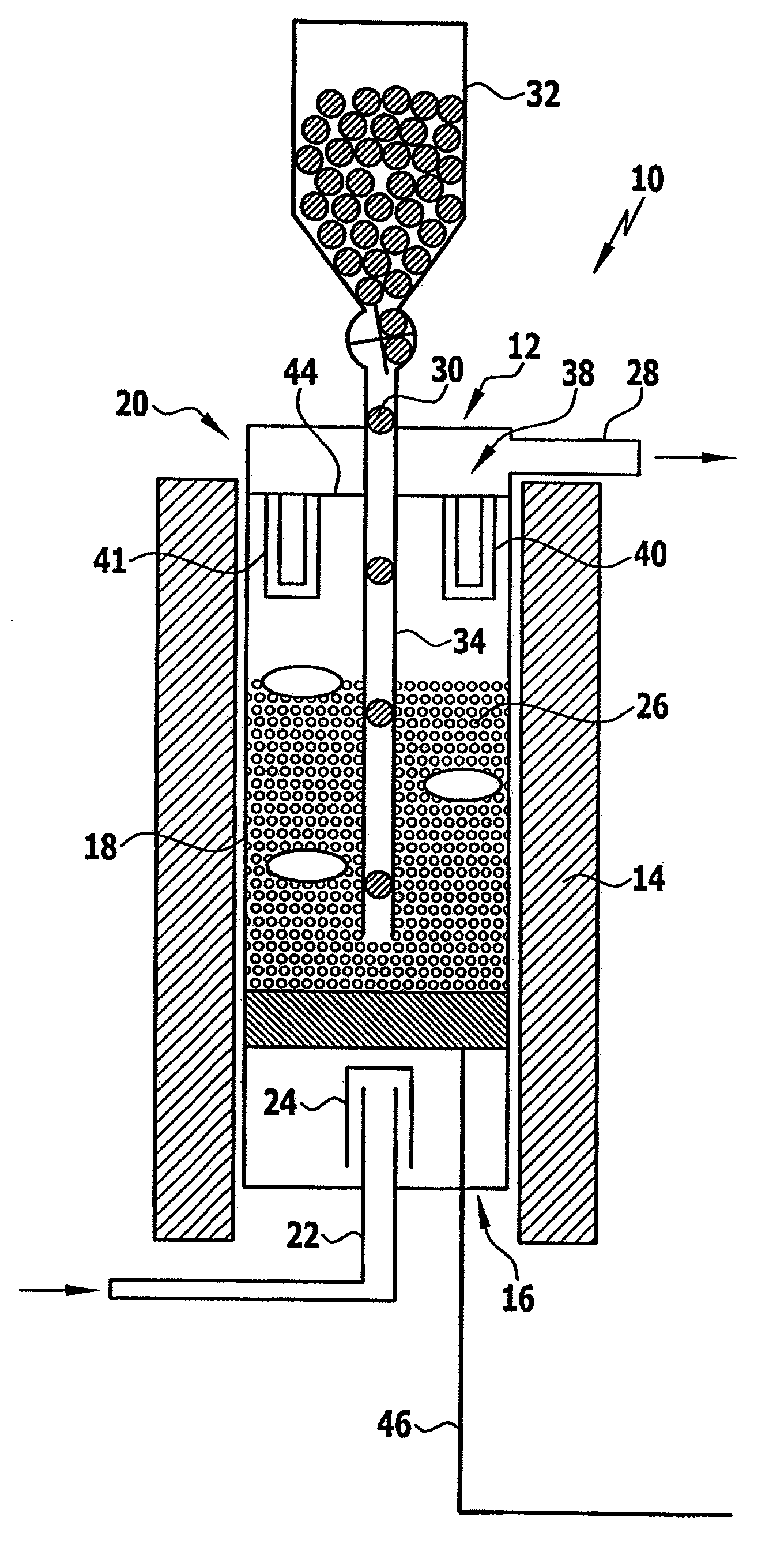

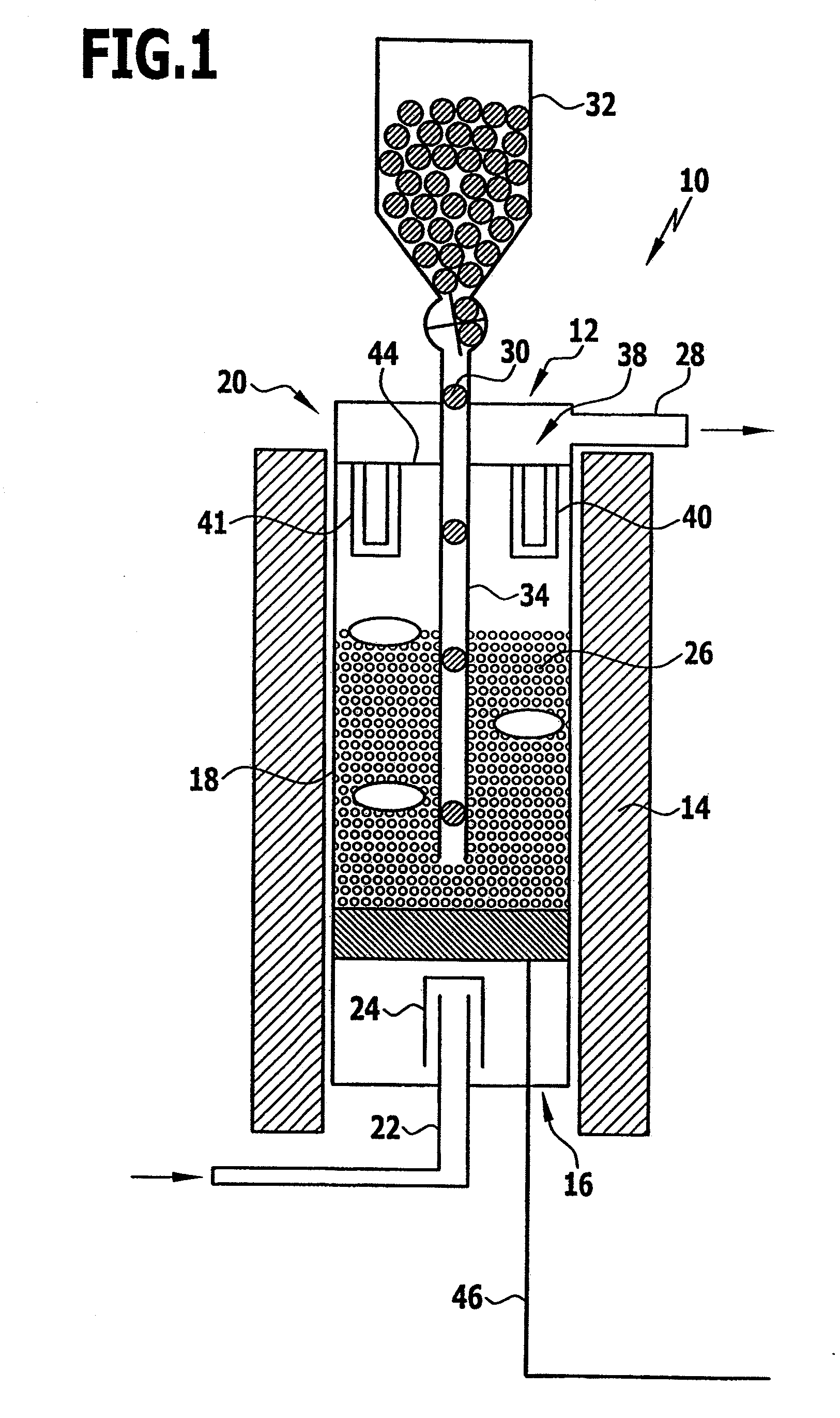

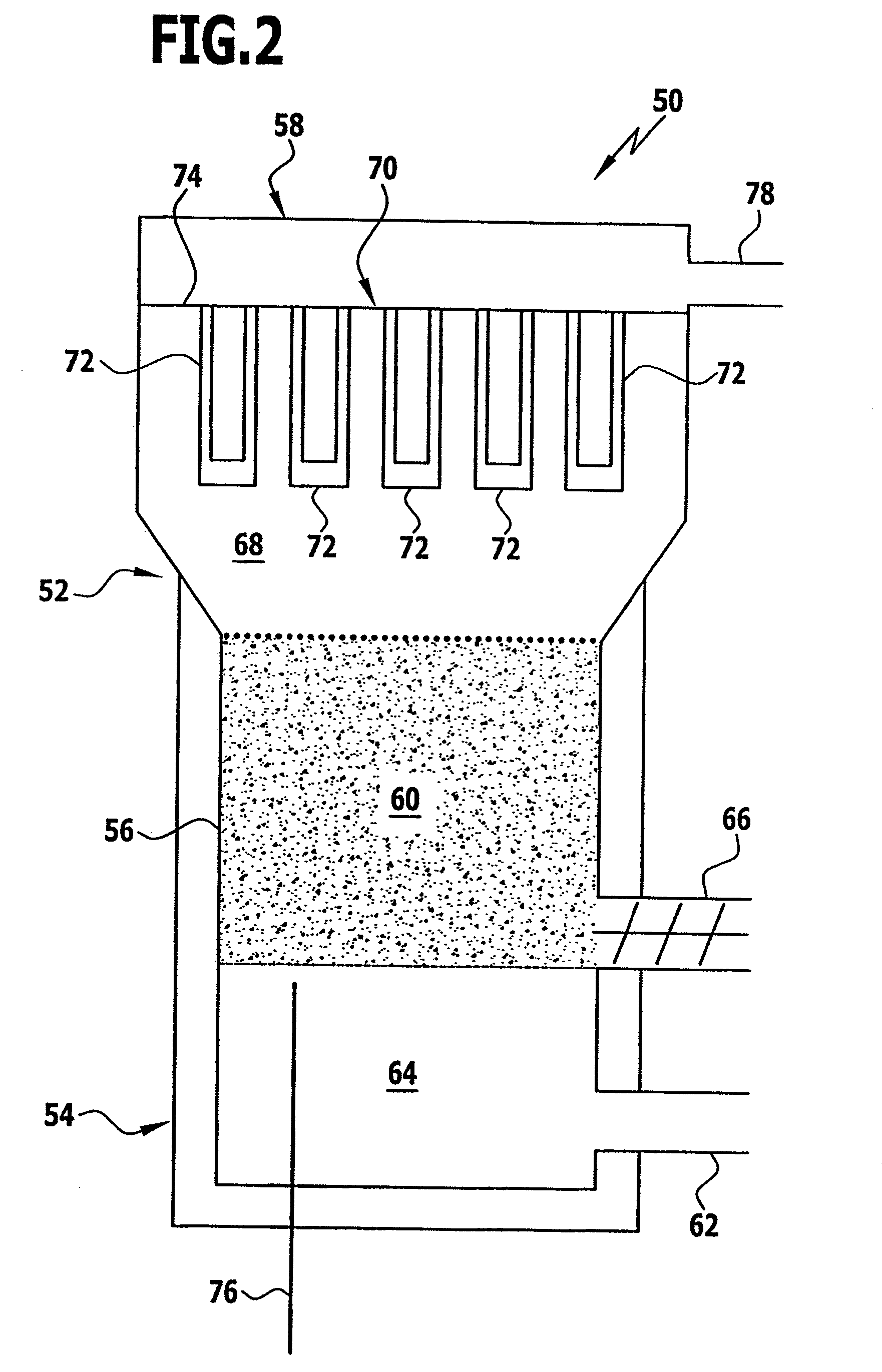

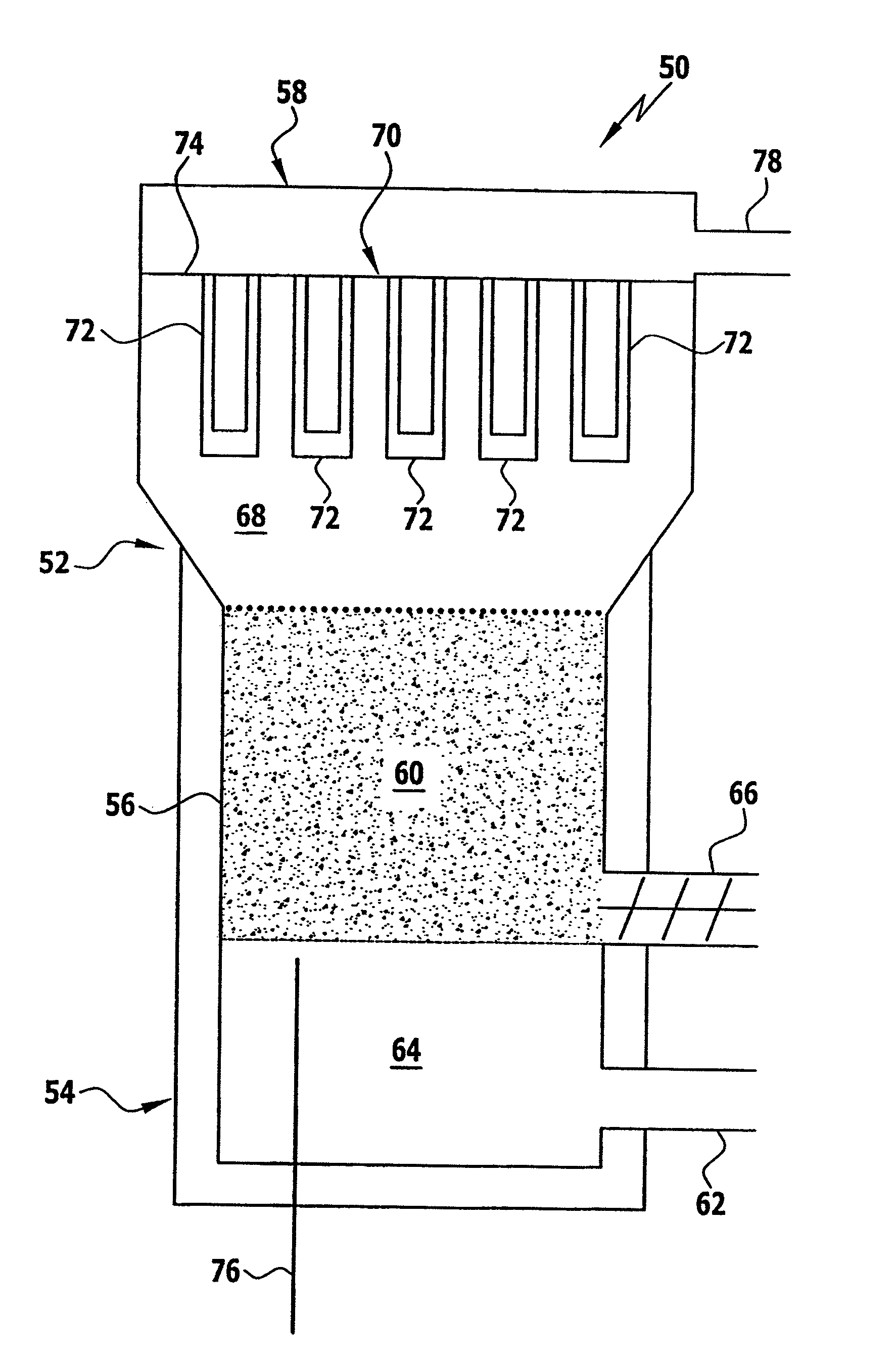

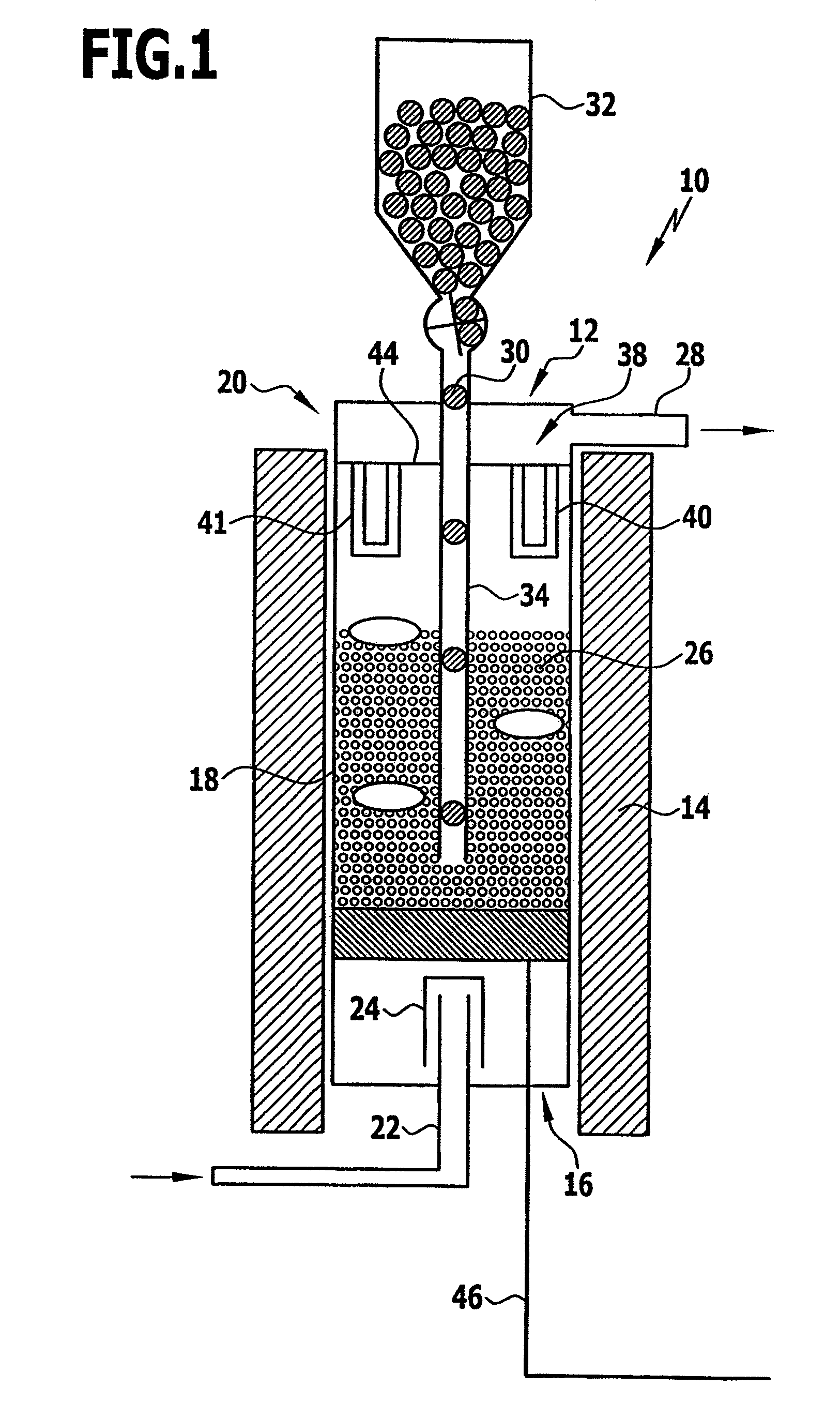

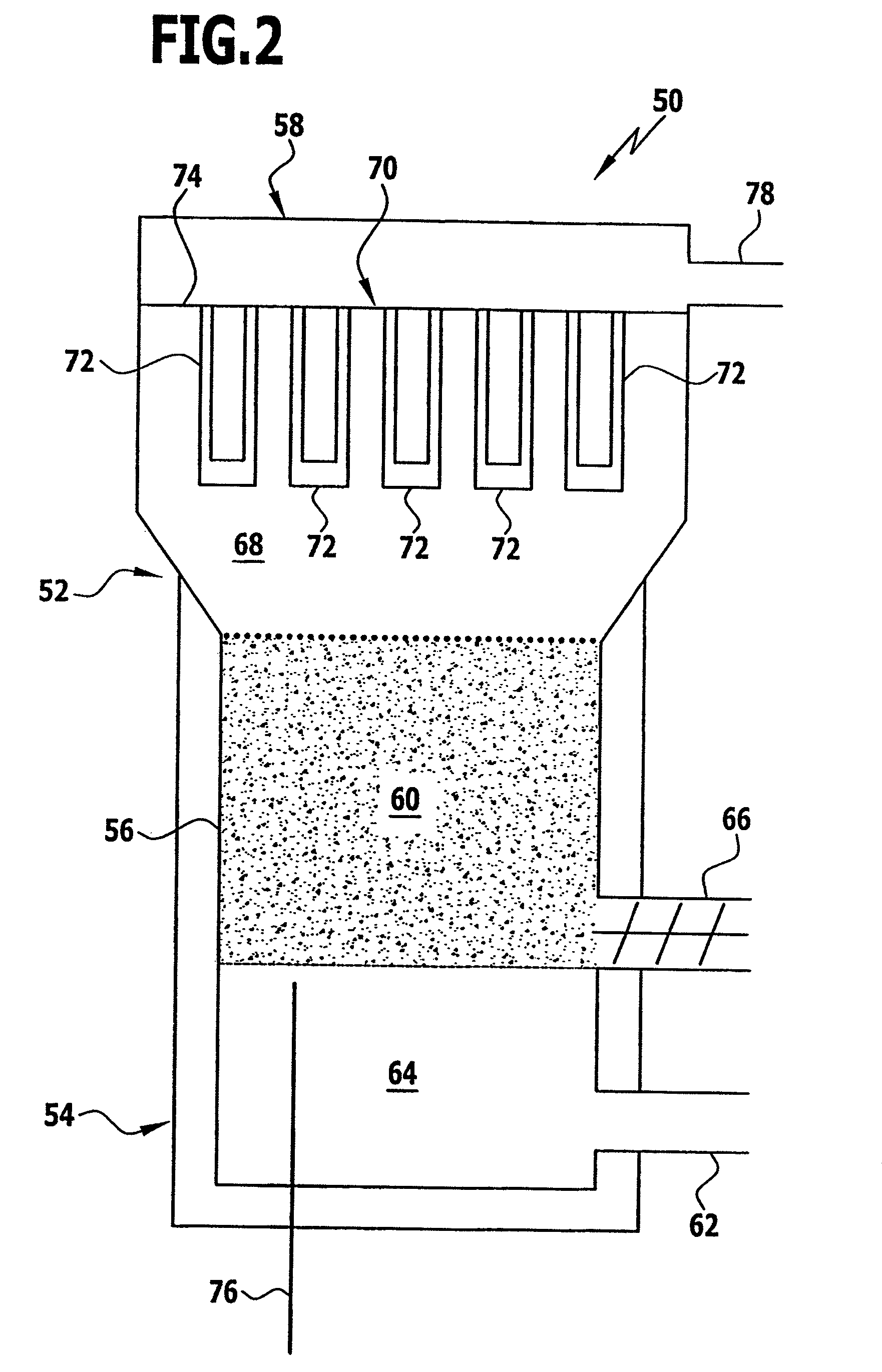

Gasification apparatus and method for generating syngas from gasifiable feedstock material

InactiveUS20100223848A1Enhance fluiditySimple and control feedingBioreactor/fermenter combinationsBiological substance pretreatmentsSyngasProcess engineering

The present invention relates to a gasification apparatus for generating syngas from gasifiable feedstock material, said apparatus comprisinga vessel having a feedstock inlet, an inlet for a gaseous gasifying medium, an outlet for exhausted feedstock material and a syngas outlet;a gasifying reactor accommodated in said vessel and in fluid communication with said feedstock inlet, said outlet for exhausted feedstock material and said inlet for said gasifying medium of said vesel; anda filtering unit accommodated in said vessel and having an upstream side and a downstream side, said upstream side of said filtering unit being in fluid communication with said reactor and said downstream side thereof being in fluid communication with said syngas outlet.

Owner:PALL CORP

Split gusset connection

ActiveUS20140318075A1Less-reliable and accurateAvoid excessive controlBuilding repairsLoad-supporting elementsEngineeringGreat Relative

A gusset connection that allows greater relative movement between connected structural members and simplifies erection in the field. The gusset connection can be a first gusset portion moveably or fixedly connected to a vertical column and a second gusset connection moveably or fixedly connected to a horizontal beam. A diagonal brace is moveably or fixedly connected to the gusset connection. The first and second gusset portions are not directly connected to each other to allow relative movement between the column, beam, and diagonal brace.

Owner:SHUHAIBAR CONSTANTINE

Gasification apparatus and method for generating syngas from gasifiable feedstock material

The present invention relates to a gasification apparatus for generating syngas from gasifiable feedstock material, said apparatus comprisinga vessel having a feedstock inlet, an inlet for a gaseous gasifying medium, an outlet for exhausted feedstock material and a syngas outlet;a gasifying reactor accommodated in said vessel and in fluid communication with said feedstock inlet, said outlet for exhausted feedstock material and said inlet for said gasifying medium of said vessel; anda filtering unit accommodated in said vessel and having an upstream side and a downstream side, said upstream side of said filtering unit being in fluid communication with said reactor and said downstream side thereof being in fluid communication with said syngas outlet.

Owner:PALL CORP

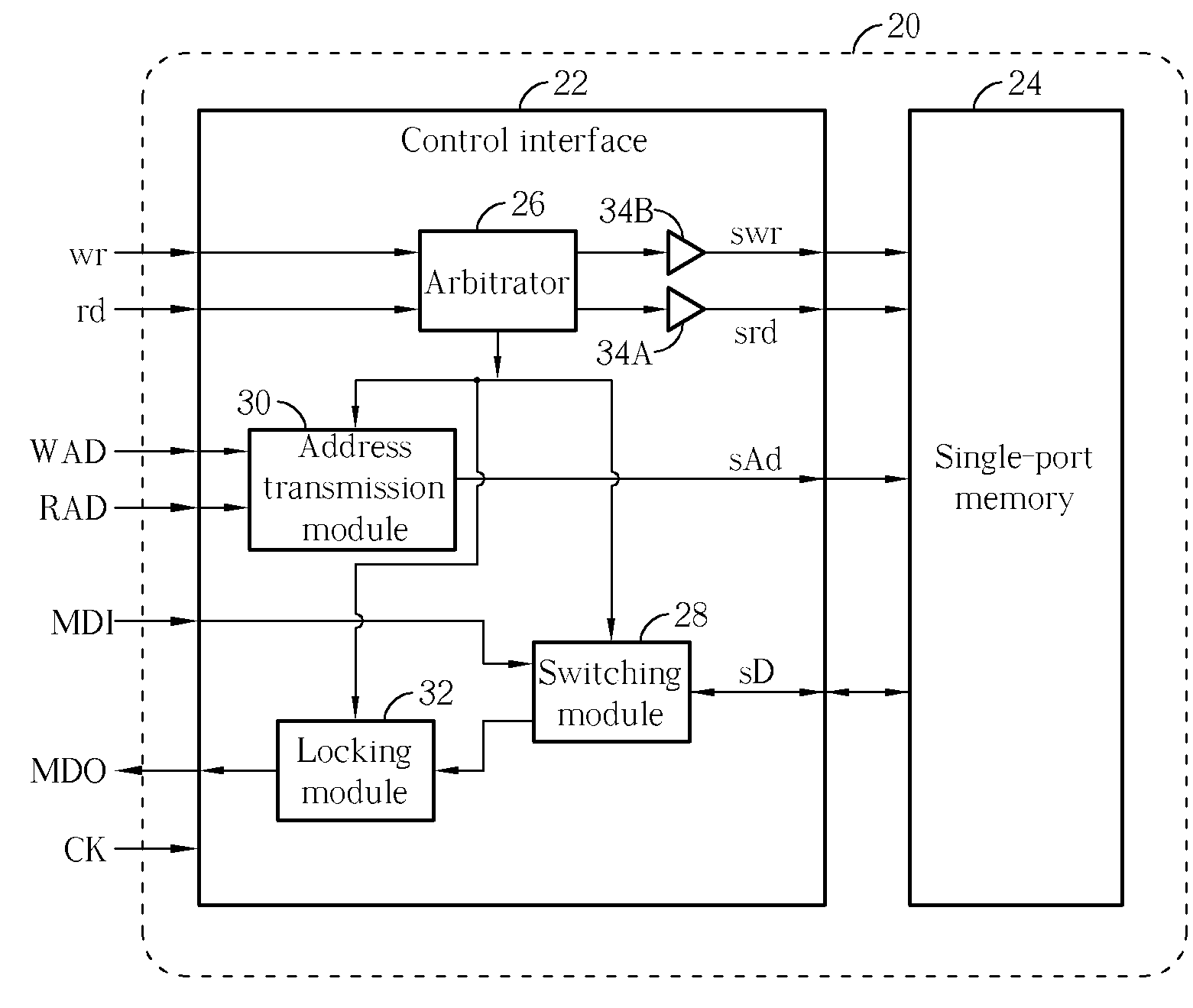

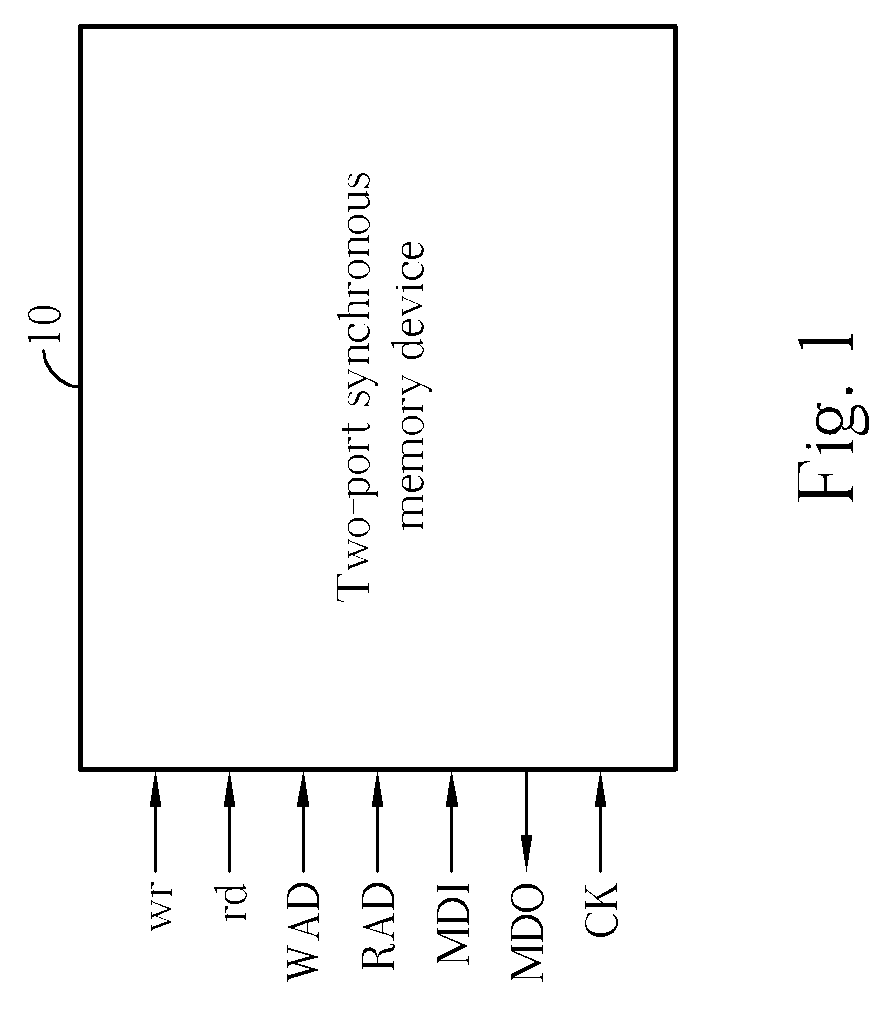

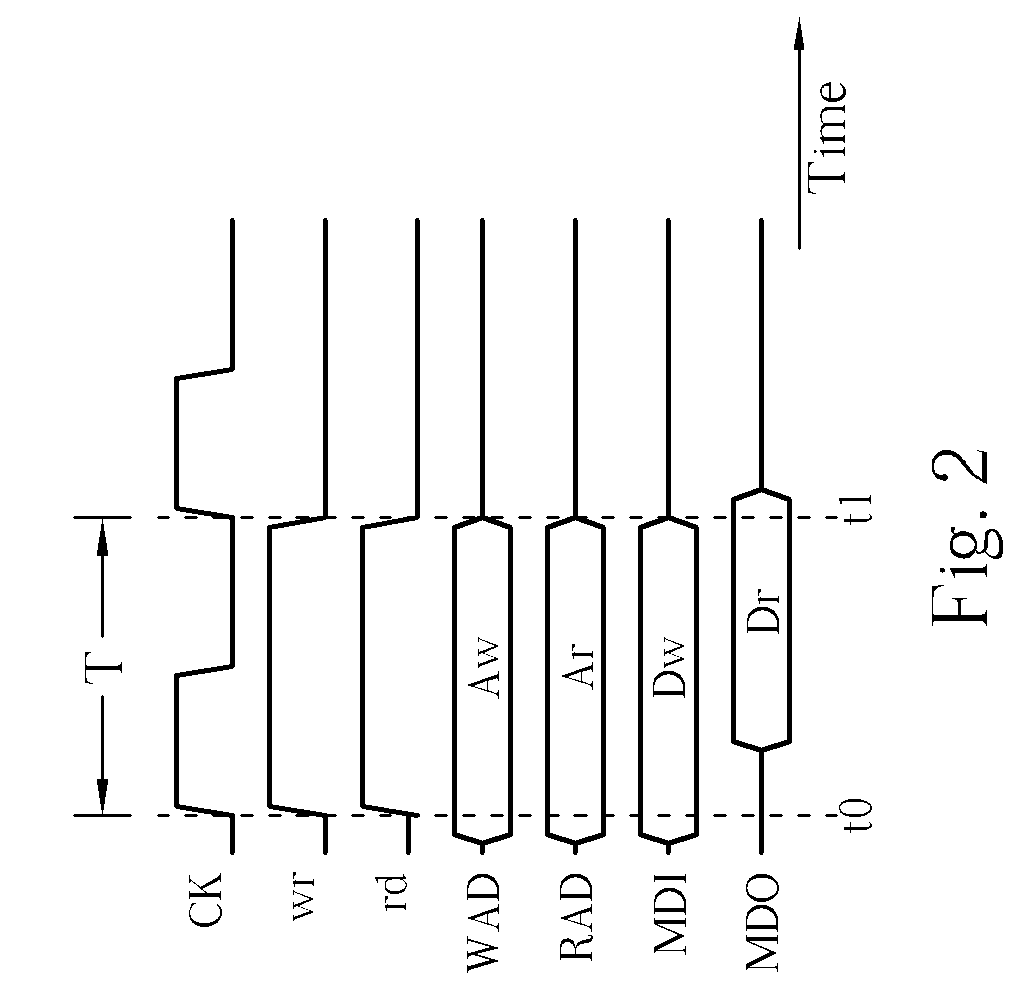

Method And Related Apparatus For Realizing Two-Port Synchronous Memory Device

Method and related apparatus for realizing a two-port synchronous memory device with a single-port memory. Clock-triggered two-port synchronous memory device can synchronously receive reading and writing commands within a clock period to simultaneous execute these two commands, while a single port memory must execute a single reading and writing command sequentially. Since a single-port memory features a lower cost and a smaller layout area, the invention realizes a two-port synchronous memory device by making a single-port memory first execute one of the reading / writing commands and then the other command within a single clock period, such that the two commands are completed after a single clock period. Thus a two-port synchronous memory device can be realized with a single-port memory.

Owner:VIA TECH INC

Slide rail structure

ActiveUS20120141053A1Smooth slidingLow costServersSliding contact bearingsEngineeringMechanical engineering

A slide rail structure includes a first rail, a second rail, a third rail, and two bearing seats including bearings. The bearing seat is disposed between the first rail and the second rail. The second rail is received between the first rail and the third rail. The second rail slides relative to the first rail via the bearings. The third rail slidably contacts the second rail.

Owner:FULIAN PRECISION ELECTRONICS (TIANJIN) CO LTD

Markovian-sequence generator and new methods of generating Markovian sequences

ActiveUS8566258B2Extensive controlMore “costly”Mathematical modelsElectrophonic musical instrumentsConstraint satisfaction problemDSPACE

A new type of Markovian sequence generator and generation method generates a Markovian sequence having controllable properties, notably properties that satisfy at least one control criterion which is a computable requirement holding on items in the sequence. The Markovian sequence is generated chunkwise, each chunk containing a plurality of items in the sequence. During generation of each chunk a search is performed in the space of Markovian sequences to find a chunk-sized series of items which enables the control criterion to be satisfied. The search can be performed using a generate and test approach in which chunk-sized Markovian sequences are generated then tested for compliance with the requirement(s) of the control criteria. Alternatively, the search can be performed by formulating the sequence-generation task as a constraint satisfaction problem, with one or more constraints ensuring that the generated sequence is Markovian and one or more constraints enforcing the requirement(s) of the control criteria. The sequence generator can be used in an interactive system where a user specifies the control criterion via an inputting device (20).

Owner:SONY CORP