Patents

Literature

34results about How to "Effective instruction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Adaptive training system, method and apparatus

ActiveUS20150050623A1Effective instructionEffective trainingCosmonautic condition simulationsBatteries circuit arrangementsComputerized systemData memory

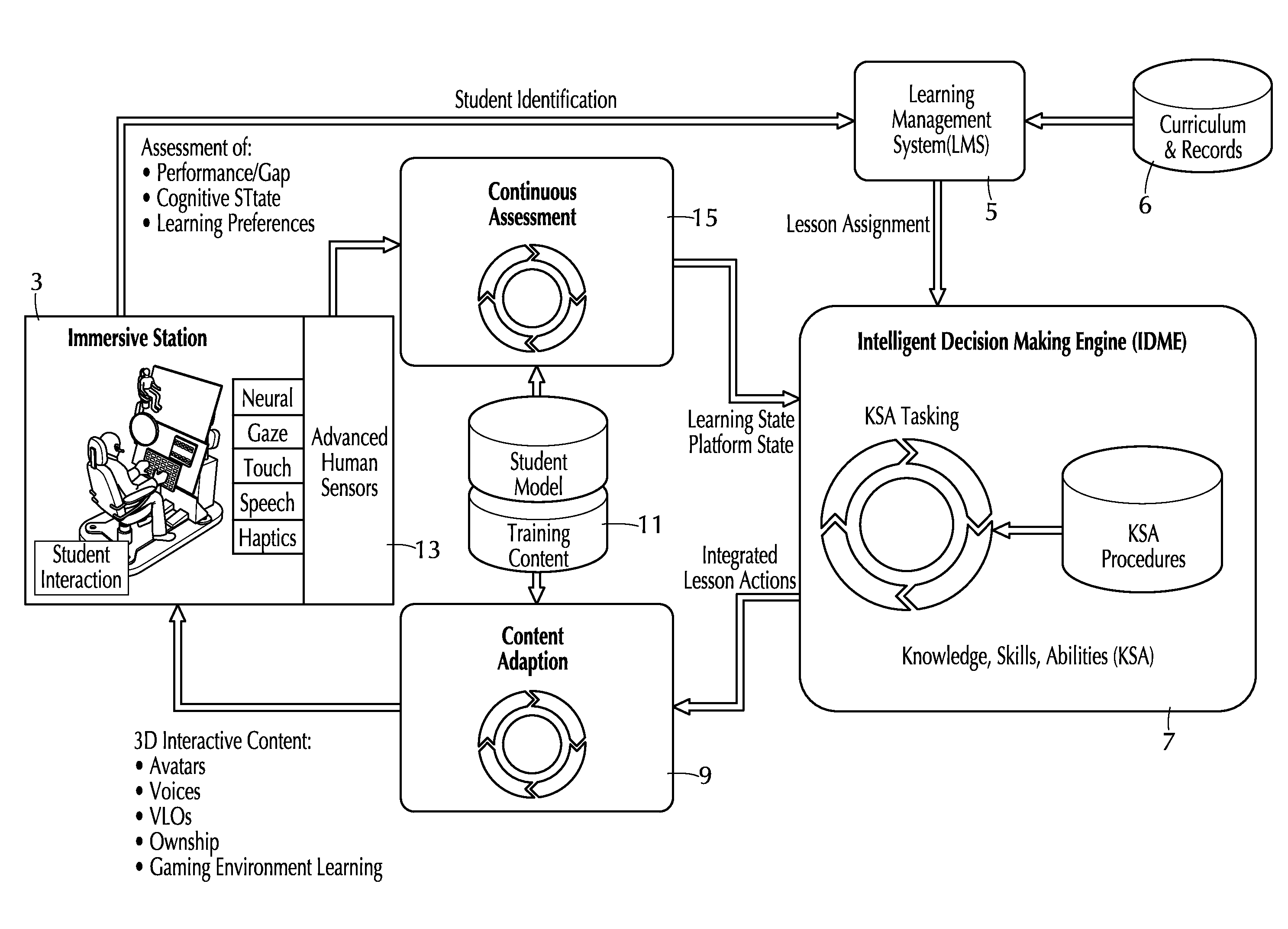

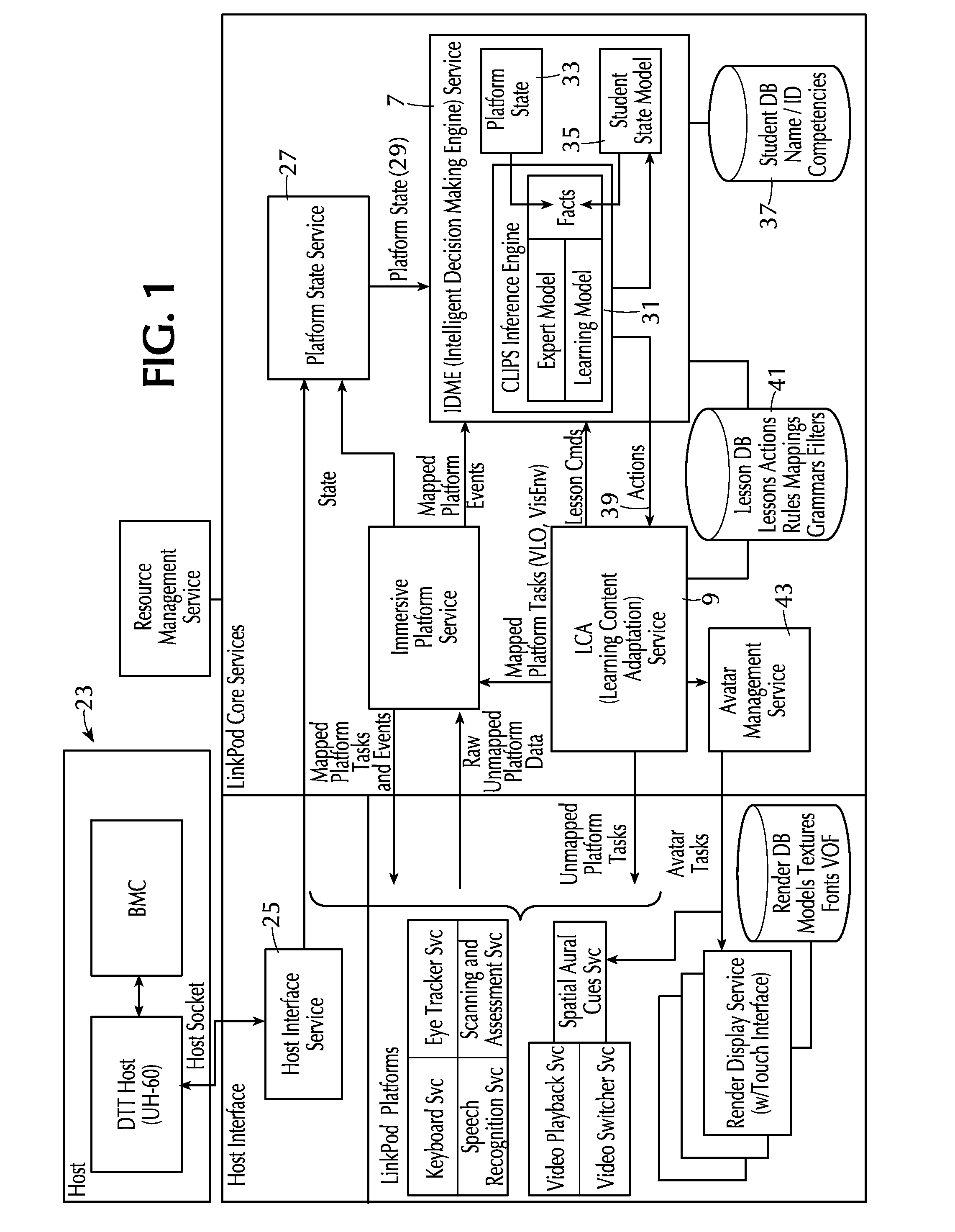

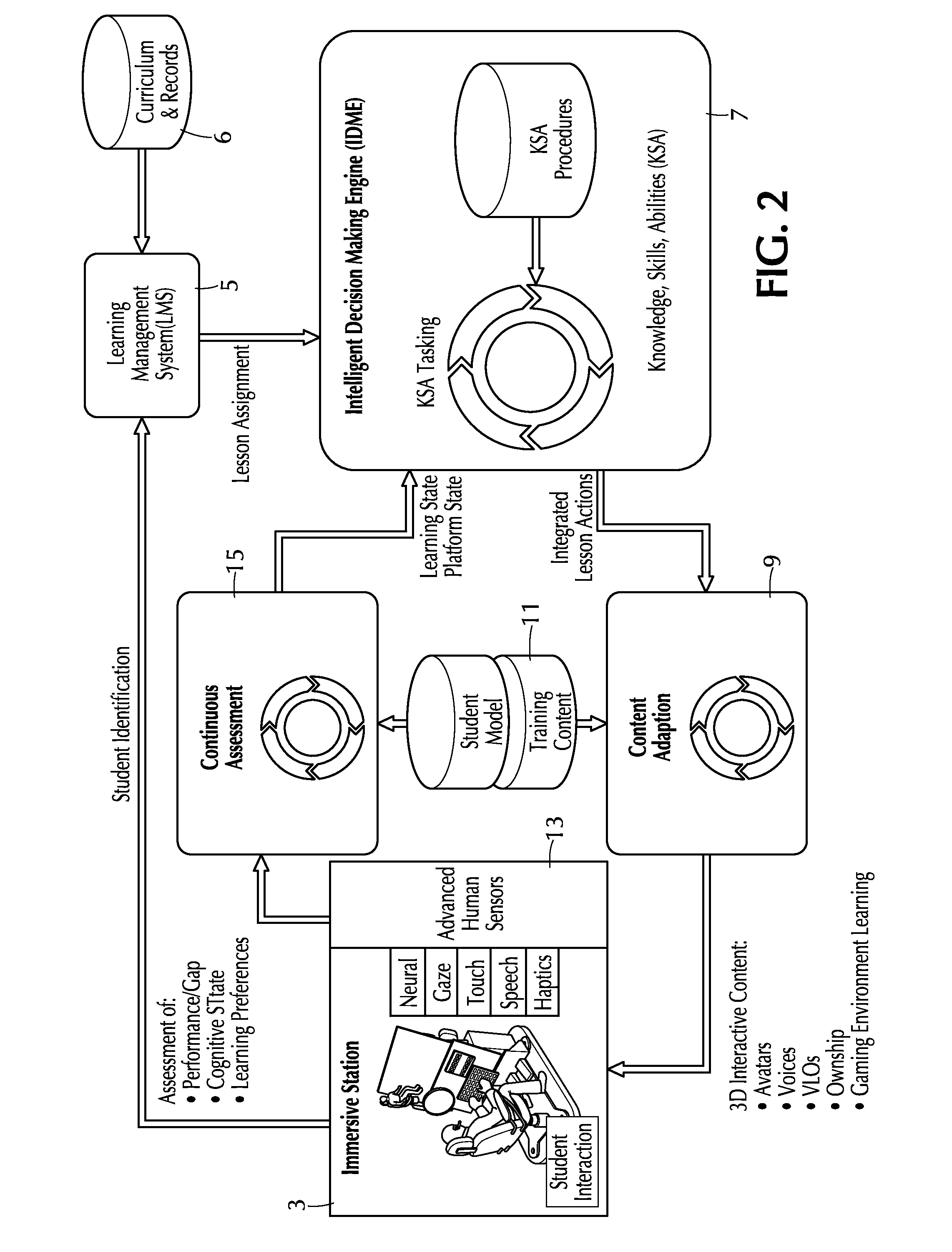

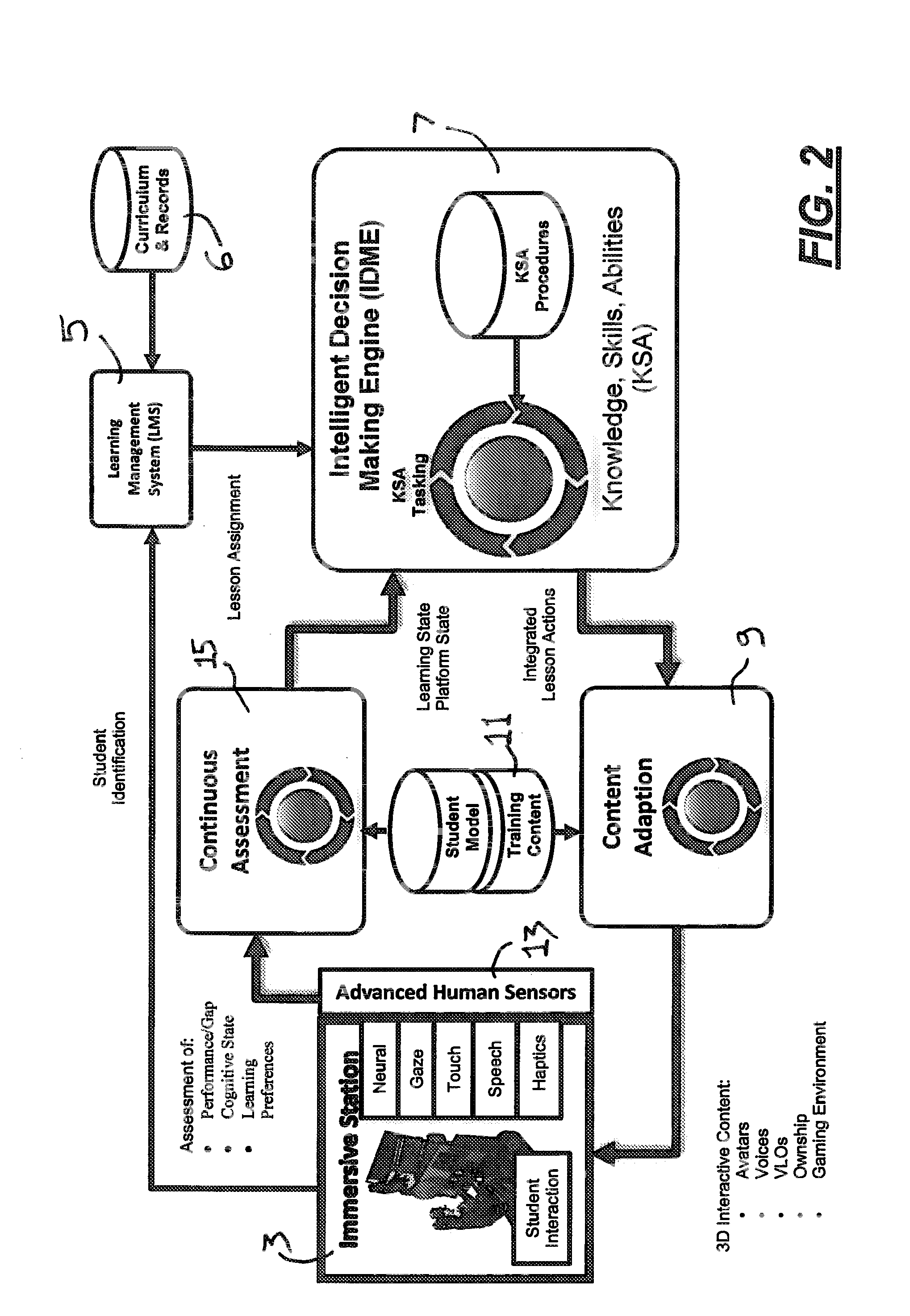

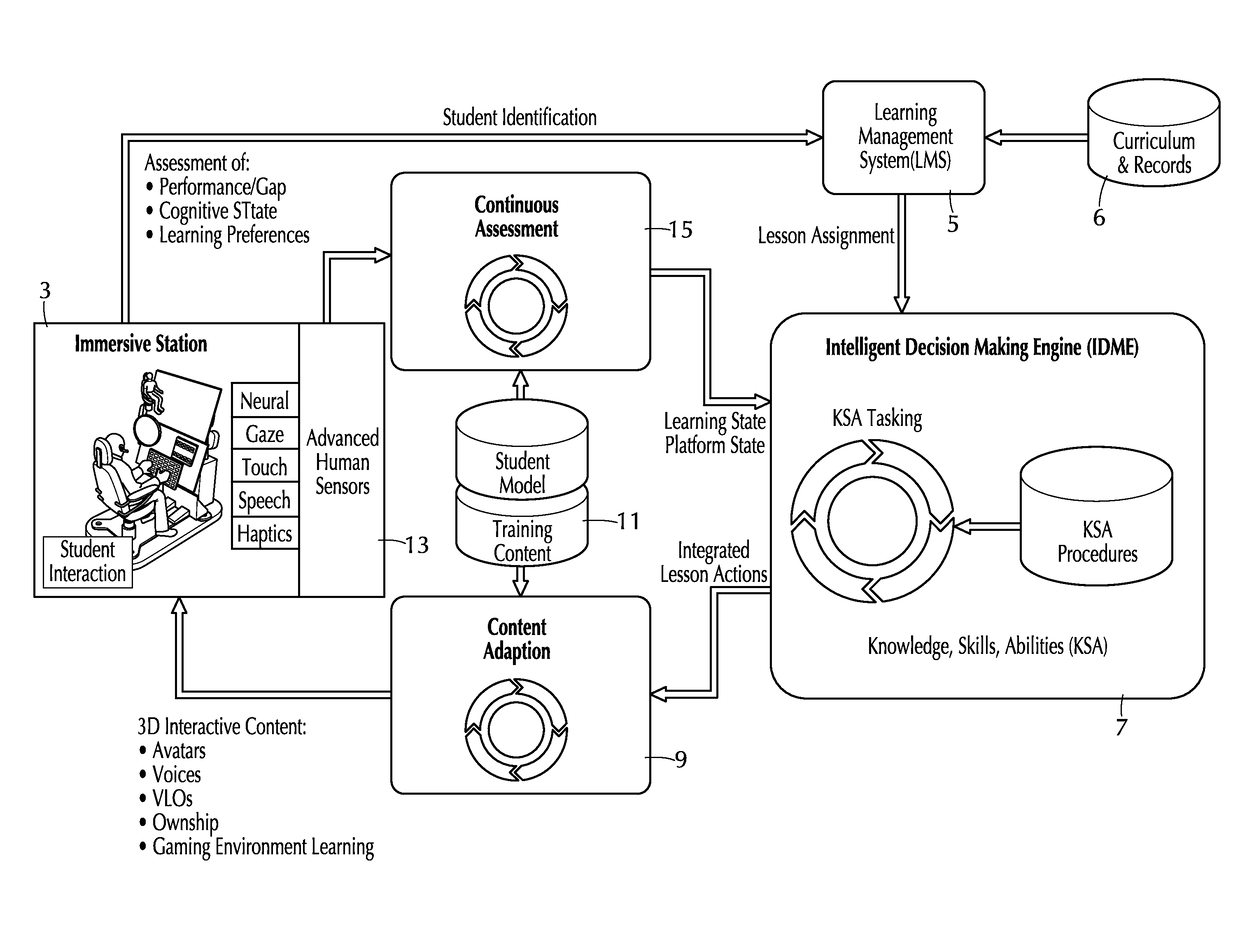

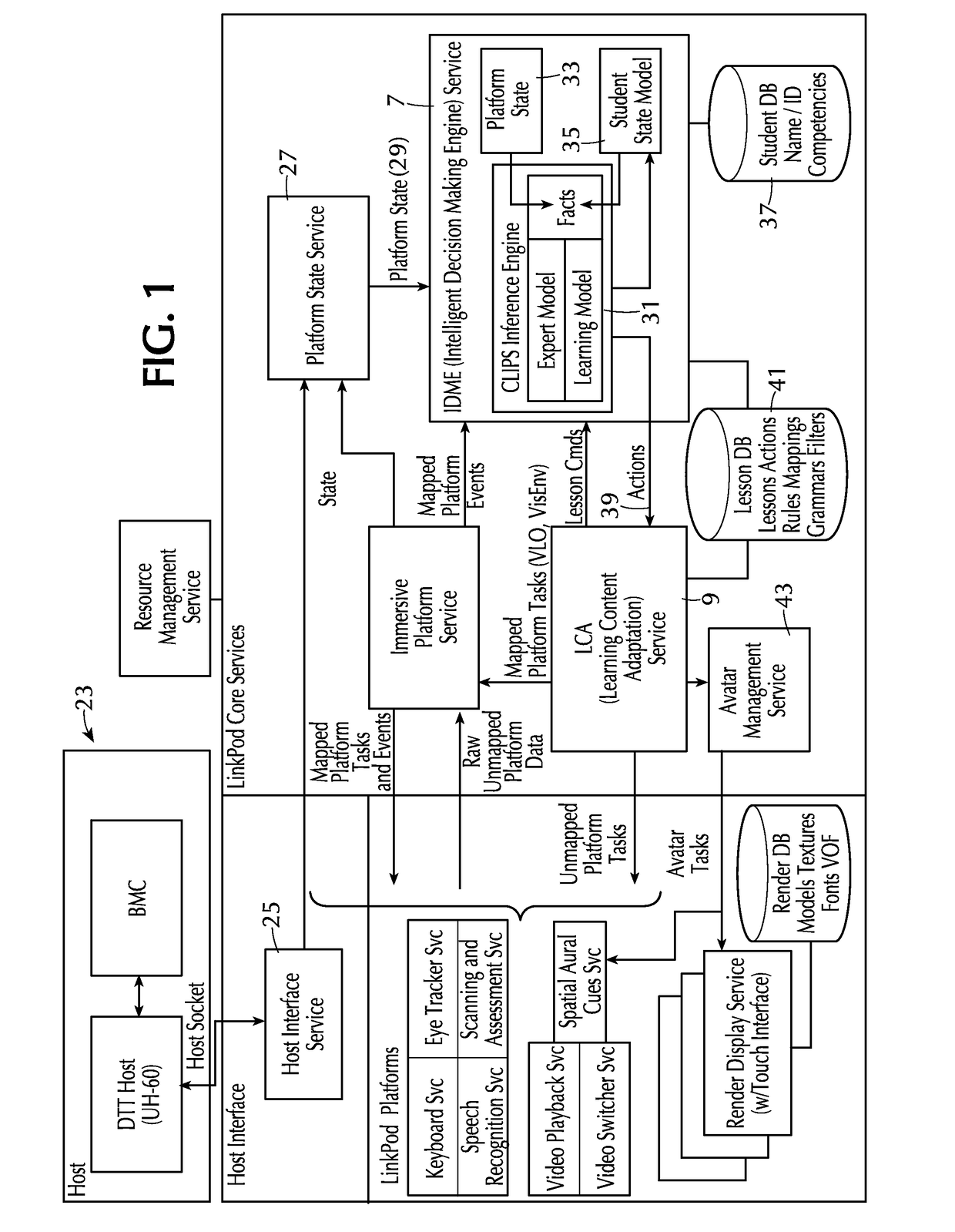

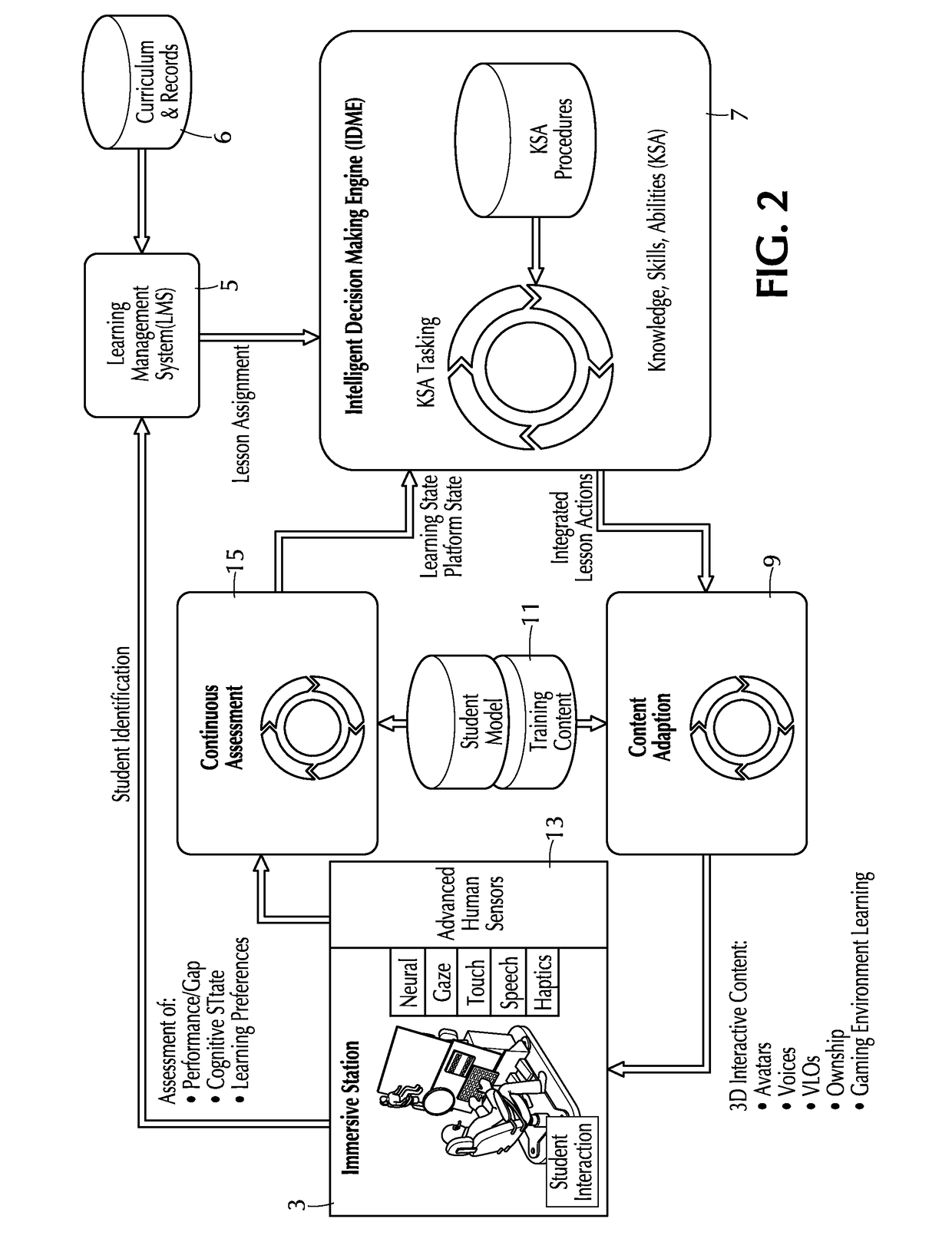

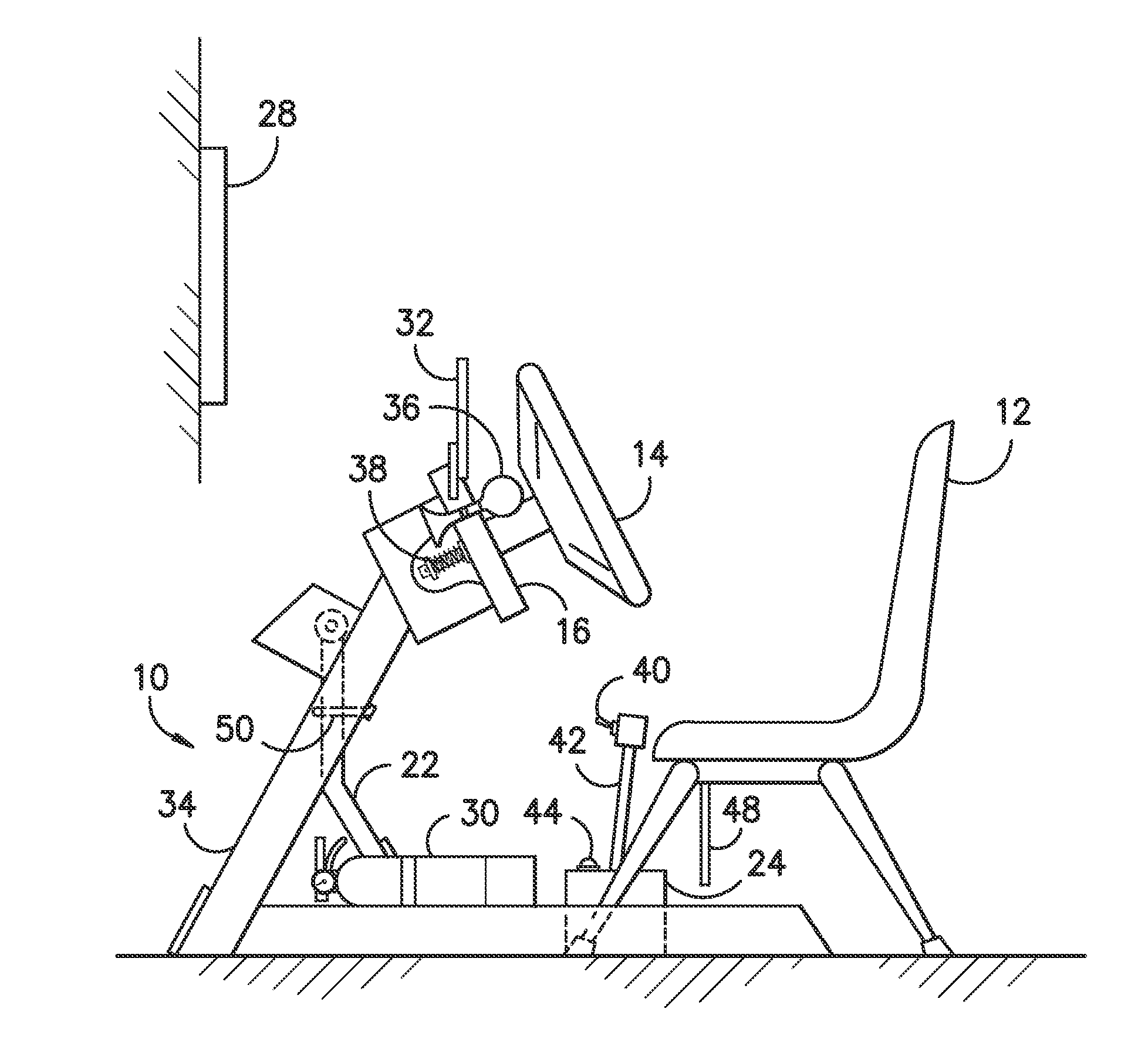

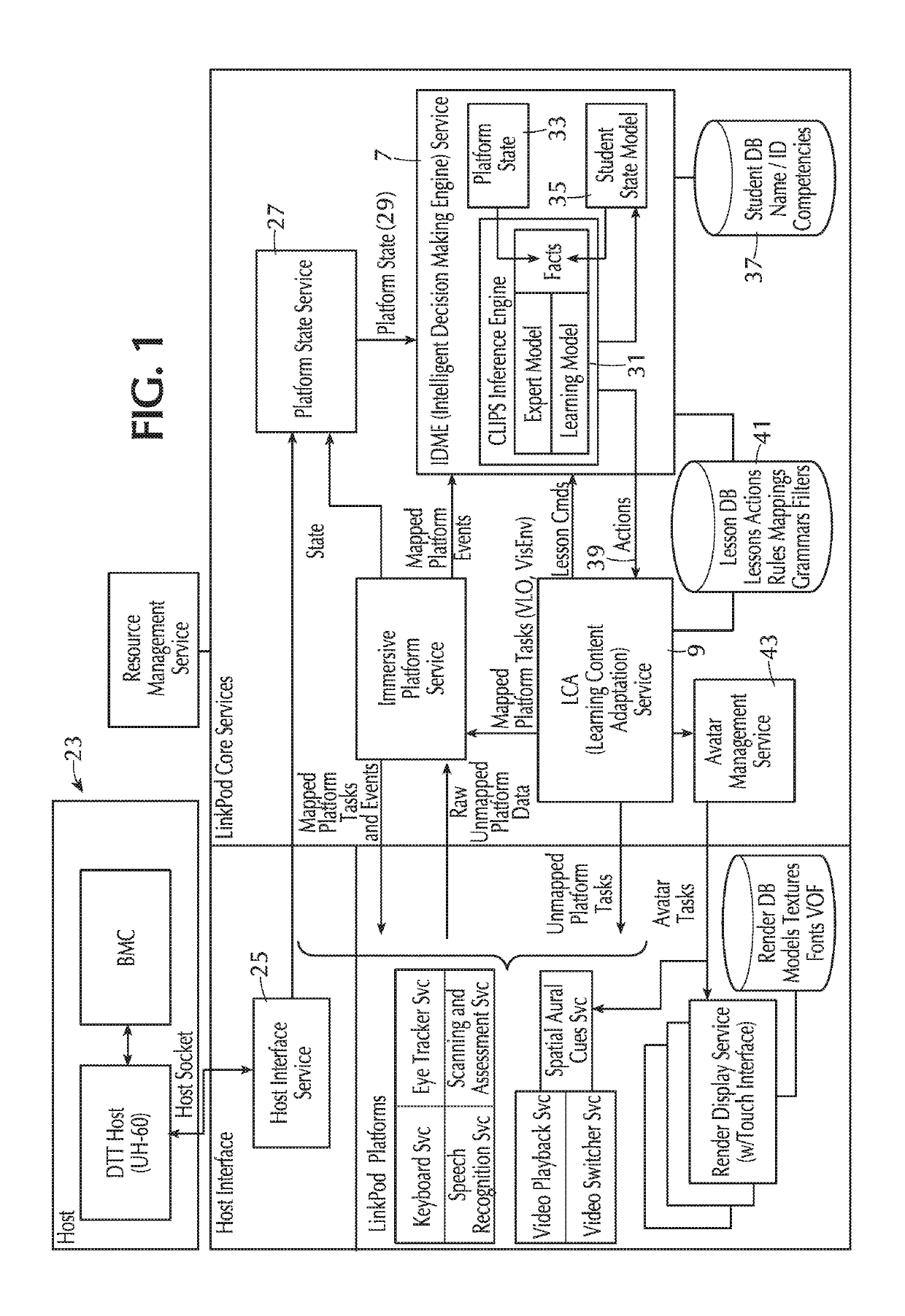

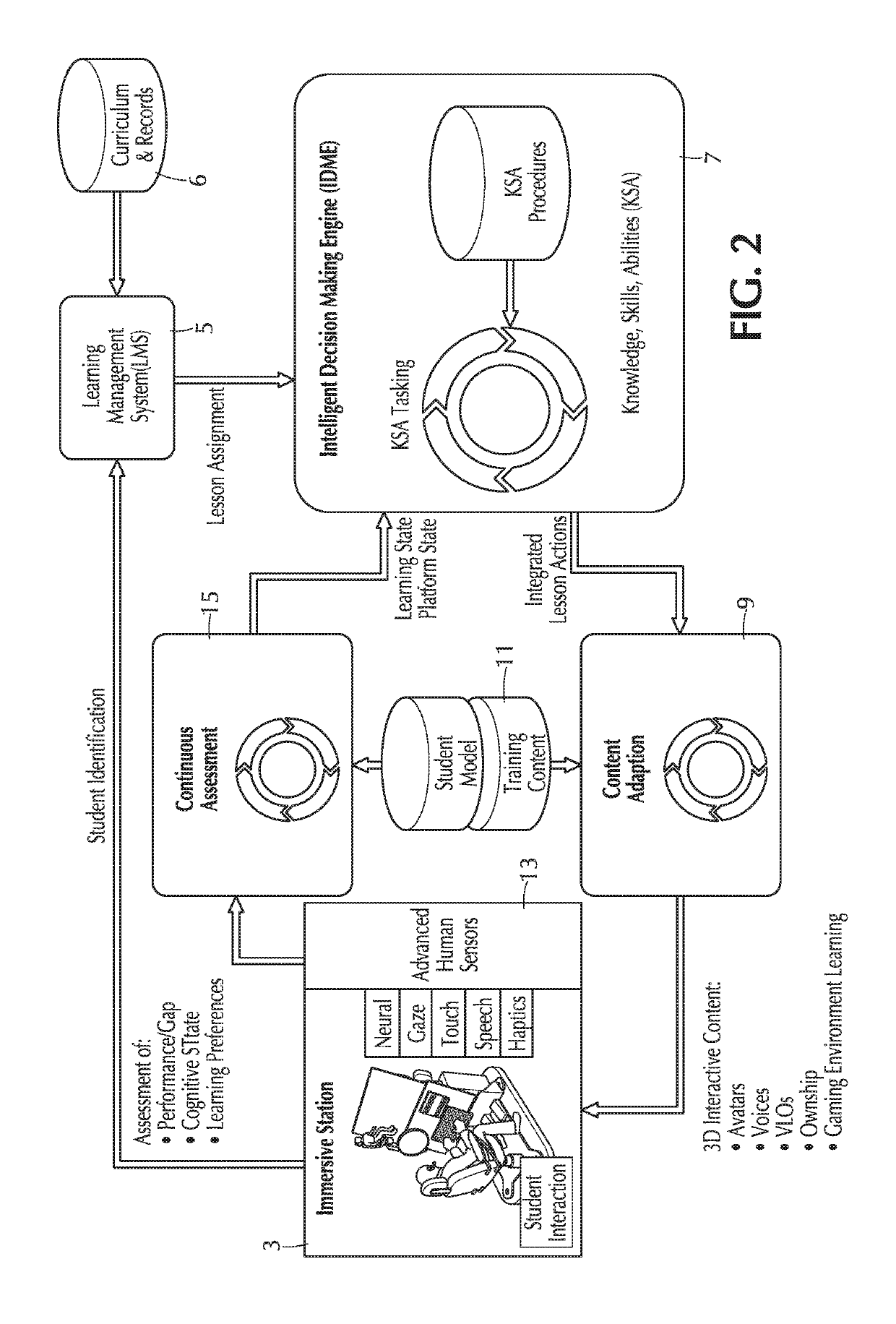

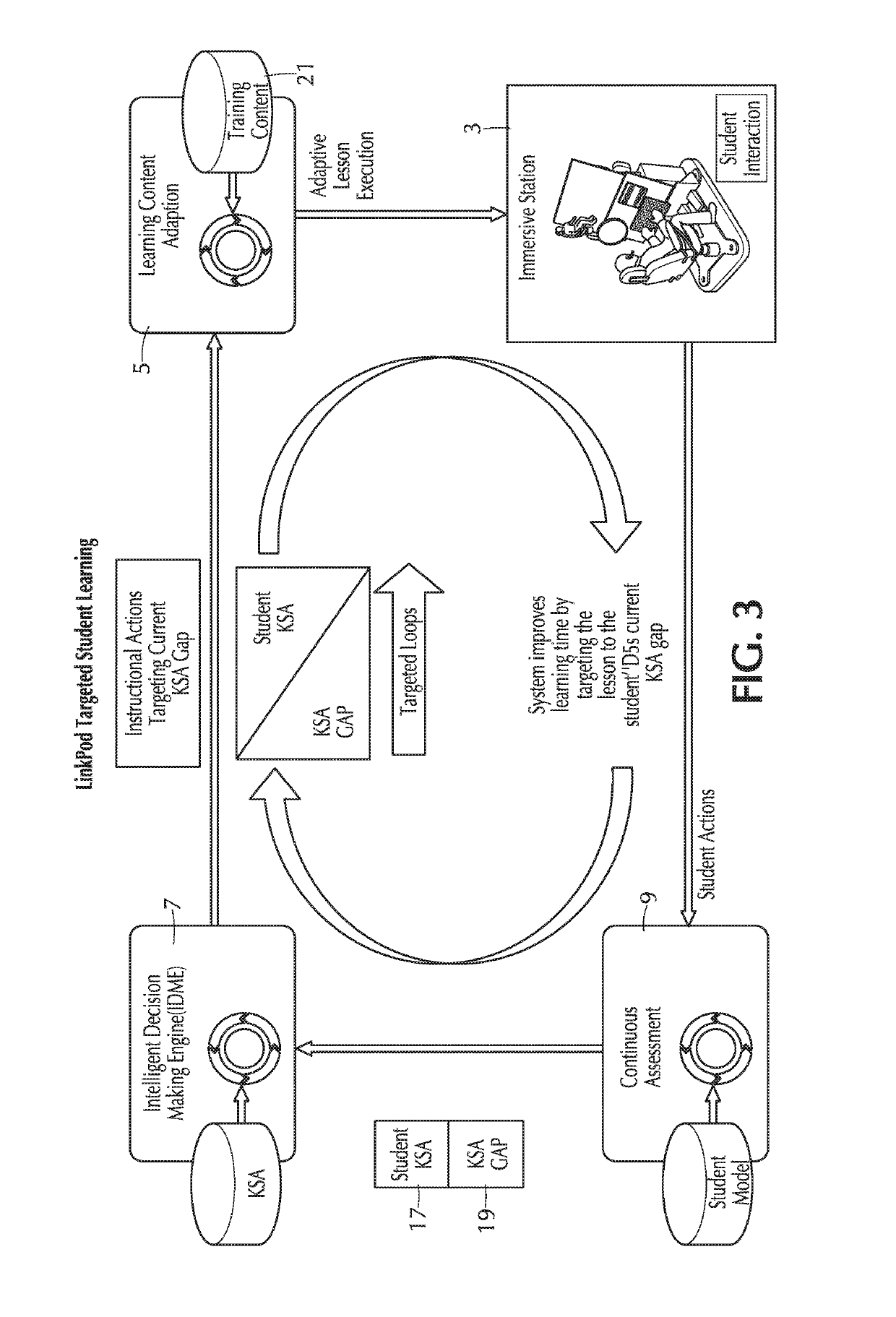

A system and method for training a student employ a simulation station that displays output to the student and receives input. The computer system has a rules engine operating on it and computer accessible data storage storing (i) learning object data including learning objects configured to provide interaction with the student at the simulation system and (ii) rule data defining a plurality of rules accessed by the rules engine. The rules data includes, for each rule, respective (a) if-portion data defining a condition of data and (o) then-portion data defining an action to be performed at the simulation station. The rules engine causes the computer system to perform the action when the condition of data is present in the data storage. For at least some of the rules, the action comprises output of one of the learning objects so as to interact with the student. The system may be networked with middleware and adapters that map data received over the network to rules engine memory.

Owner:CAE USA INC

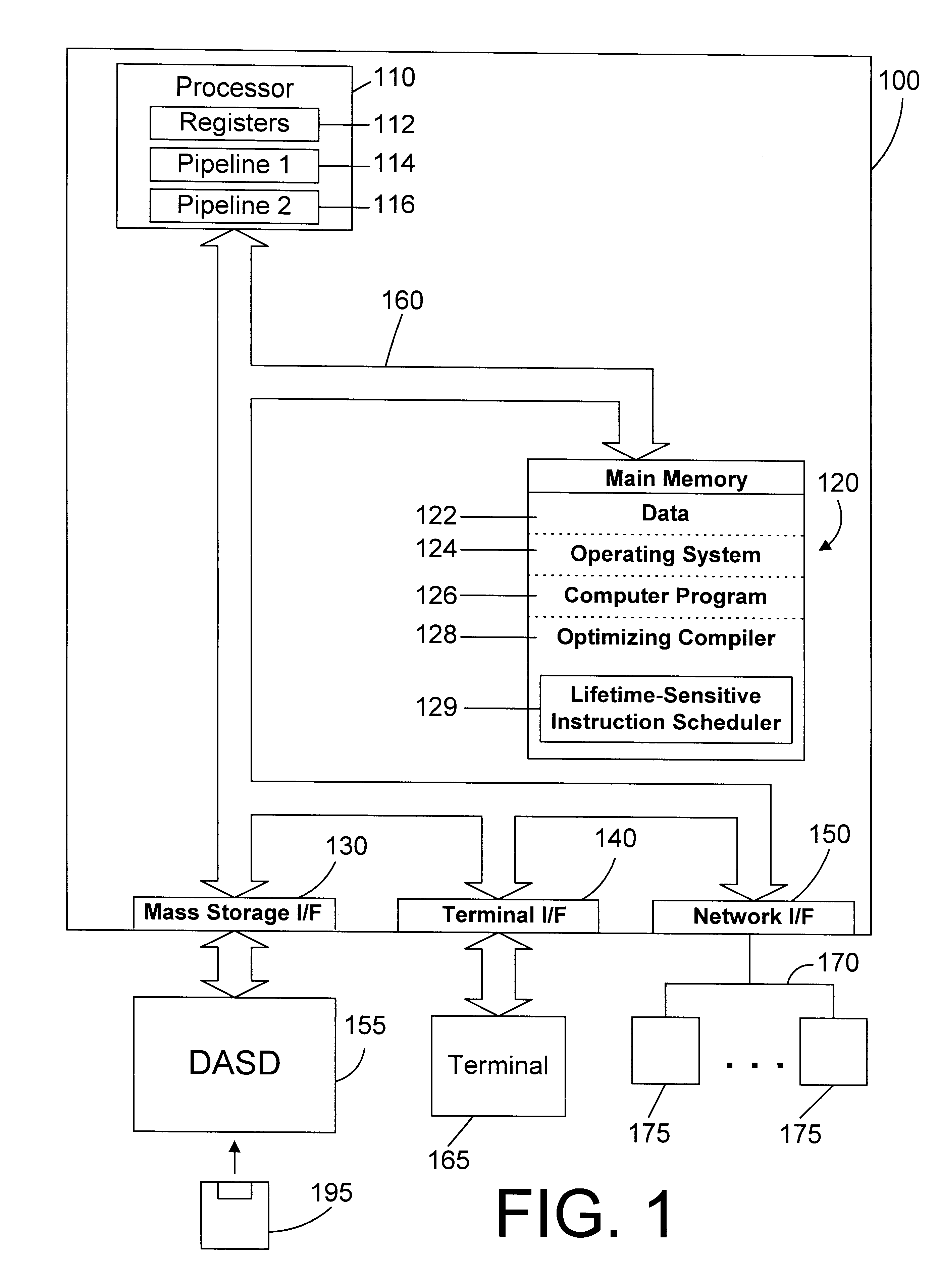

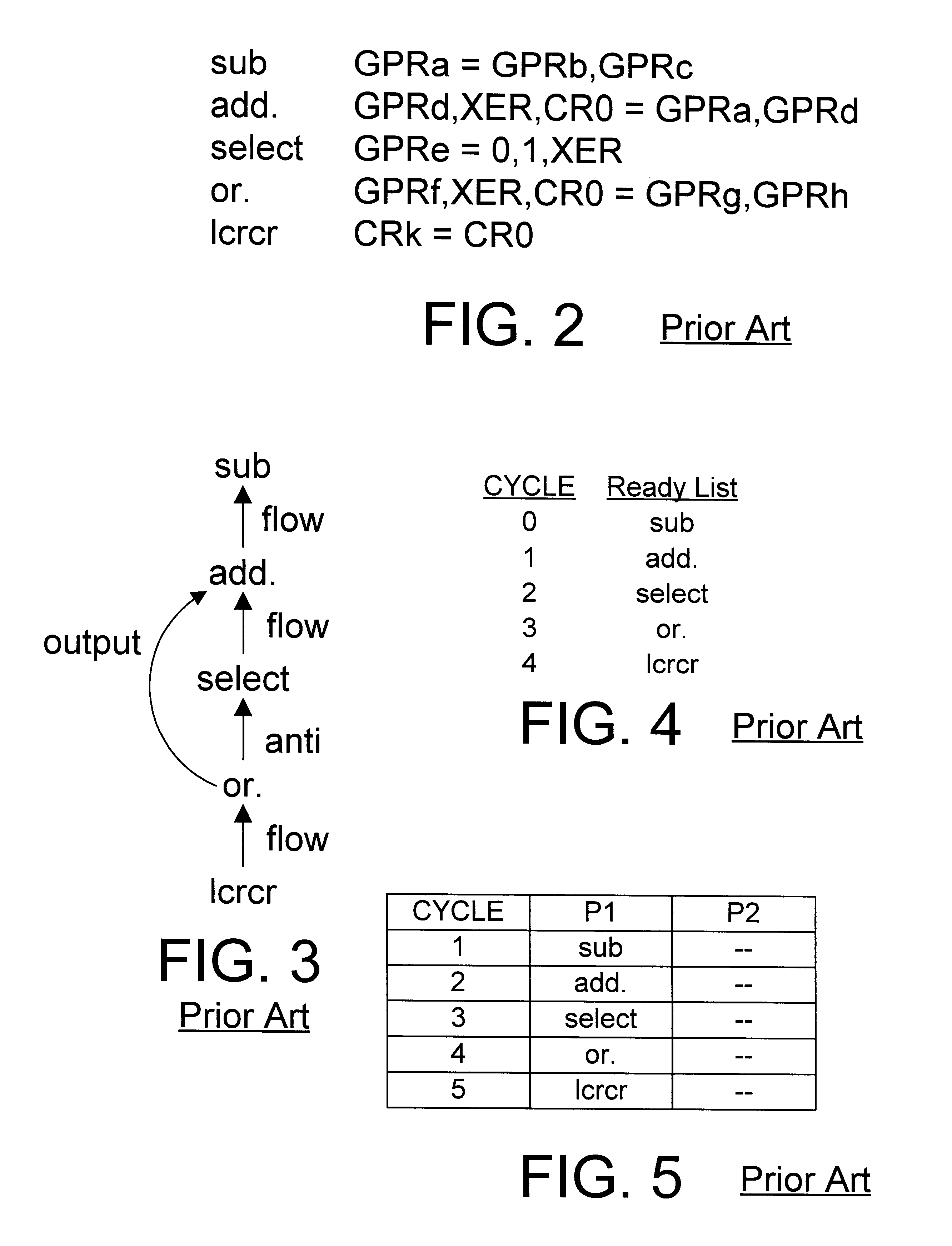

Lifetime-sensitive instruction scheduling mechanism and method

InactiveUS6305014B1Effective instructionHigh degree of parallelismSoftware engineeringSpecific program execution arrangementsScheduling instructionsDegree of parallelism

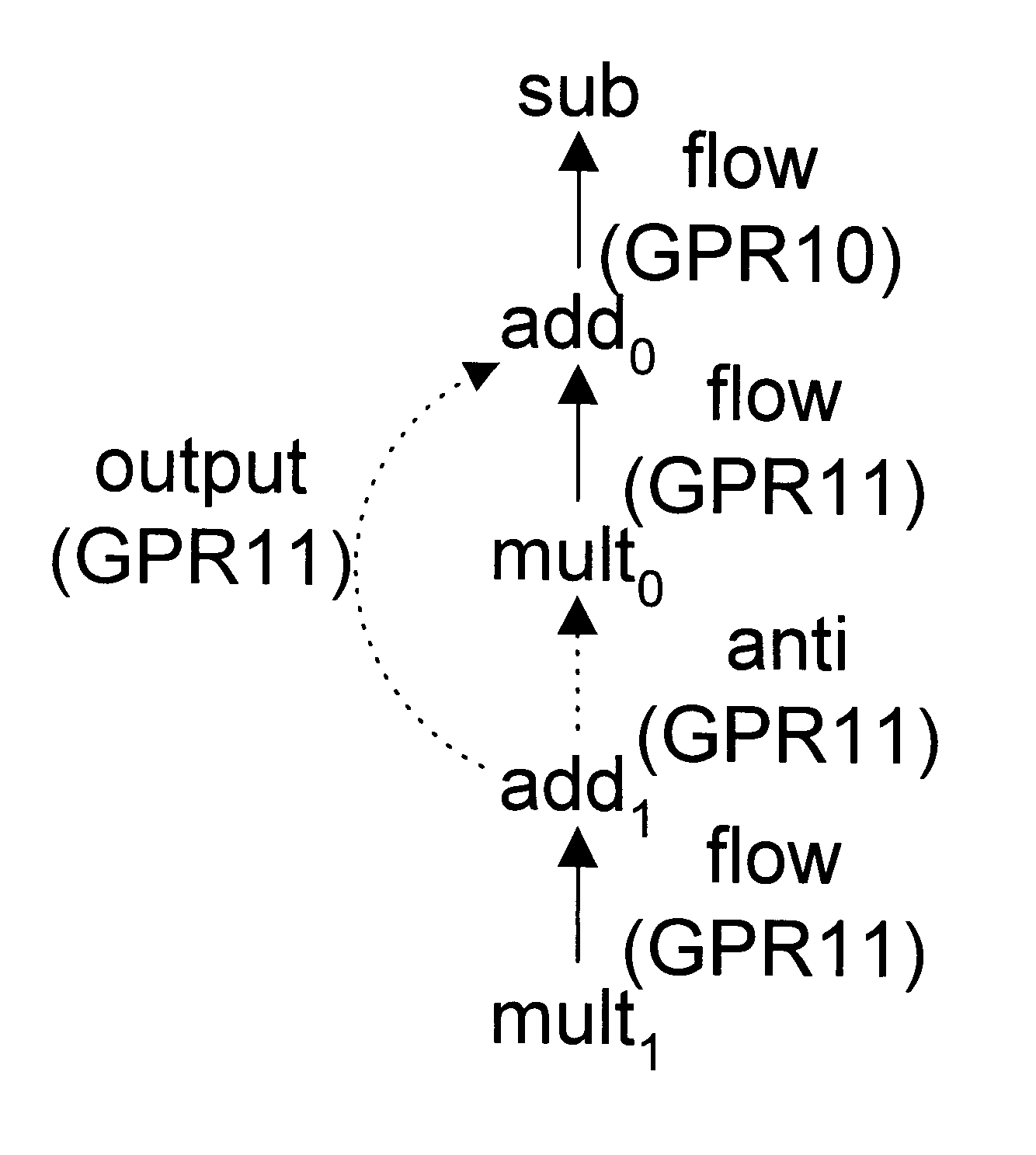

An instruction scheduler in an optimizing compiler schedules instructions in a computer program by determining the lifetimes of fixed registers in the computer program. By determining the lifetimes of fixed registers, the instruction scheduler can achieve a schedule that has a higher degree of parallelism by relaxing dependences between instructions in independent lifetimes of a fixed register so that instructions can be scheduled earlier than would otherwise be possible if those dependences were precisely honored.

Owner:IBM CORP

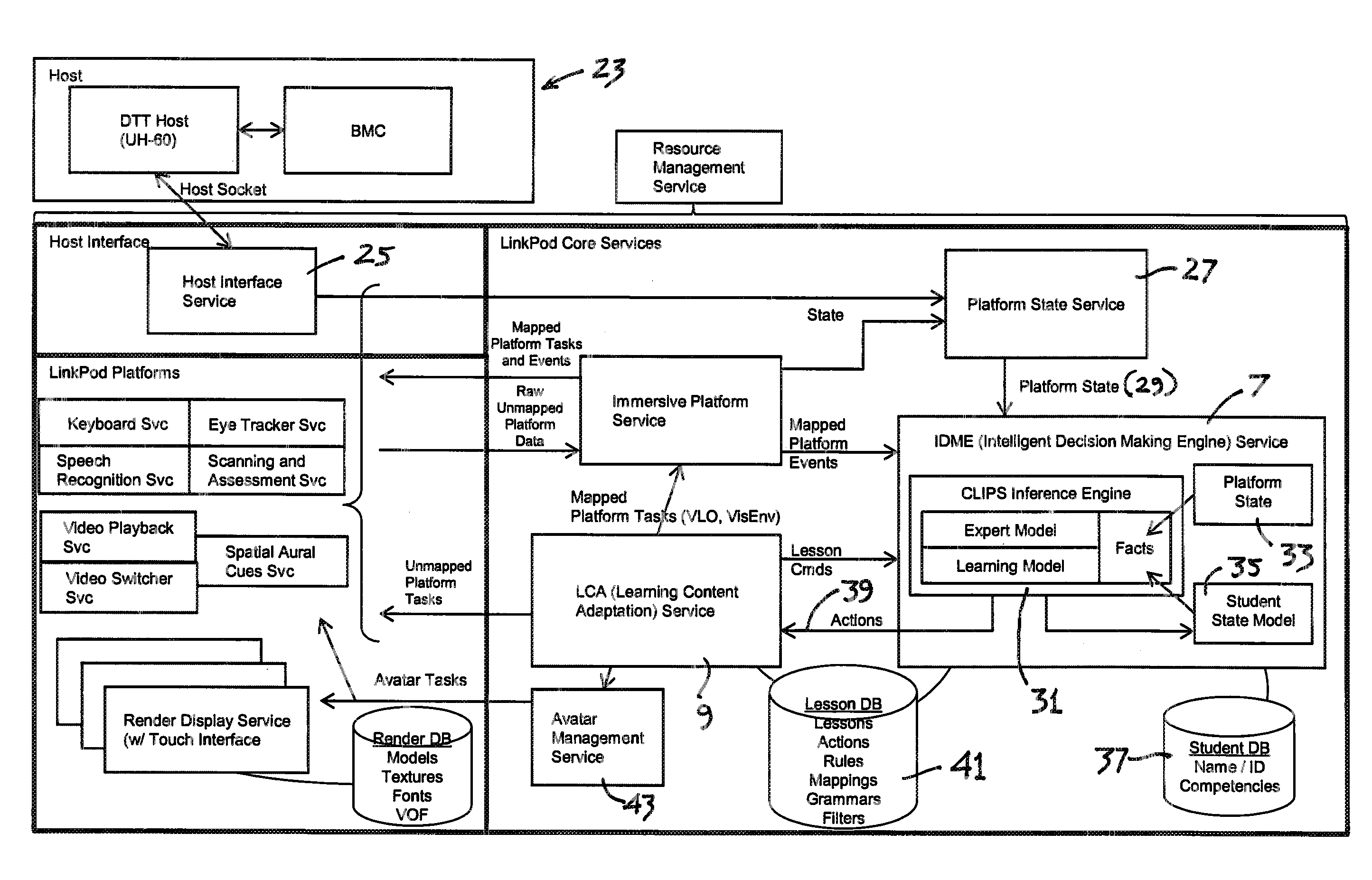

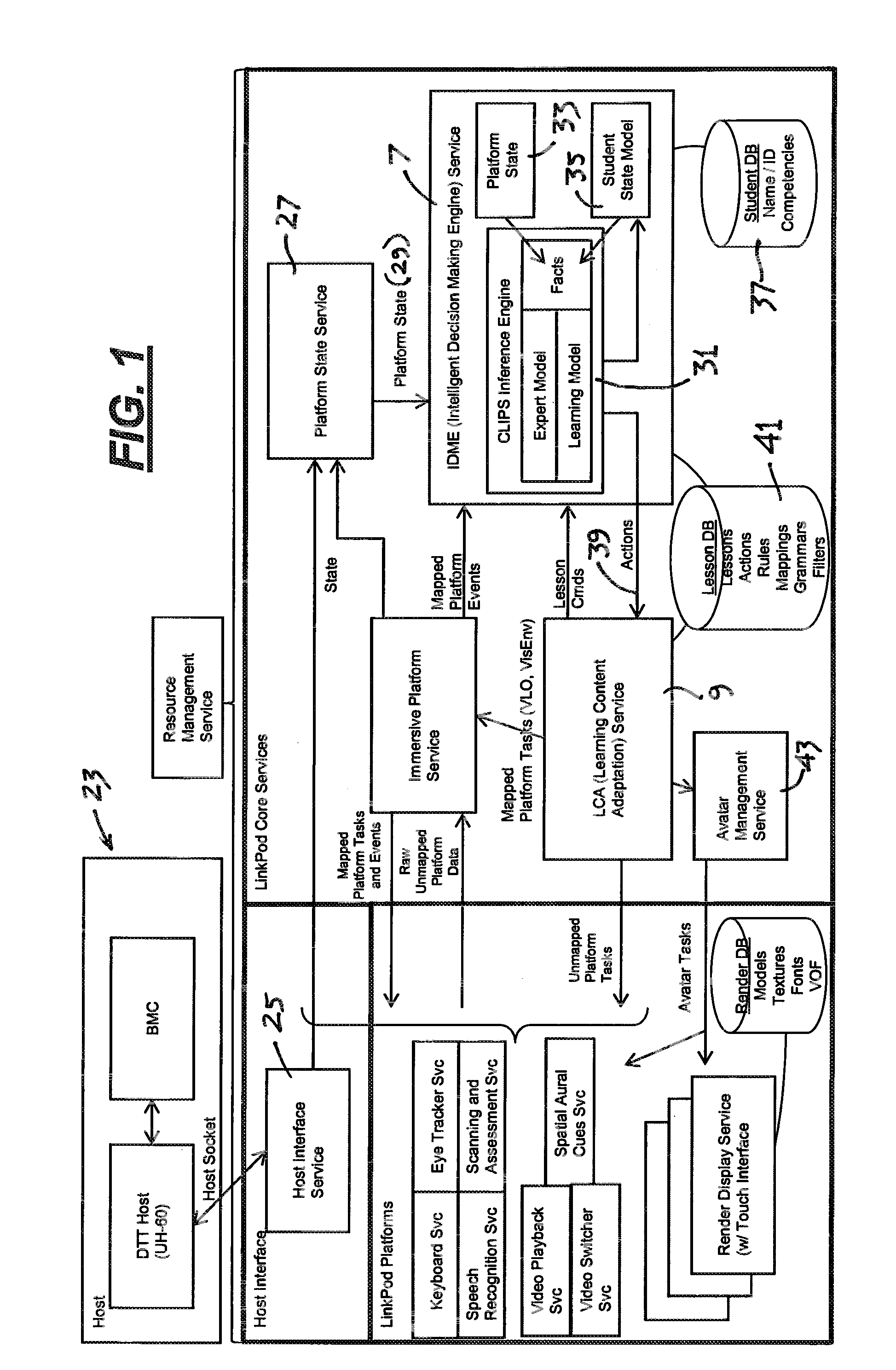

Adaptive training system, method, and apparatus

ActiveUS20140186810A1Effective instructionEffective trainingElectrical appliancesSimulatorsAdaptive learningComputerized system

A system and method for training a student employ a simulation station that displays output to the student and receives input. The computer system has a rules engine operating on it and computer accessible data storage storing (i) learning object data including learning objects configured to provide interaction with the student at the simulation system and (ii) rule data defining a plurality of rules accessed by the rules engine. The rules data includes, for each rule, respective (a) if-portion data defining a condition of data and (b) then-portion data defining an action to be performed at the simulation station. The rules engine causes the computer system to perform the action when the condition of data is present in the data storage. For at least some of the rules, the action comprises output of one of the learning objects so as to interact with the student.

Owner:CAE USA INC

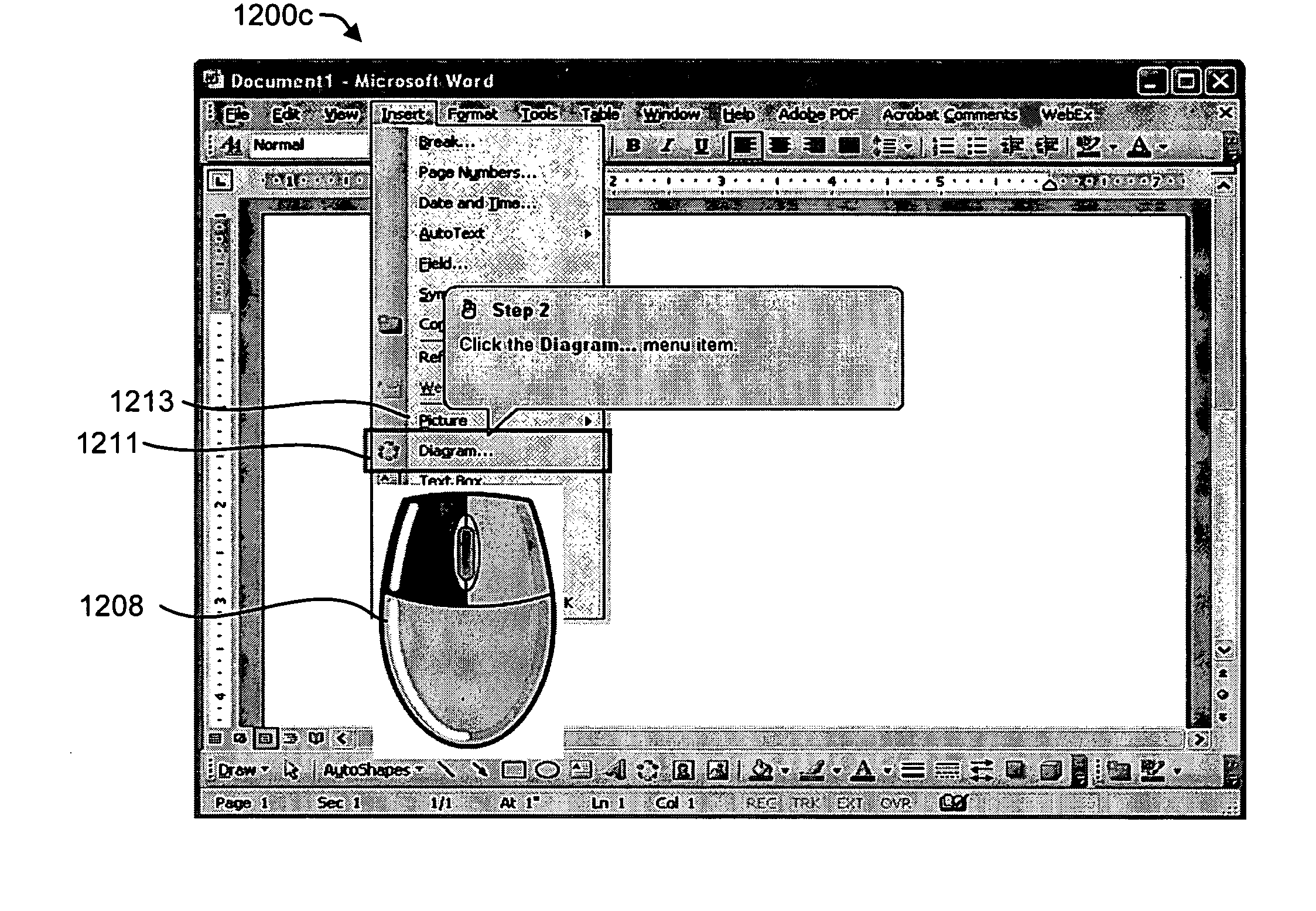

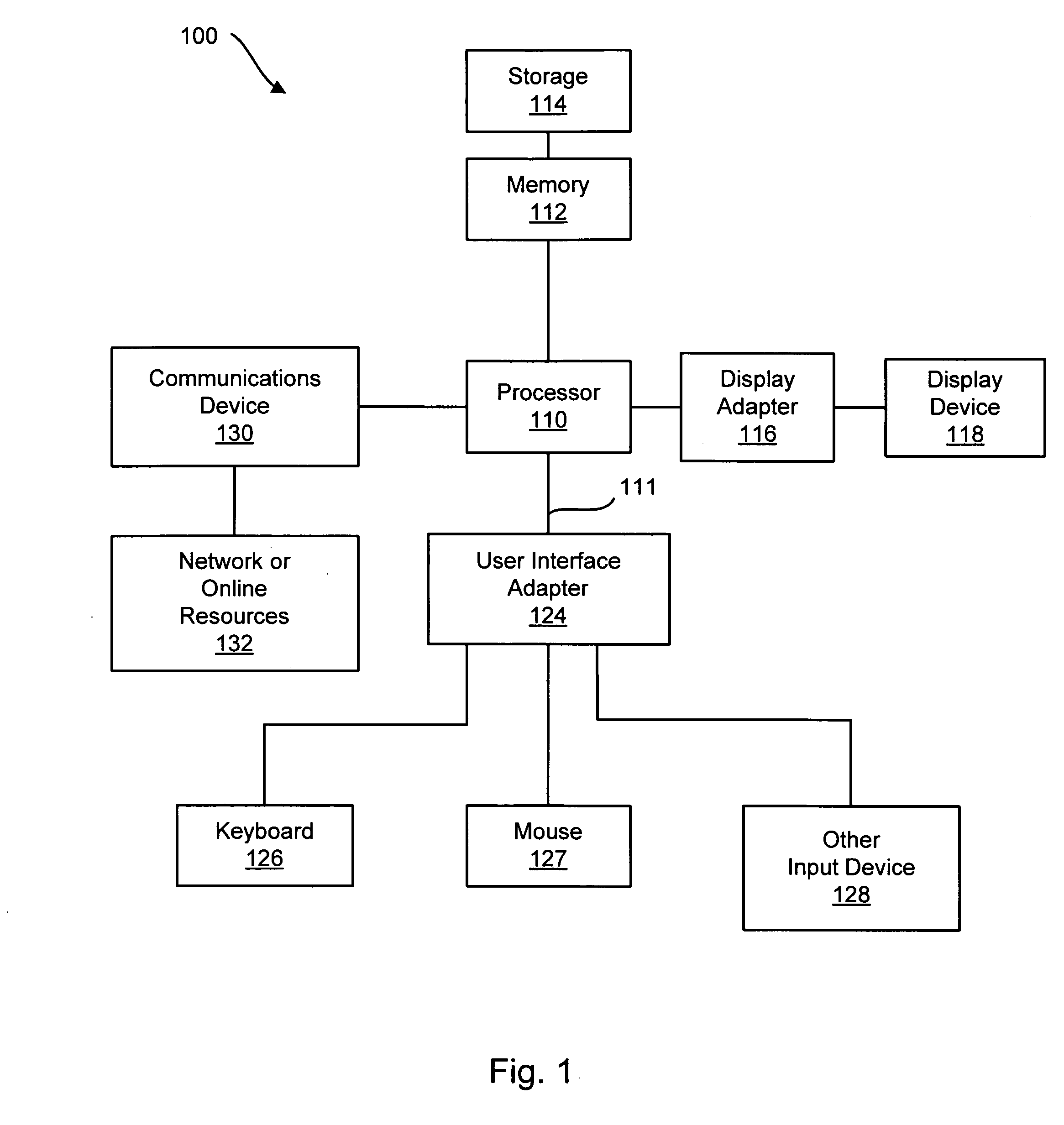

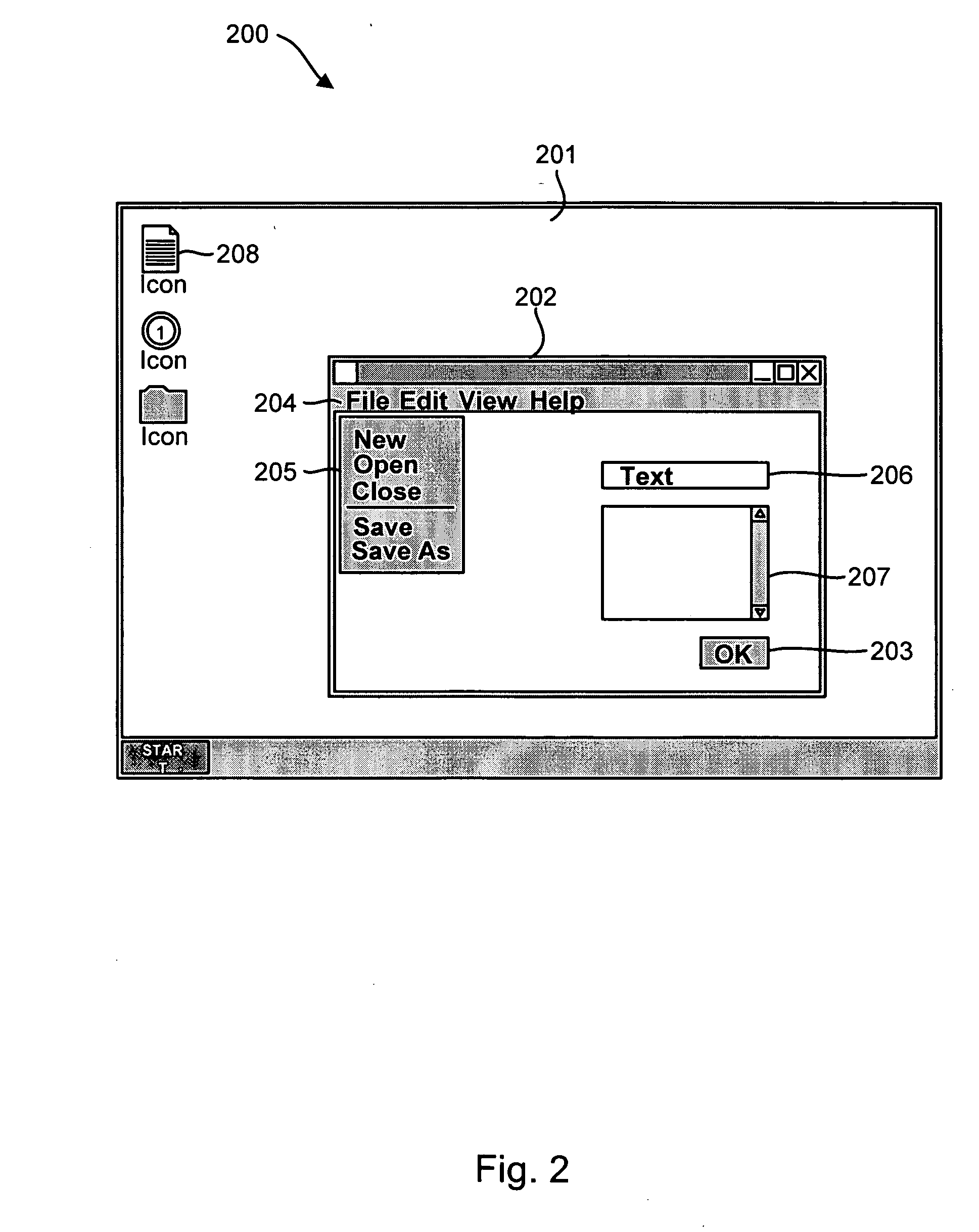

Systems and methods for teaching a person to interact with a computer program having a graphical user interface

InactiveUS20060053372A1Easy to implementEasy to useDigital computer detailsExecution for user interfacesGraphicsGraphical user interface

Systems and methods are disclosed for teaching a person how to perform a task within a computer program with at least one graphical user interface object. A script is formulated that contains step-by-step instructions indicating to a person how to perform a task within a computer program through interacting with at least one graphical user interface object of the computer program. The script is formulated by reference to an entity map, which contains programming instructions for accessing at least one graphical user interface object of the program to perform a step of the task. The script is executed by displaying a partial graphical overlay on top of an actual, non-simulated graphical user interface of the program. Each graphical user overlay instructs a user how to provide pertinent user input to graphical user interface objects of the computer program. The partial graphical overlay is positioned adjacent to the pertinent graphical user interface object of the program regardless of the position of that object without any reprogramming of the underlying computer program.

Owner:GUBLER MARION E

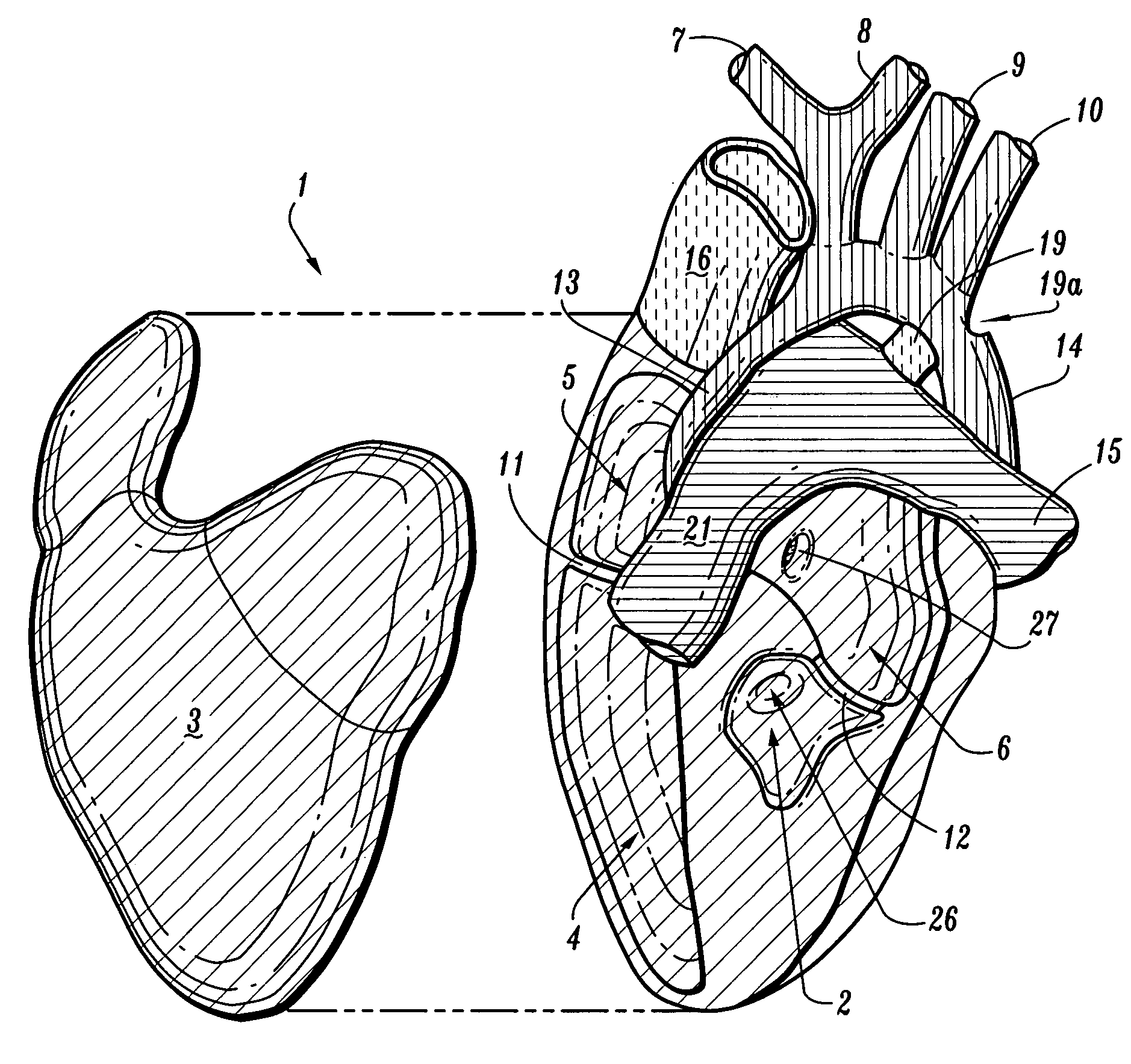

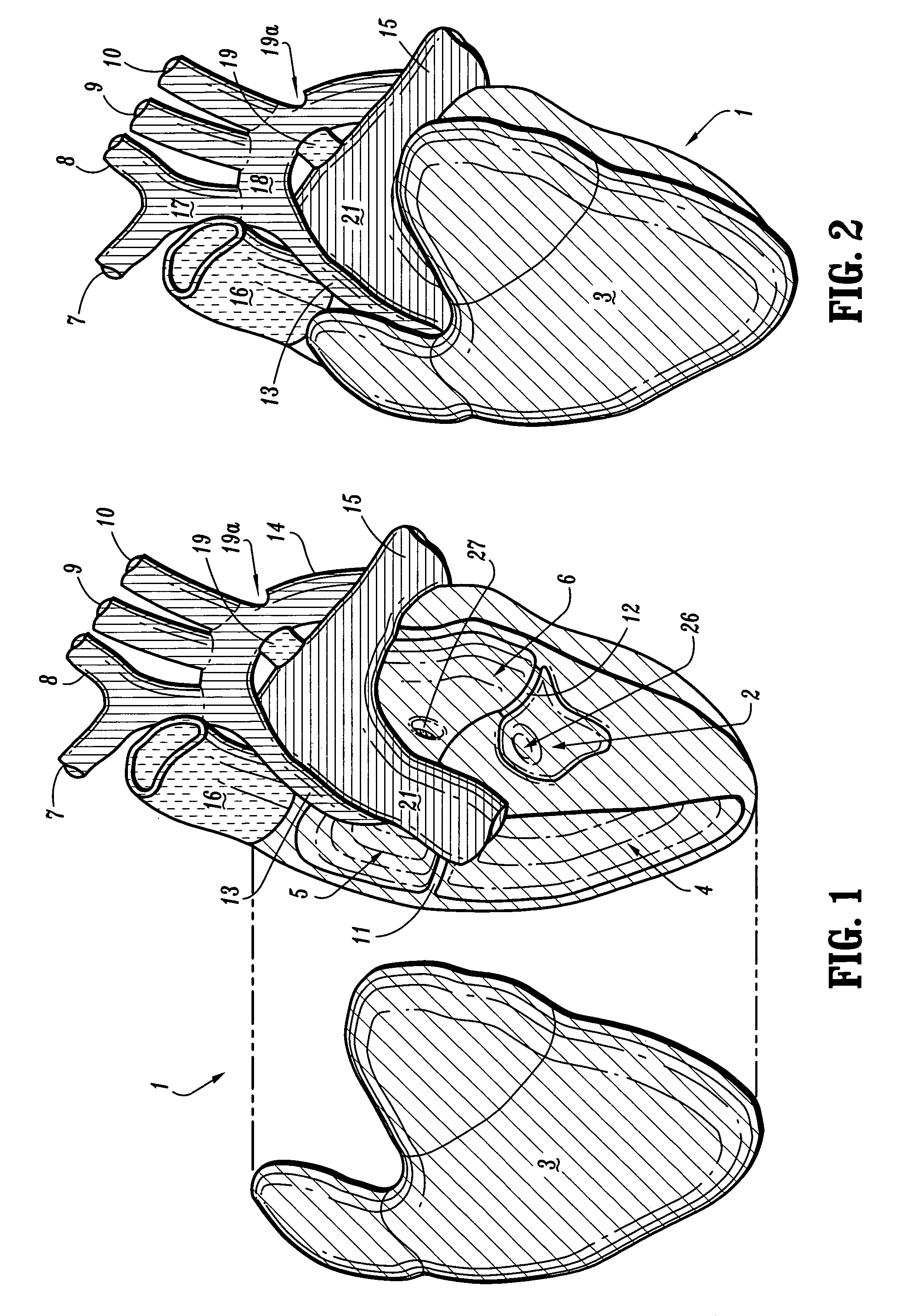

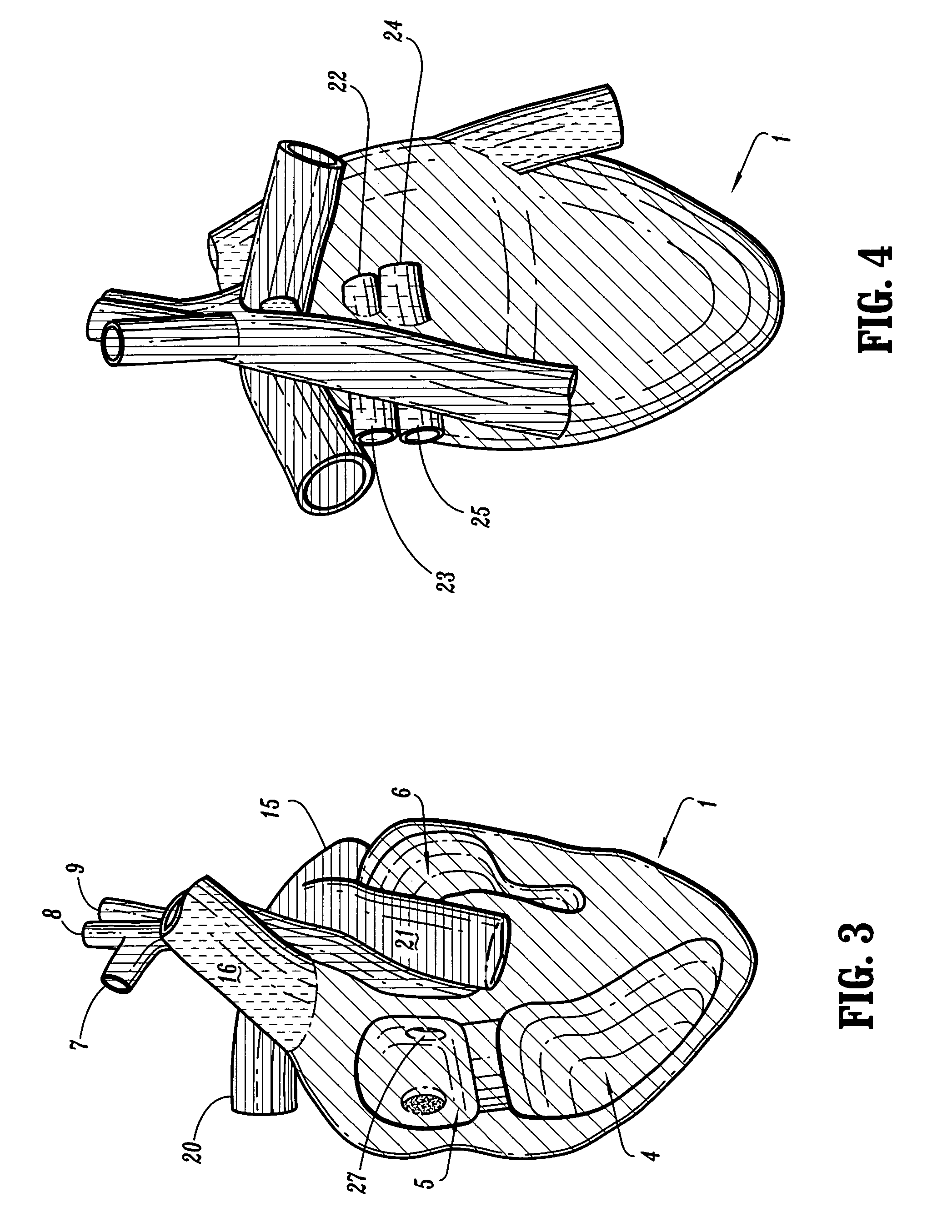

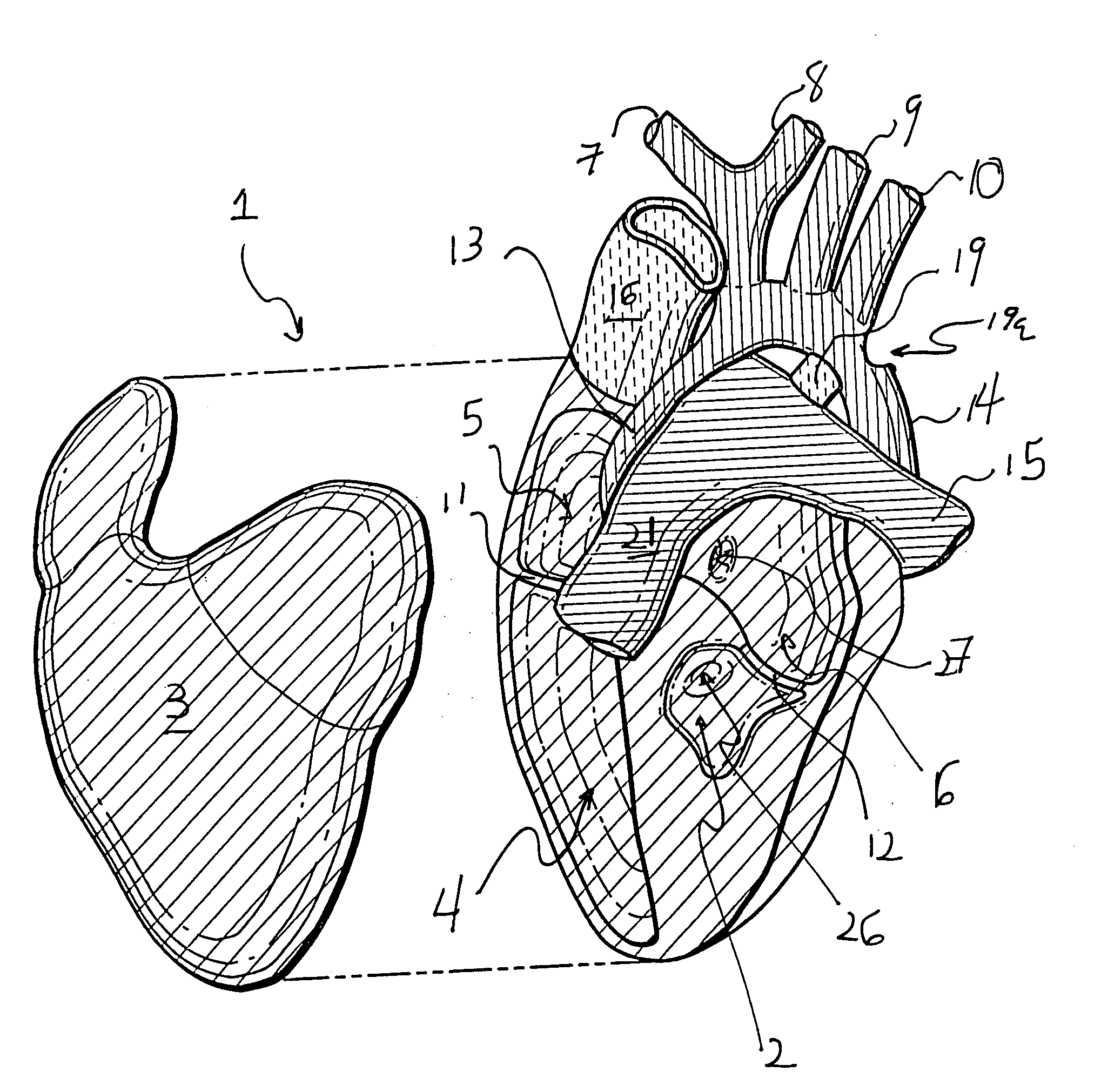

Pediatric congenital heart defect repair model

InactiveUS7083418B2Easy to understandImprove performanceEducational modelsBiomedical engineeringMedical treatment

Owner:BALBY BY DESIGN

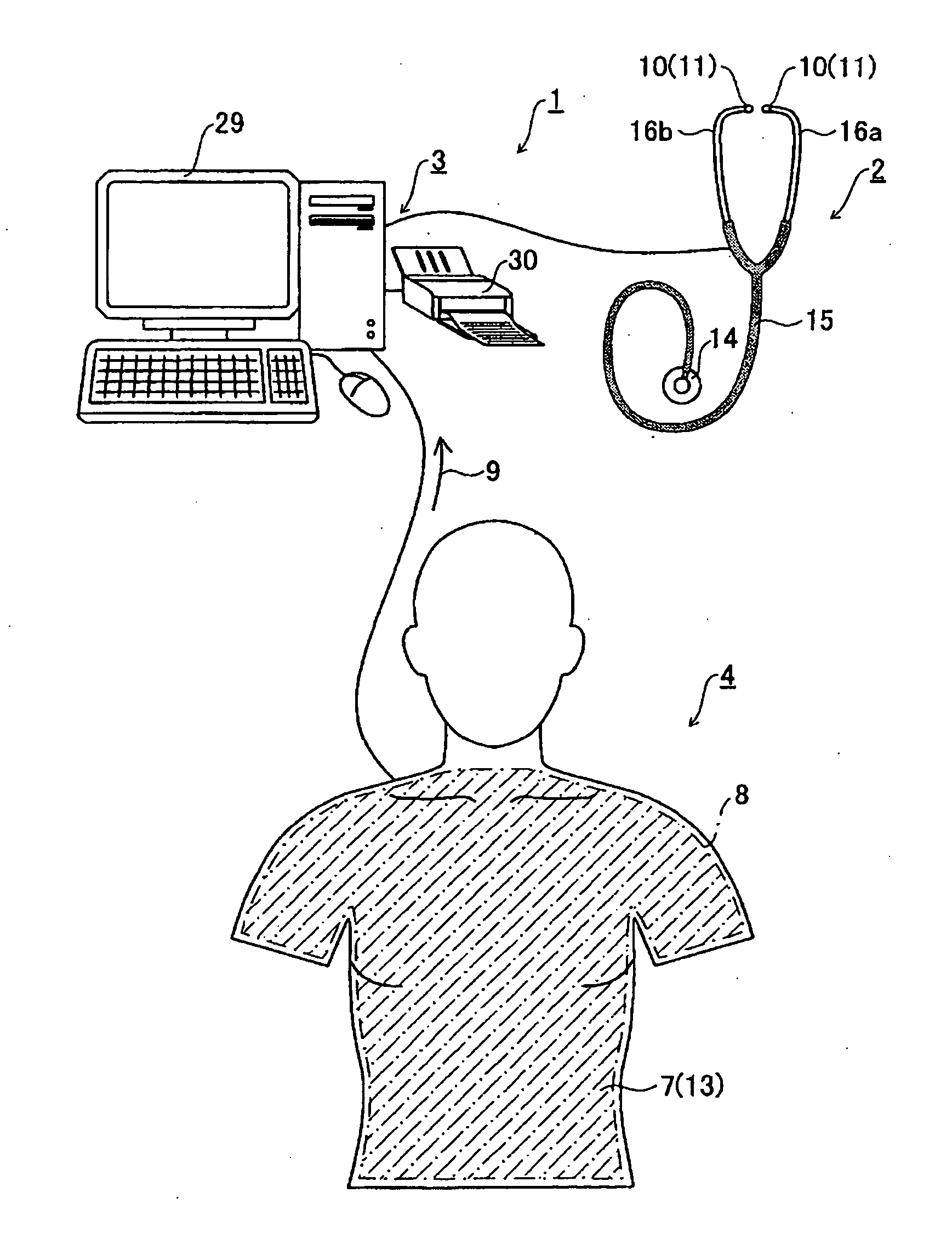

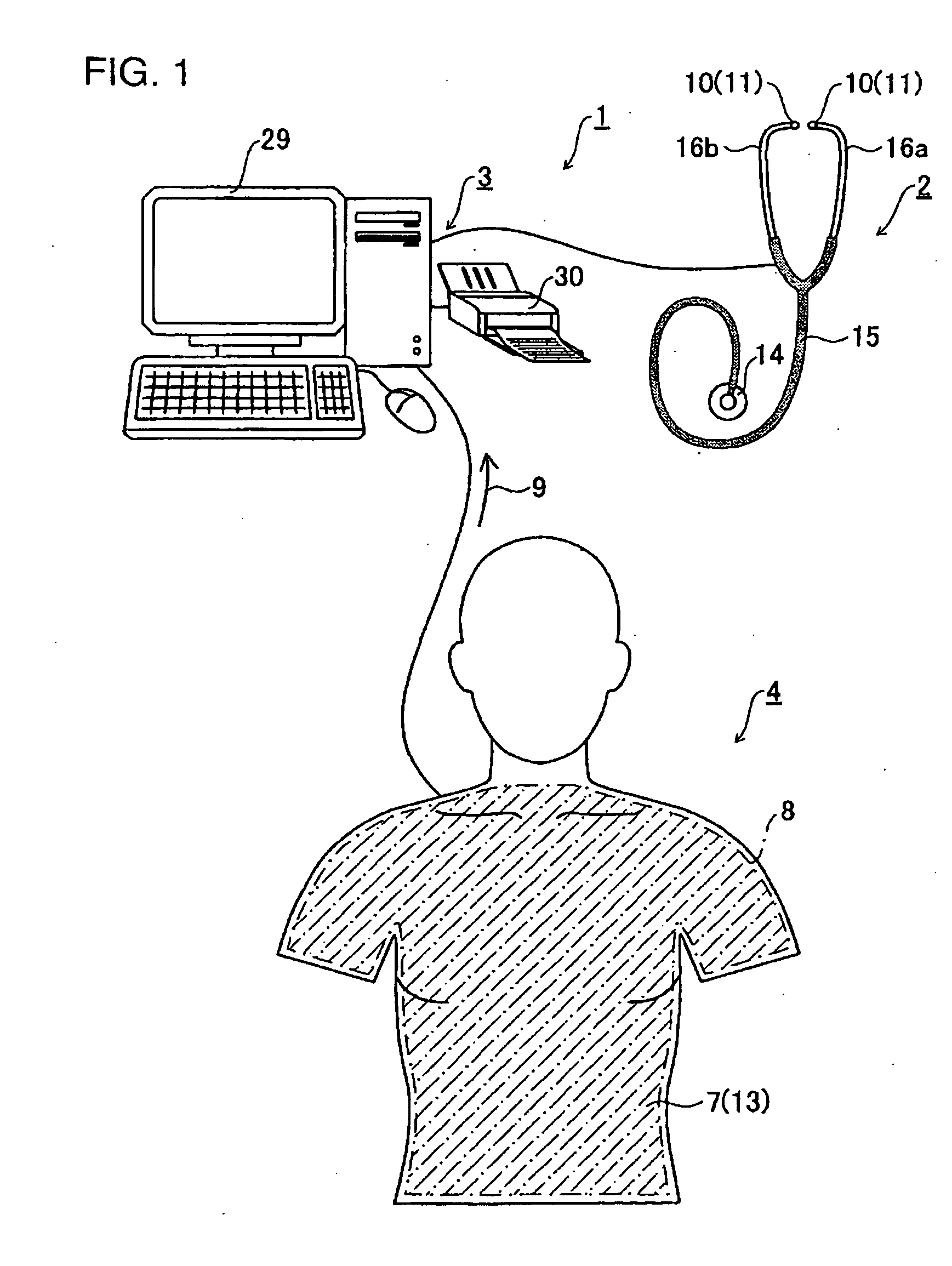

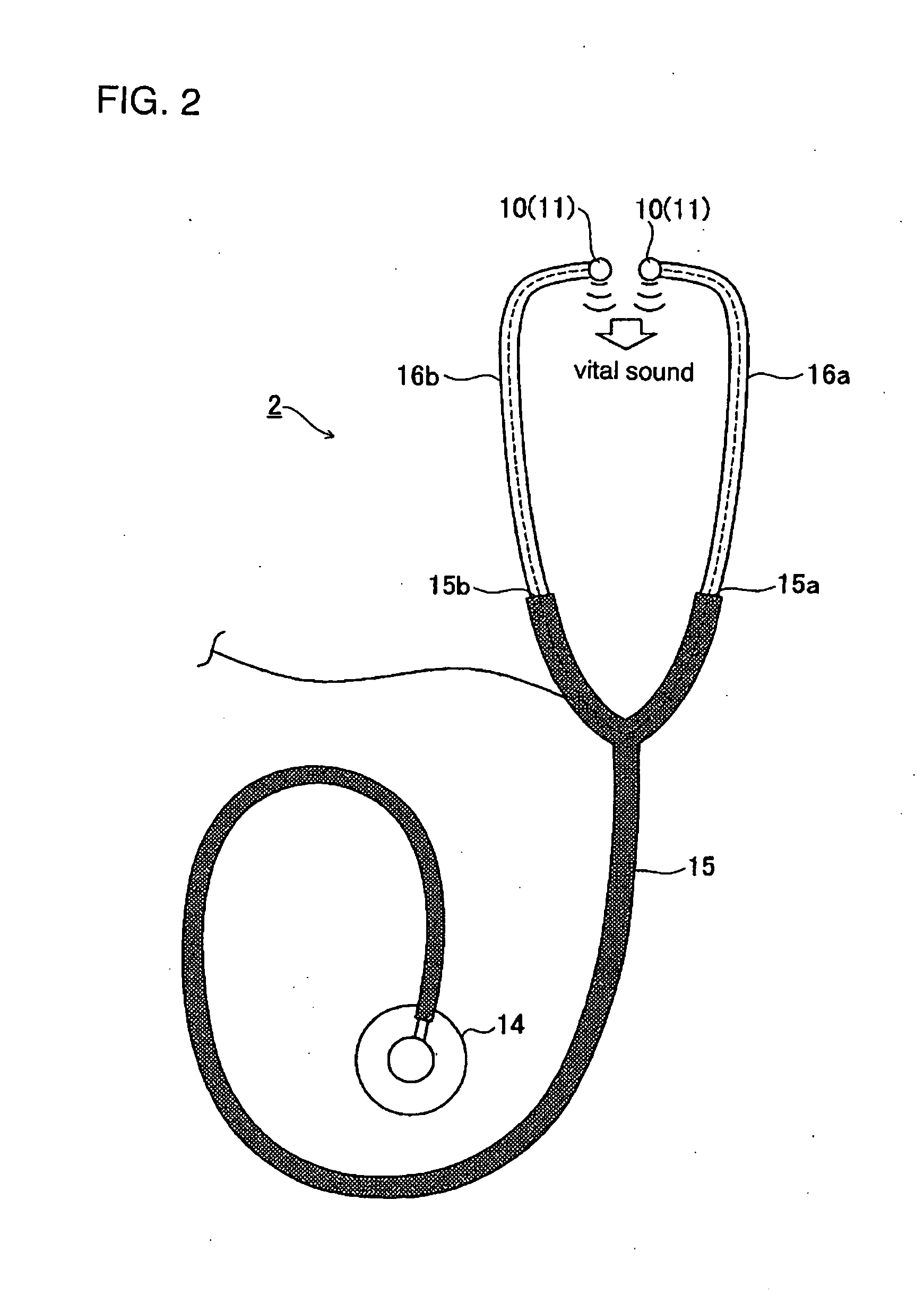

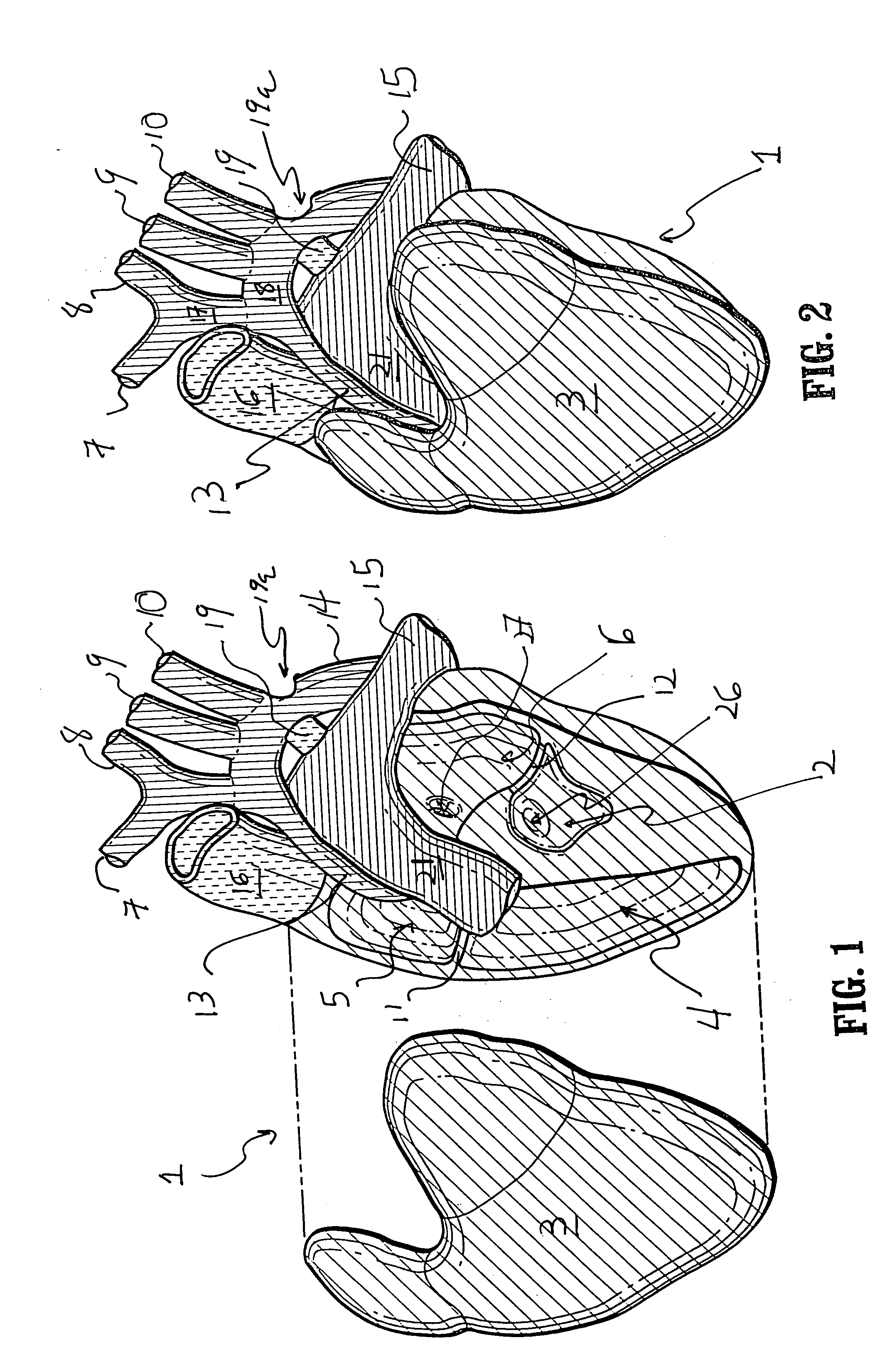

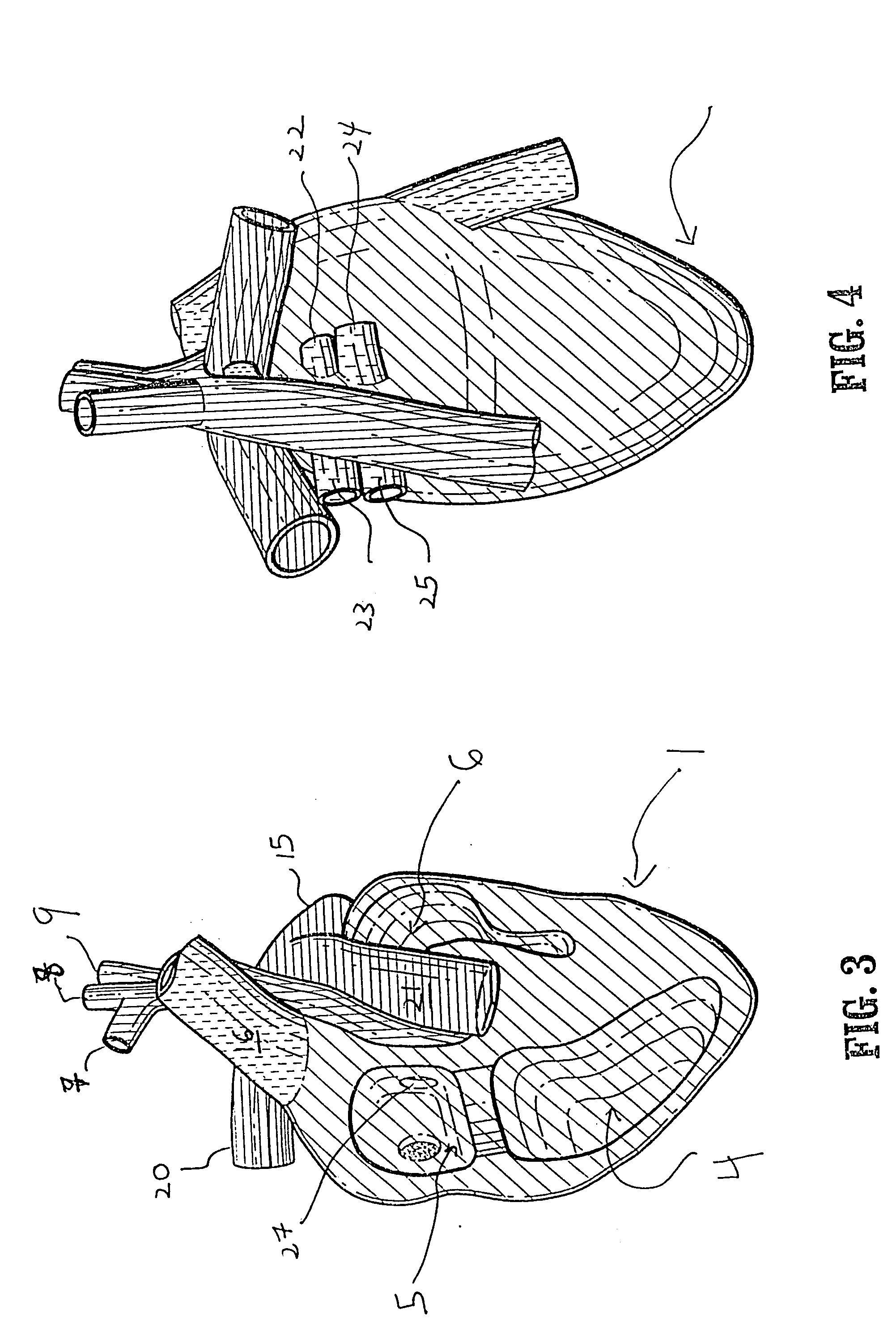

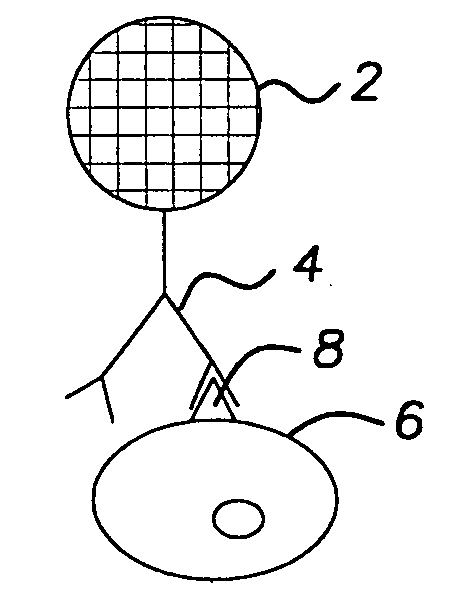

Auscultation training device

InactiveUS20050048455A1Improve teaching efficiencyEffective instructionSpeech analysisAuscultation instrumentsAuscultationStethoscope

The auscultation training device enables a trainee to experience and learn various case studies without feeling the difference from the actual auscultatory action using the actual stethoscope in order to obtain the auscultatory technique. The auscultation training device 1 mainly comprises the model human body 4, which is an imitation of a human body upper torso; the stethoscope simulator 2 that the trainee 5 uses to perform the simulation of the auscultatory action on the model human body 4; an auscultatory sensor 8 which detects the auscultatory action by the trainee 5 with the stethoscope simulator 2; and the controller 3 which is connected to the stethoscope simulator 2 and the auscultatory sensor 8 respectively, whereby the controller receives the detected signals 9 of the auscultatory action transmitted from the auscultatory sensor 8, and then controls and processes signals for reproduction of vital sounds including those such as cardiac sounds and breathing sounds of the human body by a vital sound player 11 installed in ear piece 10 of the stethoscope simulator 2.

Owner:GIFU UNIVERSITY

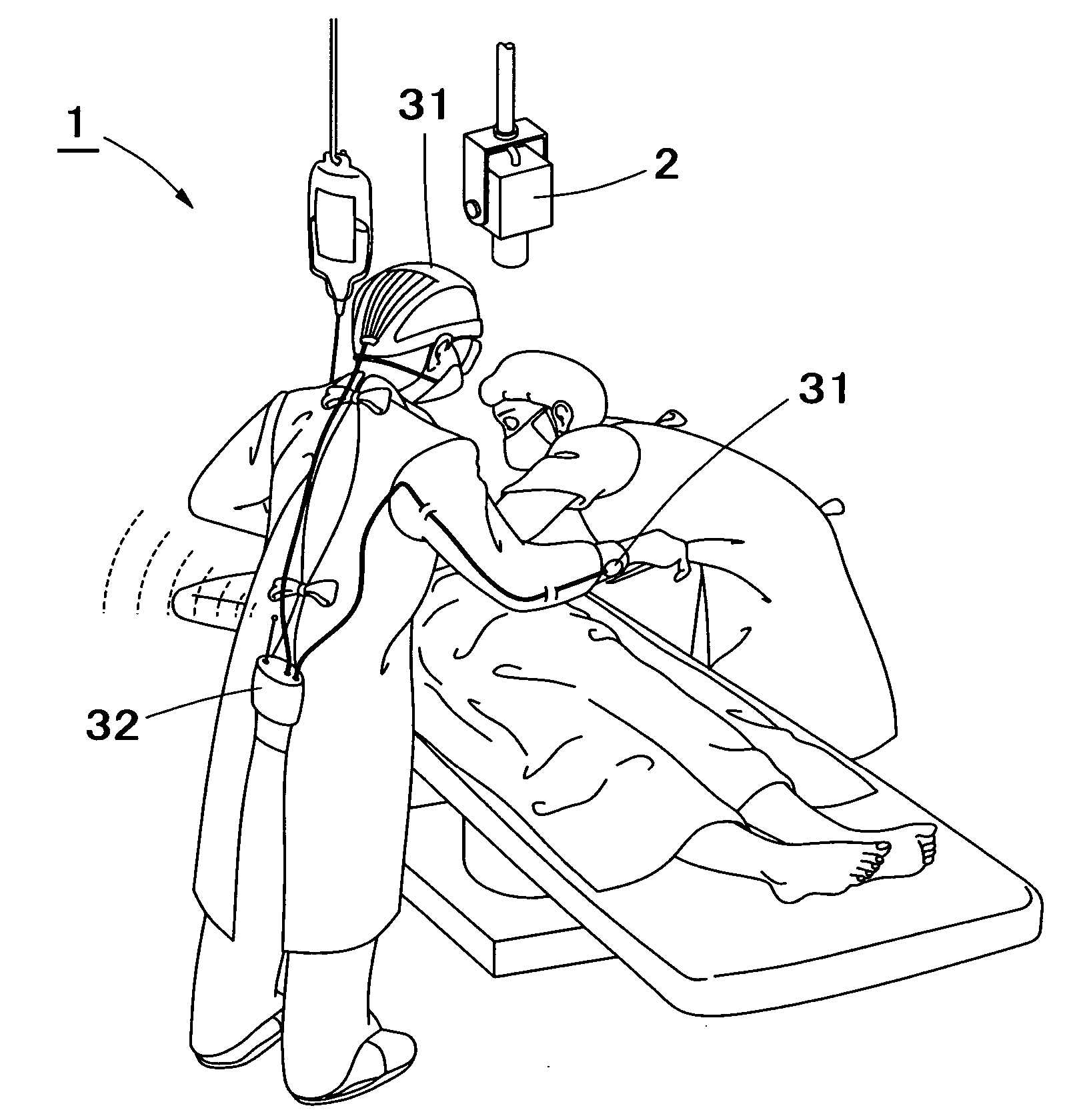

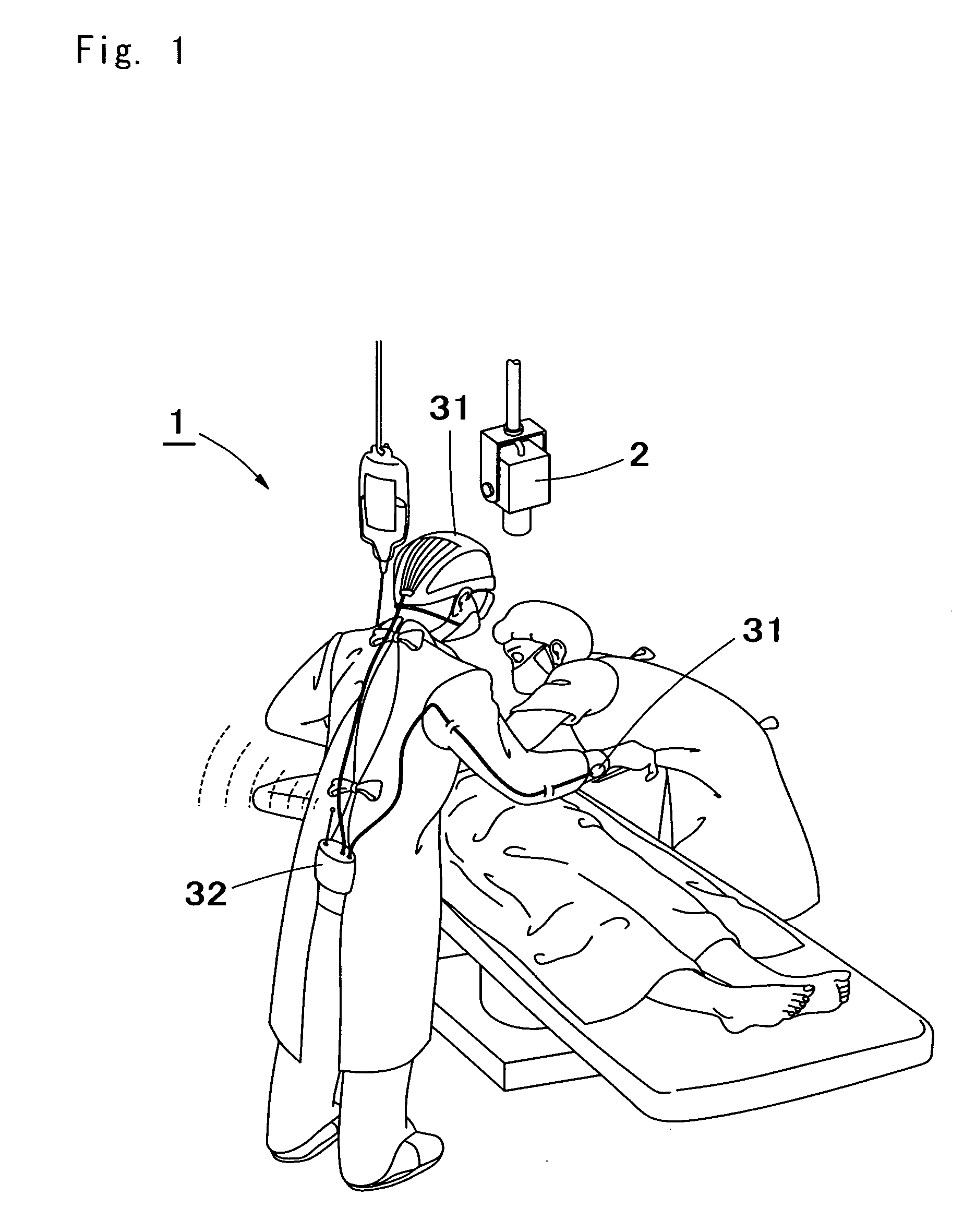

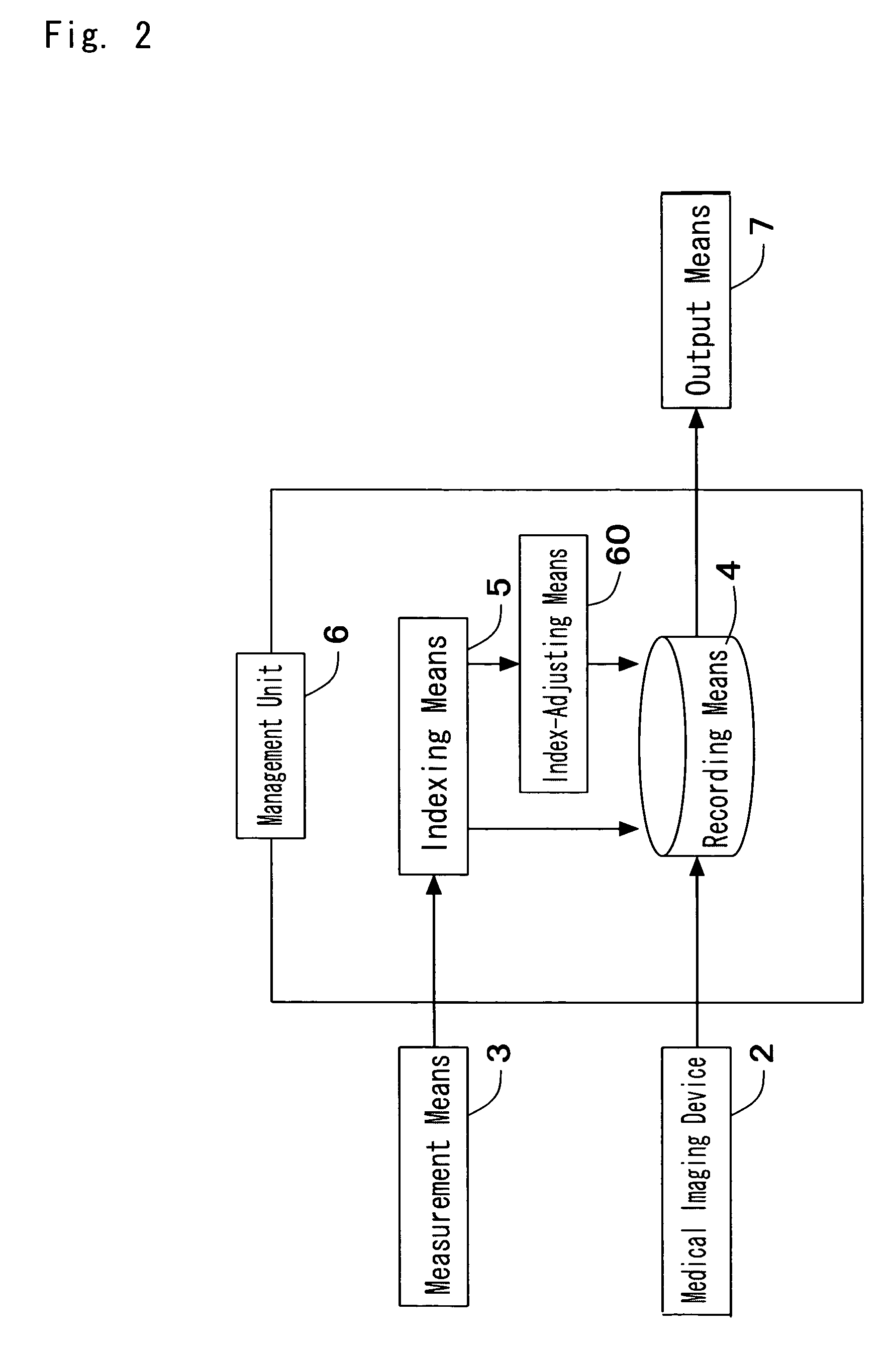

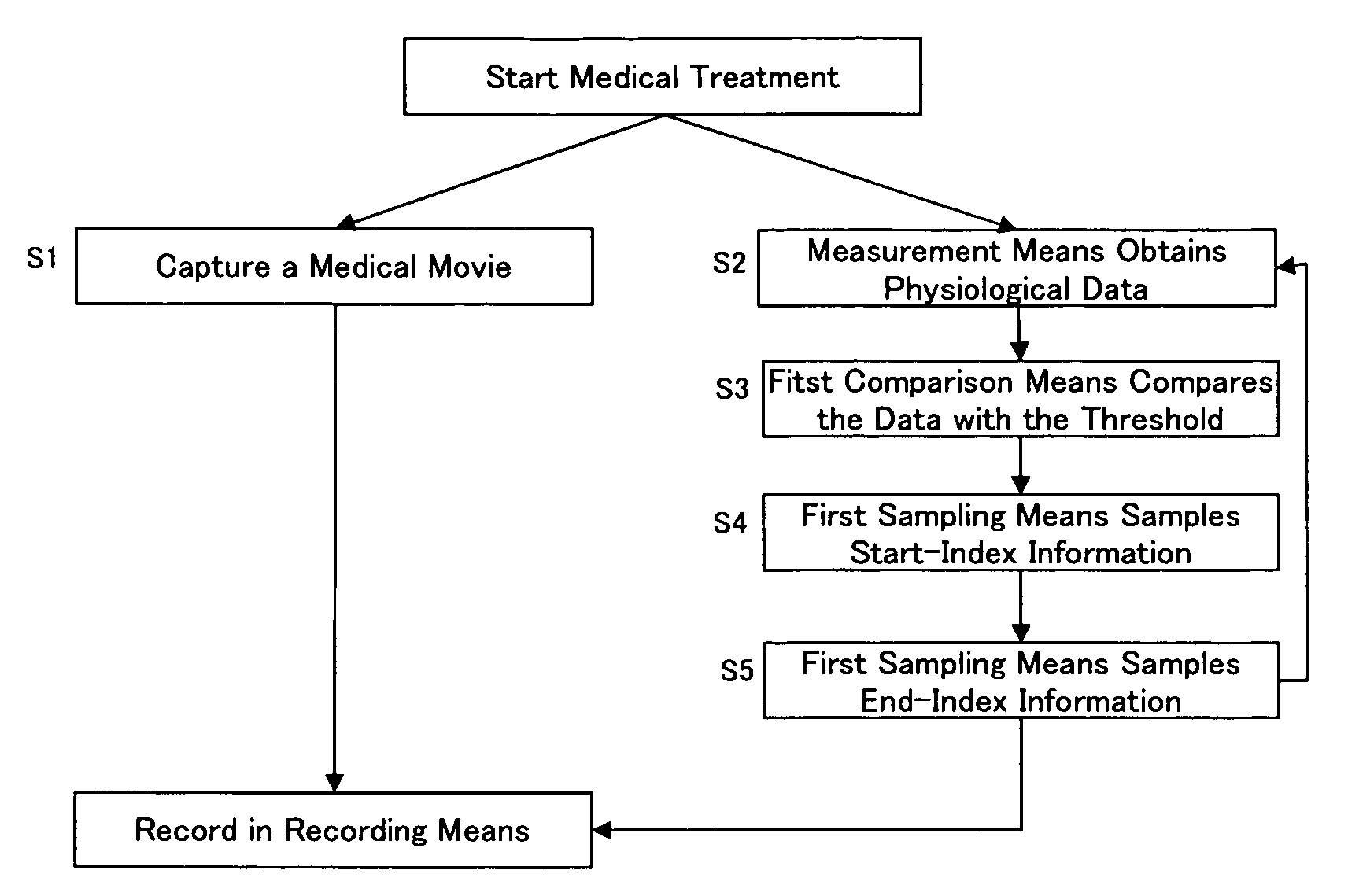

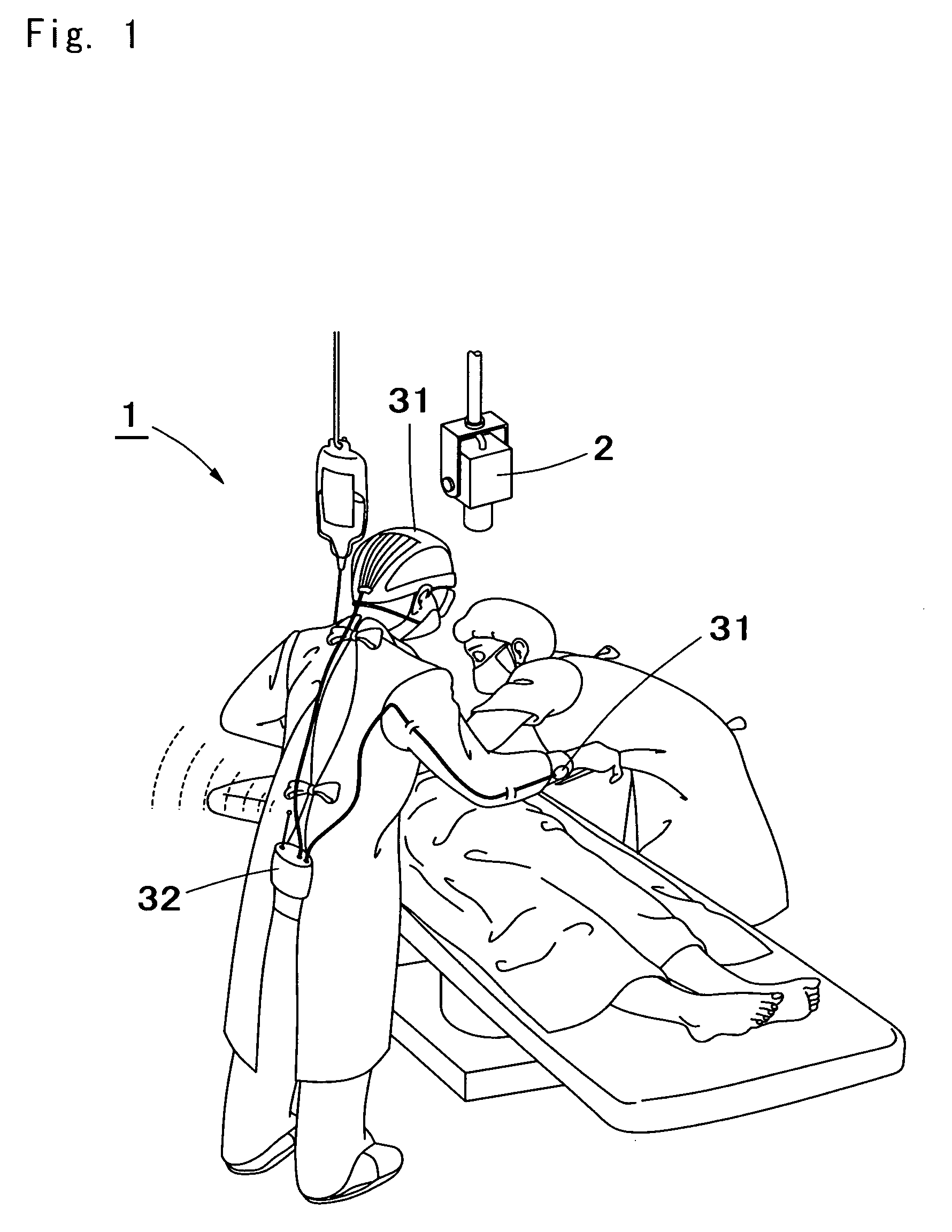

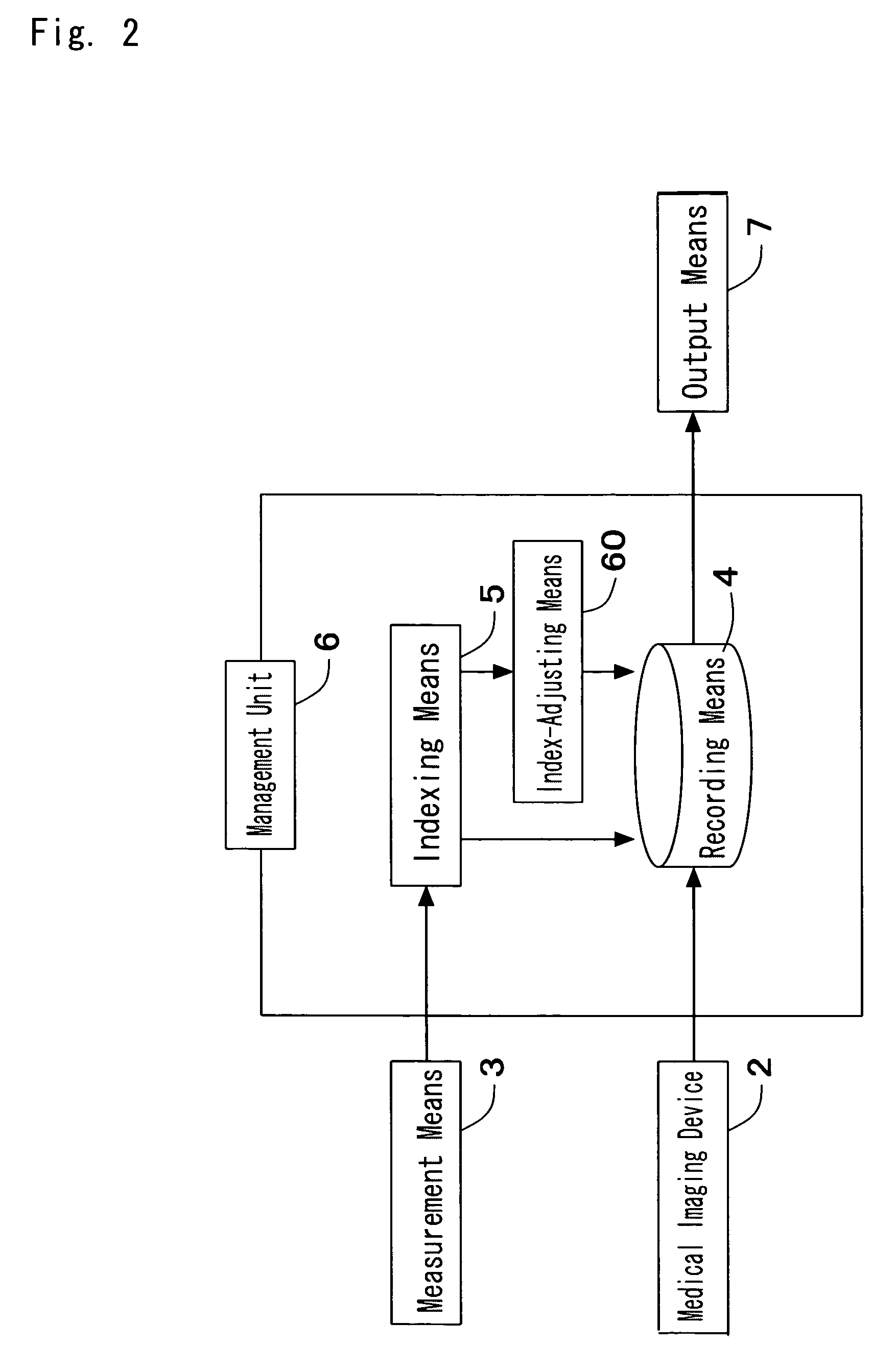

Medical image management system and medical image management method

ActiveUS20070225574A1Efficient indexingReduce memory sizeSurgeryDiagnostic recording/measuringMedical imagingComputer science

A medical image management system includes: a medical imaging device for imaging a patient to receive a medical treatment and creating a medical moving picture; and recording means for recording the medical moving picture imaged by the medical imaging device. The system further includes: measurement means for measuring biological information on a person who performs the medical treatment; and index addition means for adding an index to the medical moving picture recorded in the recording means, according to the measurement result obtained by the measurement means. By providing this system, it is possible to add an index to the medical moving picture recorded, according to the change of the biological information on the person who performs medical treatment on a patient.

Owner:SEVENTH DIMENSION DESIGN

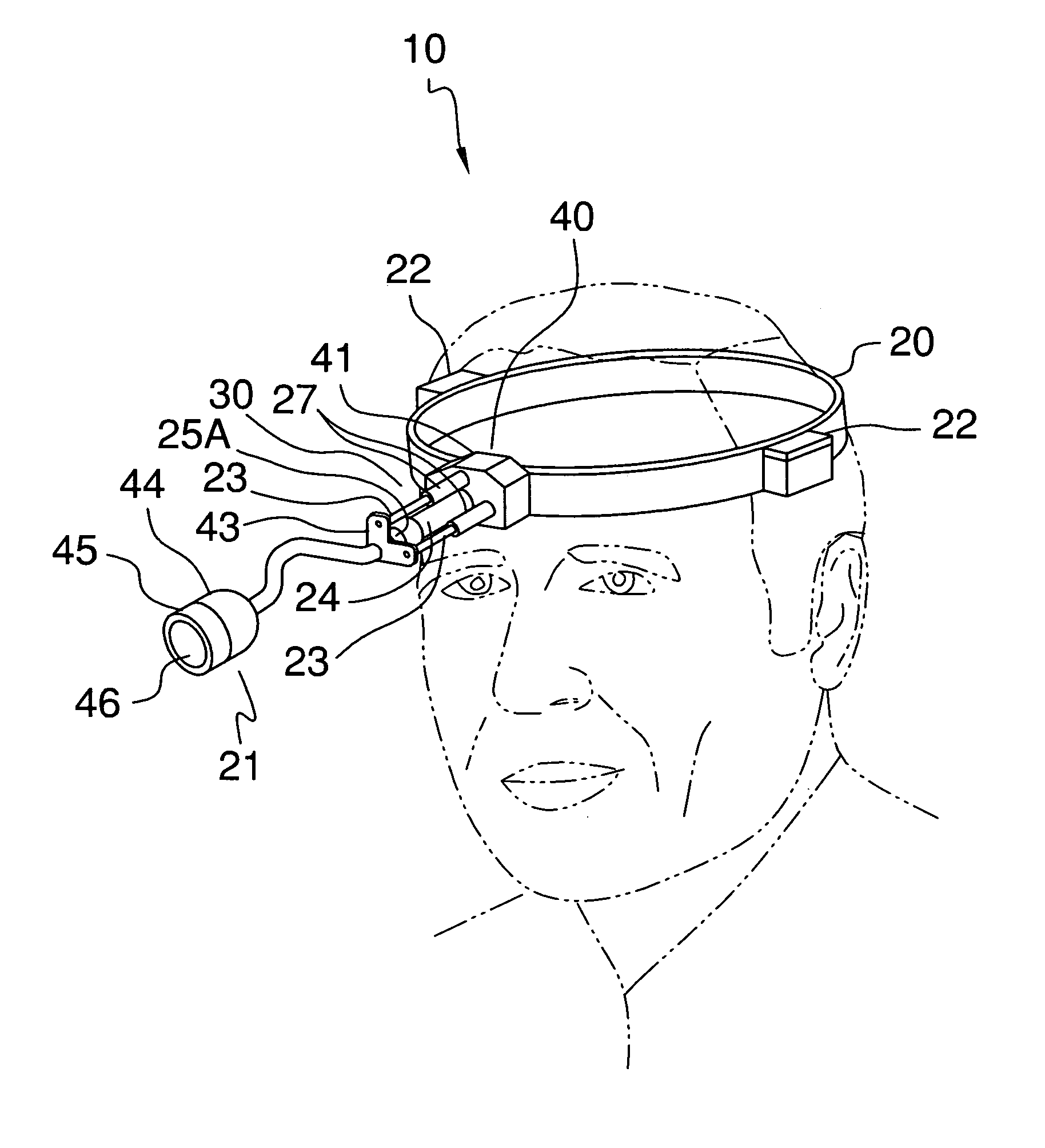

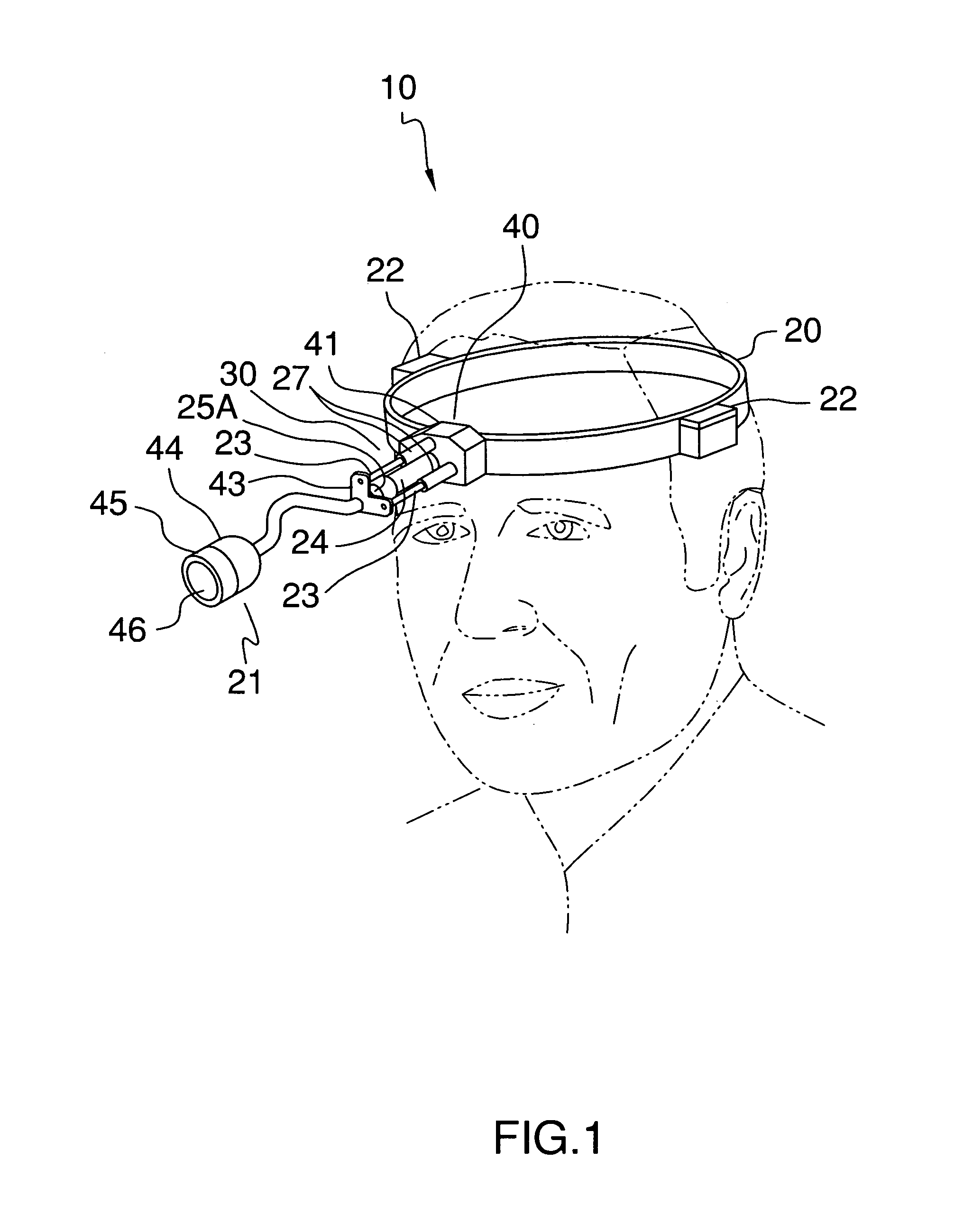

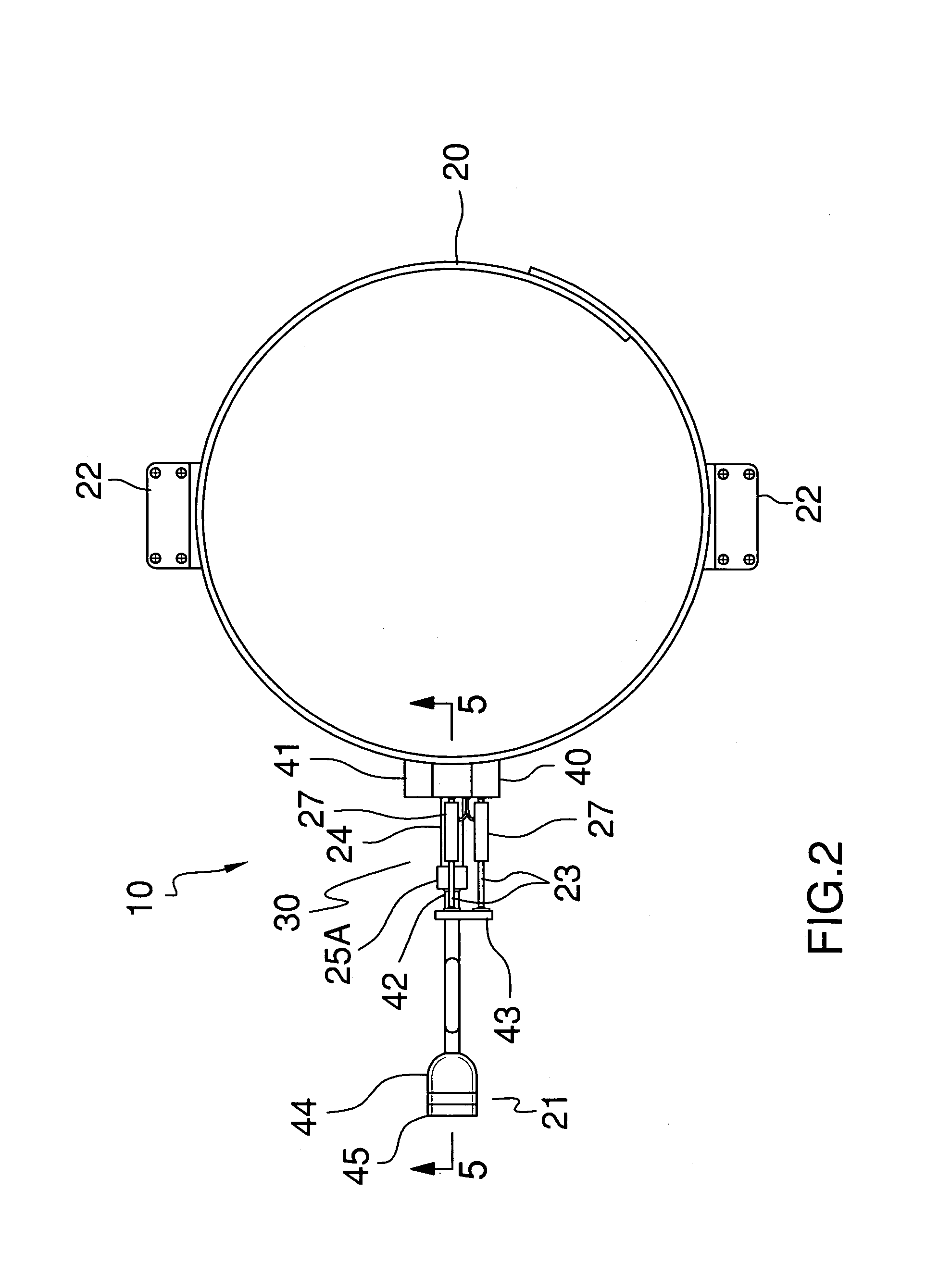

Voice-controlled surgical lighting assembly

InactiveUS7370991B1Easy to chargeEffective instructionLighting support devicesDiagnosticsElectricityS Voice

The assembly includes a strap adaptable to a variety of positions. Such a strap is placed directly about the user's head. A light-emitting source spaced from the strap includes a power supply source electrically coupled to the light-emitting assembly. Such a power supply source is rechargeable. A voice-activated mechanism for biasing the light-emitting source is defined from the strap so that the light-emitting assembly can be adapted along an x-axis, y-axis and z-axis. A motor assembly is directly and operably conjoined to the voice-activated mechanism and the light-emitting assembly. The voice-activated mechanism cooperates with the light-emitting source and the motor assembly during operating conditions. Such a voice operating mechanism is power-operated. The voice-activated mechanism is conveniently responsive to a user's voice commands in such a manner that the user can selectively operate the motor assembly and the light-emitting source from a remote location.

Owner:ELLIS FANT WANDA J

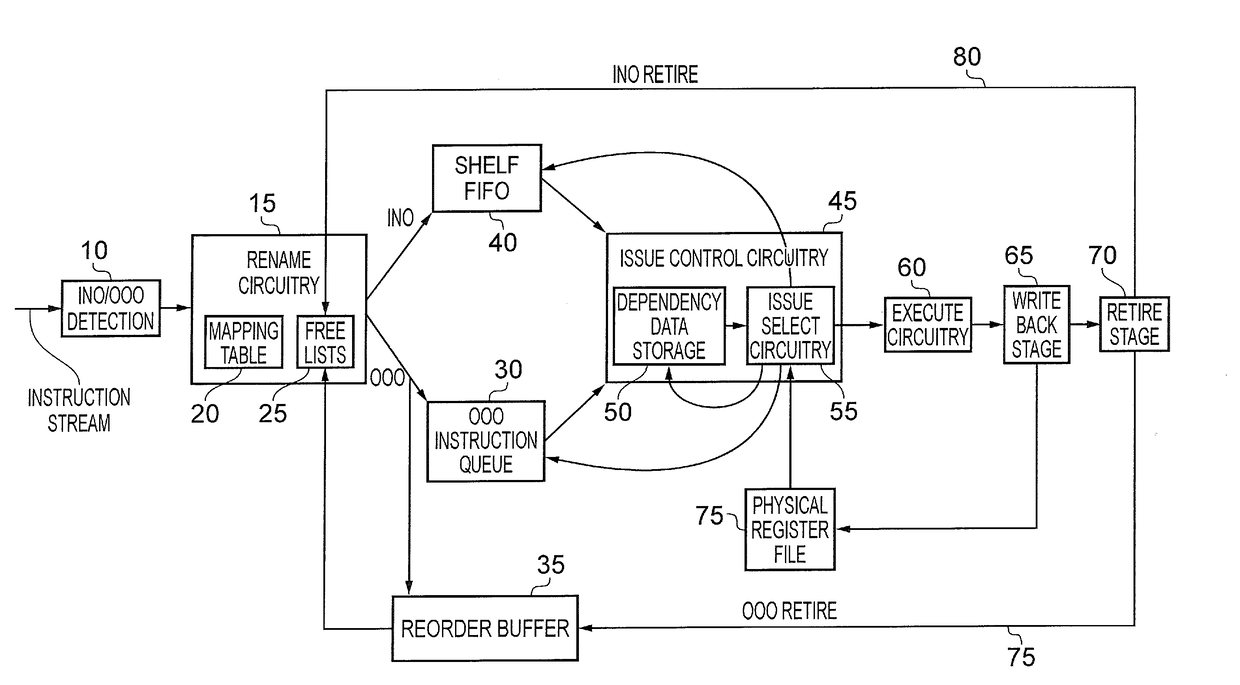

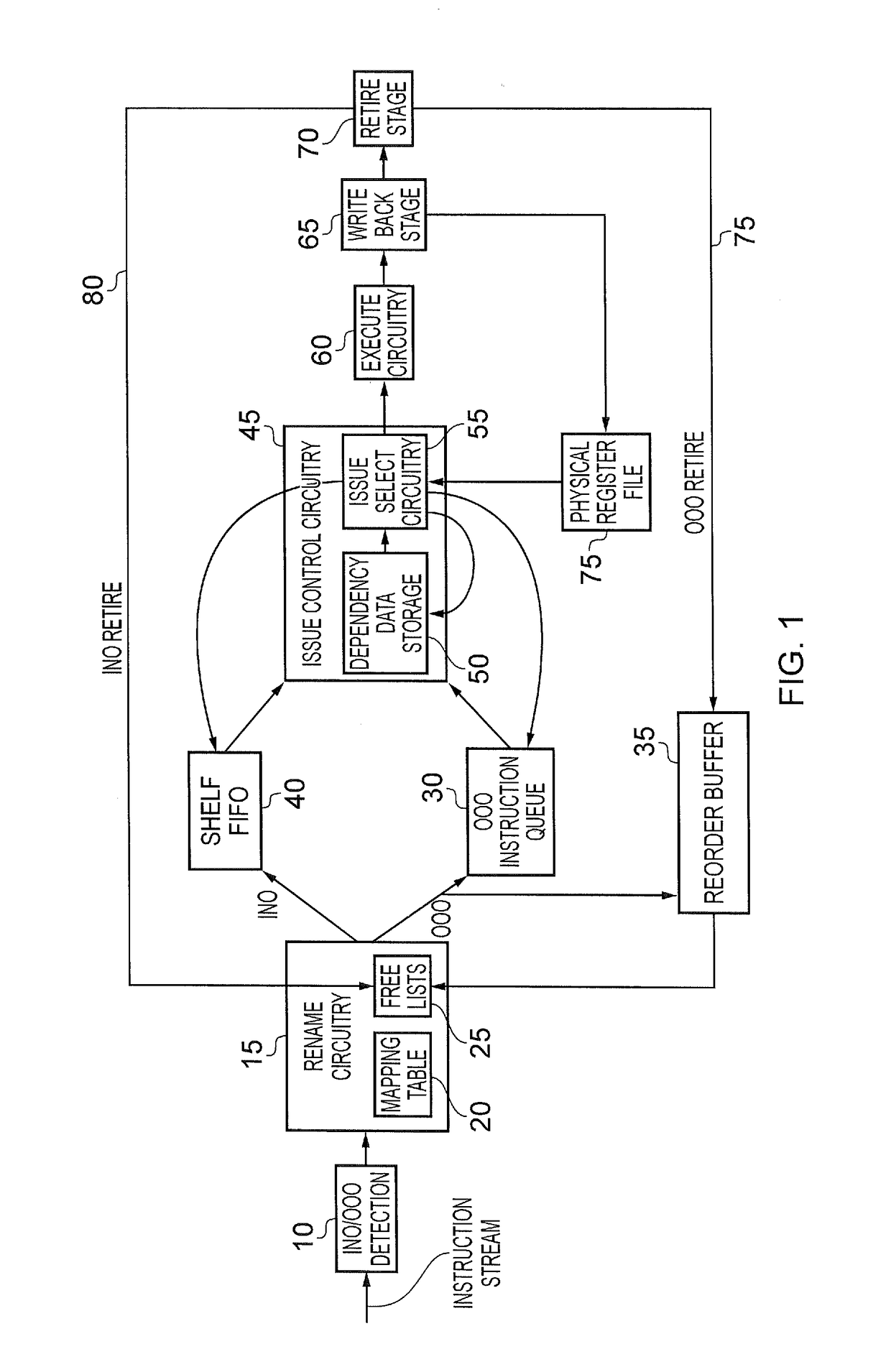

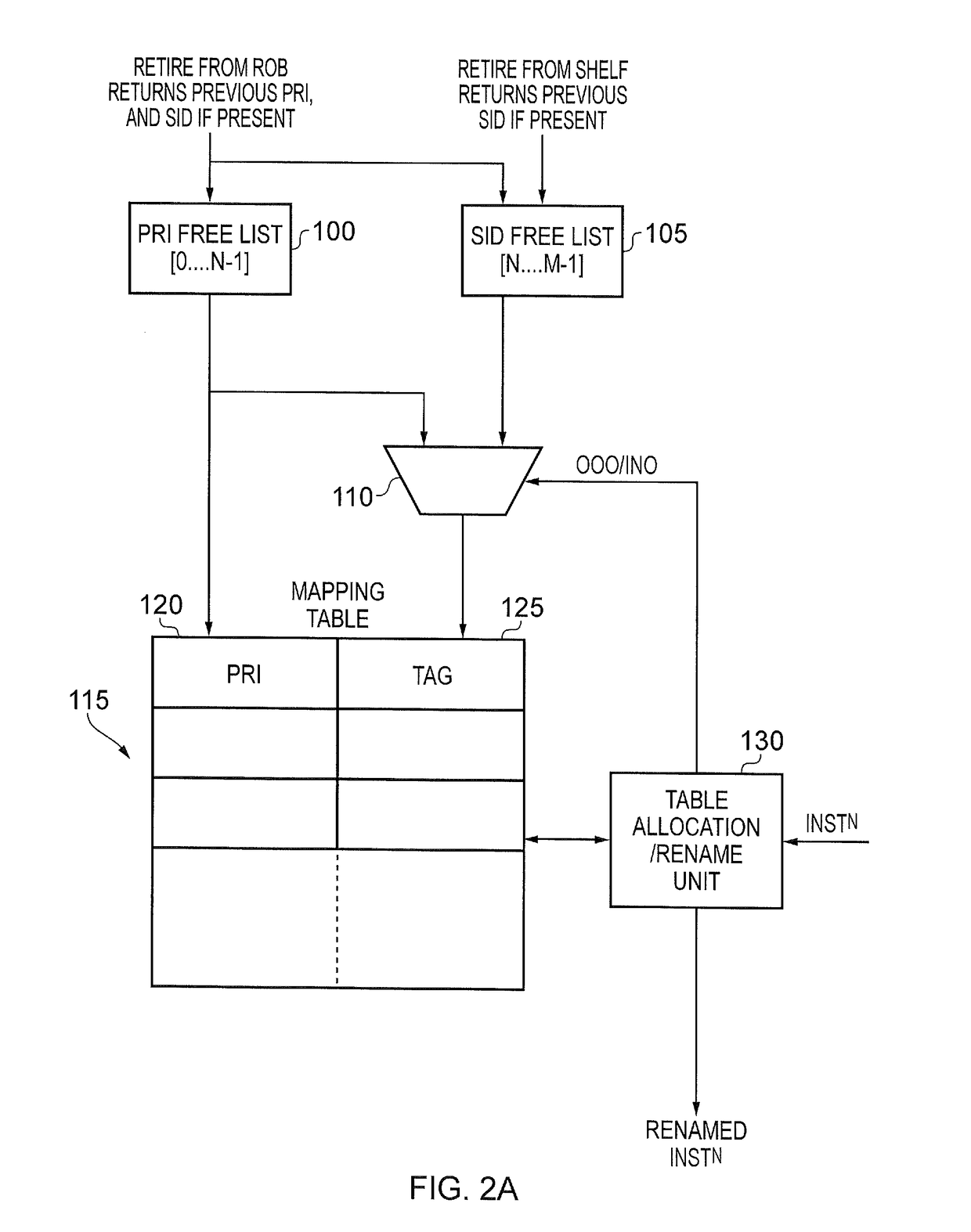

Data processing apparatus and method for executing a stream of instructions out of order with respect to original program order

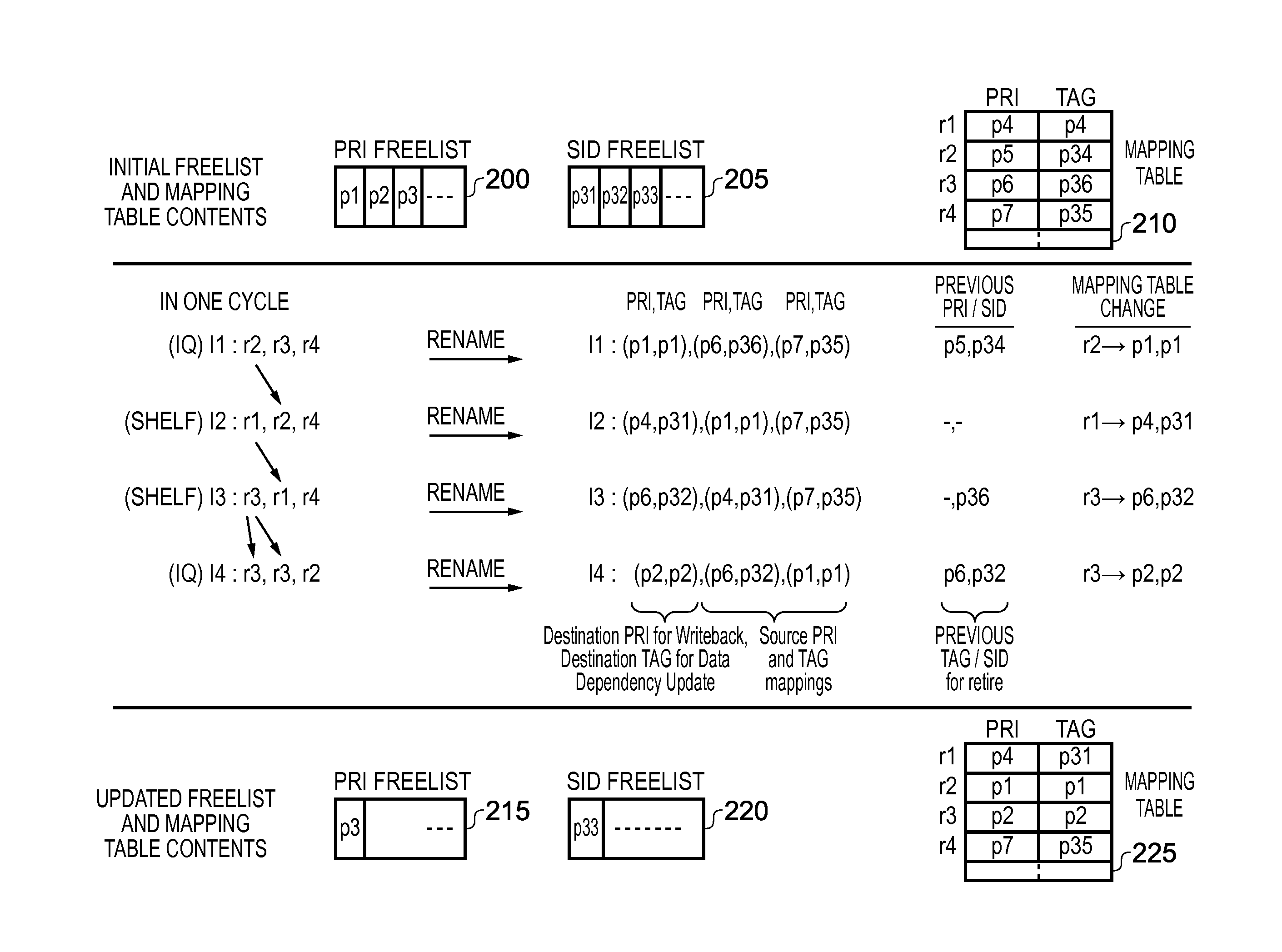

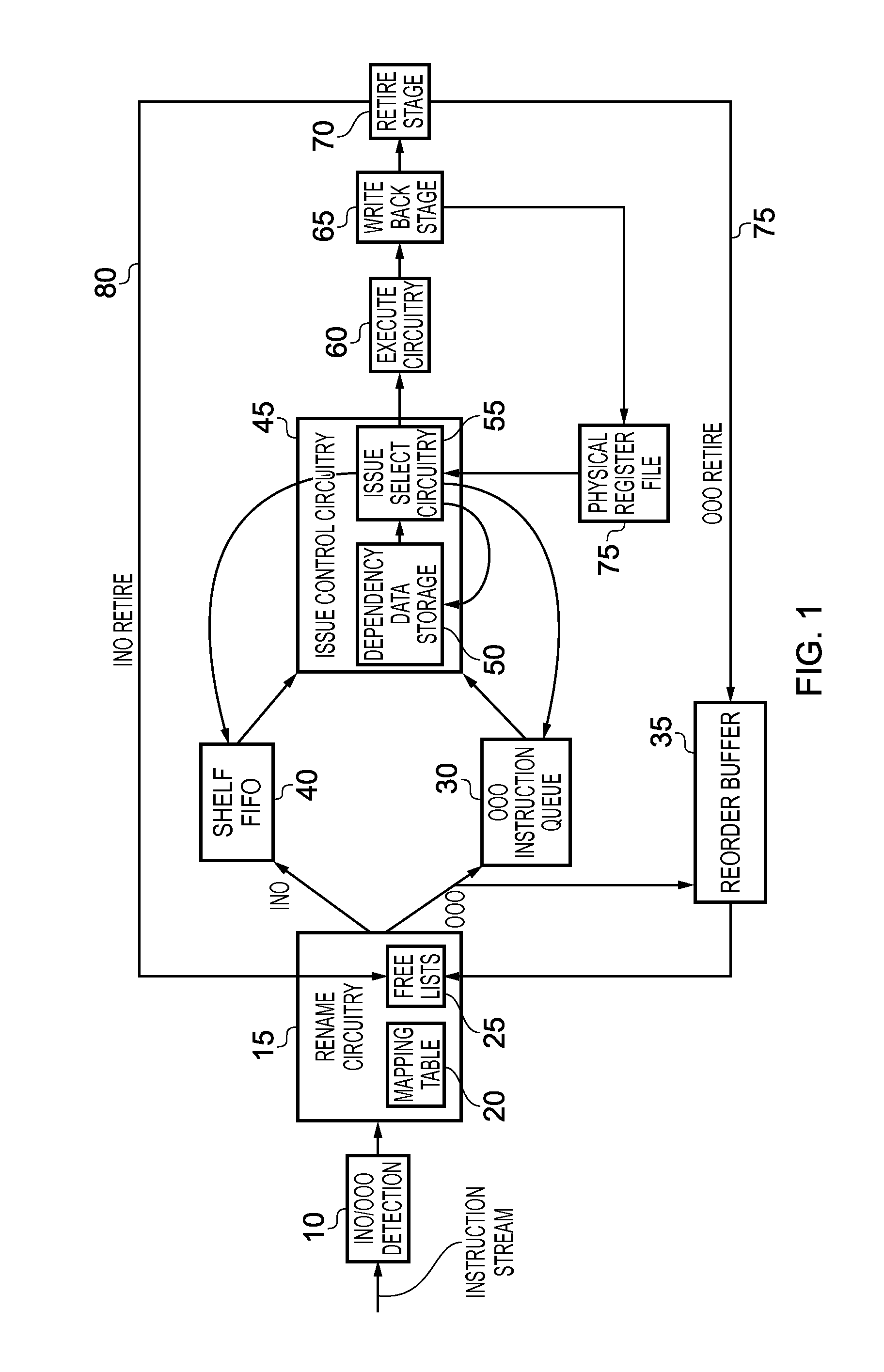

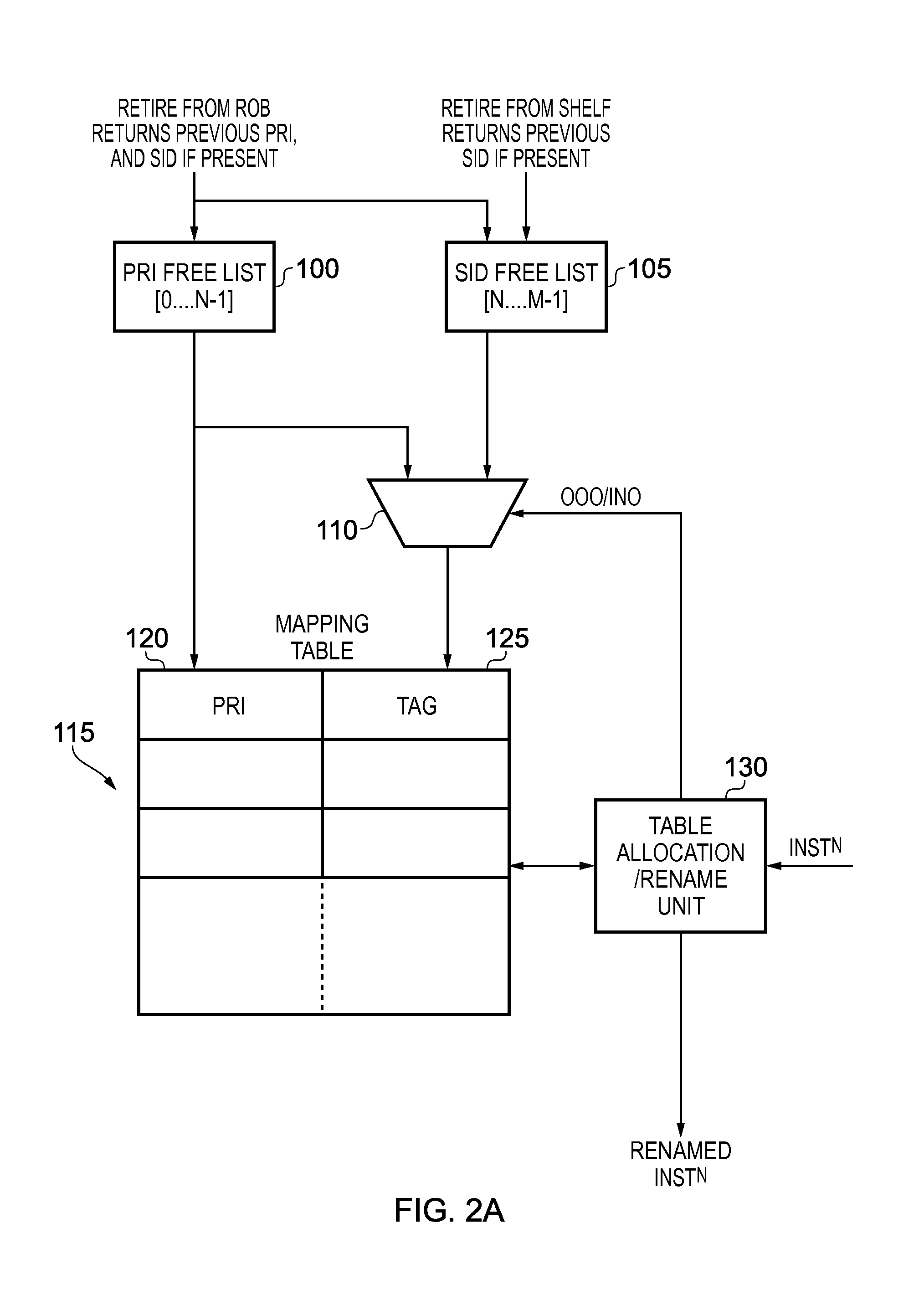

InactiveUS20150277925A1Reduce energy consumptionIncreases effective instruction windowRegister arrangementsDigital computer detailsParallel computingComputer science

A data processing apparatus and method are provided for executing a stream of instructions out-of-order with respect to original program order. At least some of the instructions in the stream identify one or more architectural registers from a set of architectural registers. The apparatus comprises a plurality of out-of-order components configured to manage execution of a first subset of instructions out-of-order, the plurality of out-of-order components being configured to remove false dependencies between instructions in the first subset. The plurality of out-of-order components include a first issue queue into which the instructions in the first subset are buffered prior to execution. A second issue queue is used to buffer a second subset of instructions prior to execution, the second subset of instructions being constrained to execute in order. Issue control circuitry is configured to reference both issue queues in order to determine an order of execution of instructions, and is configured to constrain the order of execution of the first subset of instructions by true dependencies between the instructions in both the first and second issue queues, and to constrain the order of execution of the second subset of instructions by both the true dependencies and the false dependencies between the instructions in both the first and second issue queues. This approach provides improved performance and / or reduced energy consumption.

Owner:RGT UNIV OF MICHIGAN

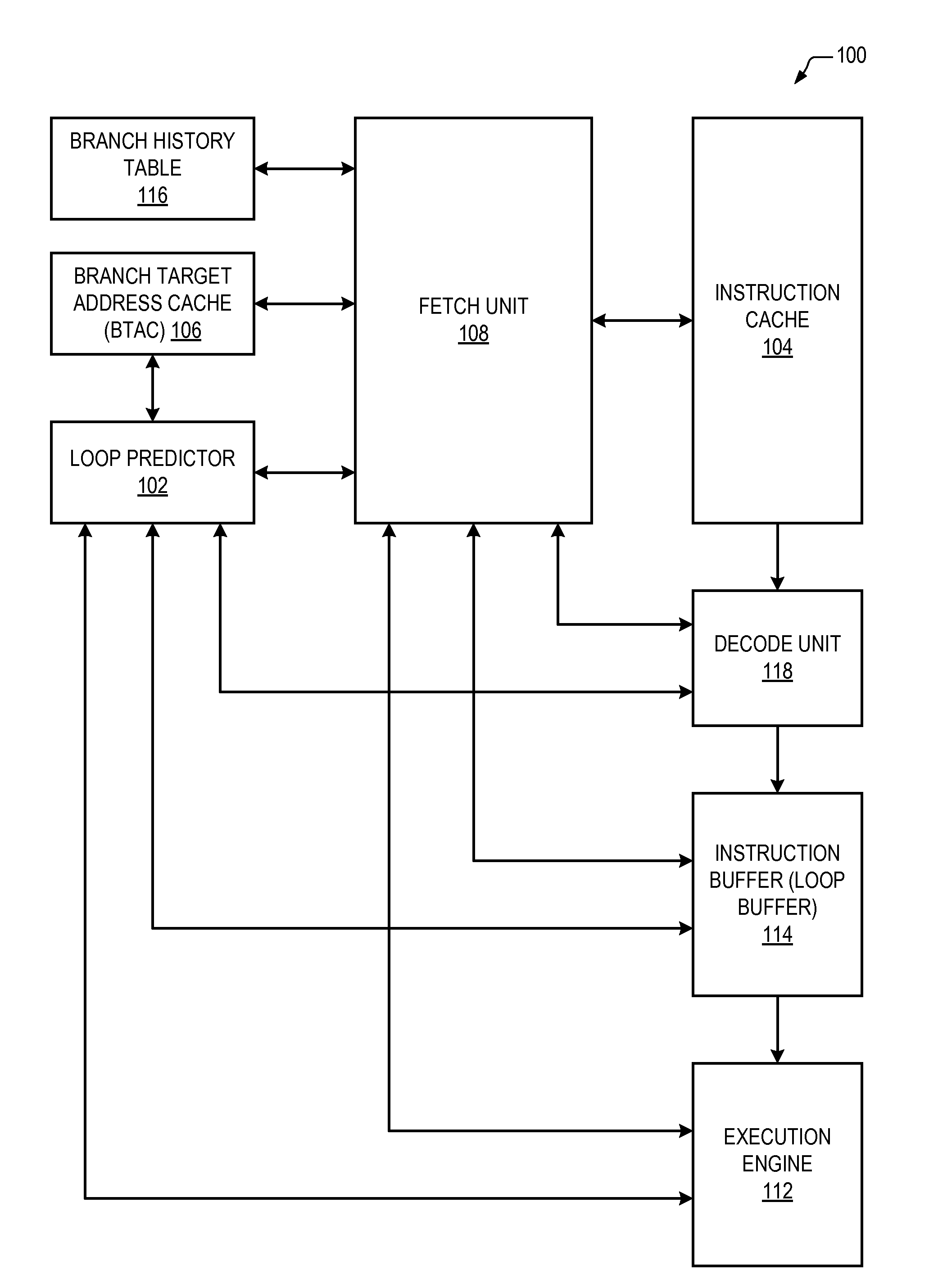

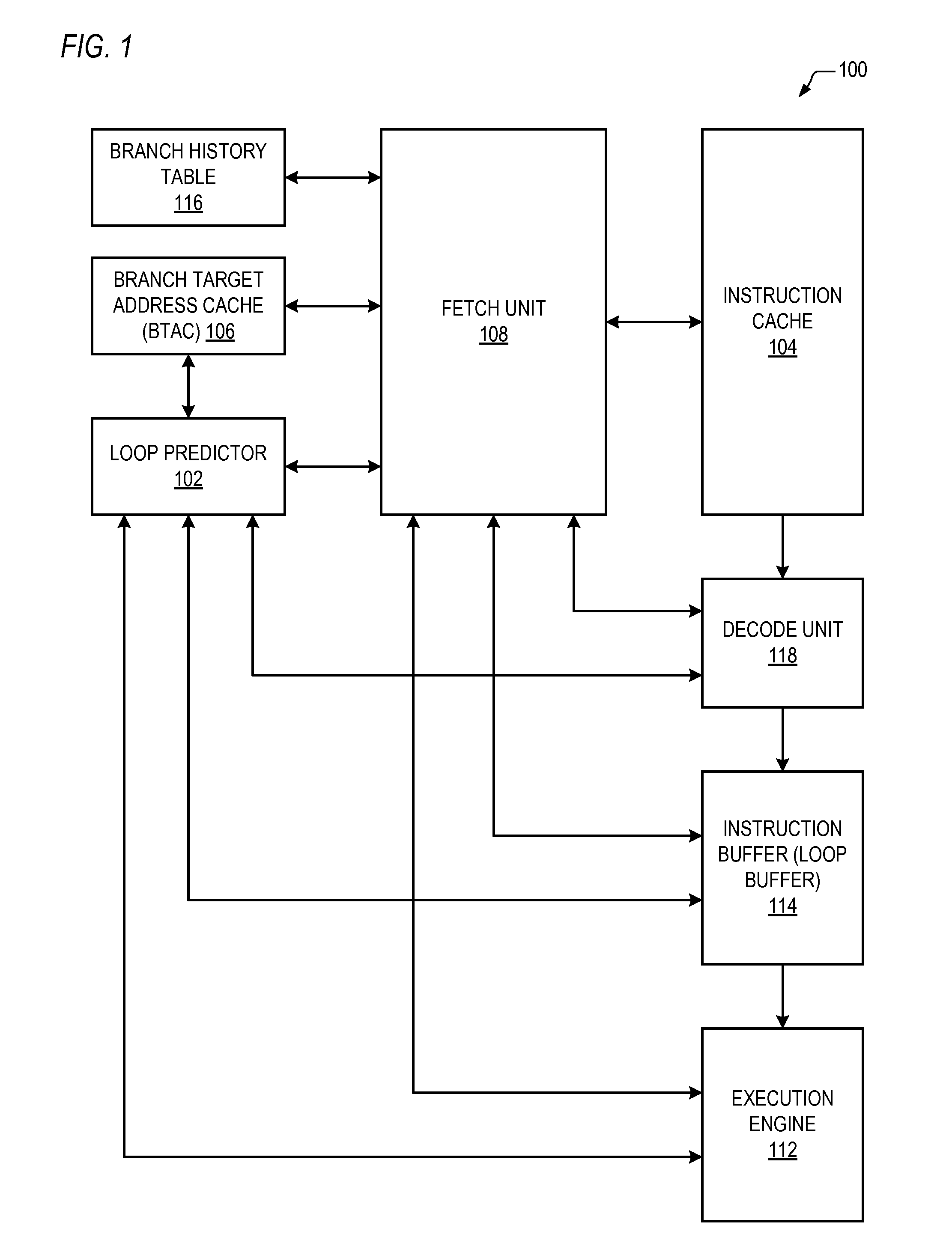

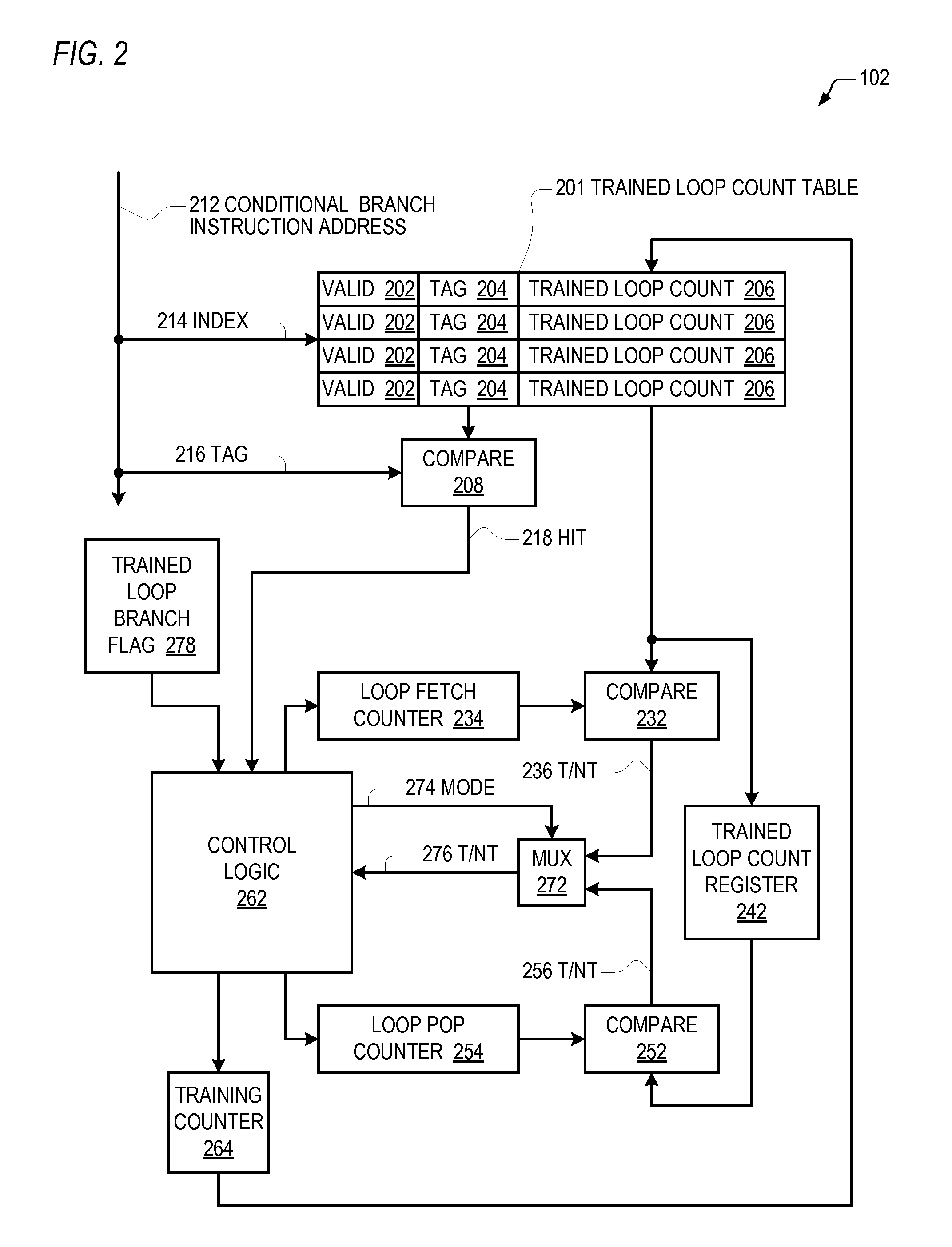

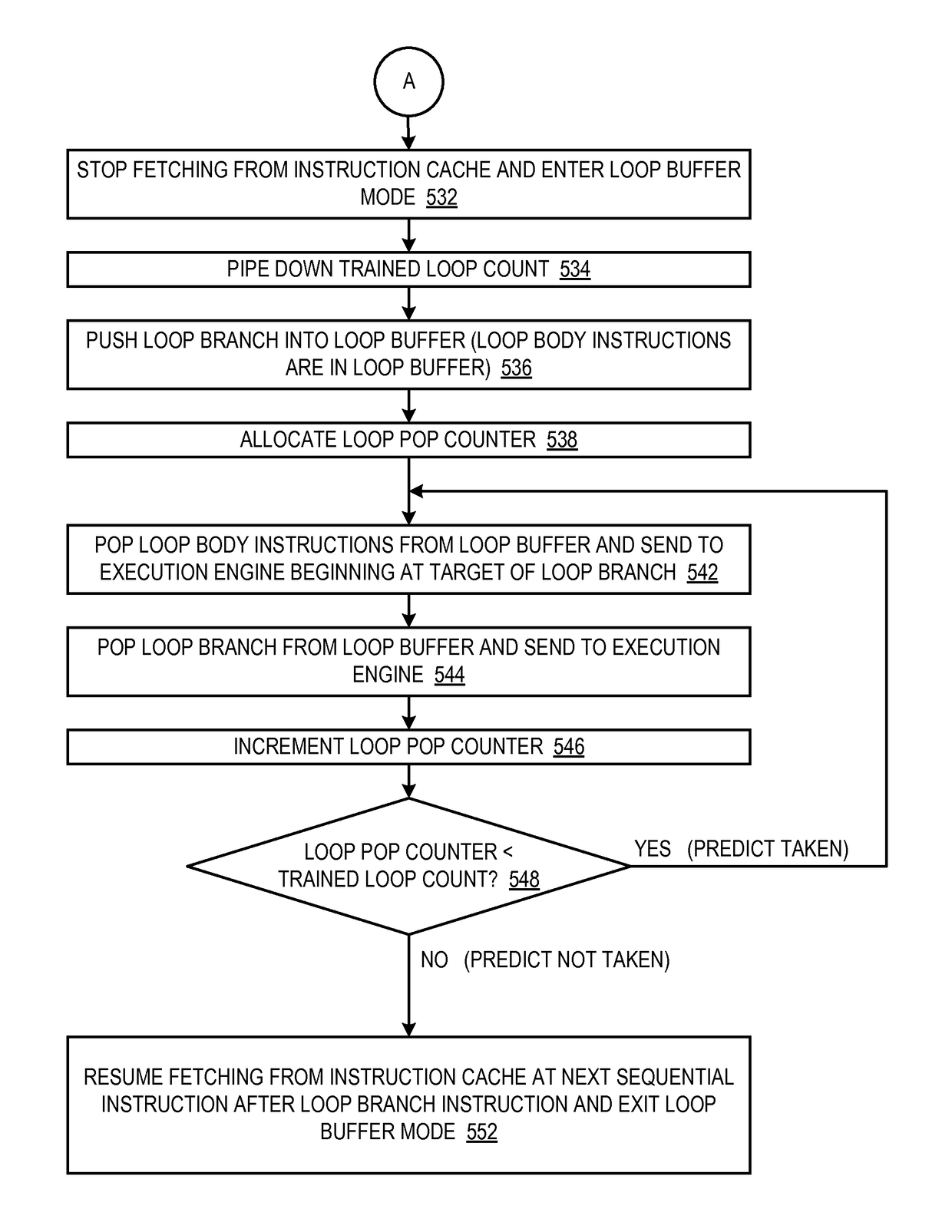

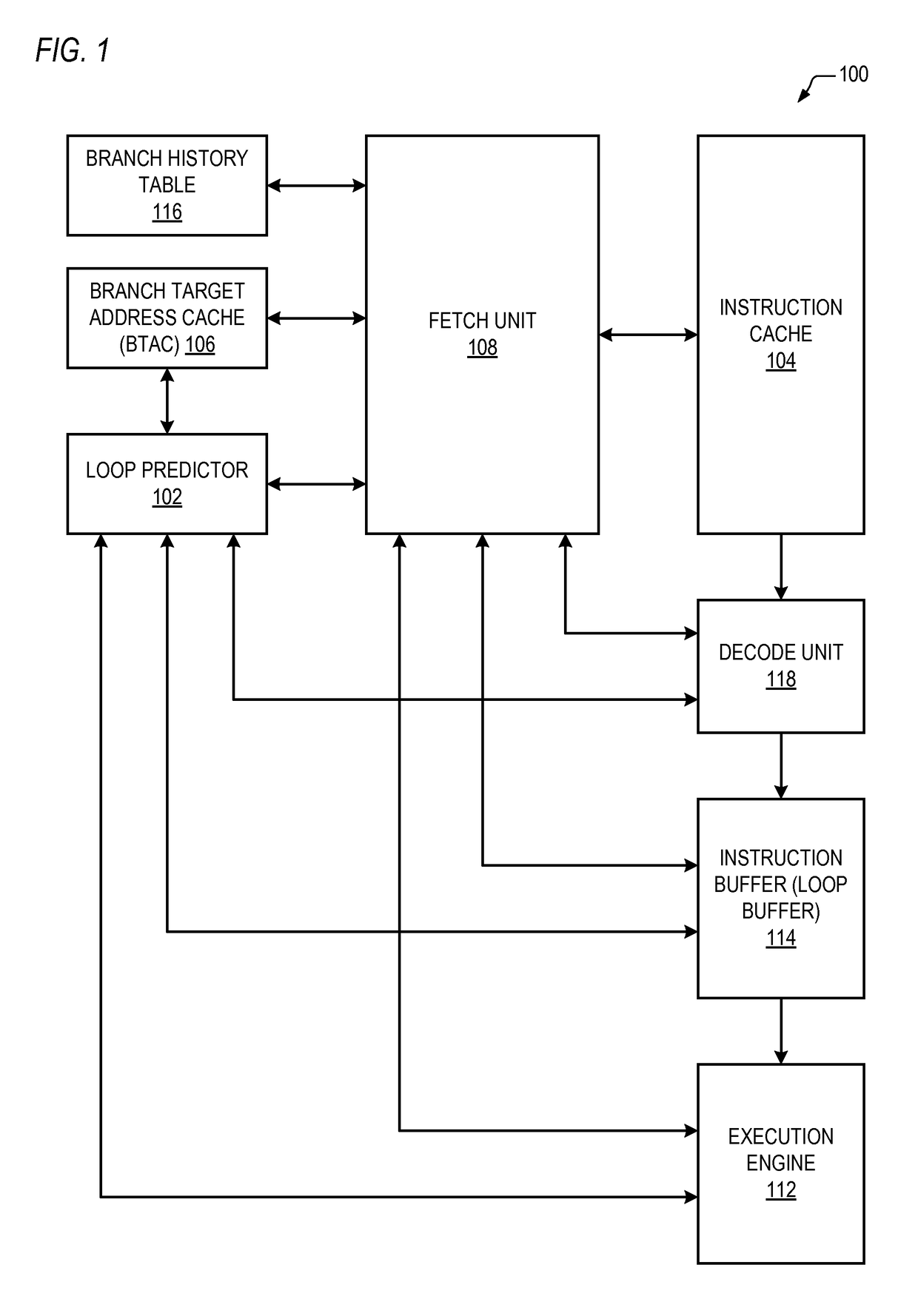

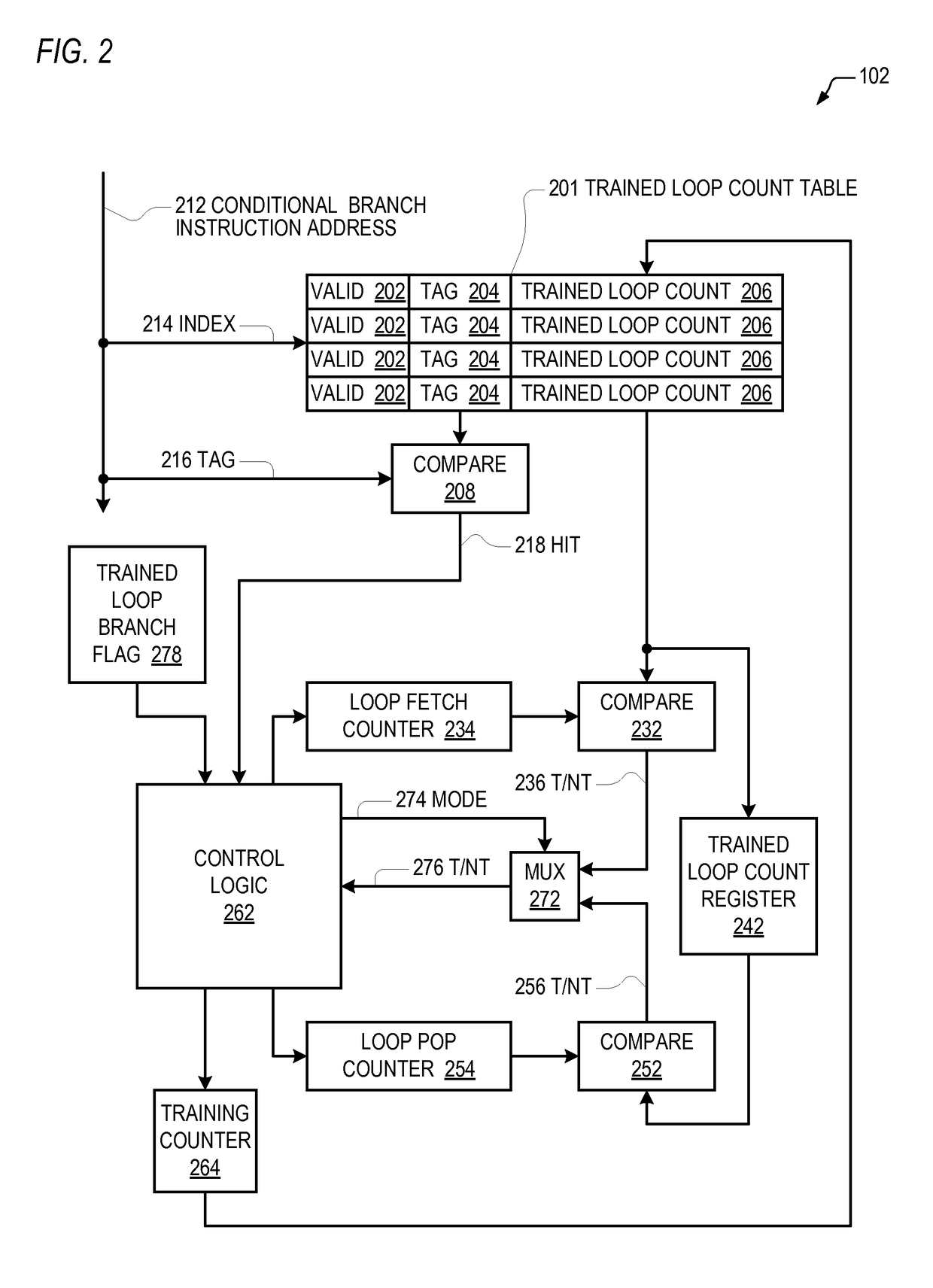

Loop predictor-directed loop buffer

ActiveUS20160092230A1Effective instructionAccurate predictionMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingBranch

A loop predictor trains a branch instruction to determine a trained loop count of a loop. When the loop fits in an instruction buffer, the processor stops fetching from an instruction cache, sends the loop instructions to an execution engine from the buffer without fetching from the cache, maintains a loop pop count of times the branch is sent to the execution engine from the buffer, and predicts the branch instruction is taken when the loop pop count is less than the trained loop count and otherwise predicts not taken.

Owner:VIA ALLIANCE SEMICON CO LTD

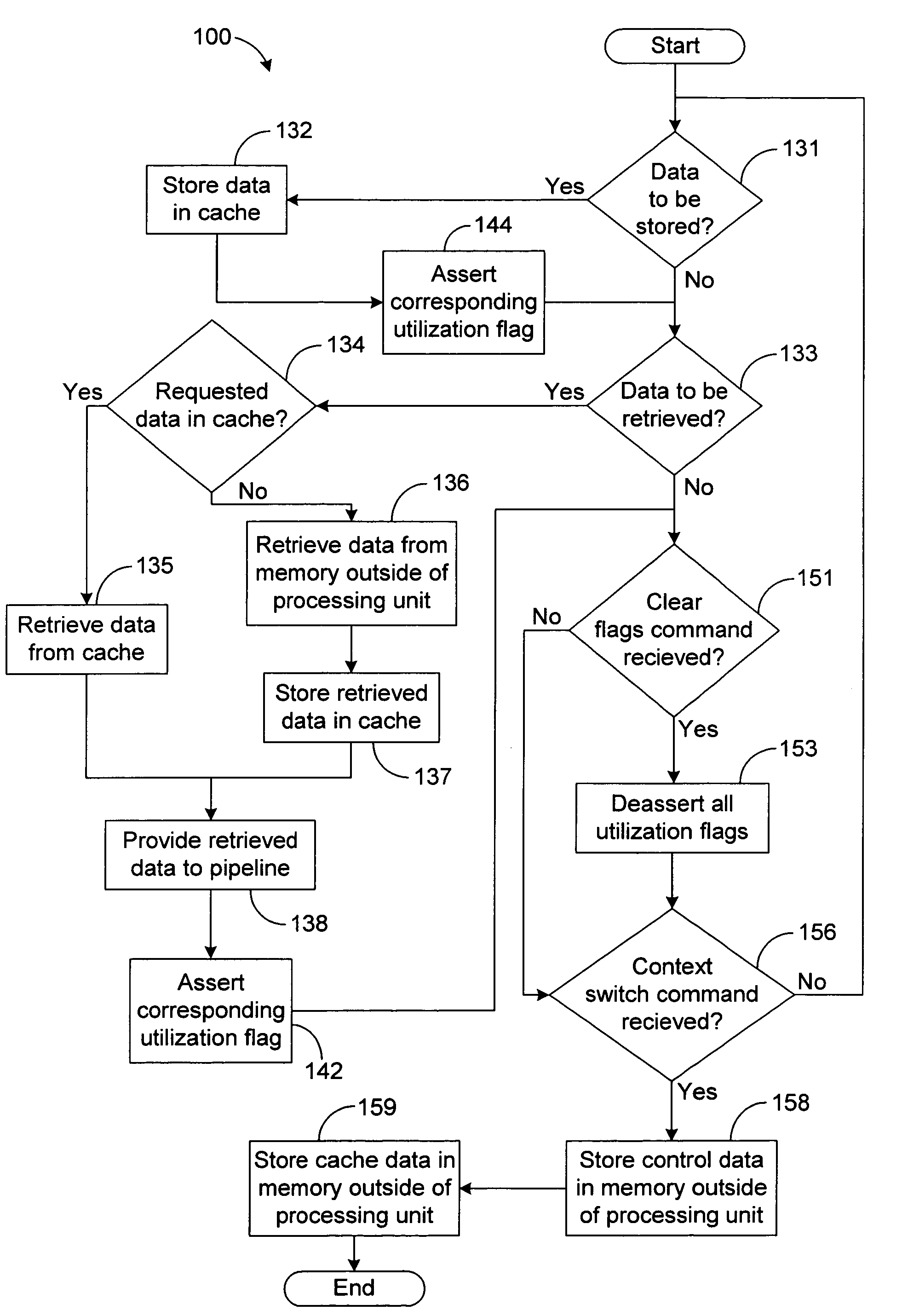

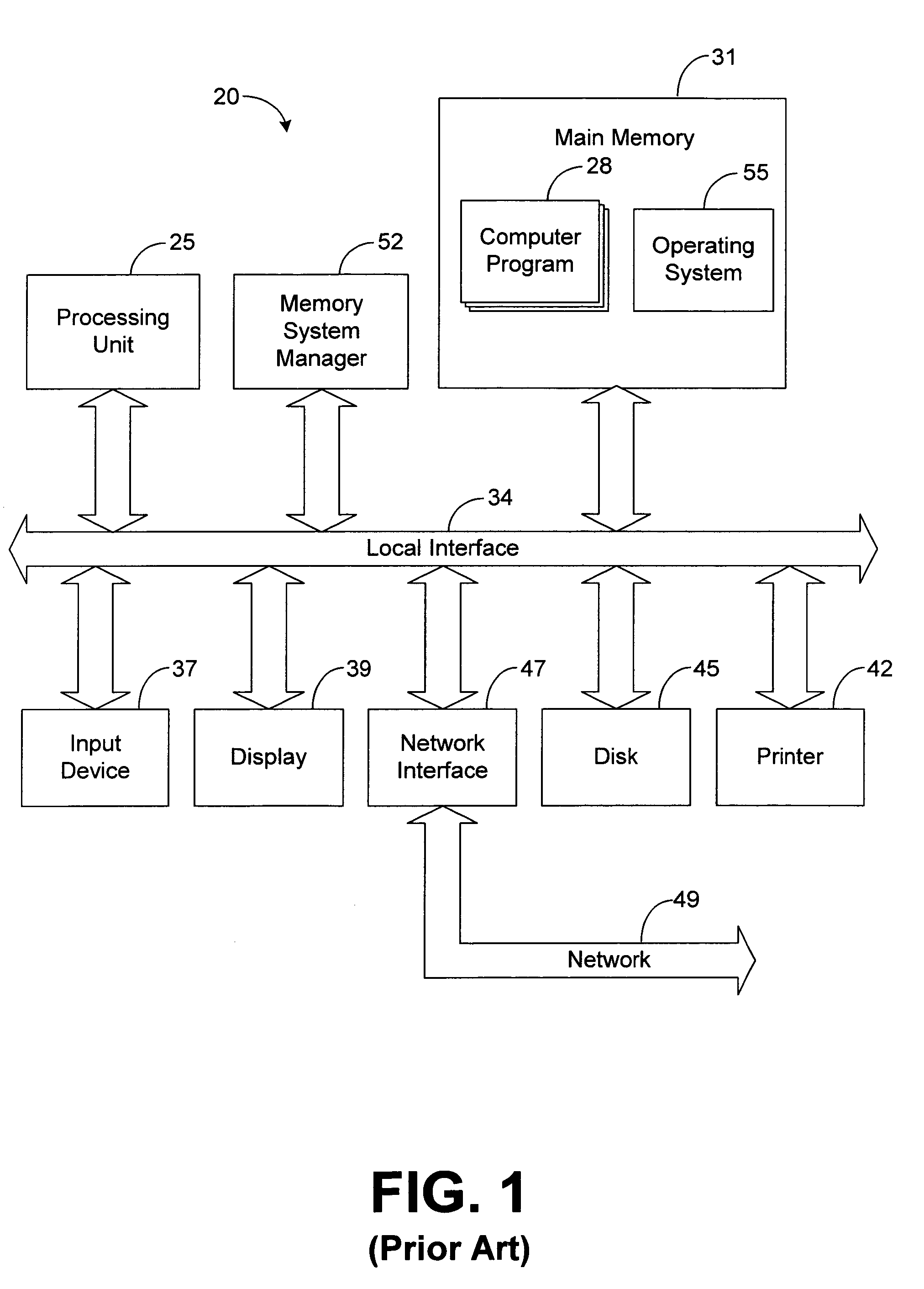

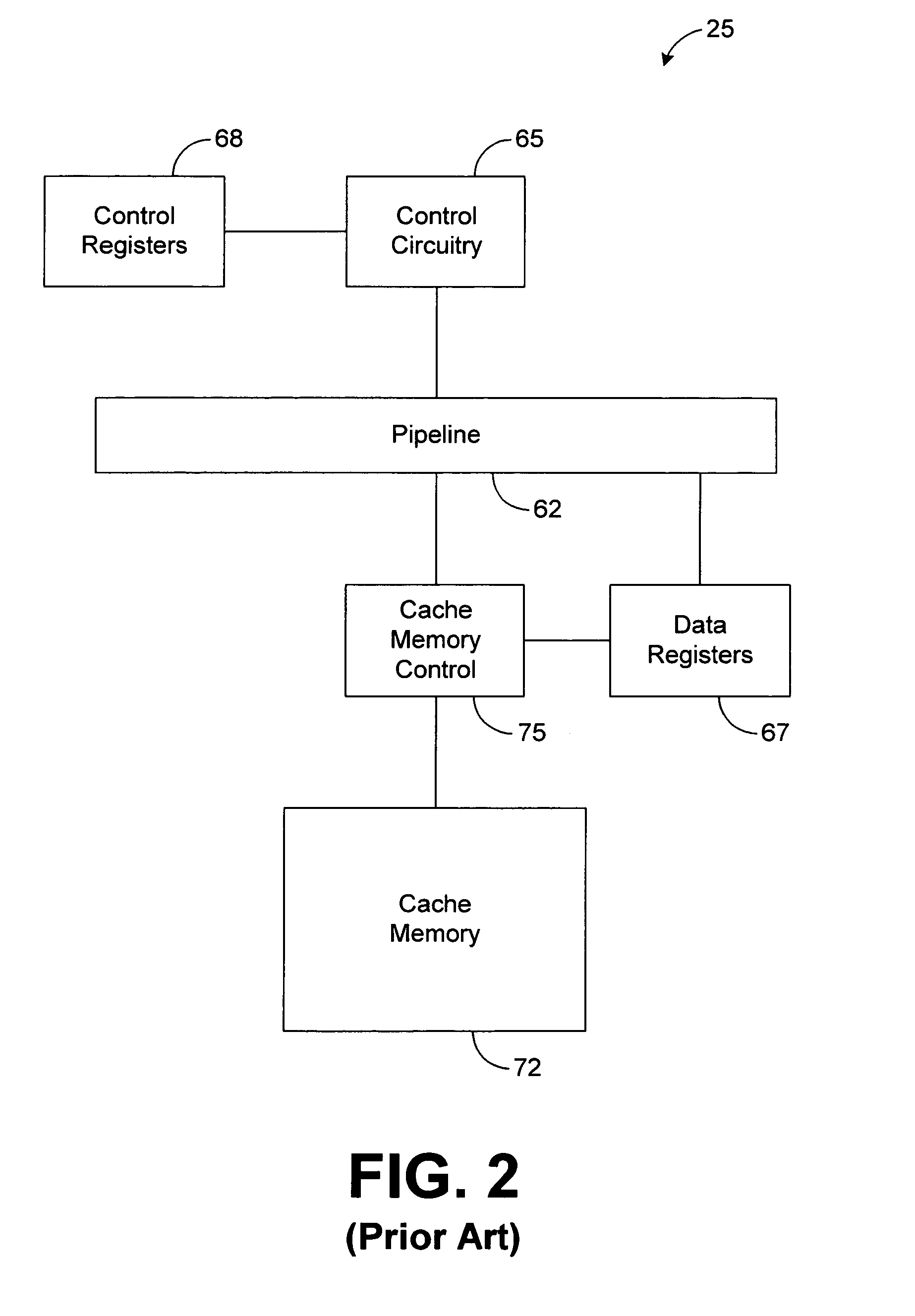

System and method for preloading cache memory in response to an occurrence of a context switch

InactiveUS7191319B1Efficient executionOvercomes inadequacy and deficiencyMemory architecture accessing/allocationDigital computer detailsParallel computingComputer memory

In a multitasking computer system, data is preloaded into cache memory upon the occurrence of a context switch. To this end, processing circuitry stops executing a computer program during a first context switch in response to a first context switch command. Later, the processing circuitry resumes executing the computer program during a second context switch in response to a second context switch command. The memory control circuitry, in response to the second context switch command, identifies an address of computer memory that is storing a data value previously used to execute an instruction of the computer program prior to the first context switch. The memory control circuitry then retrieves the data value from the computer memory and stores the retrieved data value in the cache memory. Accordingly, the retrieved data value is available to the processing circuitry for use in executing instructions of the computer program after the second context switch without the processing circuitry having to request retrieval of the foregoing data value.

Owner:HEWLETT PACKARD DEV CO LP

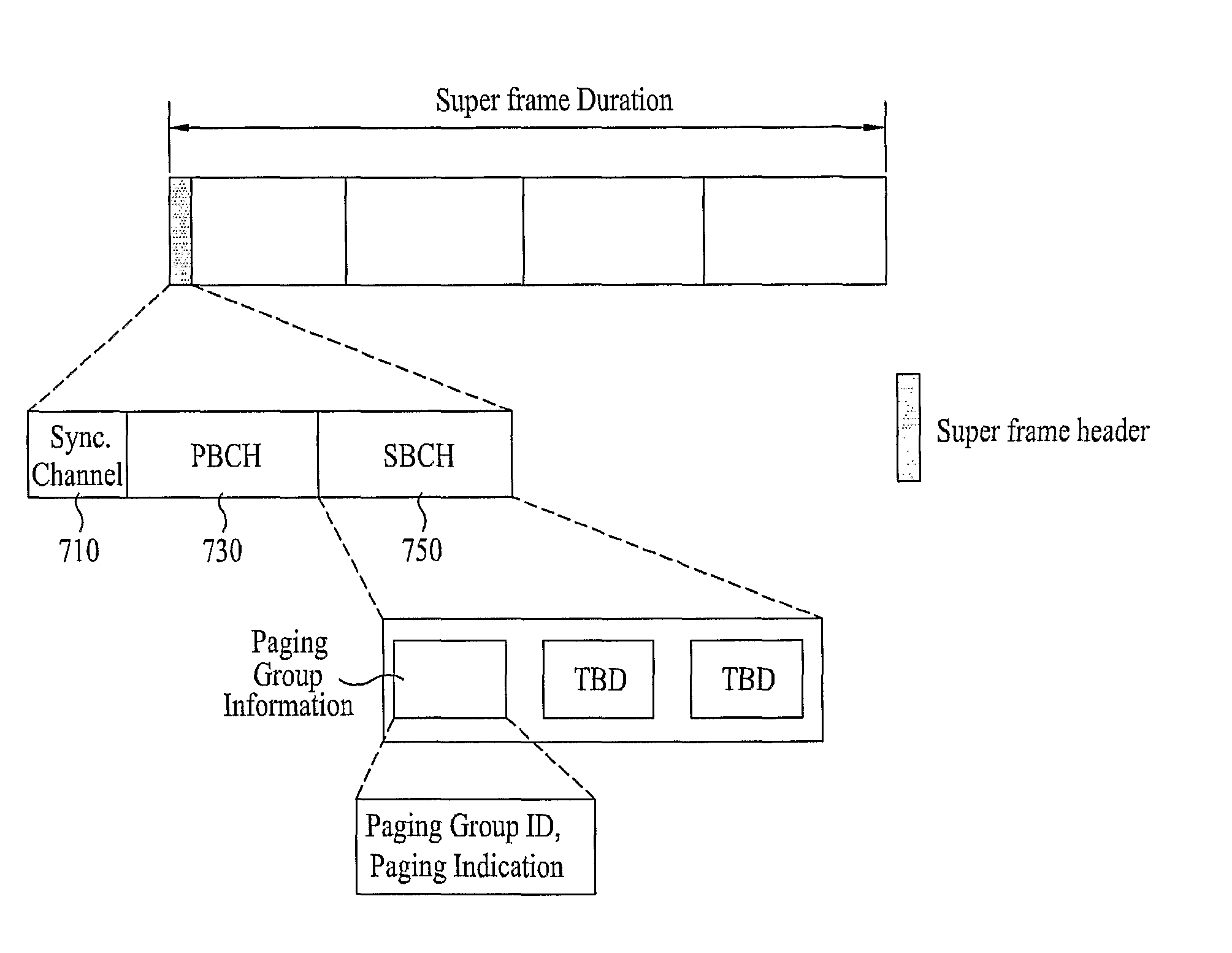

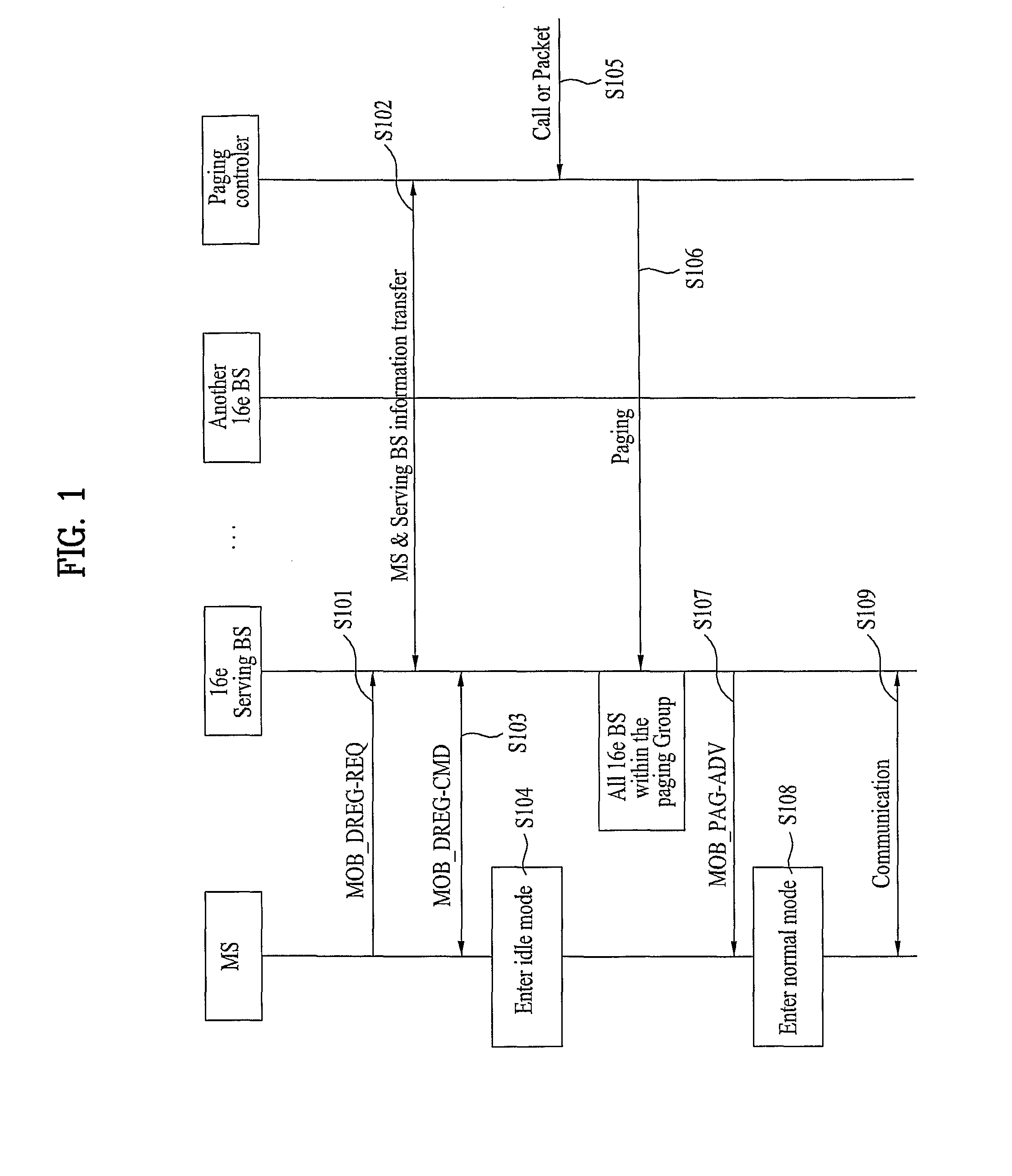

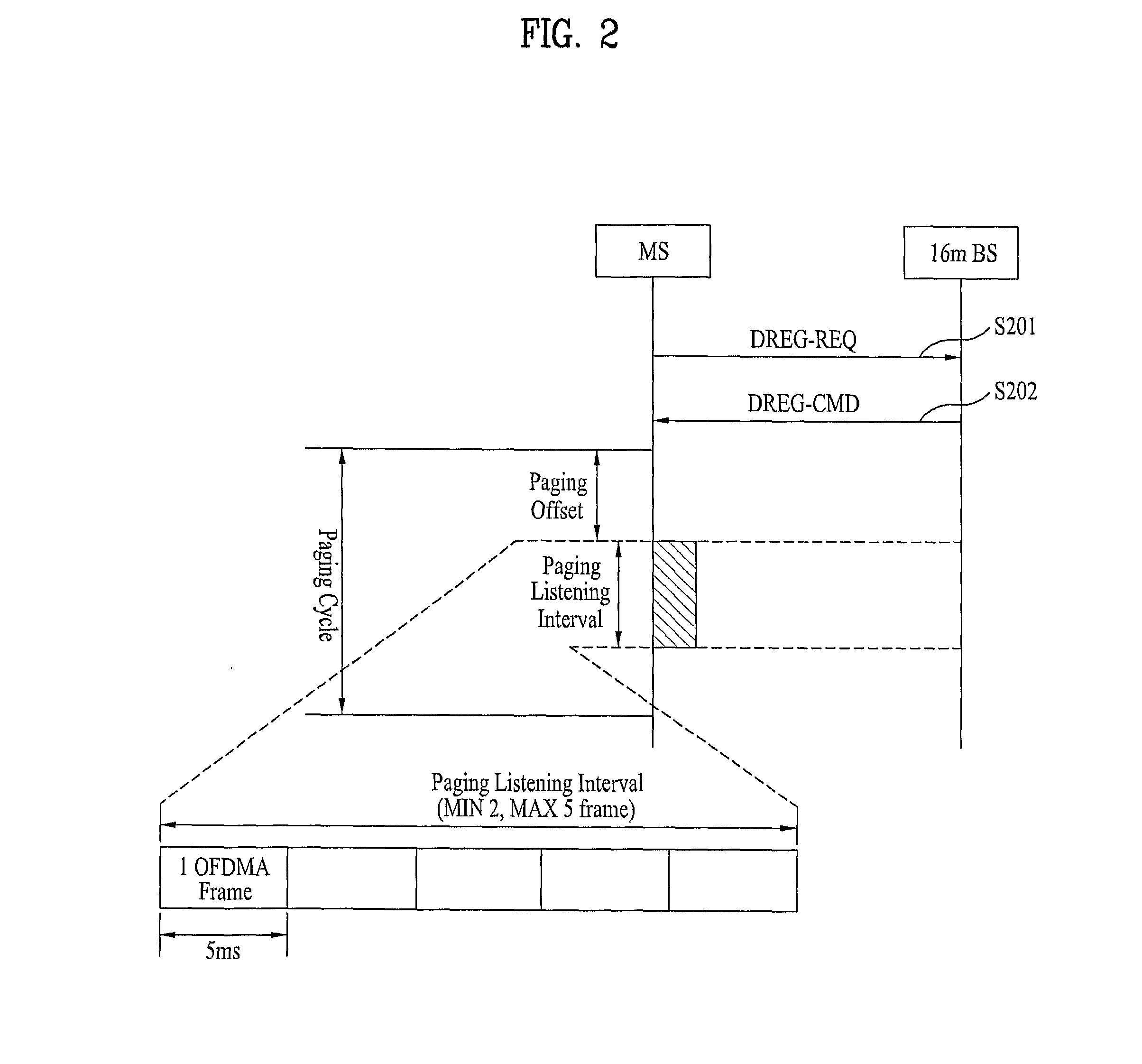

Method of transmitting and receiving paging information

InactiveUS20110134893A1Efficient methodEffective instructionTransmission systemsTime-division multiplexBroadcast channelsPaging

Various methods of transmitting paging information in a wireless access system are disclosed. A method of transmitting paging information from a base station belonging to at least one paging groups according to one embodiment of the present invention includes the steps of allocating a paging group offset (PGO) per one specific one of at least one paging groups, transmitting a message including one paging group offset (PGO) per one specific paging group, and transmitting a broadcast channel (BCH) including paging group formation on the specific paging group at a timing point indicated by the paging group offset.

Owner:LG ELECTRONICS INC

Adaptive training system, method and apparatus

ActiveUS9786193B2Effective instructionEffective trainingCosmonautic condition simulationsBatteries circuit arrangementsAdaptive learningComputerized system

A system and method for training a student employ a simulation station that displays output to the student and receives input. The computer system has a rules engine operating on it and computer accessible data storage storing (i) learning object data including learning objects configured to provide interaction with the student at the simulation system and (ii) rule data defining a plurality of rules accessed by the rules engine. The rules data includes, for each rule, respective (a) if-portion data defining a condition of data and (b) then-portion data defining an action to be performed at the simulation station. The rules engine causes the computer system to perform the action when the condition of data is present in the data storage. For at least some of the rules, the action comprises output of one of the learning objects so as to interact with the student. The system may be networked with middleware and adapters that map data received over the network to rules engine memory.

Owner:CAE USA INC

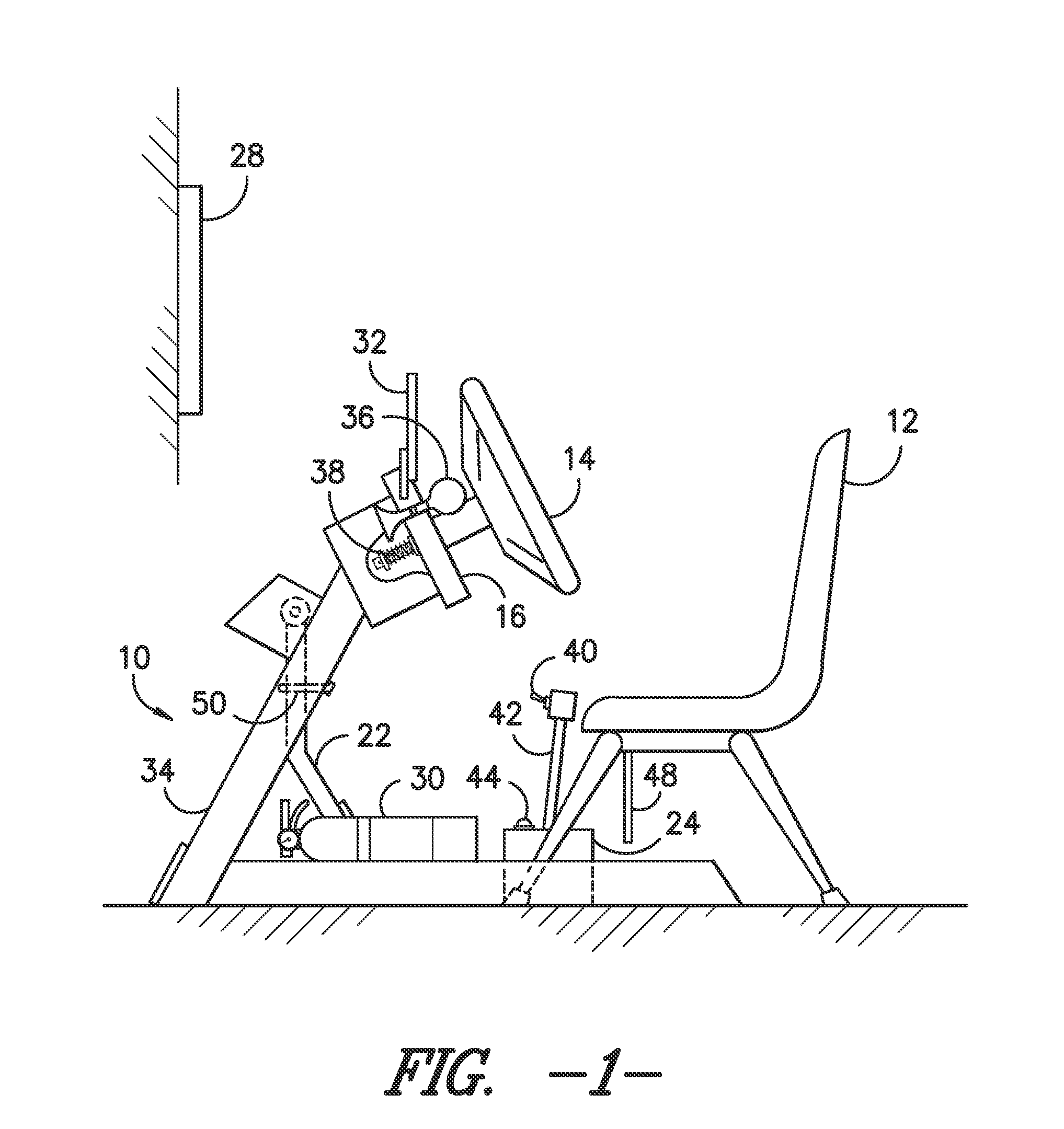

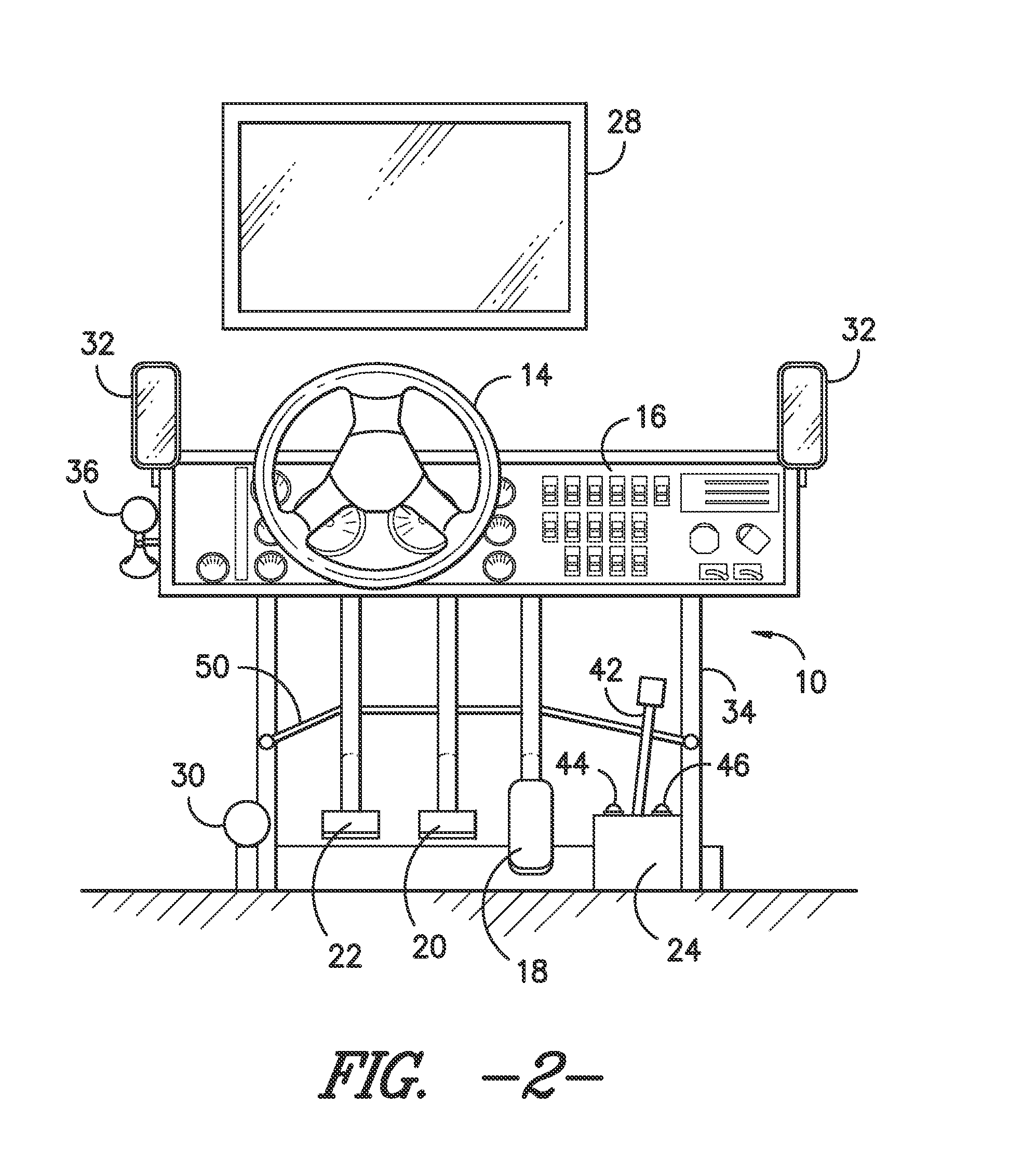

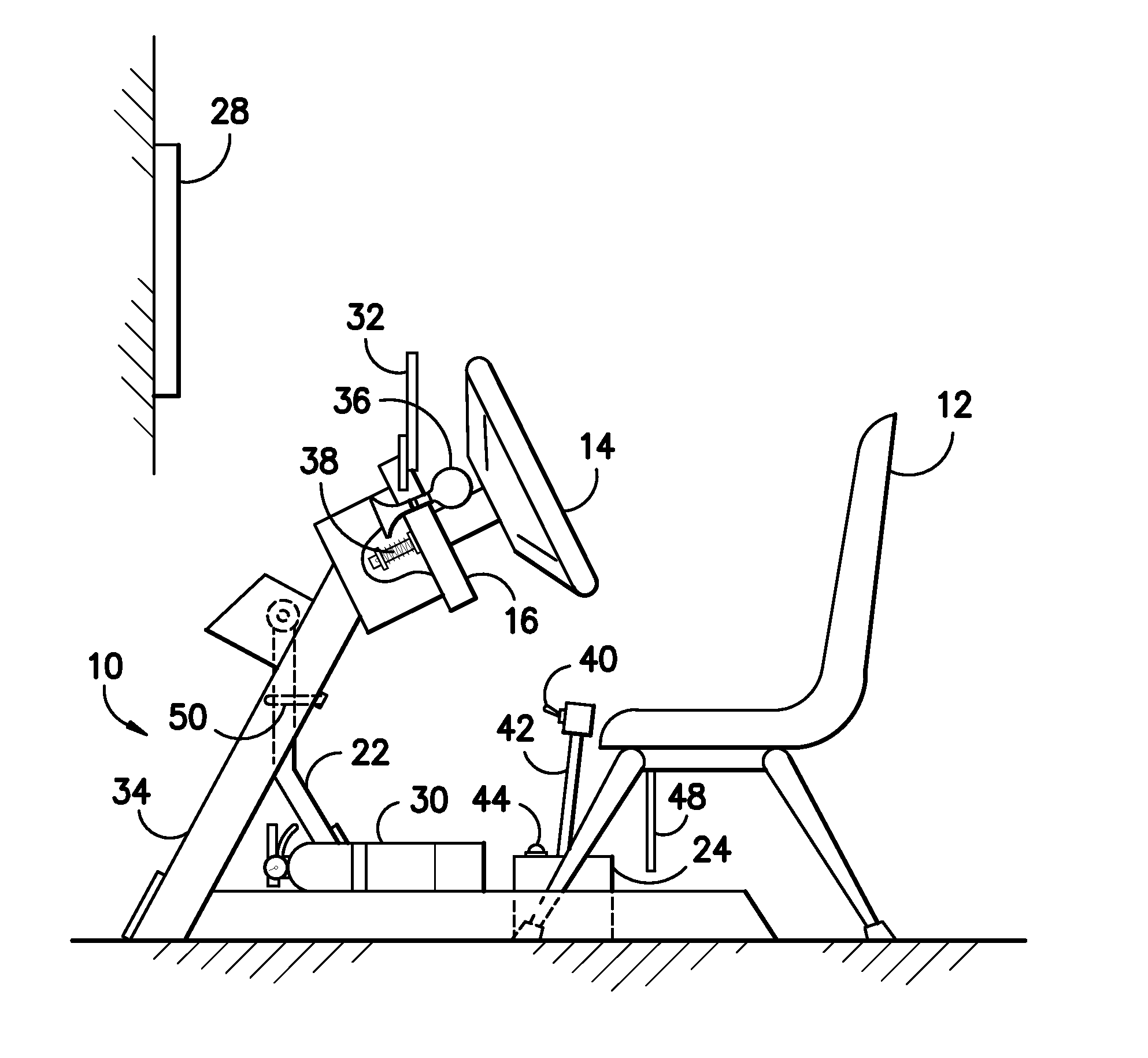

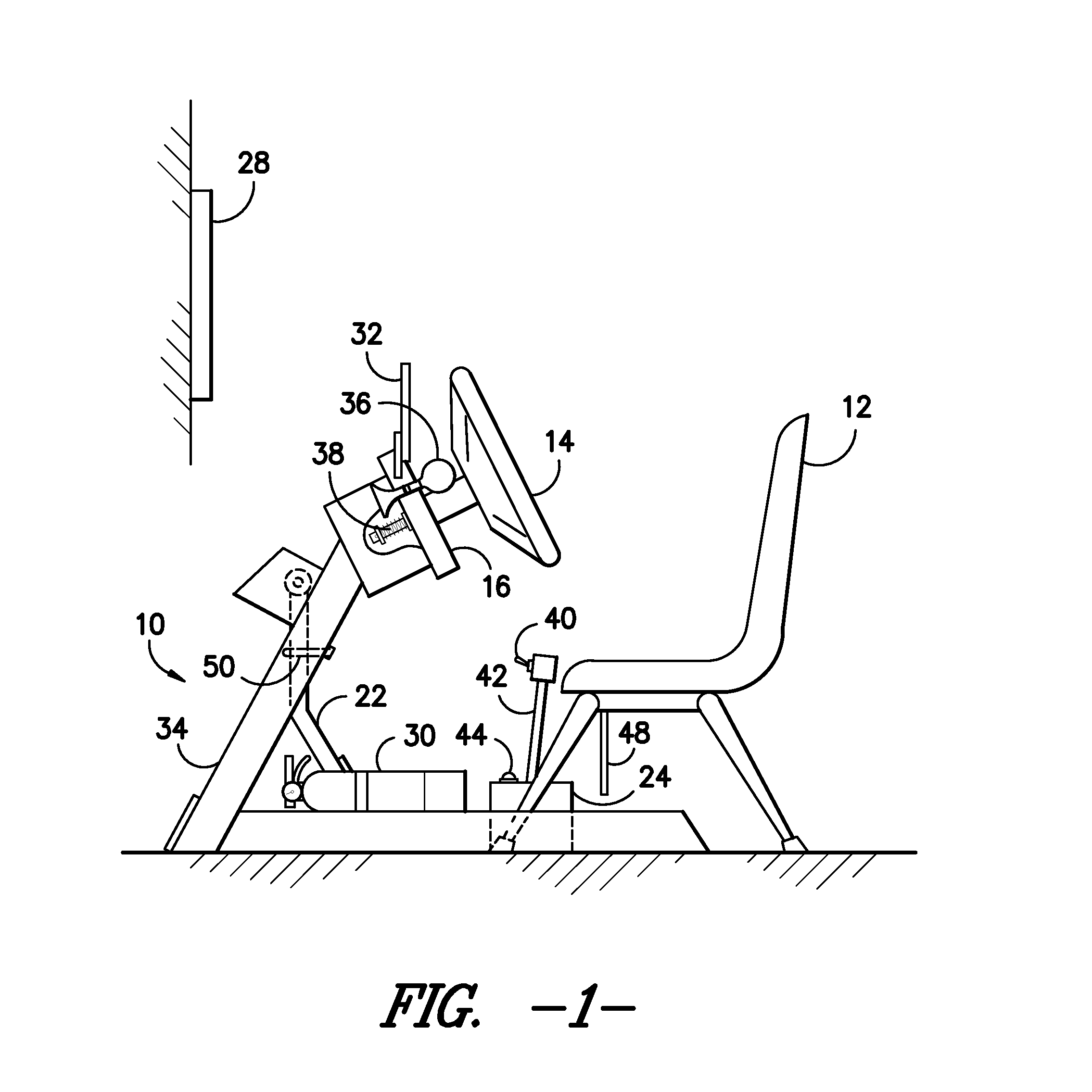

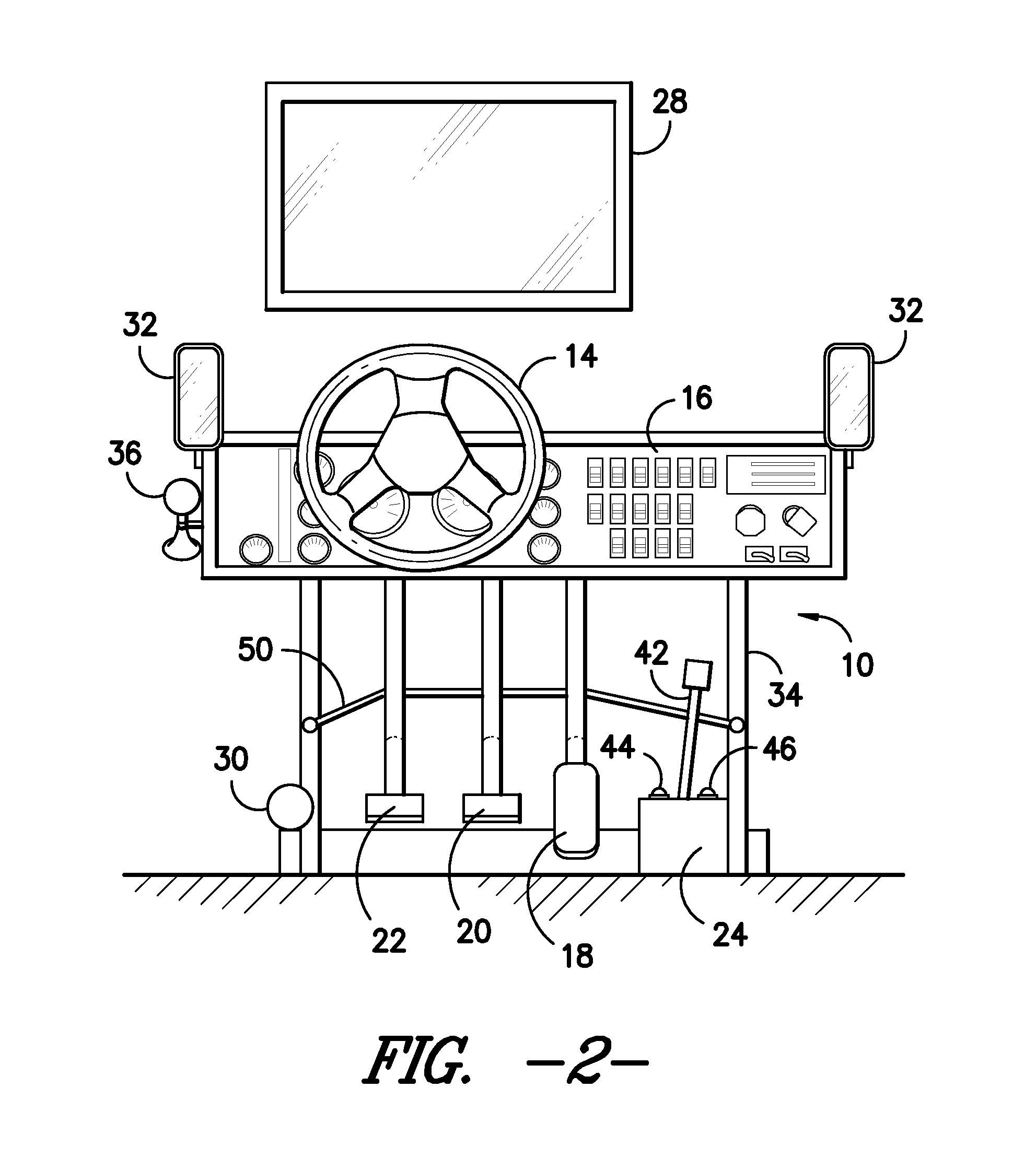

Truck driving simulator and training method

InactiveUS20130149673A1Effective instructionSafe and efficient handlingCosmonautic condition simulationsSimulatorsDashboardDriver/operator

A truck driving simulator is provided, comprising a simulated cab with a steering wheel and dashboard layout, foot pedals (accelerator, clutch, brake), gear shifting mechanism, and a video screen. In another embodiment, a series of such simulators may be placed in a classroom together with a single large screen video monitor or television at the front of the class, so that multiple students can follow along with the video simulation under the supervision of a teacher or instructor. The video monitor(s) may be used to show video footage of the actual route that will be used to test the drivers for their trucker's license. This arrangement allows students to repeatedly practice driving the actual course used for their driver's license test, and to learn concepts like clutching, double clutching and switching gears without risking damage to an actual truck and transmission.

Owner:VERATHON

Truck driving simulator and training method

InactiveUS20120009547A1Effective instructionSafe and efficient handlingCosmonautic condition simulationsSimulatorsDashboardSteering wheel

A truck driving simulator is provided, comprising a simulated cab with a steering wheel and dashboard layout, foot pedals (accelerator, clutch, brake), gear shifting mechanism, and a video screen. In another embodiment, a series of such simulators may be placed in a classroom together with a single large screen video monitor or television at the front of the class, so that multiple students can follow along with the video simulation under the supervision of a teacher or instructor. The video monitor(s) may be used to show video footage of the actual route that will be used to test the drivers for their trucker's license. This arrangement allows students to repeatedly practice driving the actual course used for their driver's license test, and to learn concepts like clutching, double clutching and switching gears without risking damage to an actual truck and transmission.

Owner:MILLER JAMES E

A data processing apparatus and method for executing a stream of instructions out of order with respect to original program order

ActiveUS20170109172A1Reduce energy consumptionEffective instructionRegister arrangementsConcurrent instruction executionData processingImproved performance

A data processing apparatus and method are provided for executing a stream of instructions out-of-order with respect to original program order. At least some of the instructions in the stream identify one or more architectural registers from a set of architectural registers. The apparatus comprises a plurality of out-of-order components configured to manage execution of a first subset of instructions out-of-order, the plurality of out-of-order components being configured to remove false dependencies between instructions in the first subset. The plurality of out-of-order components include a first issue queue into which the instructions in the first subset are buffered prior to execution. A second issue queue is used to buffer a second subset of instructions prior to execution, the second subset of instructions being constrained to execute in order. Issue control circuitry is configured to reference both issue queues in order to determine an order of execution of instructions, and is configured to constrain the order of execution of the first subset of instructions by true dependencies between the instructions in both the first and second issue queues, and to constrain the order of execution of the second subset of instructions by both the true dependencies and the false dependencies between the instructions in both the first and second issue queues. This approach provides improved performance and / or reduced energy consumption.

Owner:THE RGT OF THE UNIV OF MICHIGAN

Pediatric congenital heart defect repair model

InactiveUS20050084834A1Easy to understandImprove performanceEducational modelsBiomedical engineeringMedical treatment

Owner:BALBY BY DESIGN

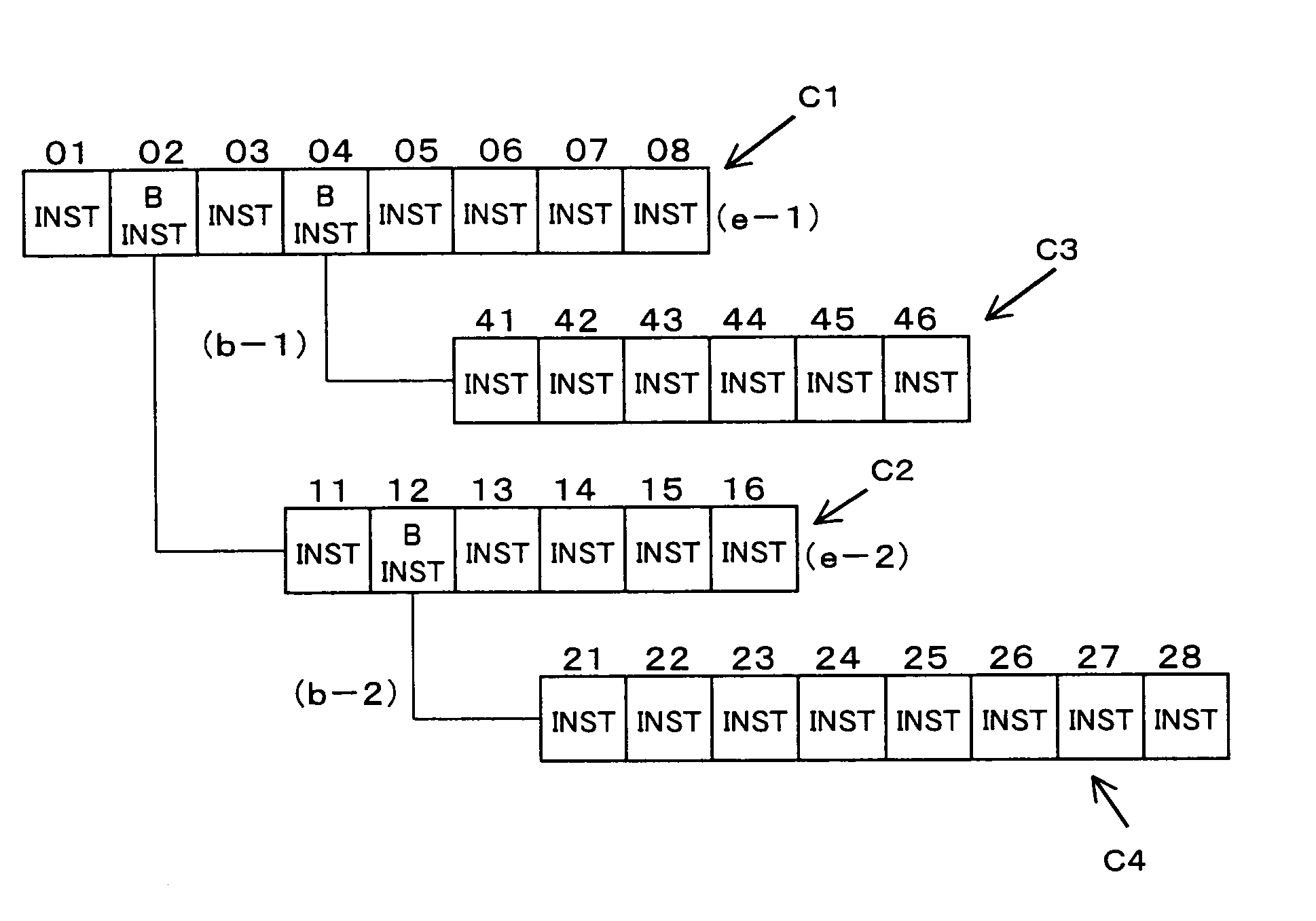

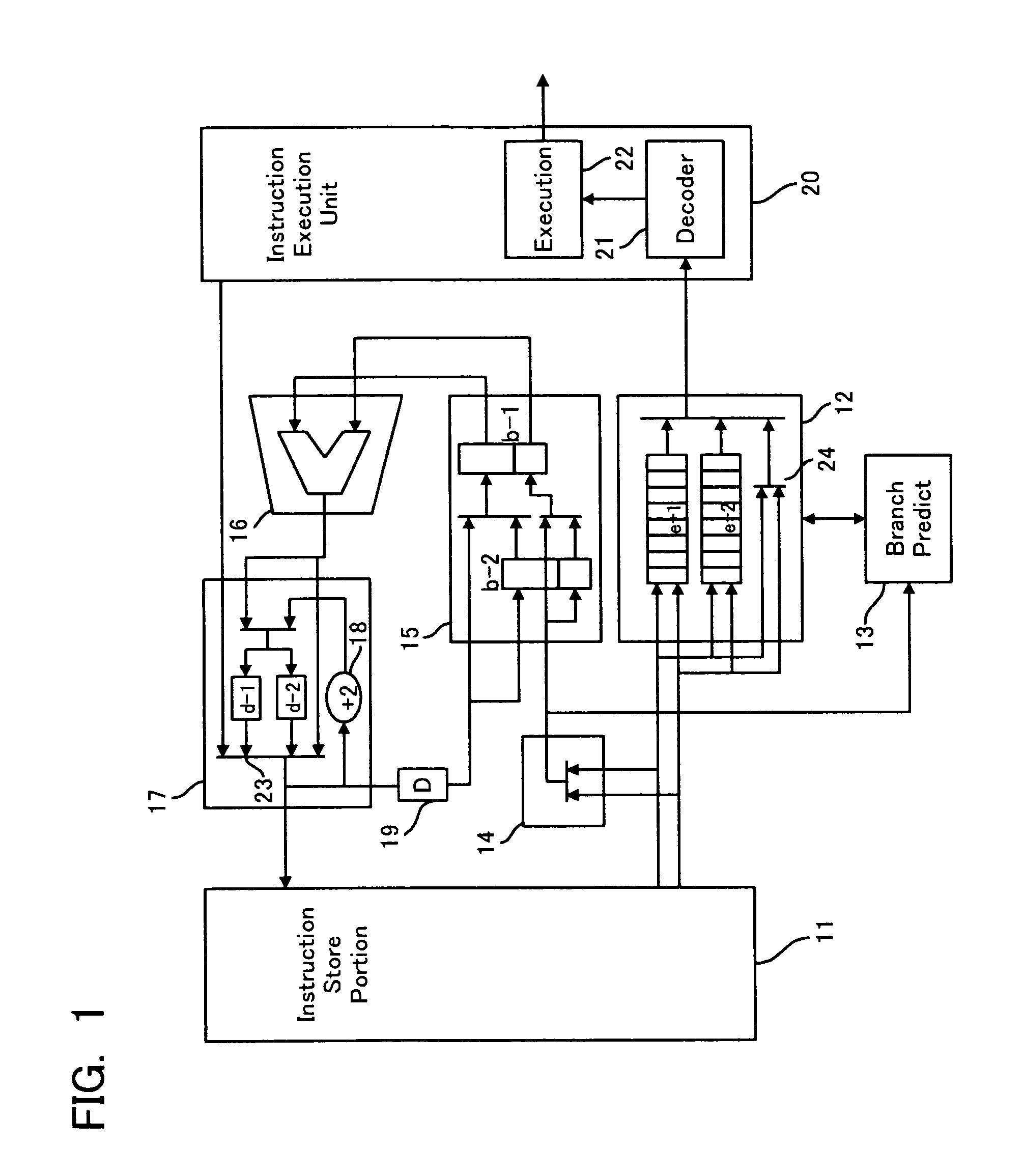

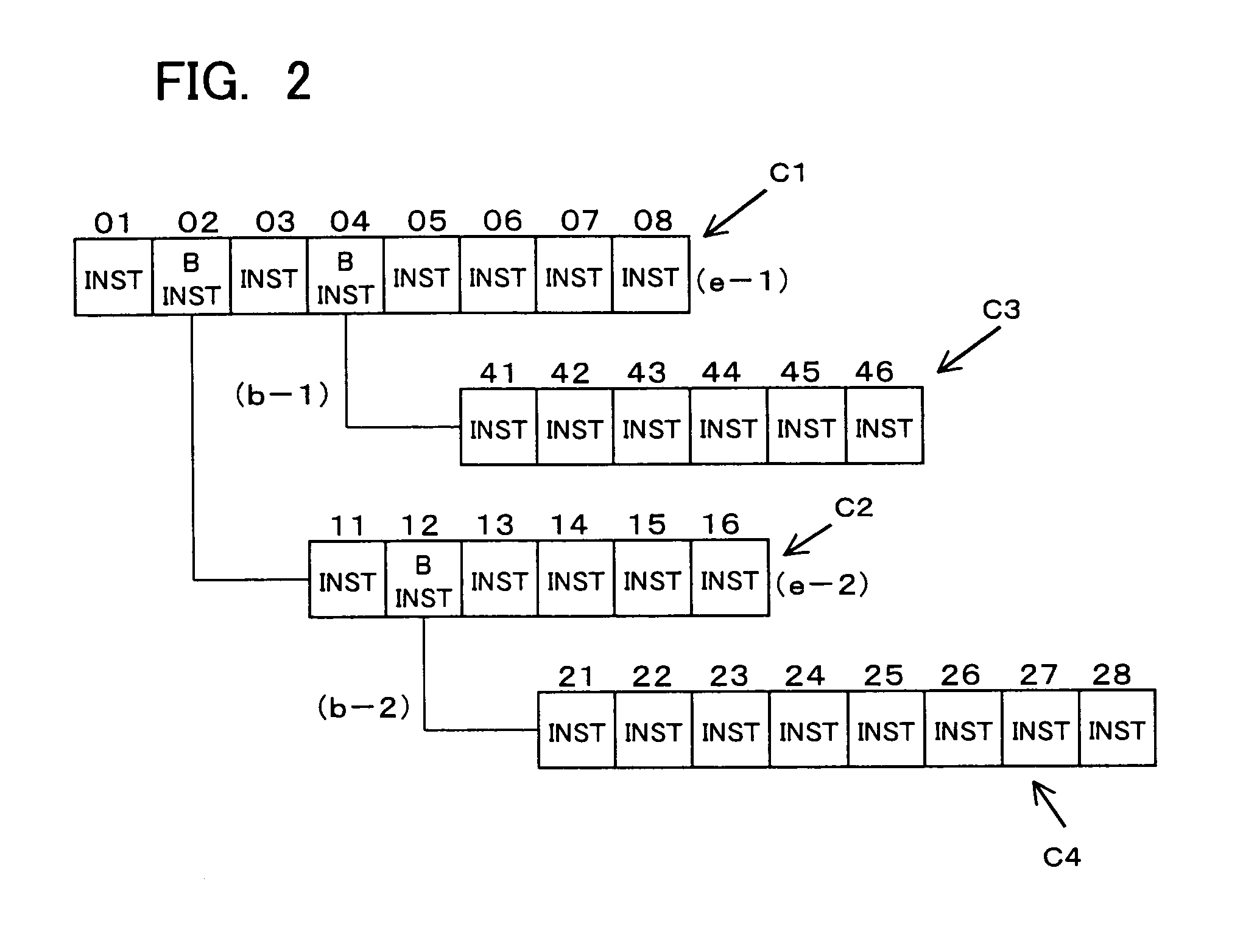

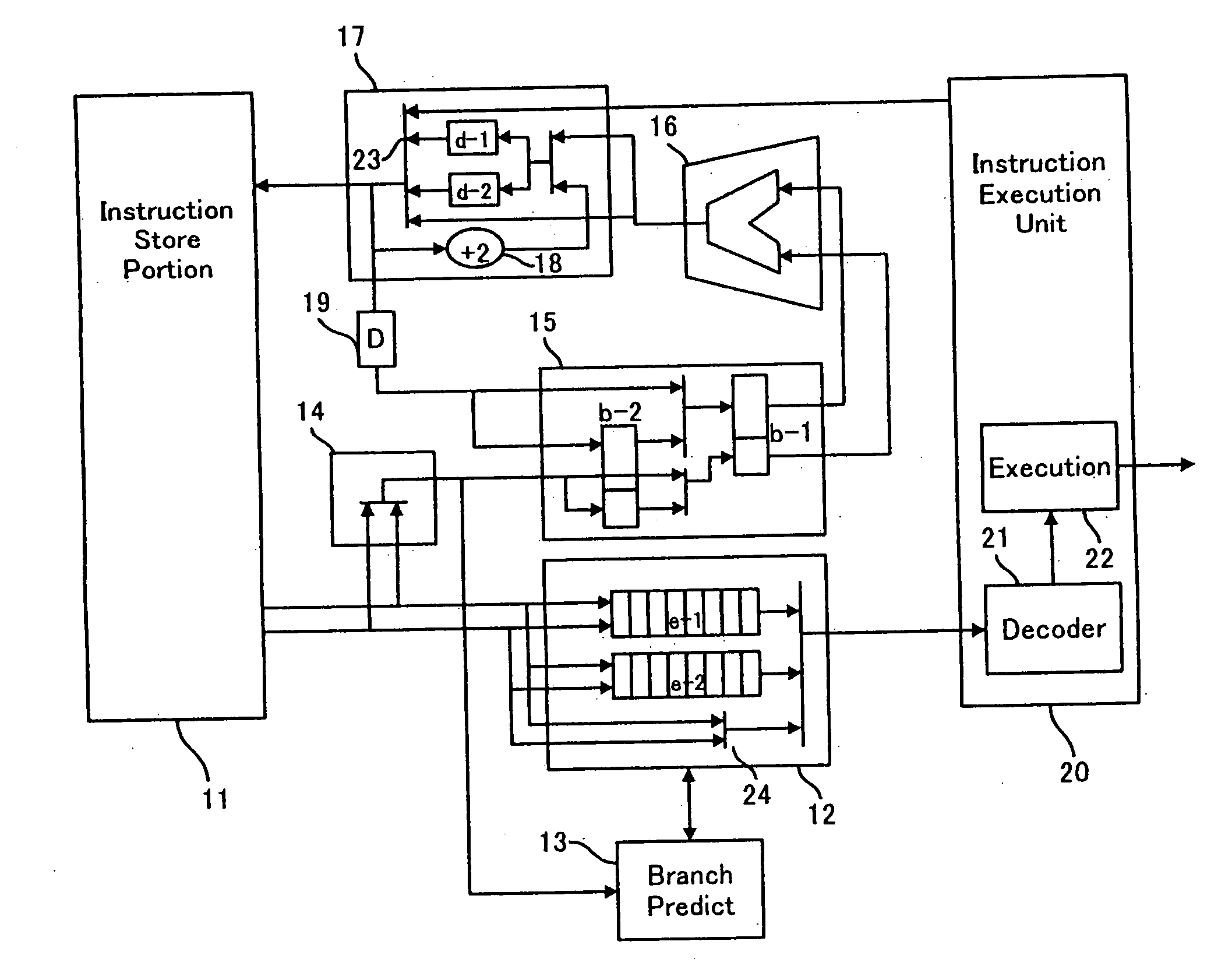

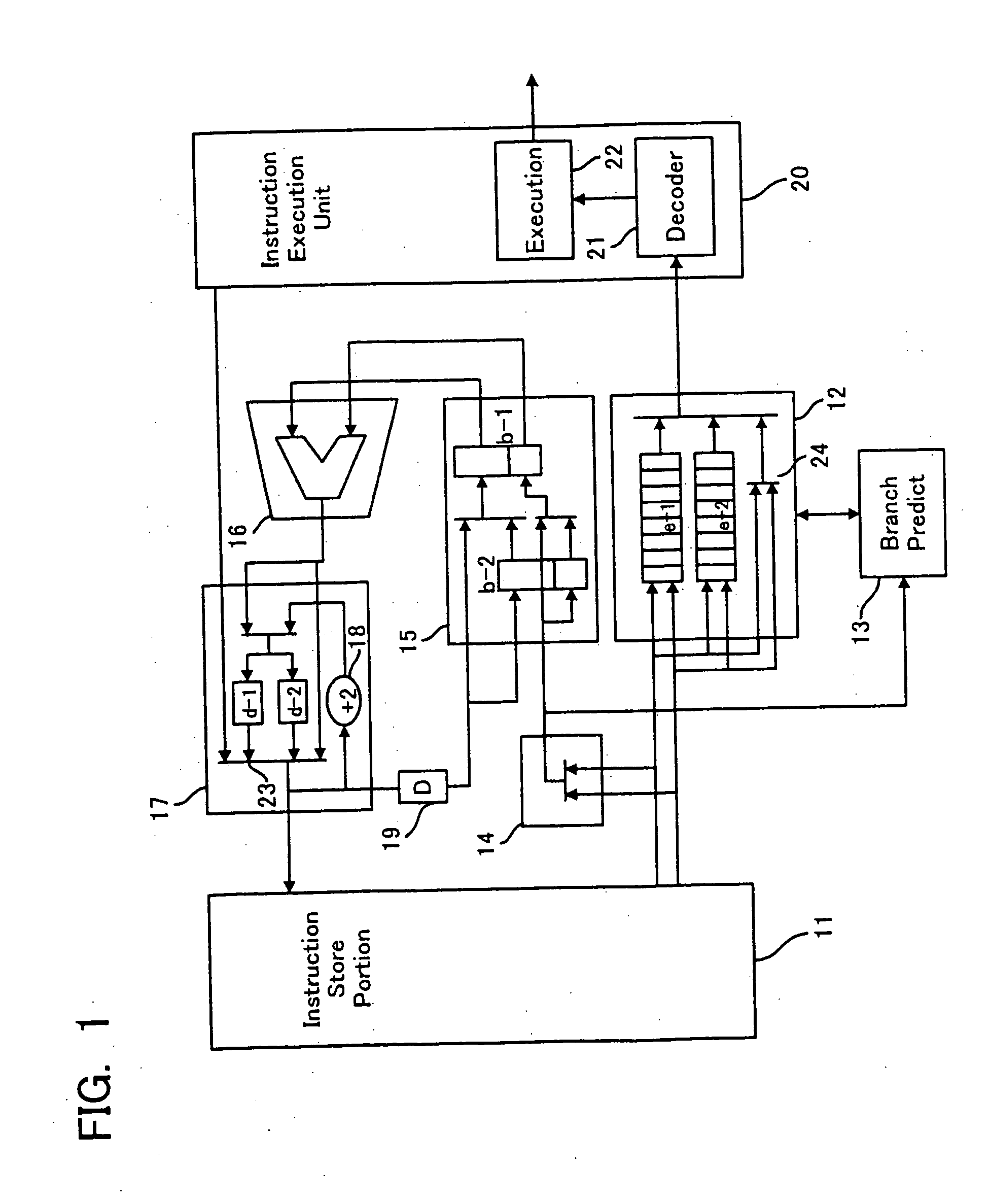

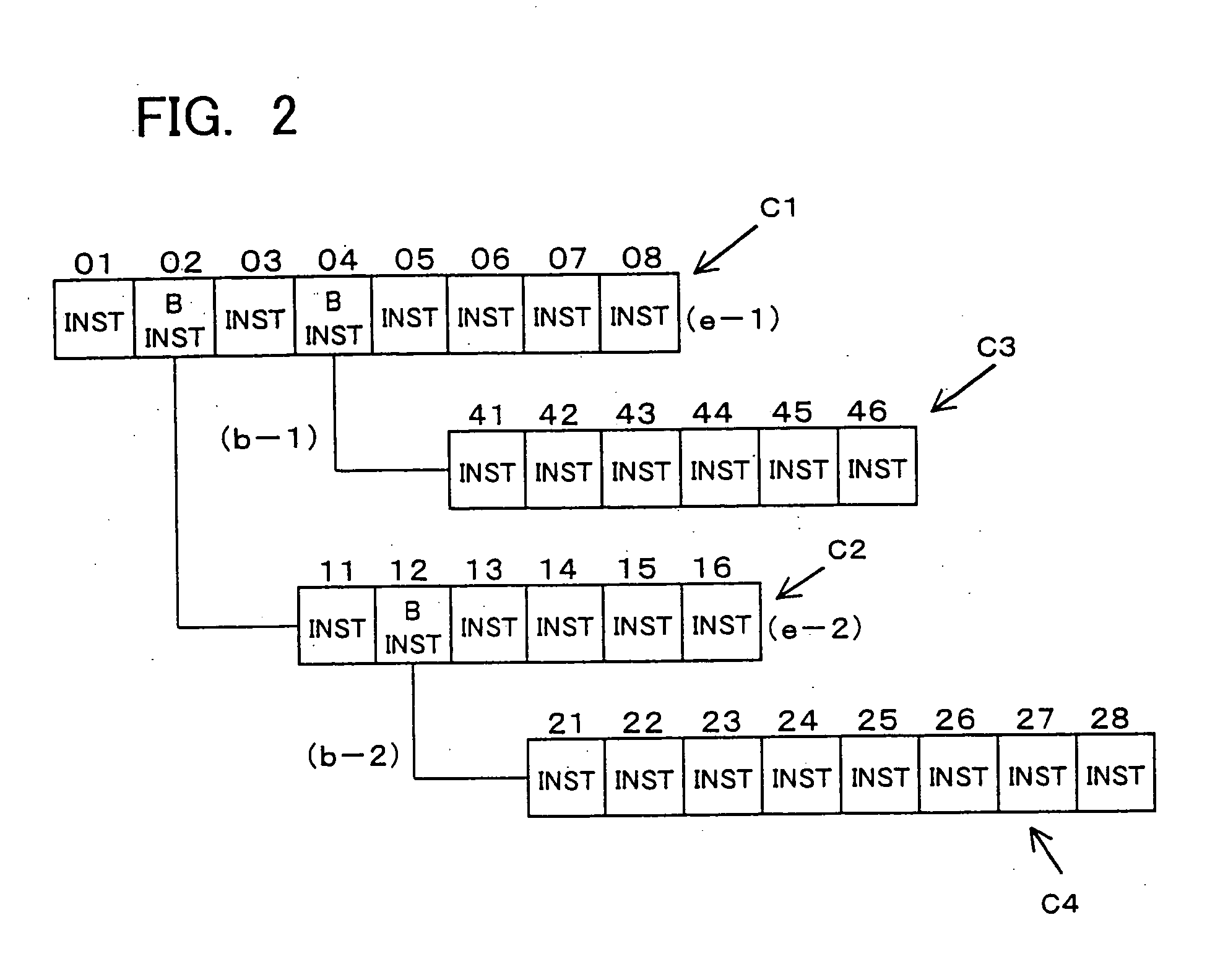

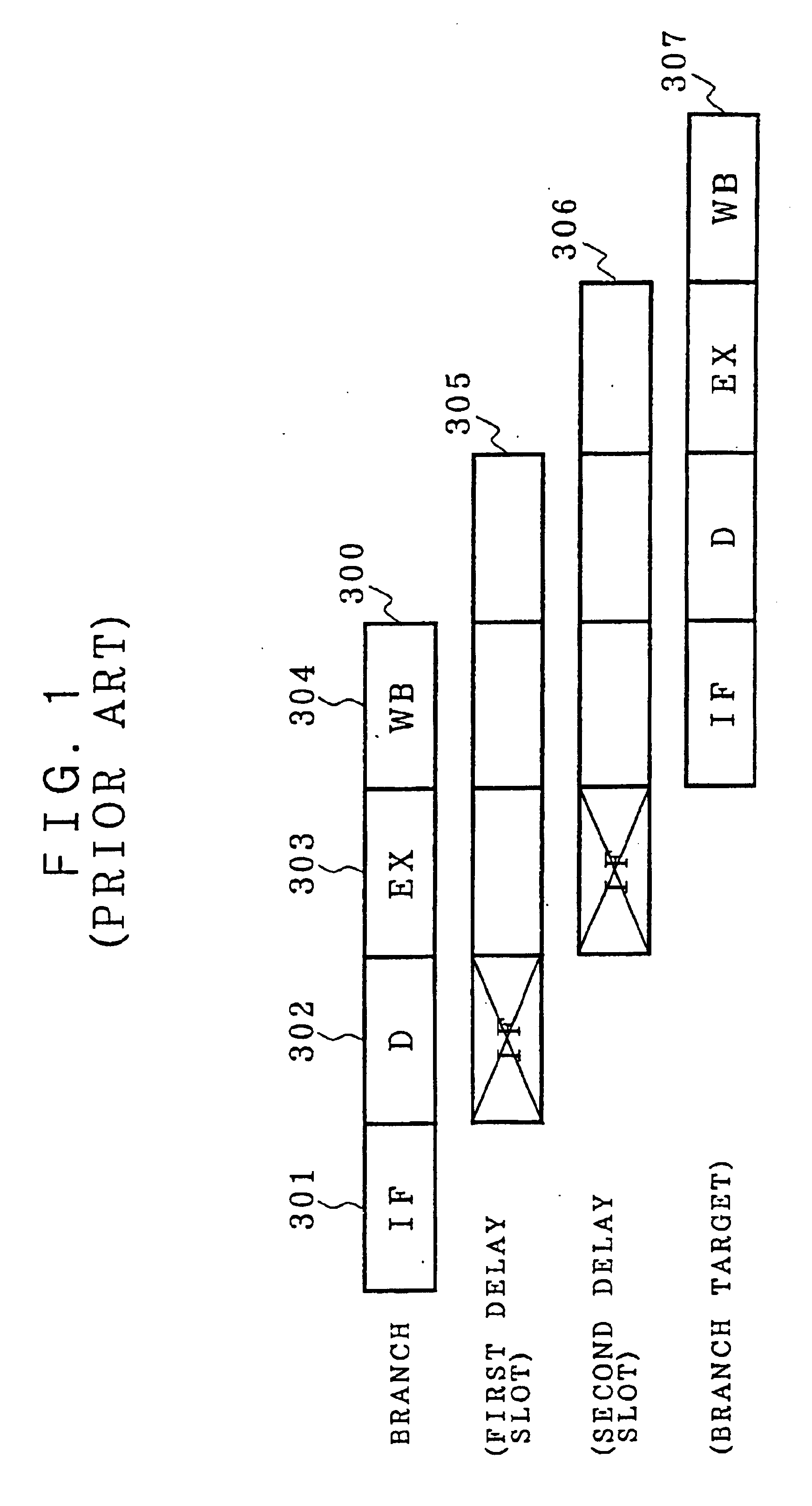

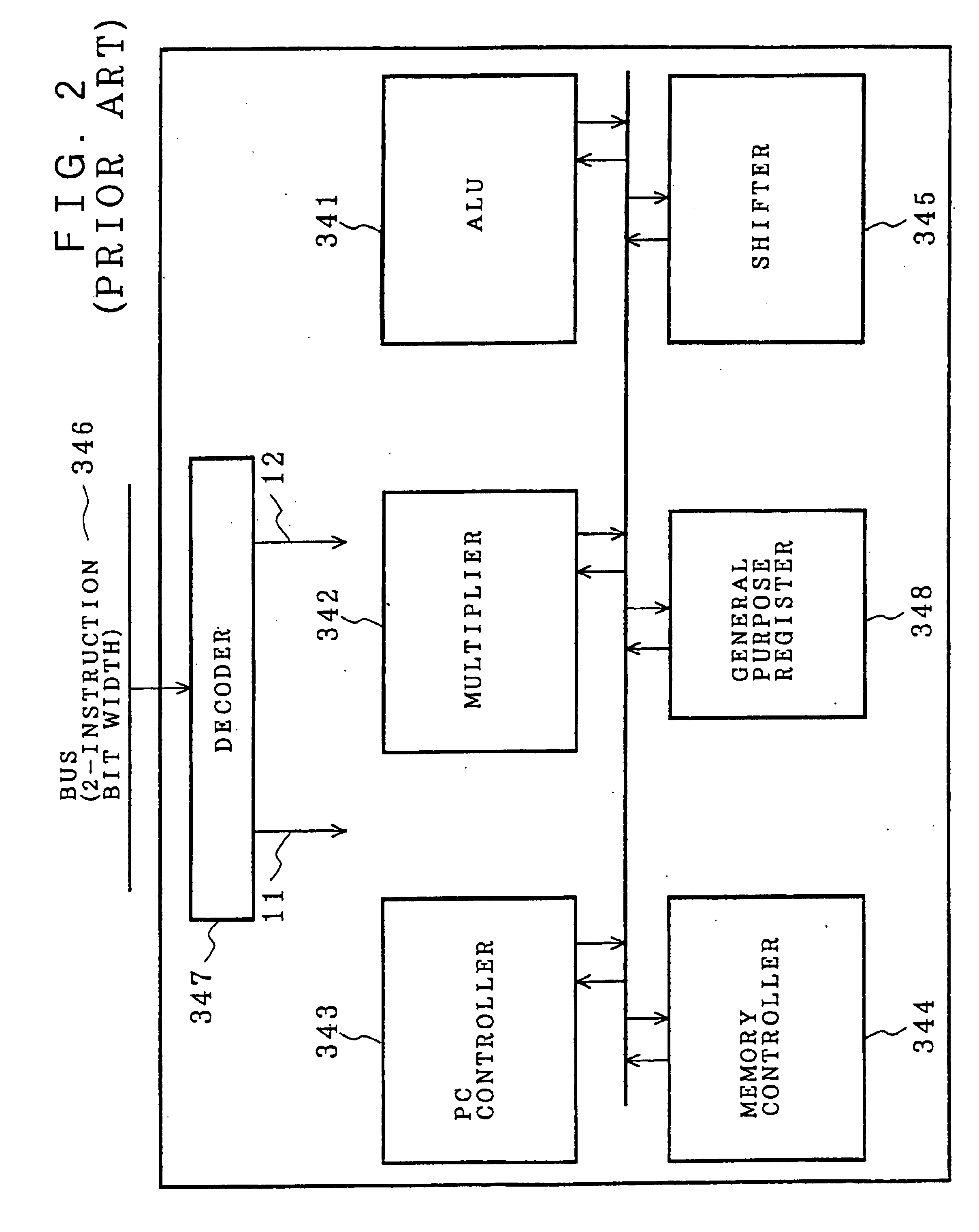

Processing device for buffering sequential and target sequences and target address information for multiple branch instructions

InactiveUS7134004B1Restrict increase hardwareReduce confusionDigital computer detailsConcurrent instruction executionInformation processingParallel computing

An information processing device reads, buffers, decodes and executes instructions from an instruction store portion by pipeline processing includes: an instruction reading request portion which assigns a read address to the instruction store portion, an instruction buffering portion which includes a plurality of instruction buffers which buffer an instruction sequence read from the instruction store portion; an instruction execution unit which decodes and executes instructions buffered by the instruction buffering portion. A branching instruction detection portion detects a branching instruction in the instruction sequence read from the instruction store portion. A branch target address information buffering portion includes a plurality of branch target address information buffers which, when the branching instruction detection portion has detected a branching instruction, buffer the branch target address information for generating the branch target address of the branching instruction.

Owner:FUJITSU LTD +1

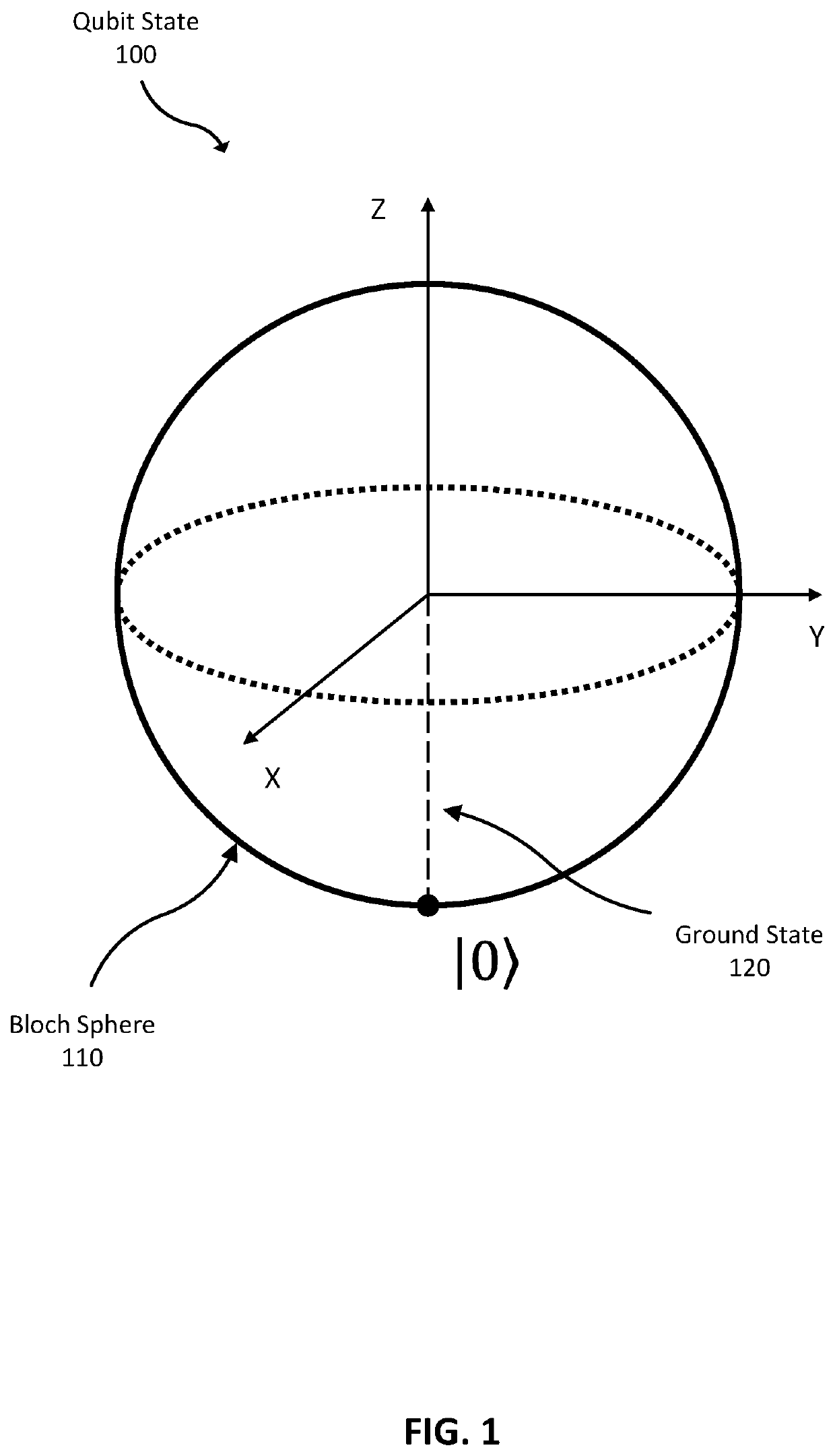

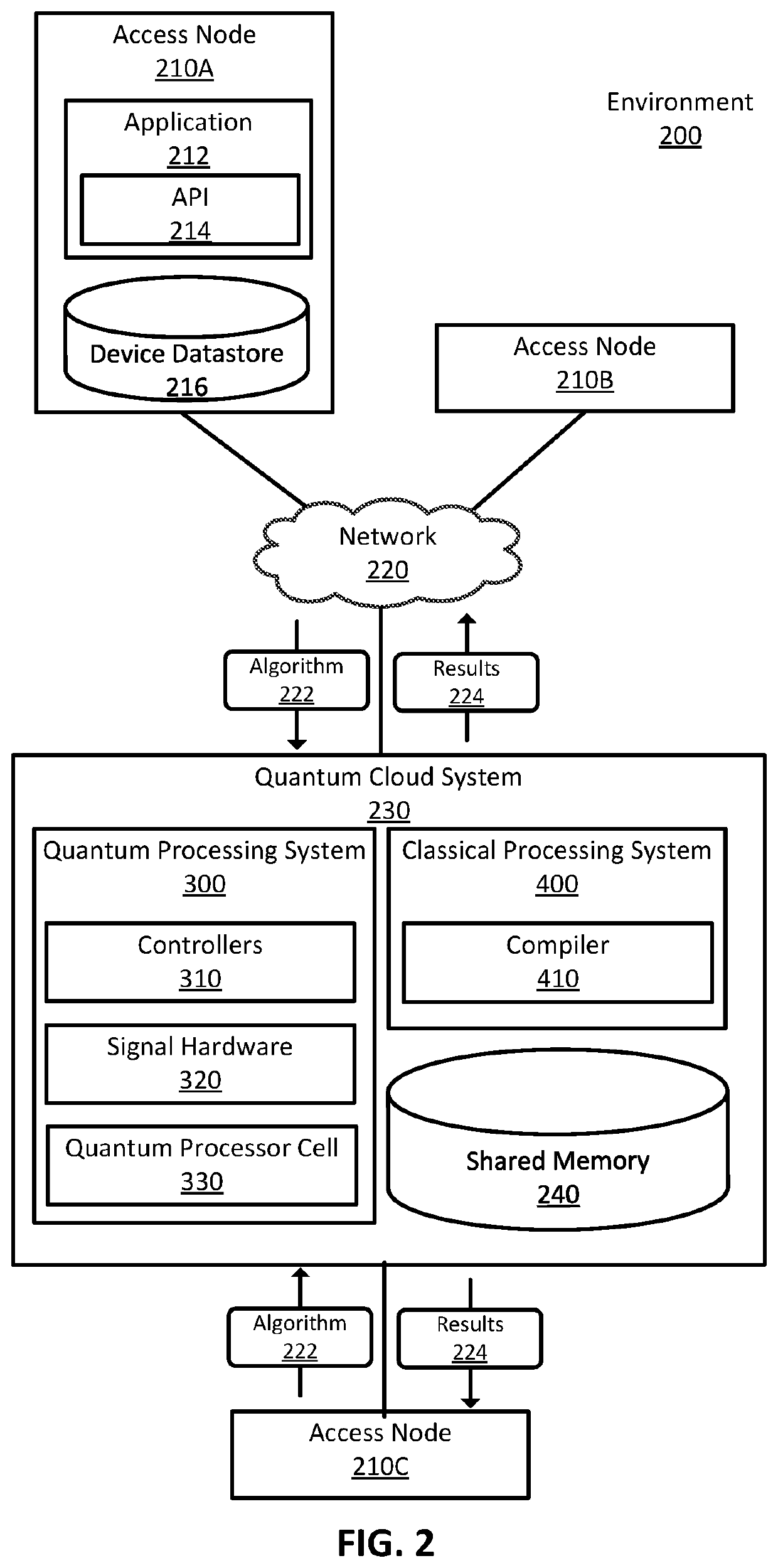

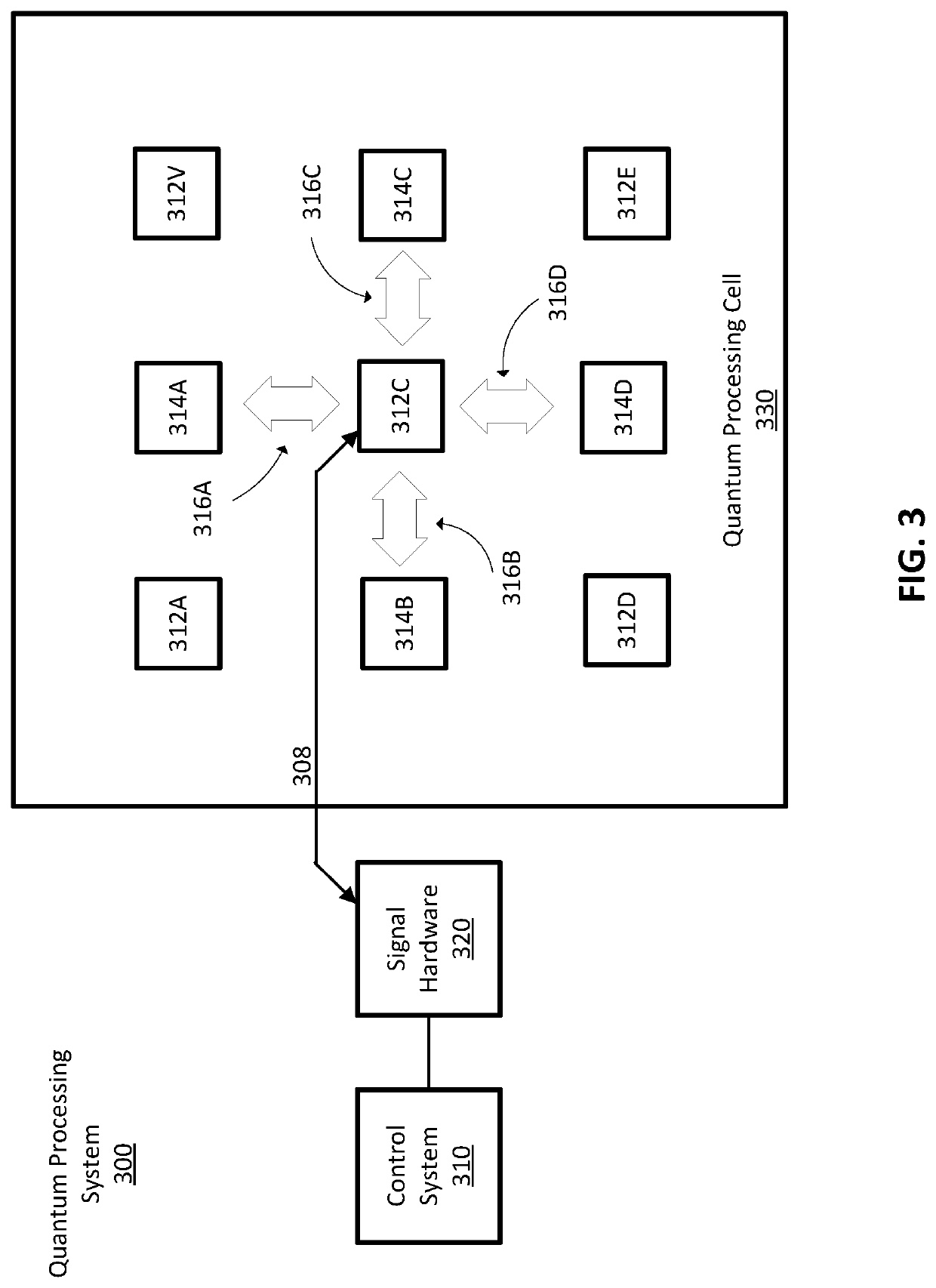

Quantum instruction compiler for optimizing hybrid algorithms

ActiveUS11494681B1Effective instructionQuantum computersKernel methodsQuantum algorithmParallel computing

A compiler for a gate-based superconducting quantum computer compiles hybrid classical / quantum algorithms for quantum processing cells with different configurations. The compiler inputs the algorithm and outputs code in a target language executable by a quantum processing cell of a quantum processing system that can execute the algorithm. The compiler includes various functionality, such as: parsing, analyzing control flows, addressing, compressing, and translating. The compiler optimizes algorithms in various manners using the functionality. Some optimizations include addressing efficiently, compressing based on simulations, and translating for efficient execution of parametric functions. The compiler may function in the environment of a cloud quantum computing system. The cloud quantum computing system may receive algorithms from remote access nodes for execution on local classical and quantum computing systems.

Owner:RIGETTI & CO

Information processing device

InactiveUS20060224870A1Restrict increase hardwareReduce confusionDigital computer detailsConcurrent instruction executionInformation processingParallel computing

The present invention is defined in that an information processing device which reads, buffers, decodes and executes instructions from an instruction store portion by pipeline processing comprises: an instruction reading request portion which assigns a read address to the instruction store portion; an instruction buffering portion including a plurality of instruction buffers which buffer an instruction sequence read from the instruction store portion; an instruction execution unit which decodes and executes instructions buffered by the instruction buffering portion; a branching instruction detection portion which detects a branching instruction in the instruction sequence read from the instruction store portion; and a branch target address information buffering portion including a plurality of branch target address information buffers which, when the branching instruction detection portion has detected a branching instruction, buffer the branch target address information for generating the branch target address of the branching instruction; wherein, when the branching instruction detection portion has detected a branching instruction, either the branch target address information of the branching instruction is stored in one of the plurality of branch target address information buffers, or the branch target instruction sequence of the branching instruction is stored in one of the plurality of instruction buffers in addition to the storing in the branch target address information buffer.

Owner:TAGO SHIN ICHIRO +7

Method, system and device for signaling, guiding and alerting

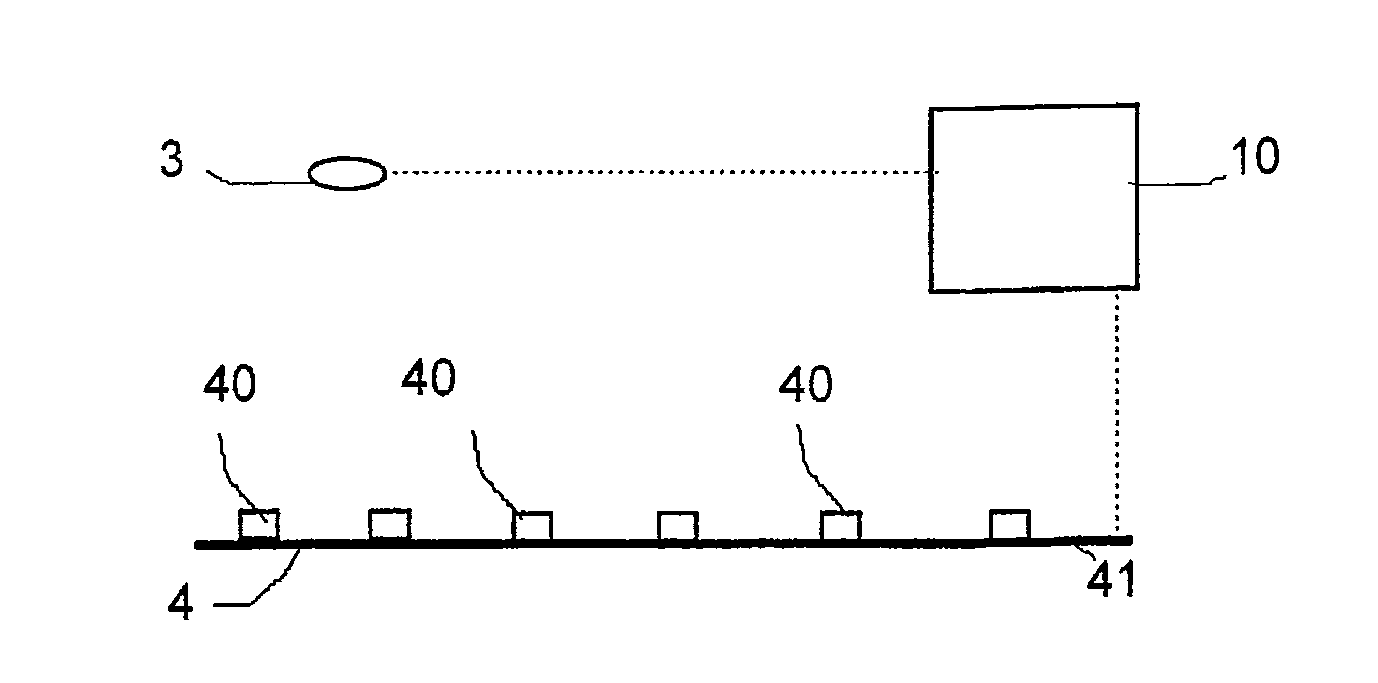

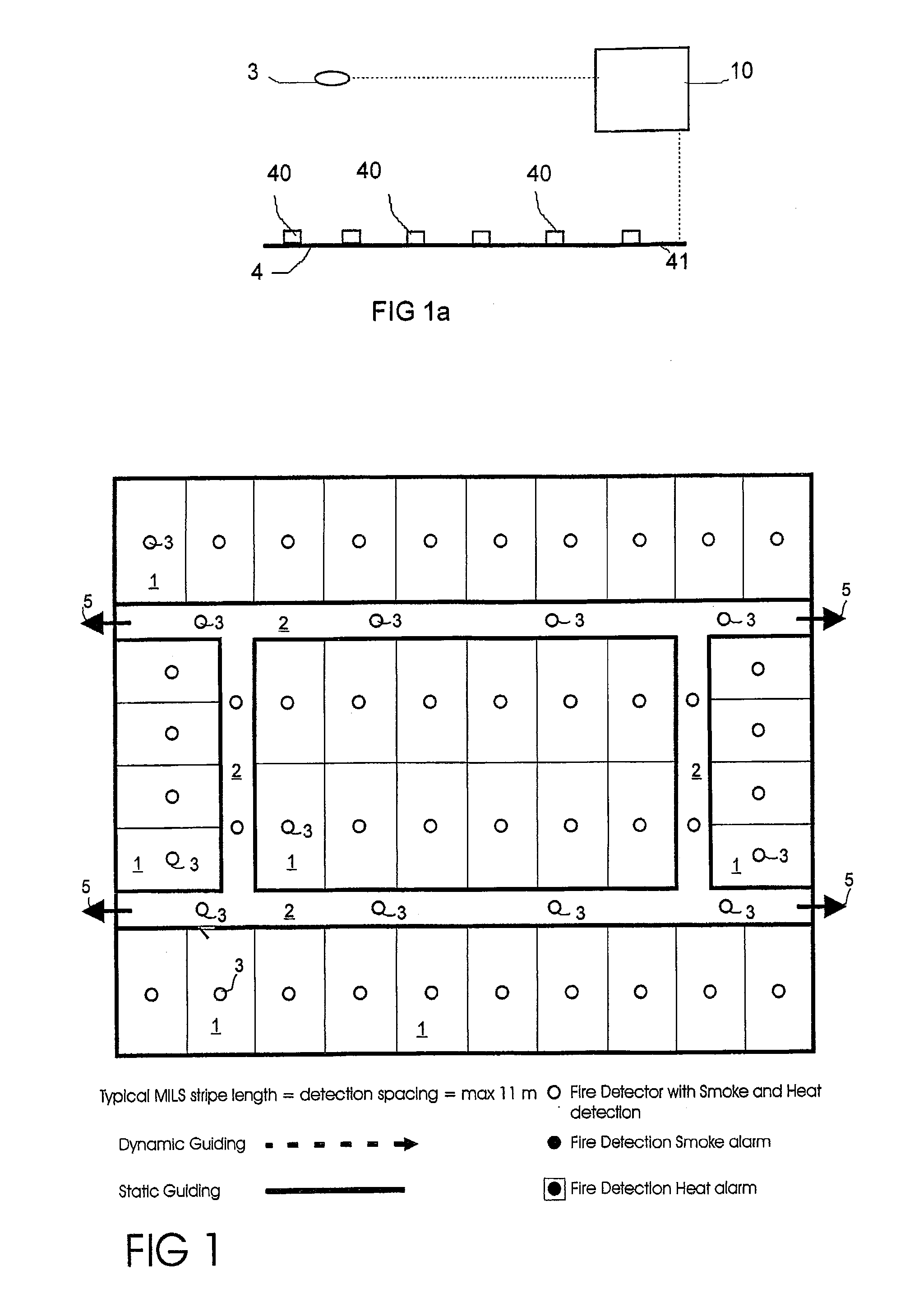

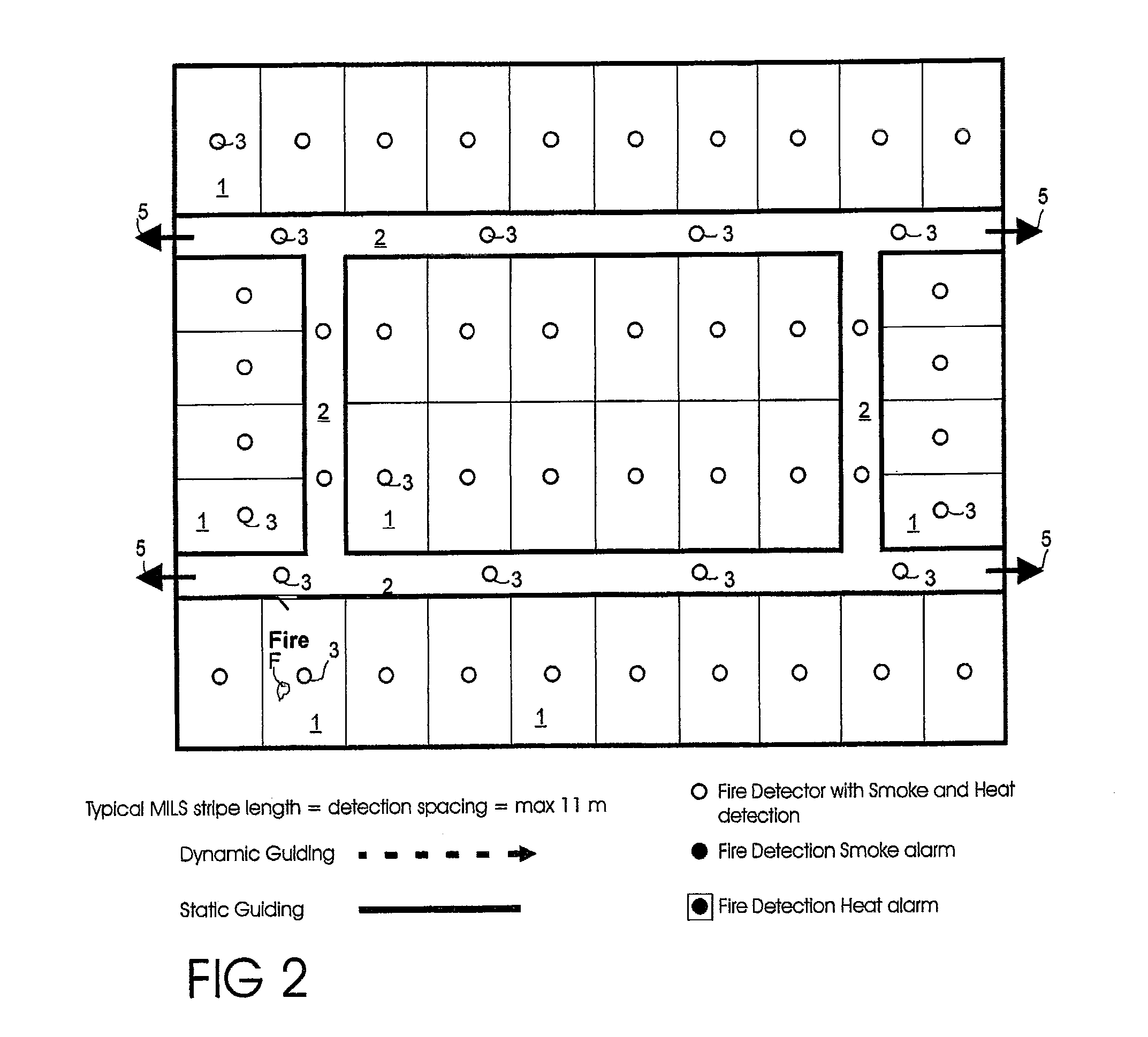

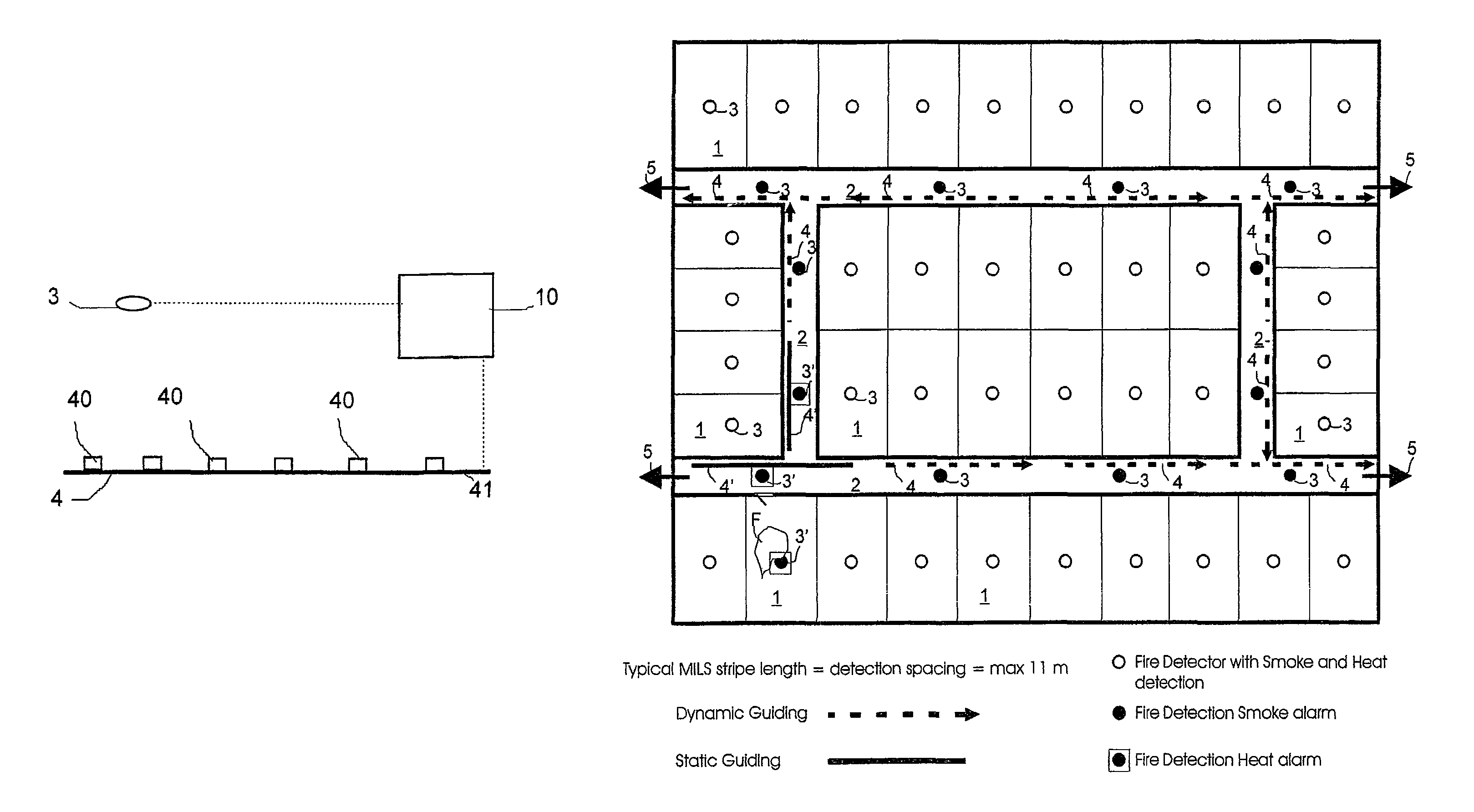

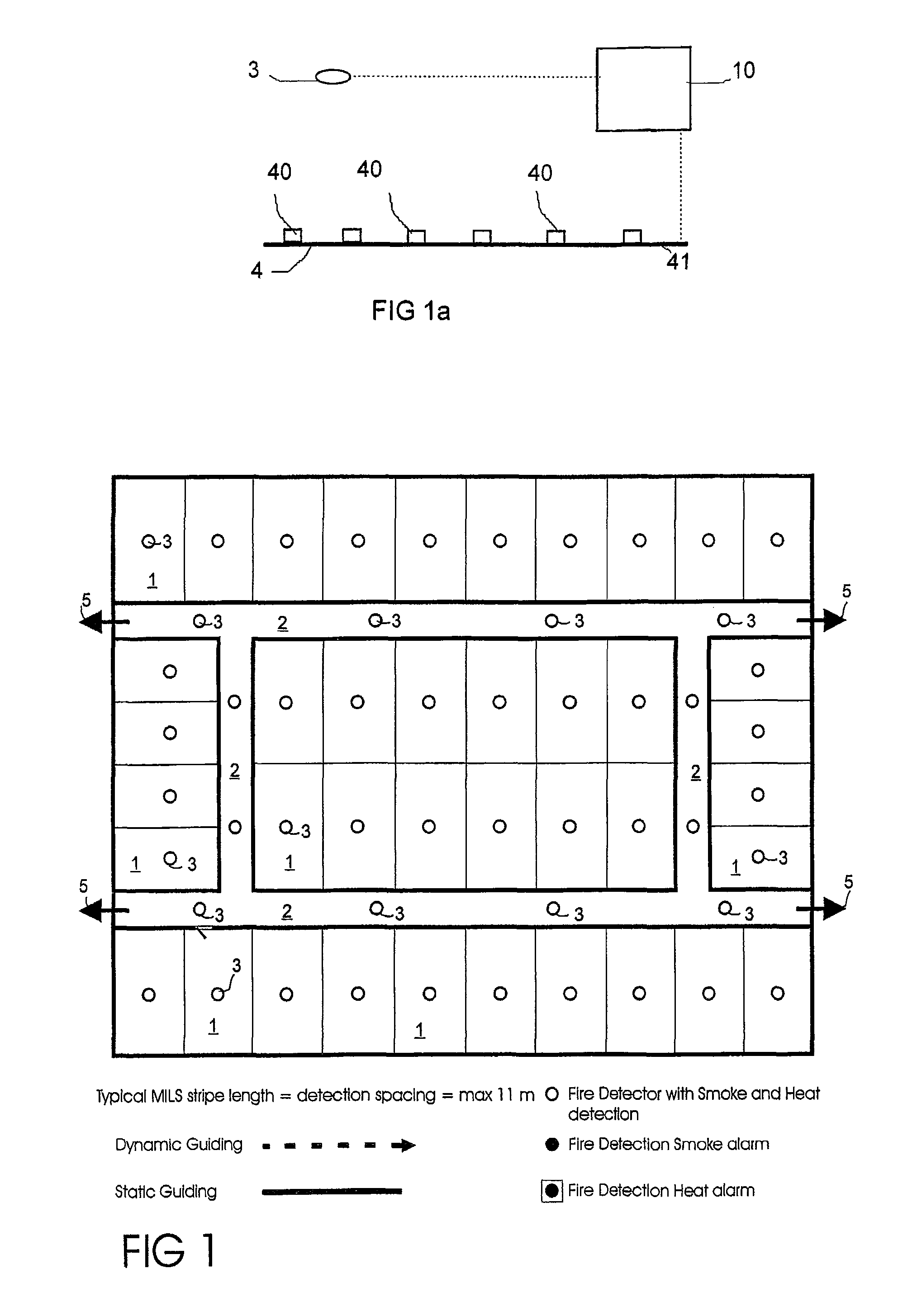

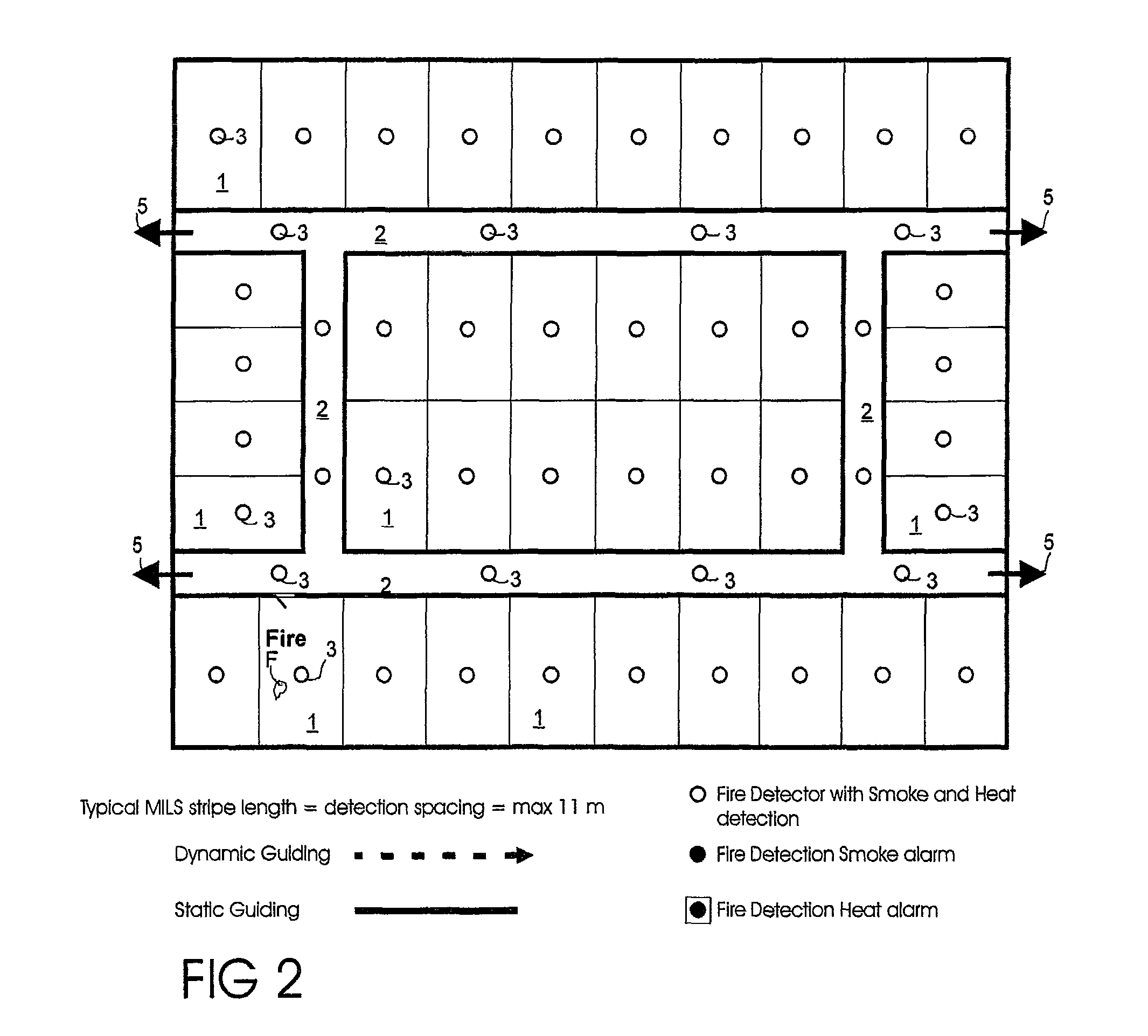

ActiveUS20110089869A1Easy to installGood attention valueElectrical apparatusPedestrian/occupant safety arrangementFire detectorContinuous light

A method for controlling guiding, signal or alert lights, particularly signal lights for an emergency escape route in a fire situation, in which method there are controlled sequentially arranged light sources, such as LED light sources. In the method, in the first step the sequentially arranged light sources (40), which are most advantageously arranged as a light source string (4) or at least as part thereof, are activated, on the basis of a signal received from a fire detector (3), to be switched to a first mode, in which first mode the sequentially arranged light sources are used for indicating the direction of an escape route, and / or to a second mode, where the light sources (40) are switched to emit continuous light. The invention also relates to a system and a device.

Owner:MARMILS OY

Method, system and device for signaling, guiding and alerting

ActiveUS8717162B2Drawbacks of known arrangements can be avoidedAvoid disadvantagesDischarge tube incandescent screensElectric discharge tubesFire detectorContinuous light

A method for controlling guiding, signal or alert lights, particularly signal lights for an emergency escape route in a fire situation, in which method there are controlled sequentially arranged light sources, such as LED light sources. In the method, in the first step the sequentially arranged light sources (40), which are most advantageously arranged as a light source string (4) or at least as part thereof, are activated, on the basis of a signal received from a fire detector (3), to be switched to a first mode, in which first mode the sequentially arranged light sources are used for indicating the direction of an escape route, and / or to a second mode, where the light sources (40) are switched to emit continuous light. The invention also relates to a system and a device.

Owner:MARMILS OY

Adaptive training system, method, and apparatus

ActiveUS10311742B2Effective instructionEffective trainingCosmonautic condition simulationsElectrical appliancesAdaptive learningComputerized system

A system and method for training a student employ a simulation station that displays output to the student and receives input. The computer system has a rules engine operating on it and computer accessible data storage storing (i) learning object data including learning objects configured to provide interaction with the student at the simulation system and (ii) rule data defining a plurality of rules accessed by the rules engine. The rules data includes, for each rule, respective (a) if-portion data defining a condition of data and (b) then-portion data defining an action to be performed at the simulation station. The rules engine causes the computer system to perform the action when the condition of data is present in the data storage. For at least some of the rules, the action comprises output of one of the learning objects so as to interact with the student.

Owner:CAE USA INC

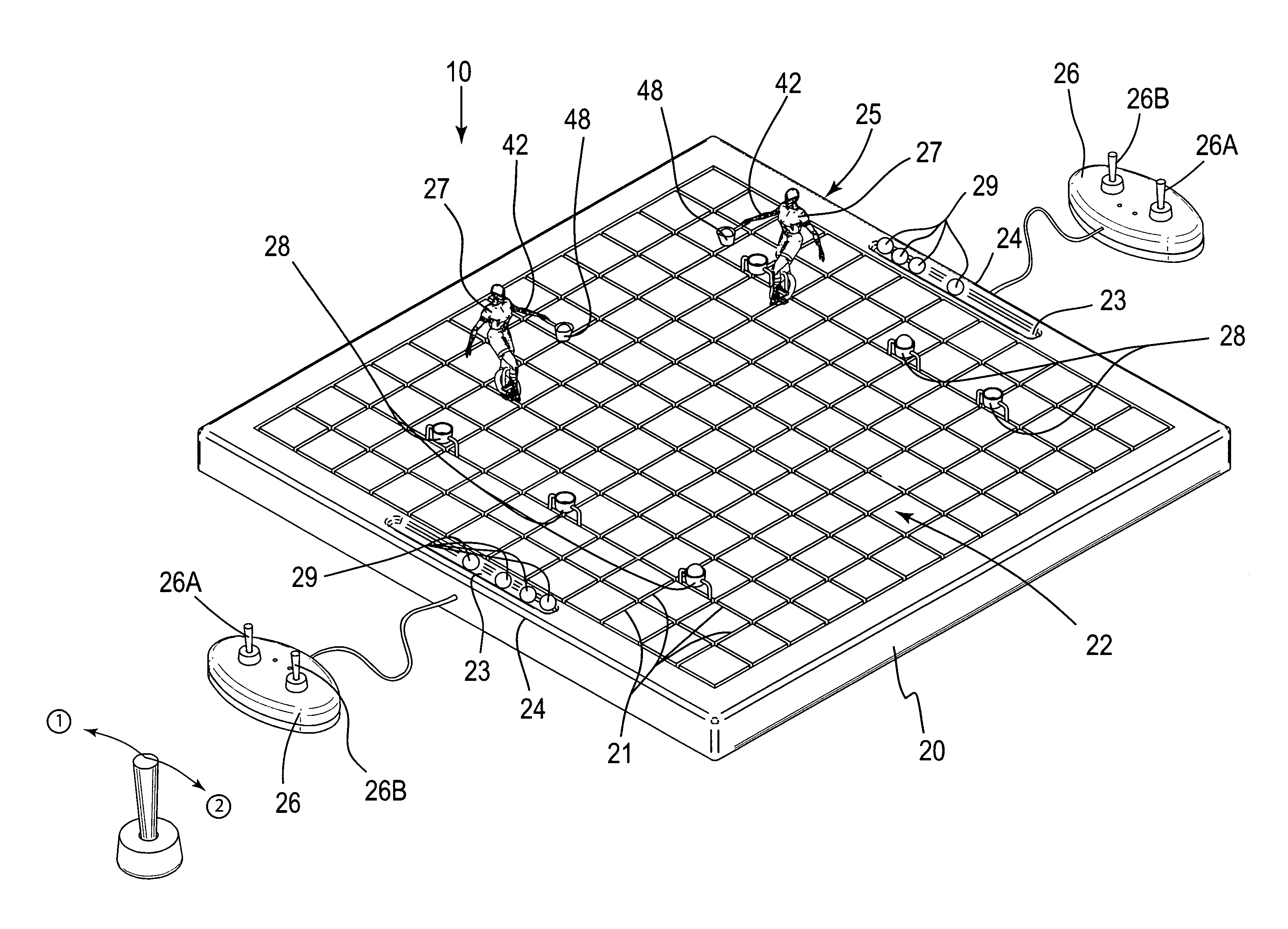

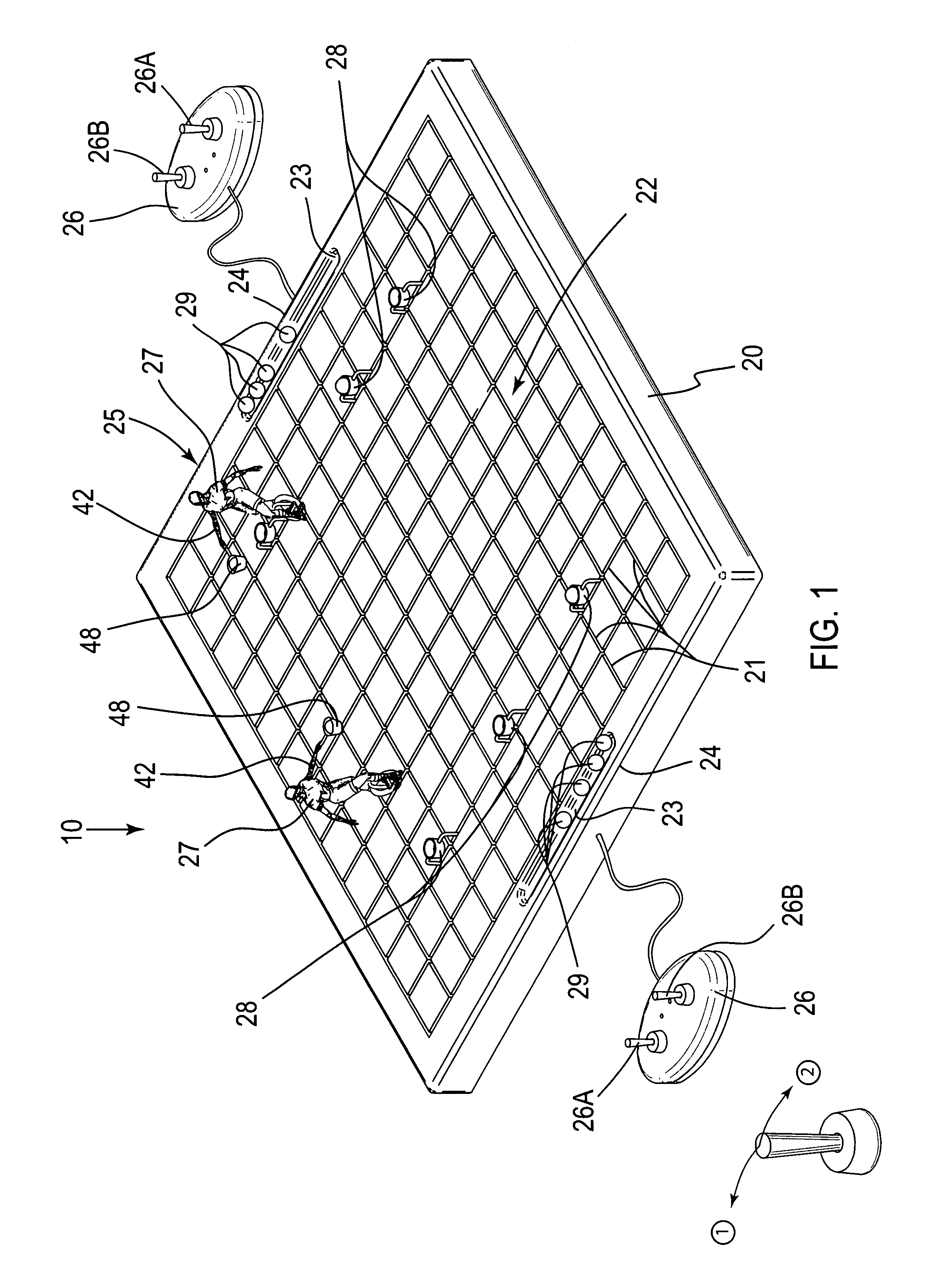

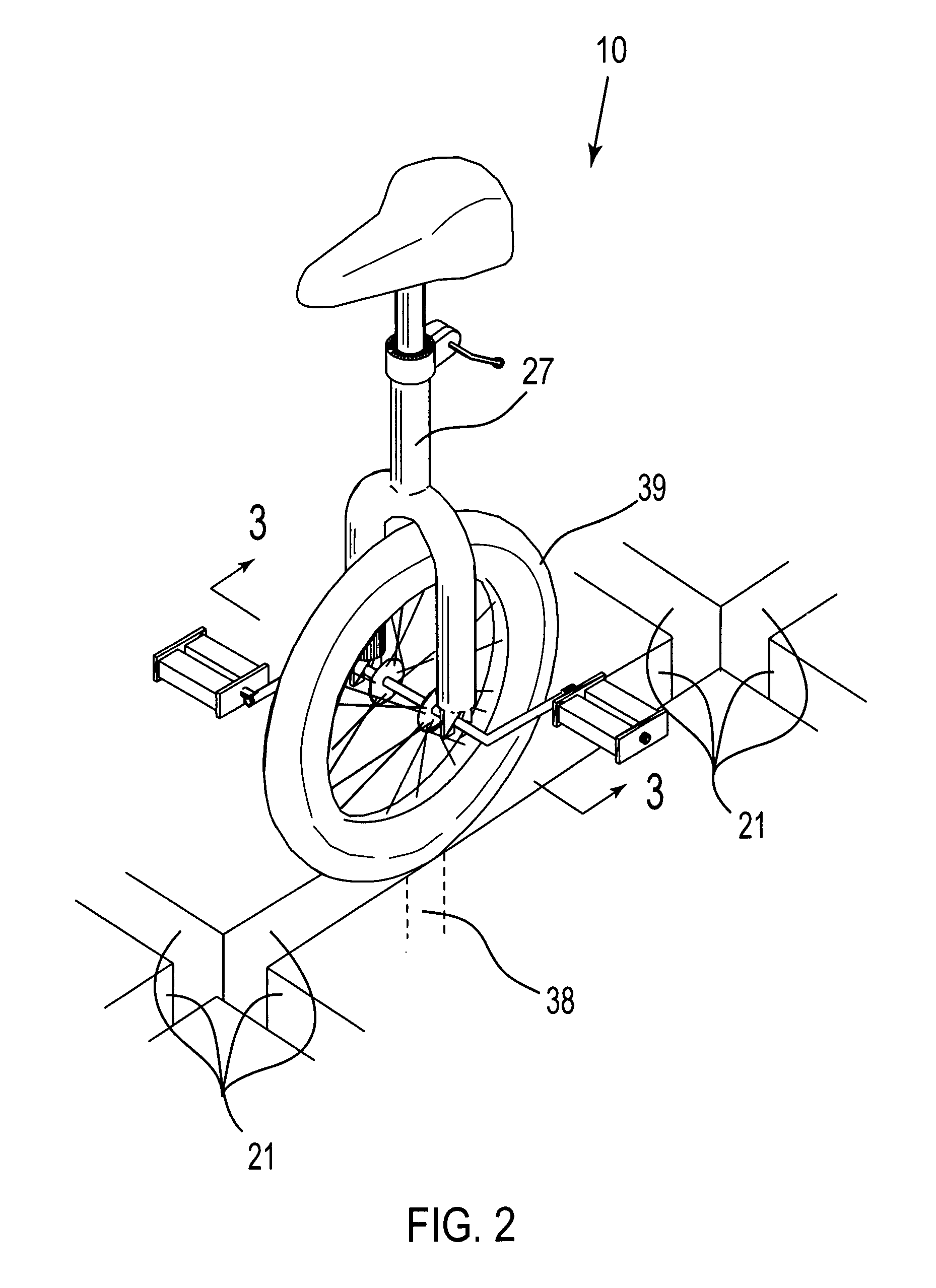

Electronic table top board game

A game board has grooves aligned parallel to X and Y axes that define travel paths along pre-determined directions covering a surface area thereof. Notches are formed along end regions oppositely spaced from each other along an outer periphery of the board. Controllers are coupled to the board, and game pieces are positional along the grooves. Target zones are anchored to the board and spaced along the grooves. Projectiles associated with the game pieces are stored within the notches. A mechanism displaces each of the game pieces along the grooves based upon a user input through an associated controller, and maintains contact with a bottom surface of the grooves. A mechanism rotates one arm of each of the game pieces such that each player tosses one of the projectiles along a travel path terminating at one of the target zones.

Owner:JOLICOEUR PIERRE

Medical image management system and medical image management method

ActiveUS8315688B2Facilitate to pick up stressful eventTreatment safetySurgeryDiagnostic recording/measuringMedical imagingComputer science

Owner:SEVENTH DIMENSION DESIGN

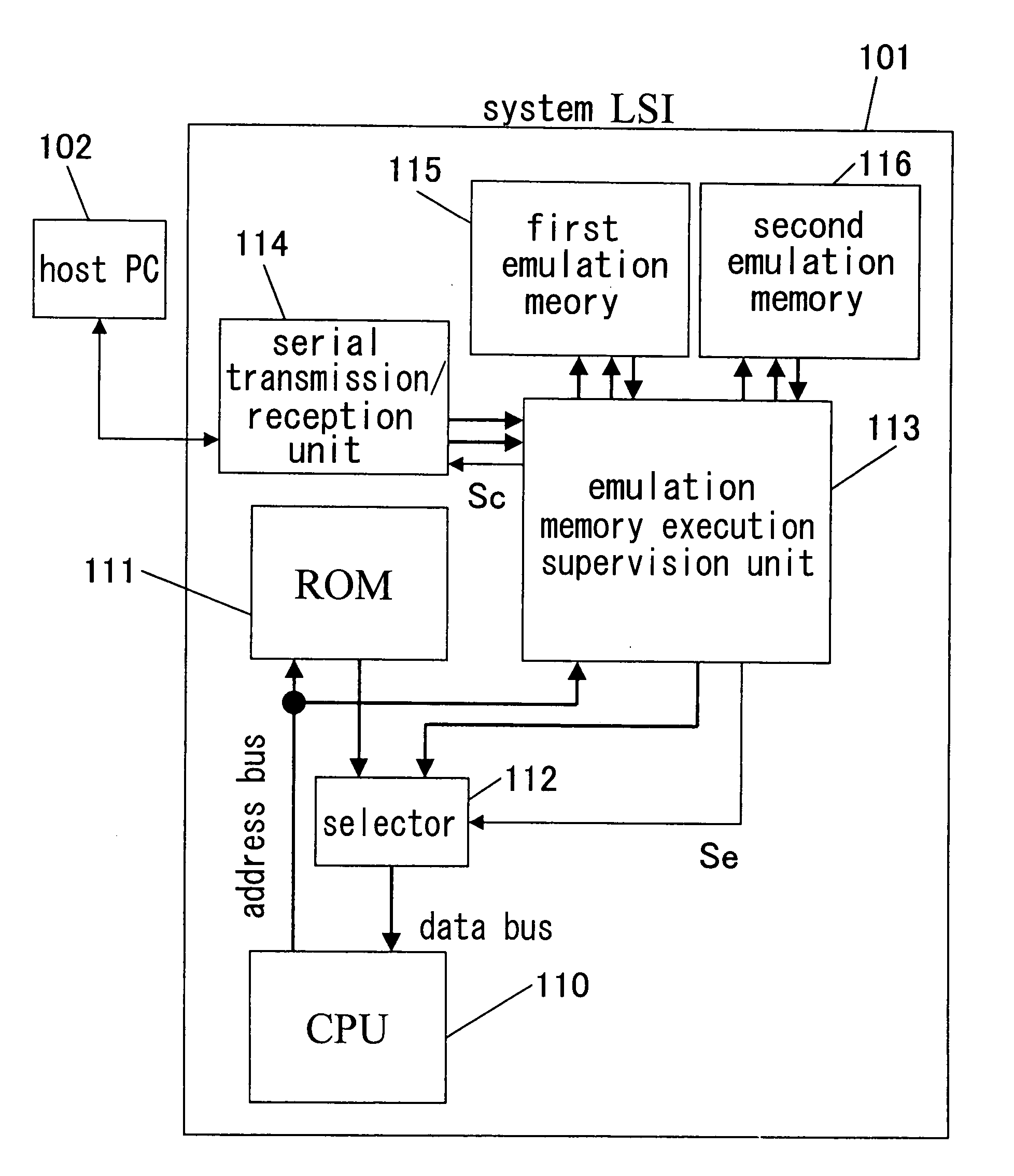

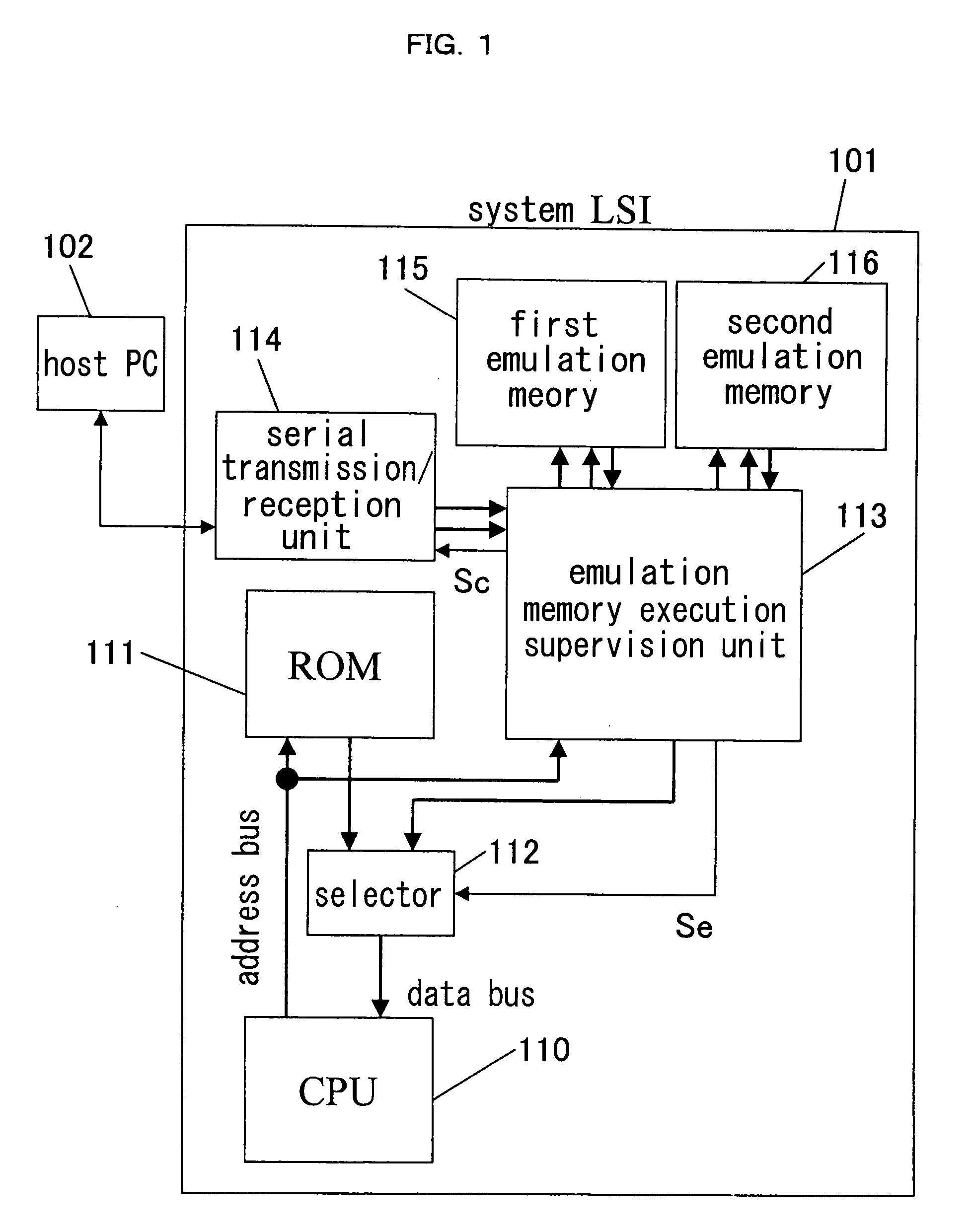

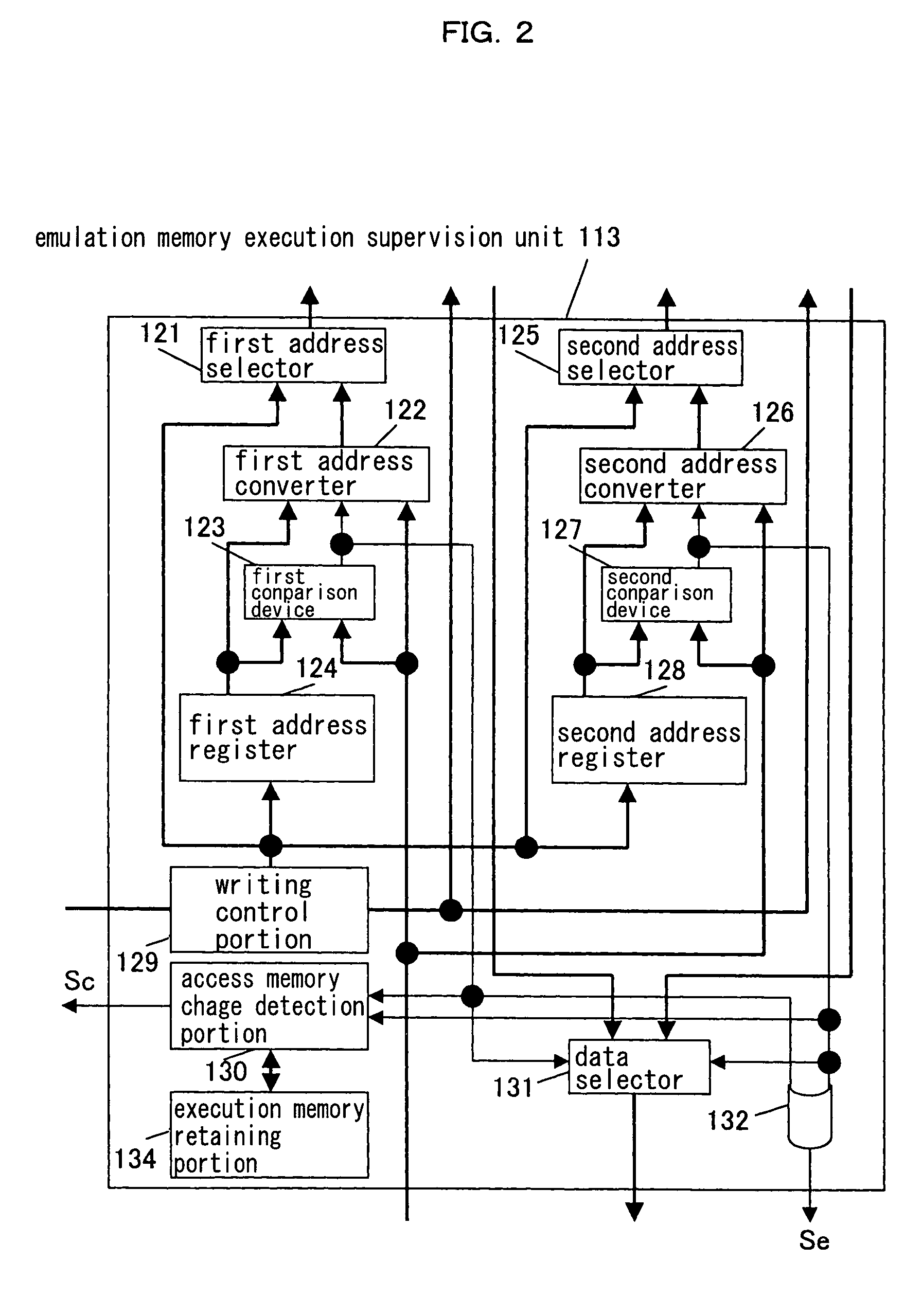

Debugger apparatus and debugging method

InactiveUS20050033542A1Effective instructionTraffic controlResistance/reactance/impedenceSoftware testing/debuggingInstruction sequenceStore instruction

A debugger apparatus according to the present embodiment comprises a host, CPU, a plurality of E-memory units (emulation memory units) for storing instructions, and an execution supervision unit. The host traces the instructions to be stored in the E-memory units and transfers the tracing result in the form of an instruction sequence. The execution supervision unit is connected to the CPU, E-memory units, and host. The execution supervision unit individually writes the instruction sequences transferred from the host in the plurality of E-memory units, reads an instruction sequence from one of the plurality of E-memory units in accordance with an instruction address of the CPU to thereby transfer the instruction sequence to the CPU, and outputs an instruction rewriting order to the host when the instruction address of the CPU is irrelevant.

Owner:PANASONIC CORP

Loop predictor-directed loop buffer

ActiveUS9891923B2Effective instructionAccurate predictionMemory architecture accessing/allocationConcurrent instruction executionParallel computingInstruction buffer

A loop predictor trains a branch instruction to determine a trained loop count of a loop. When the loop fits in an instruction buffer, the processor stops fetching from an instruction cache, sends the loop instructions to an execution engine from the buffer without fetching from the cache, maintains a loop pop count of times the branch is sent to the execution engine from the buffer, and predicts the branch instruction is taken when the loop pop count is less than the trained loop count and otherwise predicts not taken.

Owner:VIA ALLIANCE SEMICON CO LTD

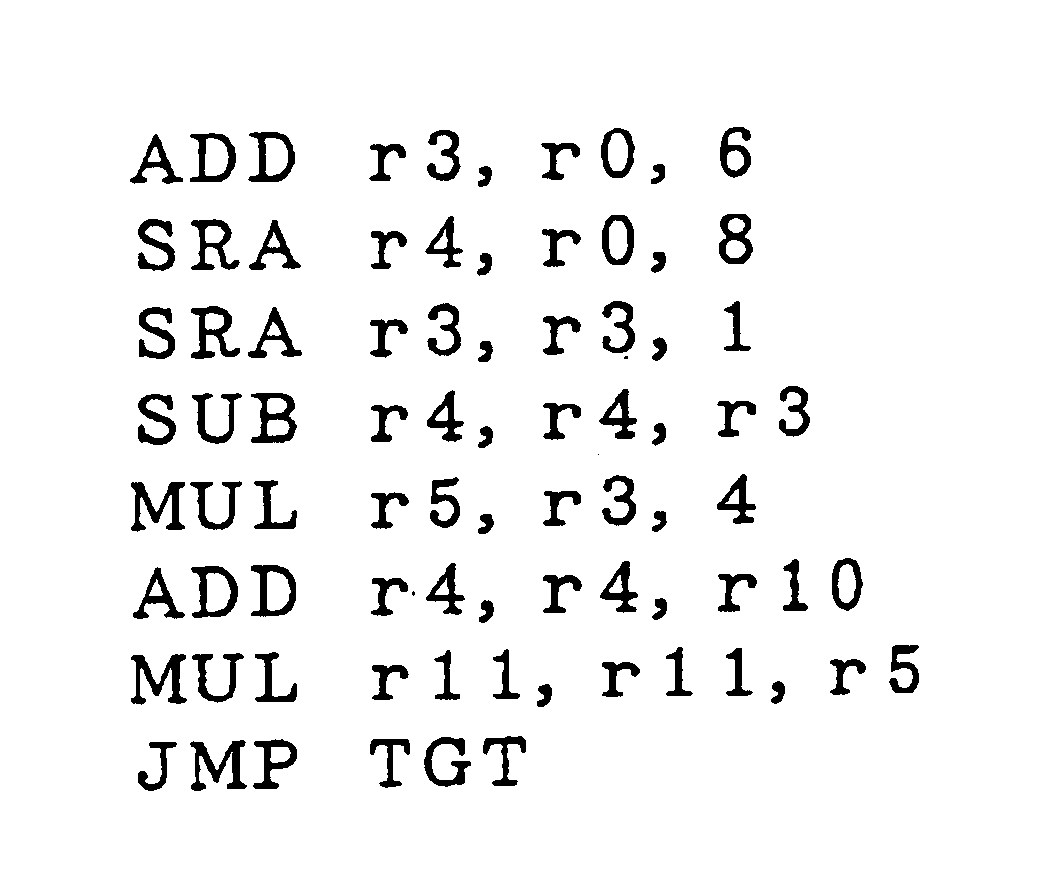

Microprocessor having delayed instructions with variable delay times for executing branch instructions

InactiveUS6851045B2Effective instruction schedulingHigh speedInstruction analysisDigital computer detailsCoincidenceDelayed time

A microprocessor including an instruction decoder for decoding a branch instruction to output a decoded result, a program counter, and a program counter controller for controlling the program counter on the basis of the decoded result. The program counter controller includes a first register for storing a first program counter value output from the instruction decoder. The program counter controller detects a coincidence of the first program counter value stored in the first register with a value of the program counter to set a second program counter value indicating a branch target of the branch instruction into the program counter.

Owner:RENESAS ELECTRONICS CORP

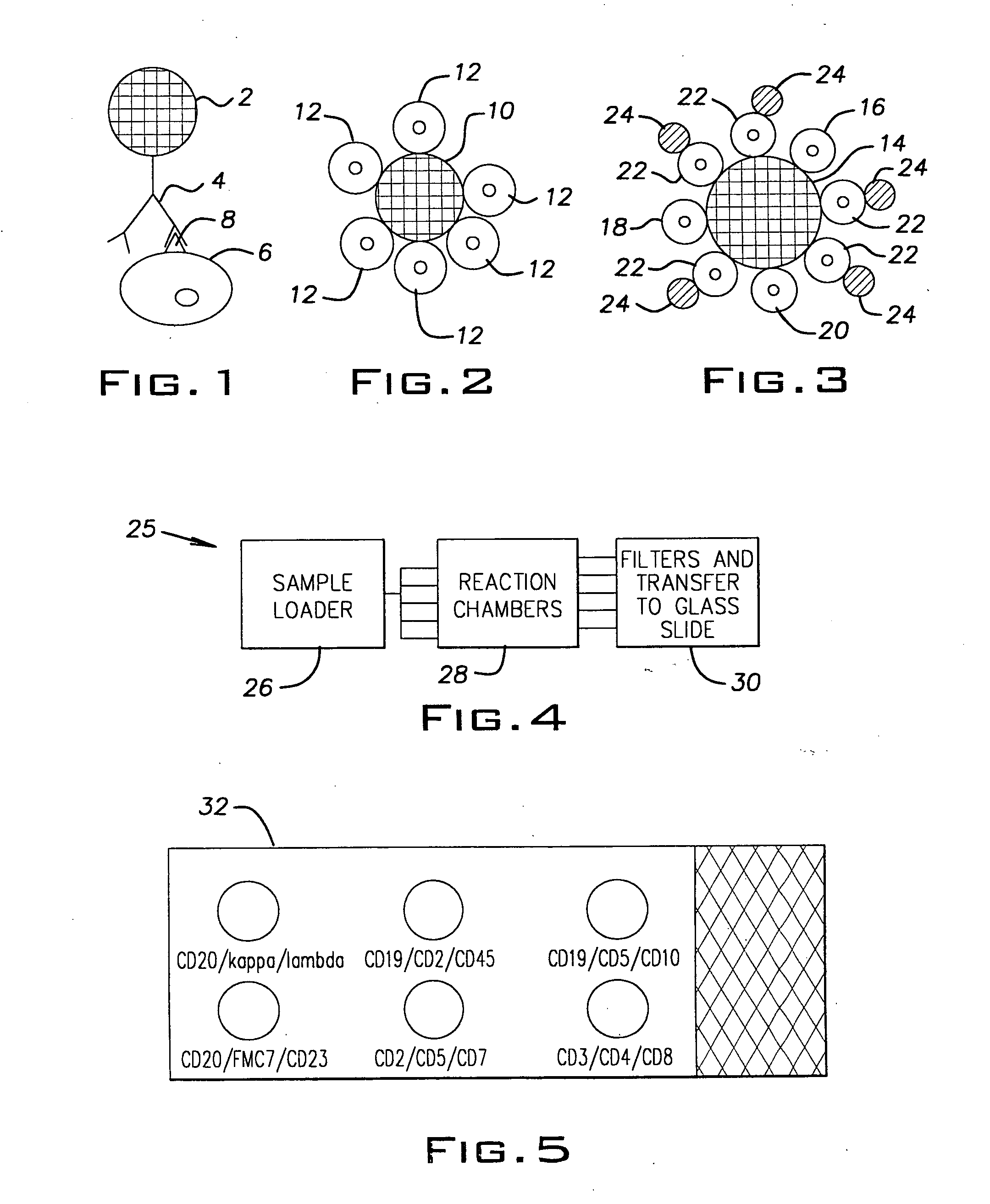

Products and methods for single parameter and multiparameter phenotyping of cells

InactiveUS20050090022A1Effective instructionChemiluminescene/bioluminescenceEnzymologyAntibodyCell complex

A method of single parameter and multiparameter characterizing of cells, particularly immunophenotyping of cells, is provided. The method preferably uses antibody coated microspheres which are adapted to bind to specific types of cells. One or more sets of coated microspheres are added simultaneously or sequentially to a suspension of cells and bind the cells they are adapted to bind. Cells may bind to one or more microspheres. The suspension is then filtered to trap bead-cell complexes. The complexes are preferably stained and then examined to characterize the cells, preferably the cells bound to the microspheres. A kit and apparatus for performing the method are also provided.

Owner:HEMATOTYPES

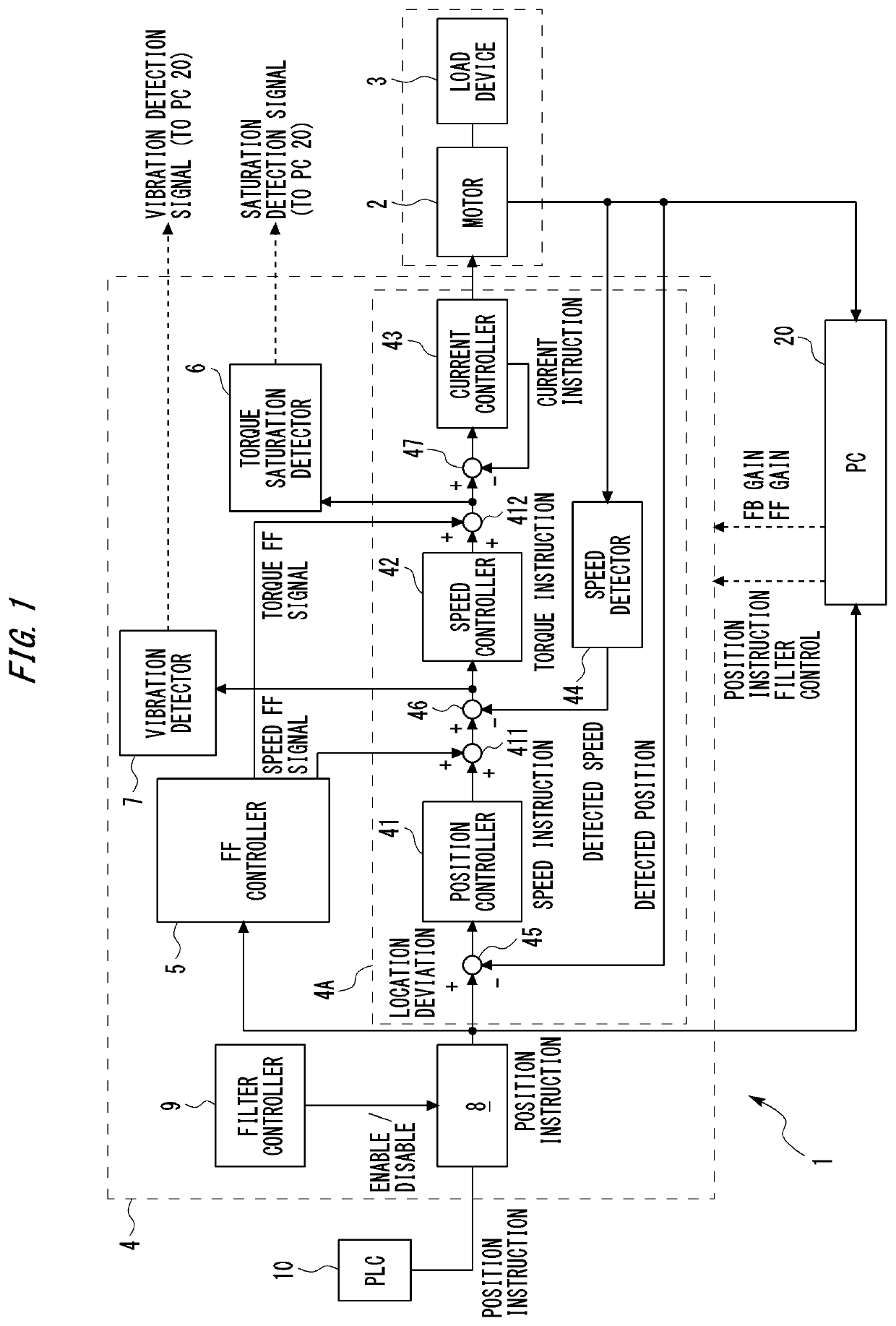

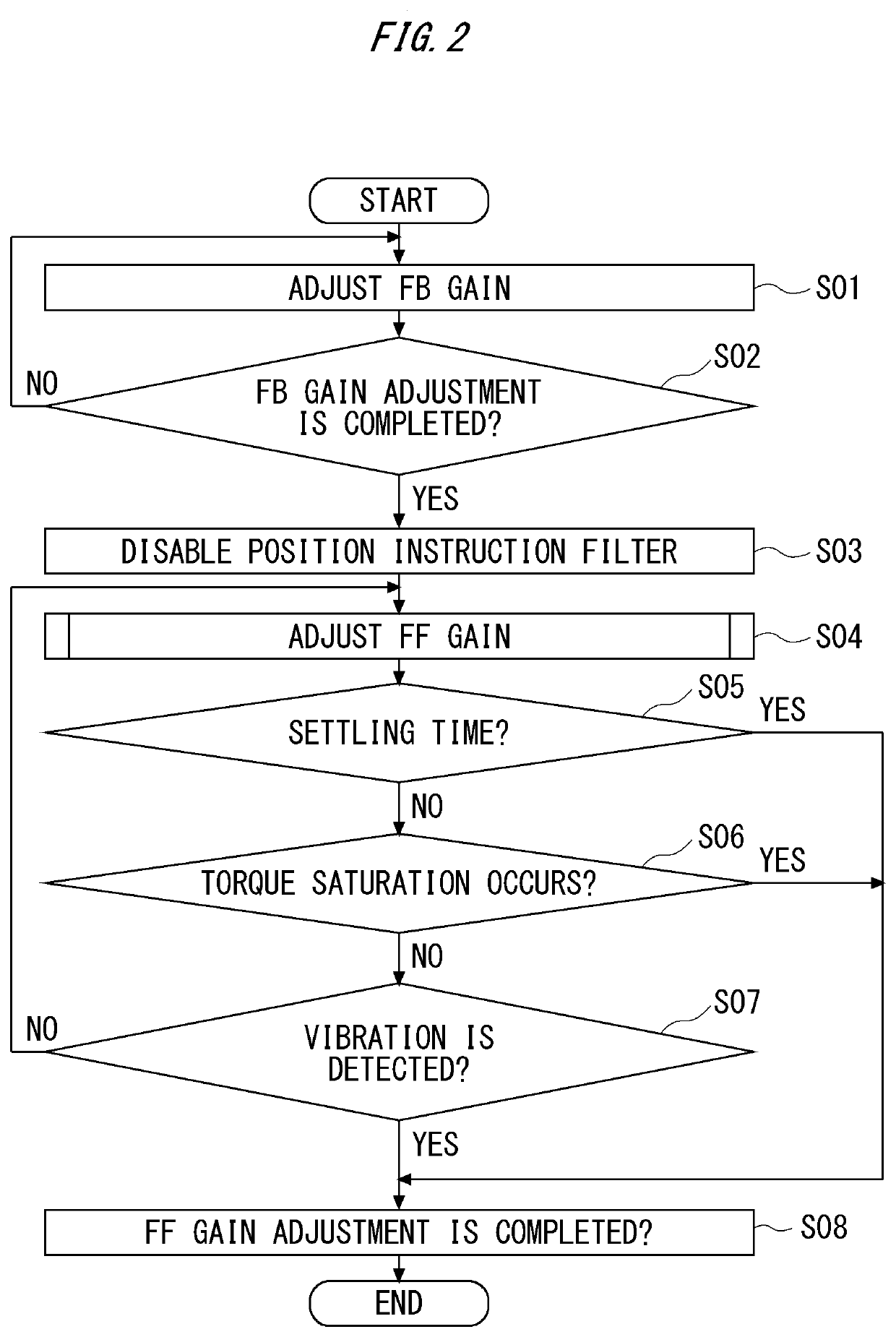

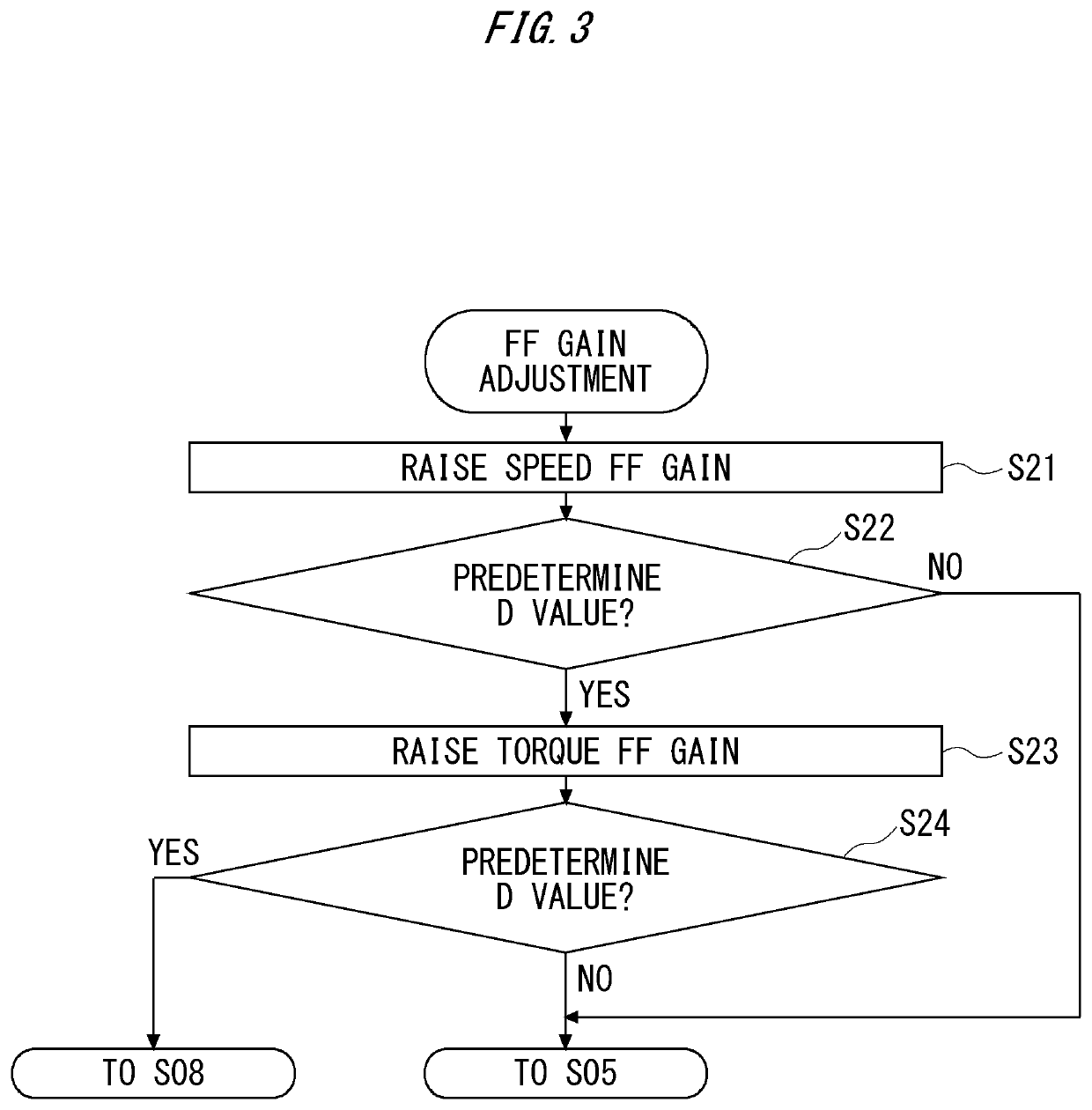

Servo control method

ActiveUS20200264568A1Effective instructionControllers with particular characteristicsSystems engineeringServo control

A servo control method includes a step of adjusting a feedback gain used in feedback control of a controlled object, the feedback control being performed based on difference information between a target value concerning an instruction and a feedback signal from the controlled object, so that the controlled object is operated by following the instruction, and a step of adjusting a feedforward gain used in feedforward control of the controlled object after the adjustment of the feedback gain.

Owner:ORMON CORP