Isomerous CMP (Chip Multi-Processor) static state task scheduling method

A task scheduling and task technology, applied in the direction of program startup/switching, resource allocation, multi-program device, etc., can solve the problem of excessive processor core idle time, untimely processing of redundant tasks, and affecting heterogeneous CMP performance, etc. problem, to achieve the effect of improving resource utilization, reducing communication overhead, and improving task scheduling efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

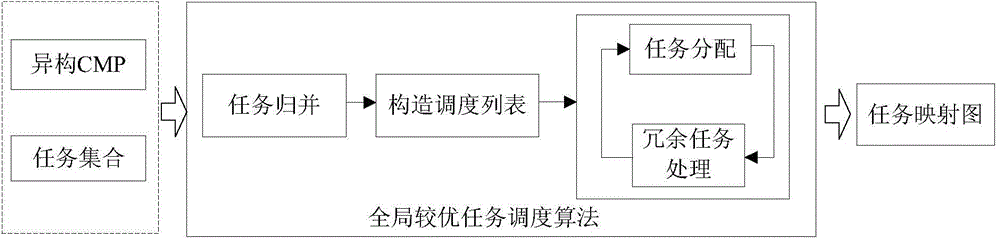

[0045] The static task scheduling method of heterogeneous CMP of the present invention comprises the following steps:

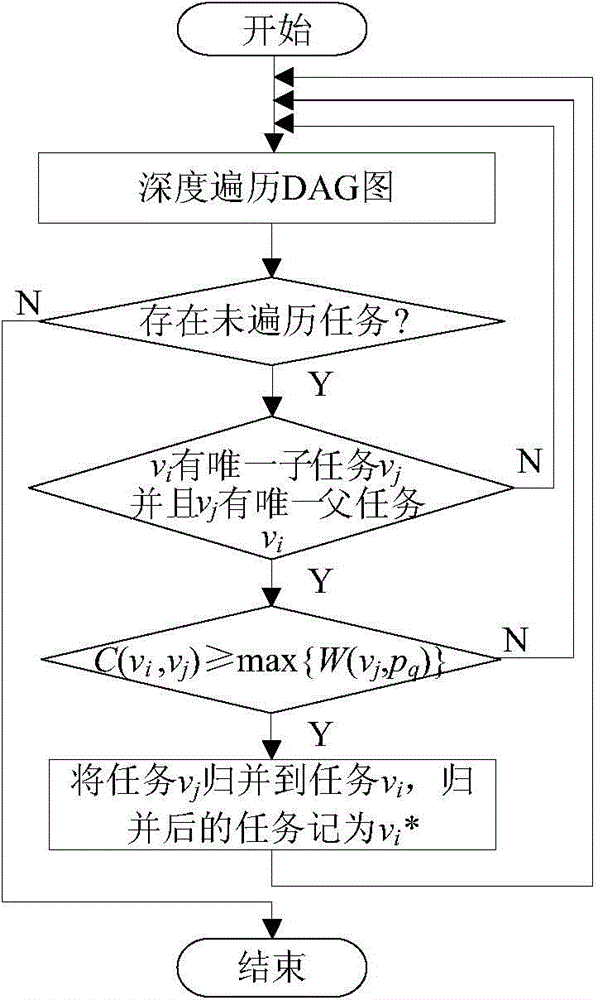

[0046] Step 1: If figure 1 , figure 2 As shown, use the linear clustering method to merge all tasks that meet the task merging conditions in the DAG graph into their parent tasks;

[0047] Depth-first traverses all tasks in the DAG graph, and merges all tasks that meet the merging conditions. By merging tasks whose communication overhead accounts for a large proportion of the total task completion time, the total task completion time is shortened and the task graph is optimized.

[0048] Two conditions must be met at the same time for task merging:

[0049] (1) The current task has a unique parent task and is the only child task of the unique parent task;

[0050] (2) The communication overhead of the current task and its only parent task is greater than or equal to its maximum computing overhead on different processor cores, that is, C(v i ,v j )≥max{...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More