A chip-to-chip interconnection device based on fpga

A chip-to-chip technology, which is applied in the field of FPGA-based chip-to-chip interconnection devices, can solve problems that do not involve LVDS interfaces, and achieve the effect of adjustable speed and high flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

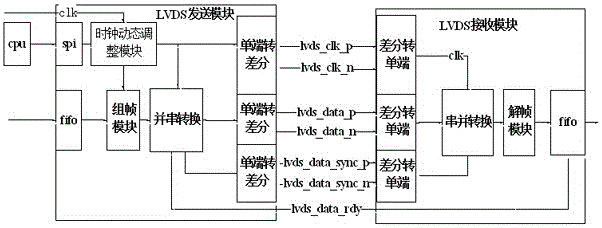

[0028] As attached figure 1 As shown, an FPGA-based inter-chip interconnection device is provided with a clock dynamic adjustment module, an LVDS sending module, and an LVDS receiving module in the FPGA chip.

[0029] Clock dynamic adjustment module:

[0030] In order to realize the dynamic reconfiguration of the rate, the scheme of dynamically reconfigurable clock is adopted, and the reconfigured clock parameters are sent to the clock dynamic adjustment module in the FPGA in real time through the spi or iic interface connected to the CPU and the FPGA. The clock output by the adjustment module is the clock of the entire device.

[0031] LVDS sending module:

[0032] The opposite end chip will send a data ready signal. When the opposite end module is ready to receive data, fifo will read the data in fifo every data bit width cycle. The read data will go through the framing module and follow the packet header. , Data length, valid data and data checksum protocol format framing at the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More