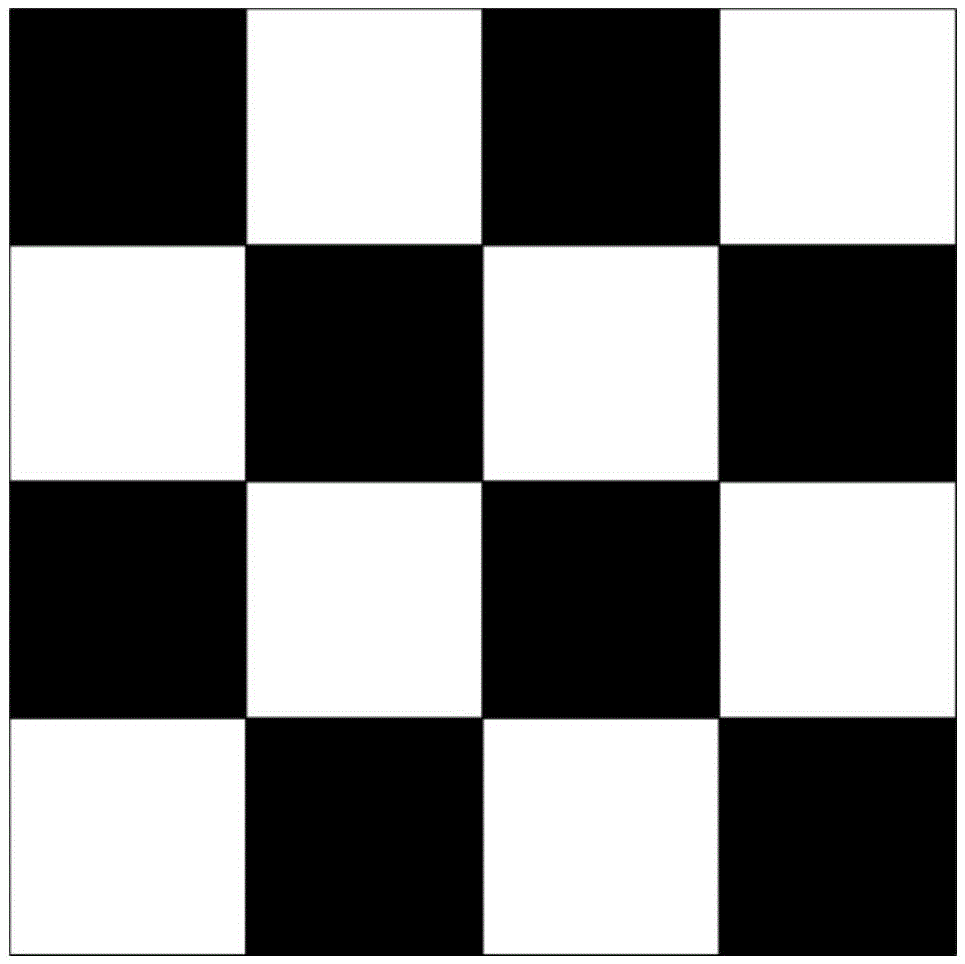

Generation Method of Arbitrary Level Checkerboard Screen Components Based on FPGA

A chessboard, picture technology, applied in instruments, static indicators, etc., can solve the problems of high hardware requirements of signal generators, insufficient detection of liquid crystal displays, large amount of bmp image data, etc., to reduce cache capacity and improve speed. , the effect of fast response

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

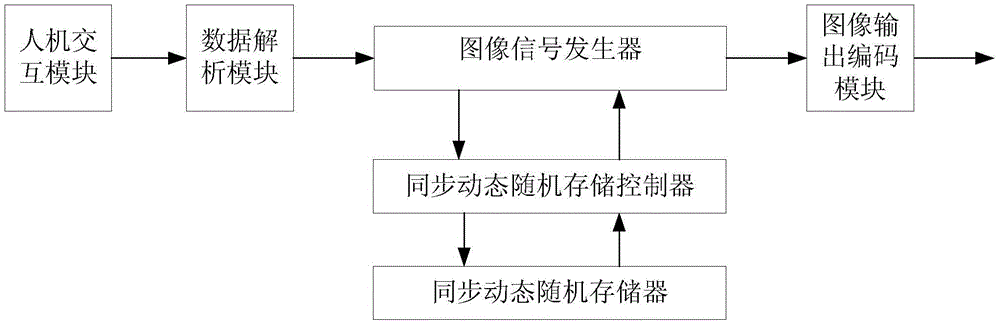

[0014] A method for generating an arbitrary order checkerboard picture component based on FPGA, comprising the steps of:

[0015] Step 1: According to the position information of the checkerboard picture to be constructed, the control data analysis module sends the horizontal coordinate information and vertical coordinate information of the upper left vertex of the checkerboard picture to the image signal generator, and the horizontal coordinate information and vertical coordinate information of the lower right vertex (the checkerboard picture can be positioned like this); Simultaneously, according to the color information control data analysis module of the checkerboard picture that needs to build, send the first color value of the checkerboard and the second color value of the checkerboard to the image signal generator; Simultaneously, accordin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More