Linear analog circuit fault diagnosis method

A technology for simulating circuit faults and diagnosis methods, which is applied in the directions of analog circuit testing, electronic circuit testing, and electrical digital data processing, etc. It can solve problems such as the influence of tolerance fault diagnosis, incompetence, and difficult solution of equations, etc., to achieve accurate fault diagnosis results , the calculation process is simple, and the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

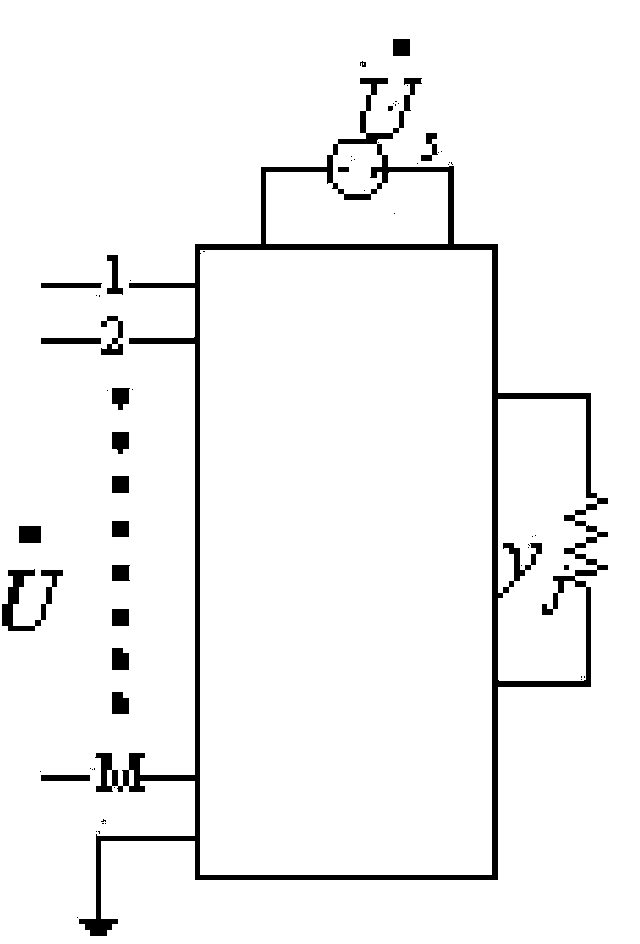

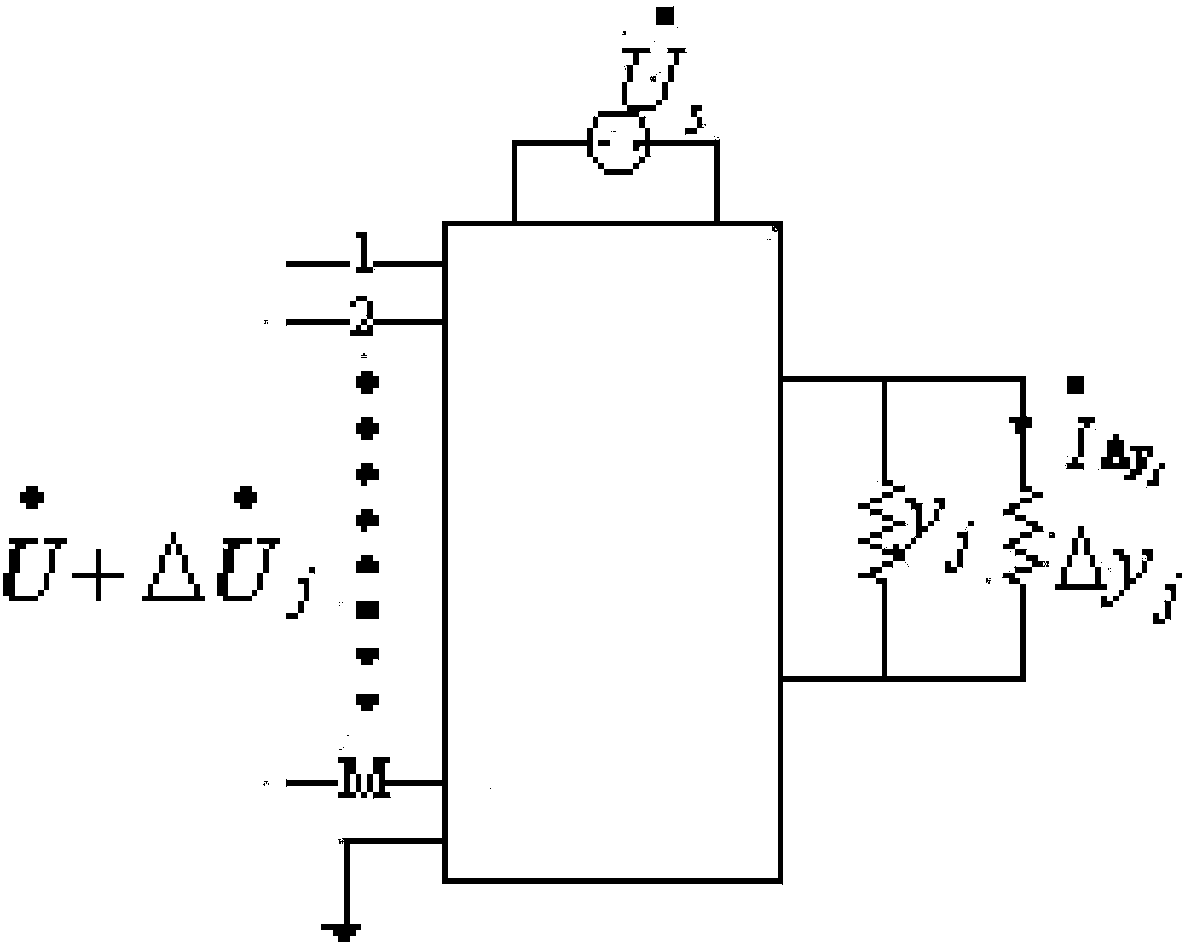

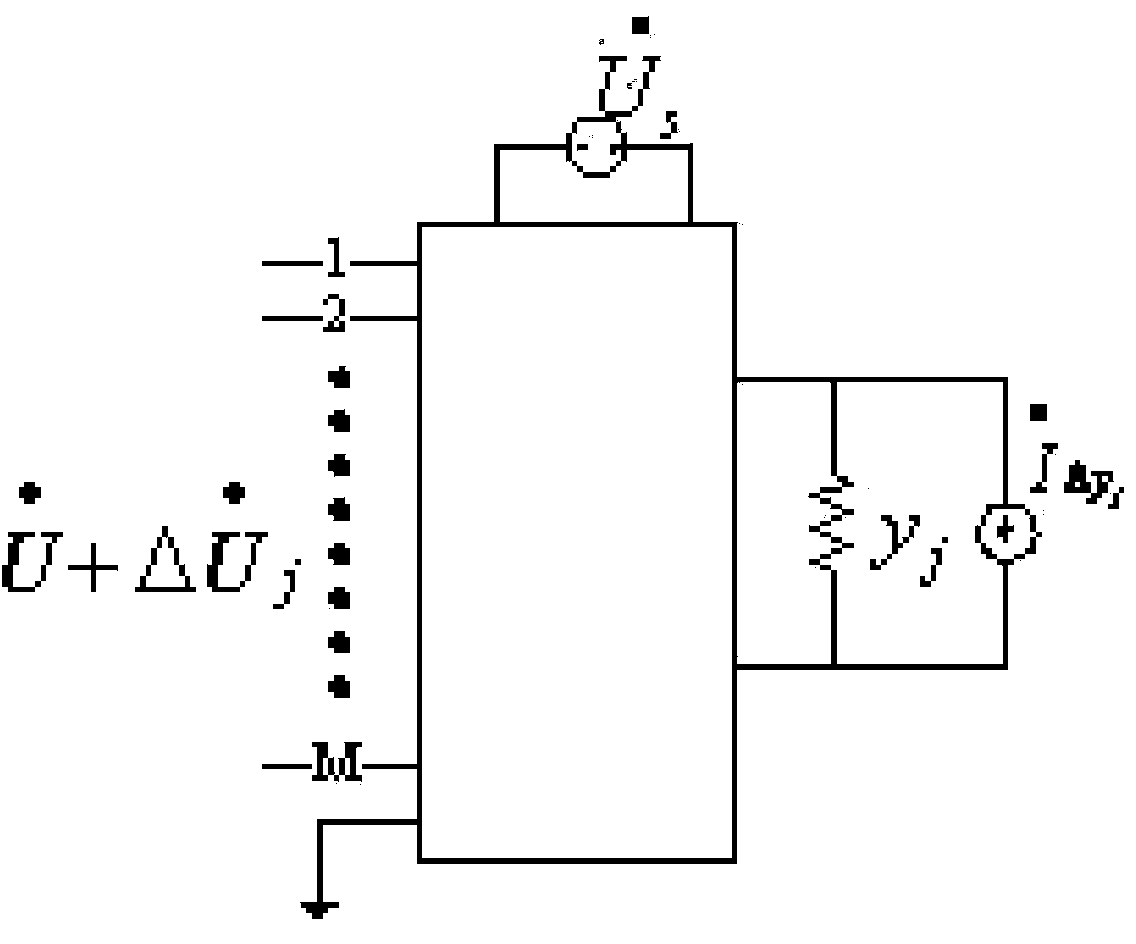

[0084] In order to illustrate the actual working process of the present invention, a second-order Thomas circuit is selected for experimental verification. The tolerance and measurement error of the experiment are defined as: resistance tolerance range a R =±5%, capacitance tolerance range a C =±10%, measurement error range e=±5%. Figure 7 is a second-order Thomas circuit diagram. Such as Figure 7 As shown, in this embodiment, the output terminals of each operational amplifier are used as measuring points, which are respectively marked as n1, n2 and n3 from left to right. fault modeling stage, the resistor R j The parameters are adjusted to 2R j , capacitive element C j adjusted to 2C j . The excitation signal is a 1kHz, 1V sinusoidal signal. Table 1 shows the simulated voltages obtained under various fault conditions in this embodiment. In this embodiment, the unit of voltage is V.

[0085]

[0086] Table 1

[0087] Table 2 is the calculated voltage phasor in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com