On-chip network congestion control method based on dynamic routing table

A network-on-chip, congestion control technology, applied in data exchange networks, digital transmission systems, electrical components, etc., can solve the problems of no dynamic routing table, increased data processing capacity of routing nodes, frequent interactive reading and writing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0083] The present invention will be described in further detail below in conjunction with the accompanying drawings.

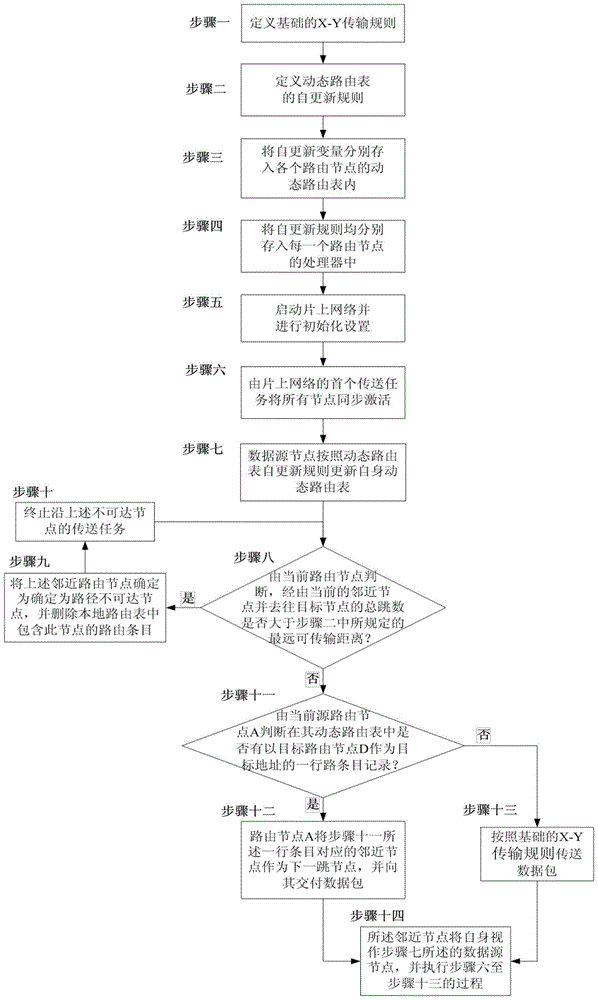

[0084] like Figure 1 to Figure 5 Shown, the present invention is based on the on-chip network congestion control method of dynamic routing table, comprises the steps:

[0085] Step 1: Define the basic X-Y transmission rules:

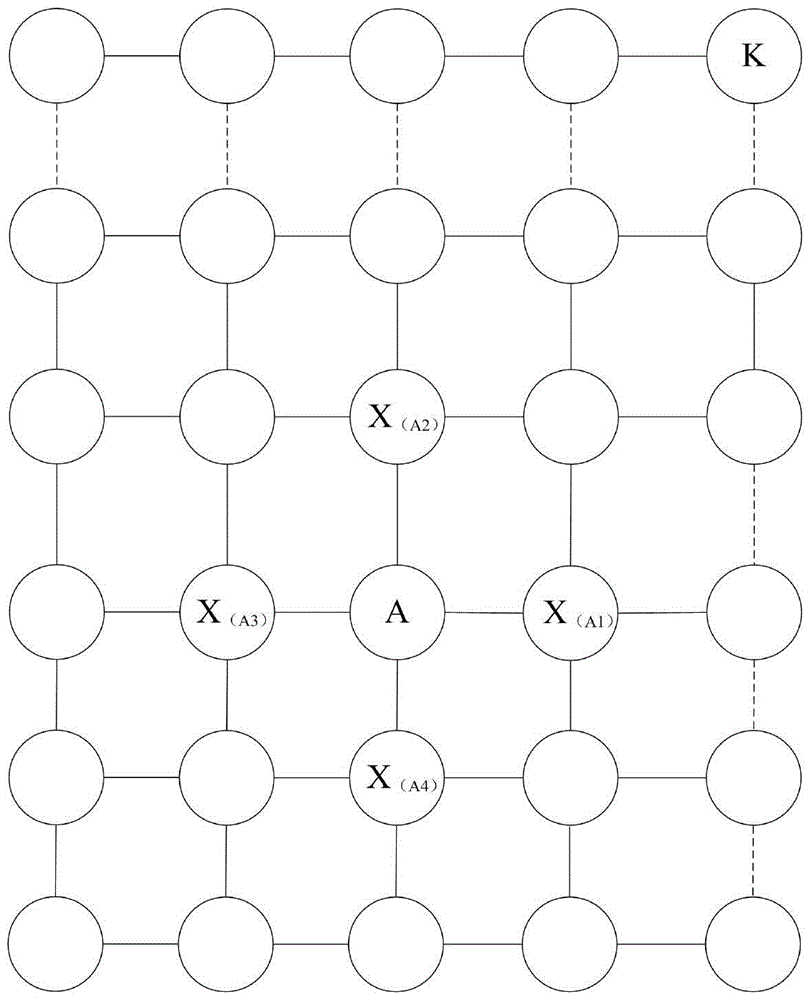

[0086] On the on-chip network of 2D mesh topology, each routing node on the rectangular array column composed of m×n routing nodes has its own unique coordinates. Let the coordinate value (x, y) of any routing node A, and The coordinate value (p,q) of an arbitrary routing node K, when starting from node A(x,y) and going to node K(p,q), it follows the following basic rules:

[0087] When the abscissa and ordinate of nodes A(x, y) and K(p, q) are different, A(x, y) always ignores the difference on the ordinate, and prefers to make the abscissa difference The adjacent node on the horizontal axis whose absolute value shrinks is used as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More