A method for adjusting the hierarchical structure of small cells in integrated circuit layout verification

A graphic structure adjustment and hierarchical structure technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem that the layout hierarchical structure affects verification efficiency, etc., to maintain data structure and integrity, and improve hierarchical processing efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

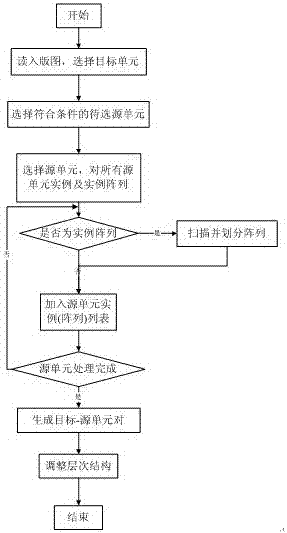

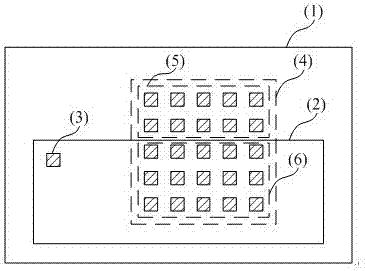

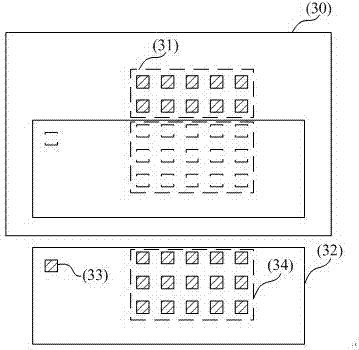

[0011] The processing flow of this method is as follows figure 1 shown. Introduce the concrete implementation of this method below in conjunction with example, as figure 2 Shown is an example layout where the cell top( figure 2 (1)) is the top-level unit, including subunit a( figure 2 (2)), subunit b( figure 2 (3)). Among them, subunit b is a qualified small unit, subunit a is not a small unit and subunit a is the only instance in the layout. The hierarchical relationship of the layout after the hierarchical adjustment method is as follows: image 3 shown. The following combination figure 2 The example shown describes the specific steps of the method:

[0012] Step 1: first traverse the layout hierarchical units, and select subunit a as a candidate target unit. Record the border information of a (for example, by means of two-dimensional buckets). Secondly, according to the area of the cell border, it is determined that the subunit b is a small unit, which meet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More