Address mapping algorithm for transposed matrix based on single-port SRAM

A technology of address mapping and transposing matrix, applied in digital video signal modification, electrical components, image communication, etc., can solve the problems of low throughput, high power consumption, high hardware overhead, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

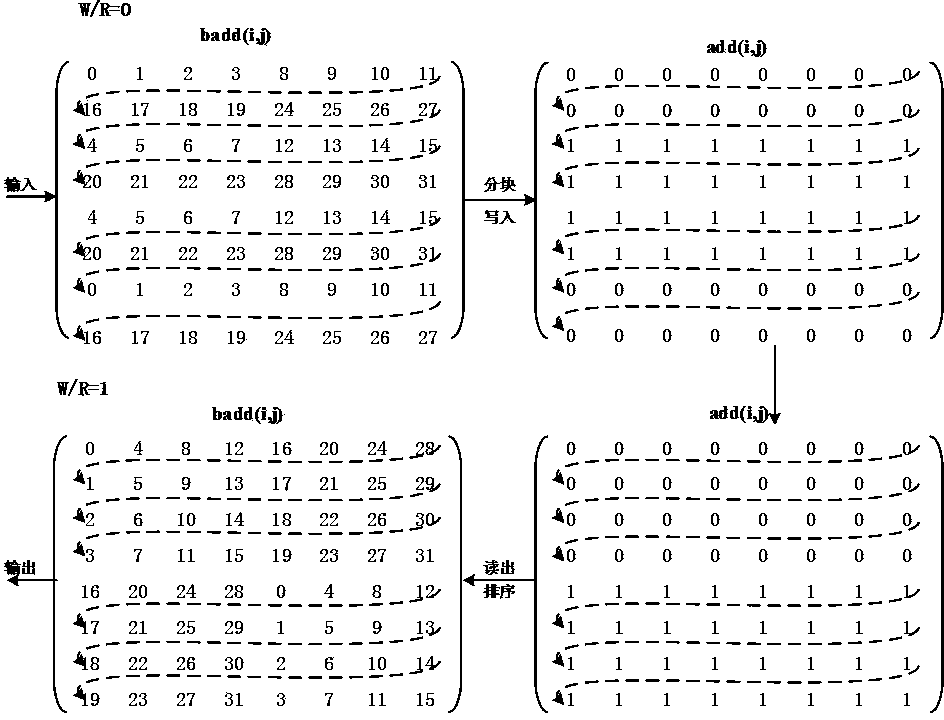

[0047] The method of the present invention will be further specifically described below by taking an 8x8 input matrix as an example through examples and in conjunction with the accompanying drawings.

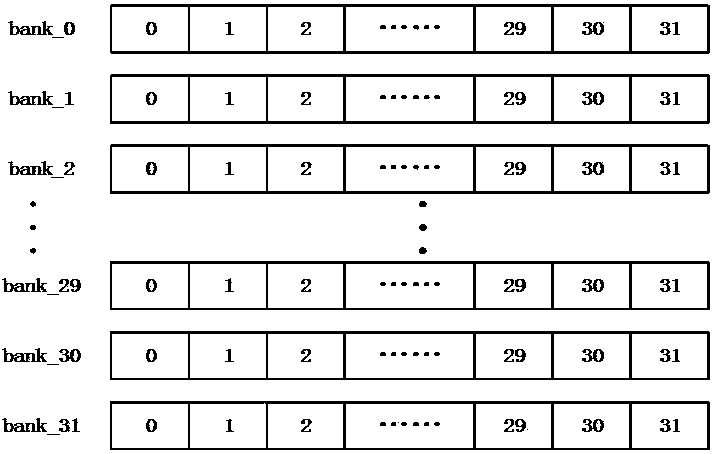

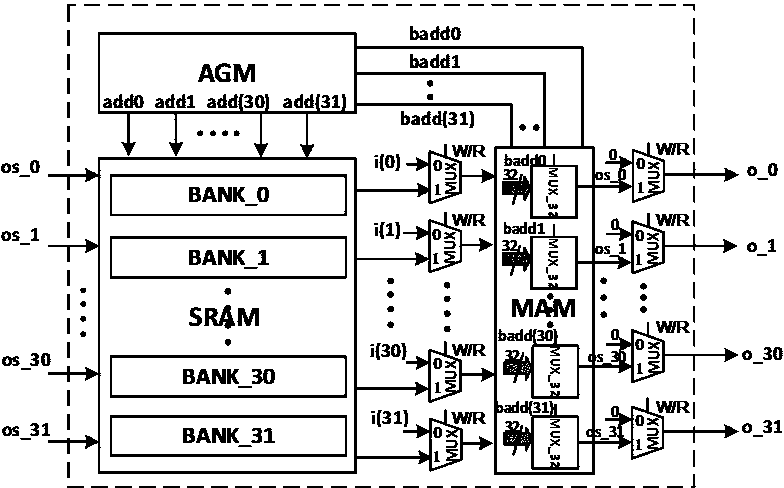

[0048] For an 8x8 input matrix, 4 rows are input each time, and the input is divided into two times. The corresponding address mapping add(i) and badd(i) is as follows Figure 1 As shown, W / R=0 during the write operation, the input data passes through the MAM module, MAM sorts the input data according to badd(i) to specify the Bank where the input data is written, and then the data is written into the i-th bank through add(i) The specified byte of the Bank; after the input data storage is completed, start the read operation W / R=1, read the column data from the SRAM according to add(i), and then sort and output the read column data according to badd(i), Four columns of data are output each time, and the output is divided into two times.

[0049] The present invention adopts an add...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More