High-speed comparator direct-current offset digital auxiliary self-calibration system and control method

A high-speed comparator and DC offset technology, applied in the direction of analog/digital conversion calibration/testing, can solve problems such as insufficient bandwidth and weak driving ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

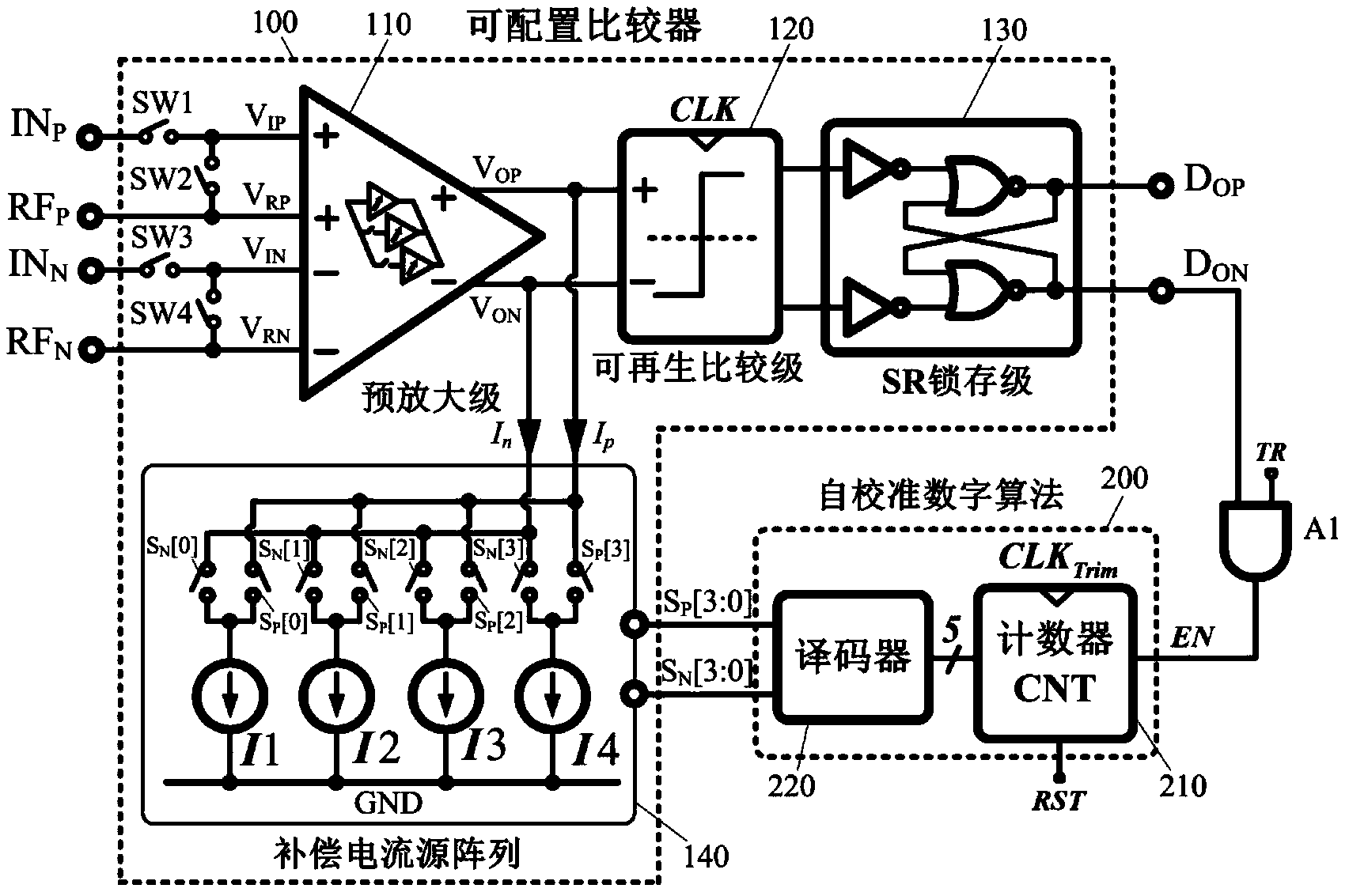

[0041] A high-speed comparator DC offset digitally assisted self-calibration system, such as figure 1 As shown, and the control method, it is composed of a configurable comparator module 100, a self-calibration module 200 and a timing signal generation circuit. The negative digital output D of the configurable comparator module 100 ON The output signal EN after passing through the AND gate A1 is used as the input signal of the self-calibration module 200, and the present invention uses S P [X:0], S N The [X:0] symbol represents a digital signal, where "X" represents the number of signal bits, "0" is 0, and S P [X:0], S N [X:0] means S P , S N The Xth bits of are all 0. The 4-bit output data S generated by the self-calibration module 200 P [3:0], S N [3:0] controls the compensating module in the configurable comparator module 100 , and then calibrates the DC offset voltage of the comparator until it is within the adjustable precision range.

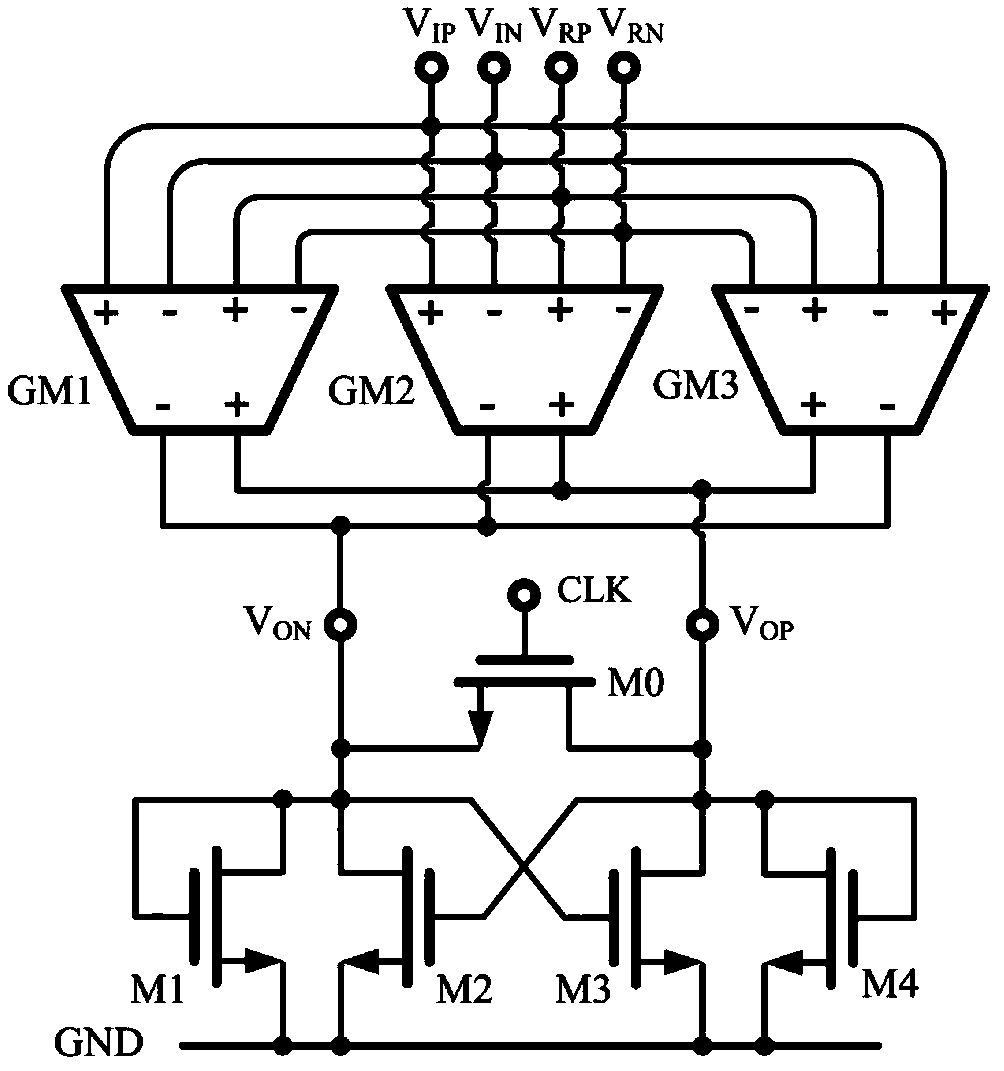

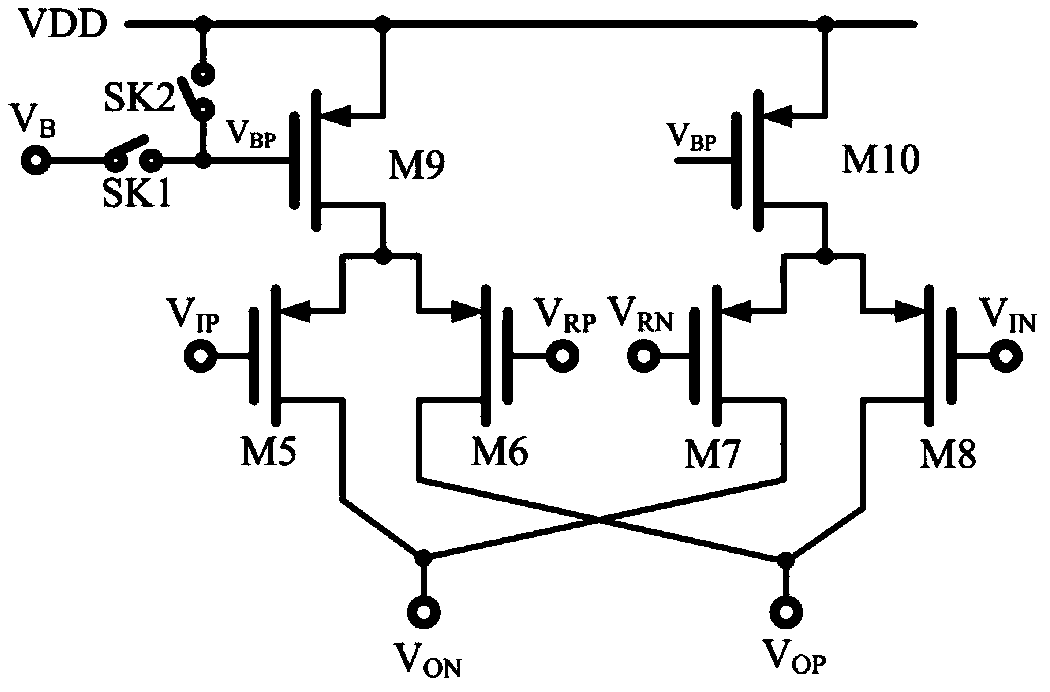

[0042] The configurable co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More