An ldpc Decoder Based on Random Computing

A random calculation and decoder technology, applied in the field of LDPC decoders, can solve the problems of high power consumption, low proportion of the logic part of the chip, large chip area, etc., to reduce the convergence time, increase the clock cycle, improve the The effect of convergence speed

Active Publication Date: 2018-04-03

FUDAN UNIV

View PDF4 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

In this case, the wiring complexity in the decoder is very high, occupying a large amount of chip area and the logic part of the chip accounts for a very low proportion, which brings additional power consumption and reduces the operating frequency of the chip.

Today, when smartphones and tablet computers are popular, excessive chip area and high power consumption are obviously unbearable

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

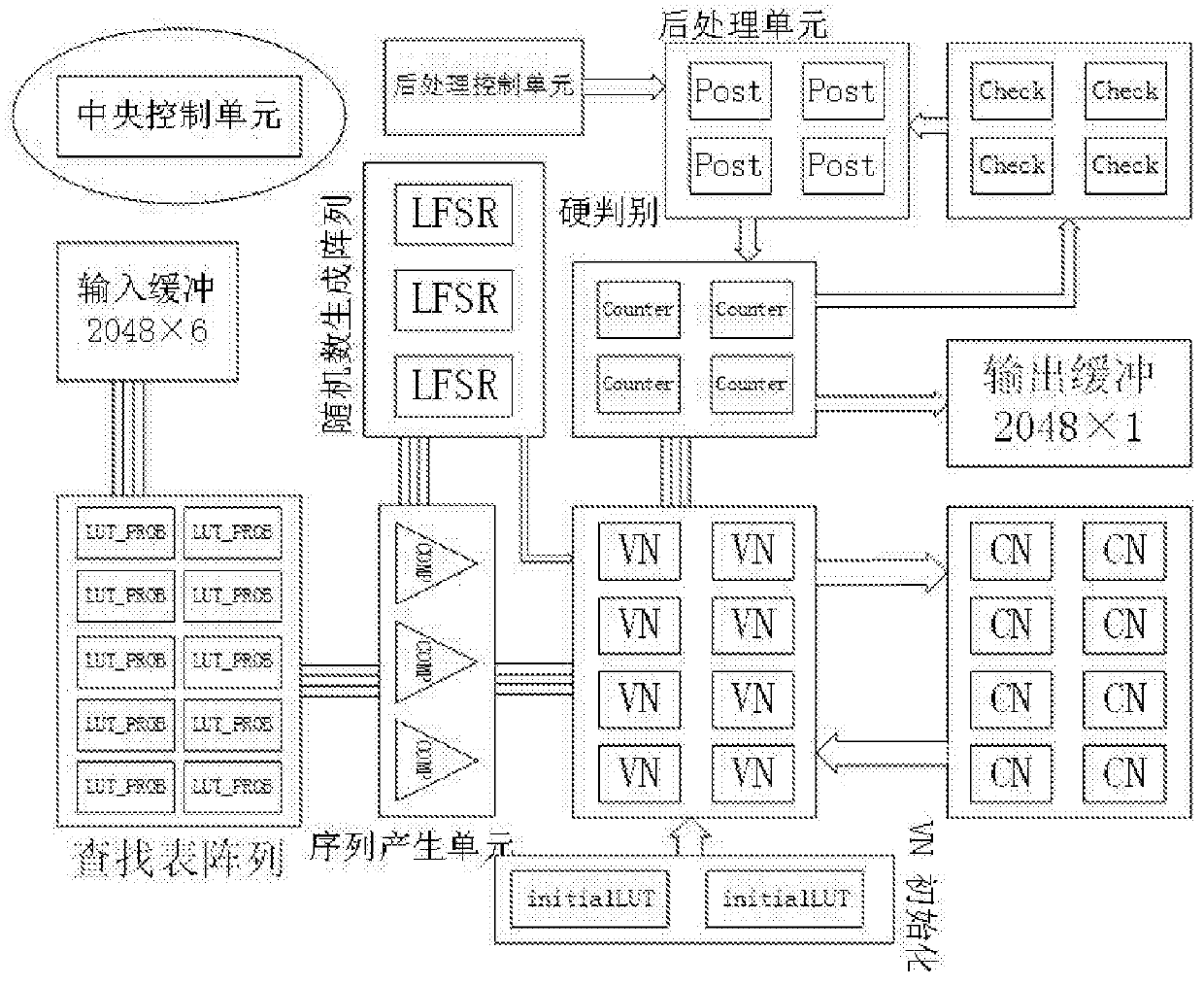

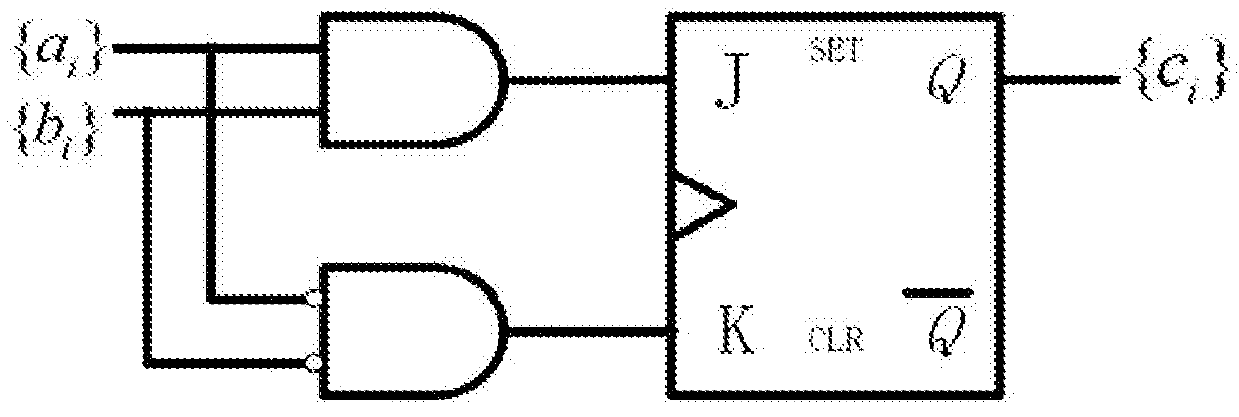

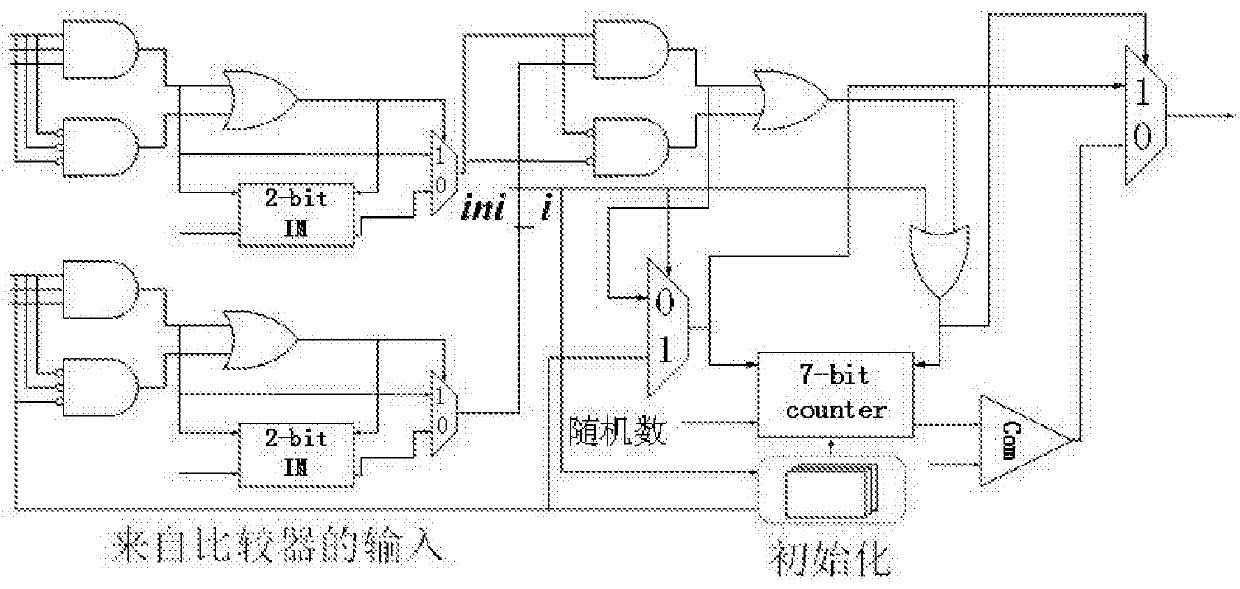

The invention belongs to the technical field of wireless digital communication and broadcasting, in particular to an LDPC decoder based on random calculation. The decoder is based on the random calculation algorithm of the belief propagation algorithm in the probability domain, and its structure includes: a lookup table LUT suitable for the NDS coefficient of the (2048,1723) parity check matrix in the IEEE 802.3an (10GBASE‑T) standard Array, and three hardware structures for accelerating convergence: the initialization module of the hard discriminant counter in the array VN based on the initialization of the lookup table LUT array; After the verification result of the verification node CN reaches a certain stage, the discriminant module output by the initialization array variable node VN is flipped over; at the same time, a new VN node structure is adopted. The invention can further improve the convergence speed of the decoder, improve the throughput rate of the decoder, and provide technical solution support for optical communication whose throughput rate is required to be as high as 100 Gbps in the future.

Description

A LDPC Decoder Based on Random Computing technical field The invention belongs to the technical field of wireless digital communication and broadcasting, in particular to an LDPC decoder based on random calculation. Background technique Today's society is a highly information-based society. Various information is transmitted back and forth through different channels, and the importance of information is constantly increasing, so the correctness of information must be guaranteed. However, the channel is usually full of various noises, and it is inevitable that some errors will occur when information is transmitted in the channel. Encoding the information transmitted in the channel before transmission and decoding after transmission is one of the most important ways to ensure the correct transmission of information. Low-density parity-check code (denoted as LDPC) decoder is an error-correcting code with excellent performance, and its performance can approach Shannon's limi...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): H03M13/11

Inventor 陈赟张启晨吴迪曾晓洋

Owner FUDAN UNIV