Method for improving functional verification efficiency of embedded processor

An embedded processor, functional verification technology, applied in functional inspection, detection of faulty computer hardware, etc., can solve problems such as difficult to find problem recurrence, redundant application scenarios, wasting time, etc., to shorten the time to market, improve Verify the effect of efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

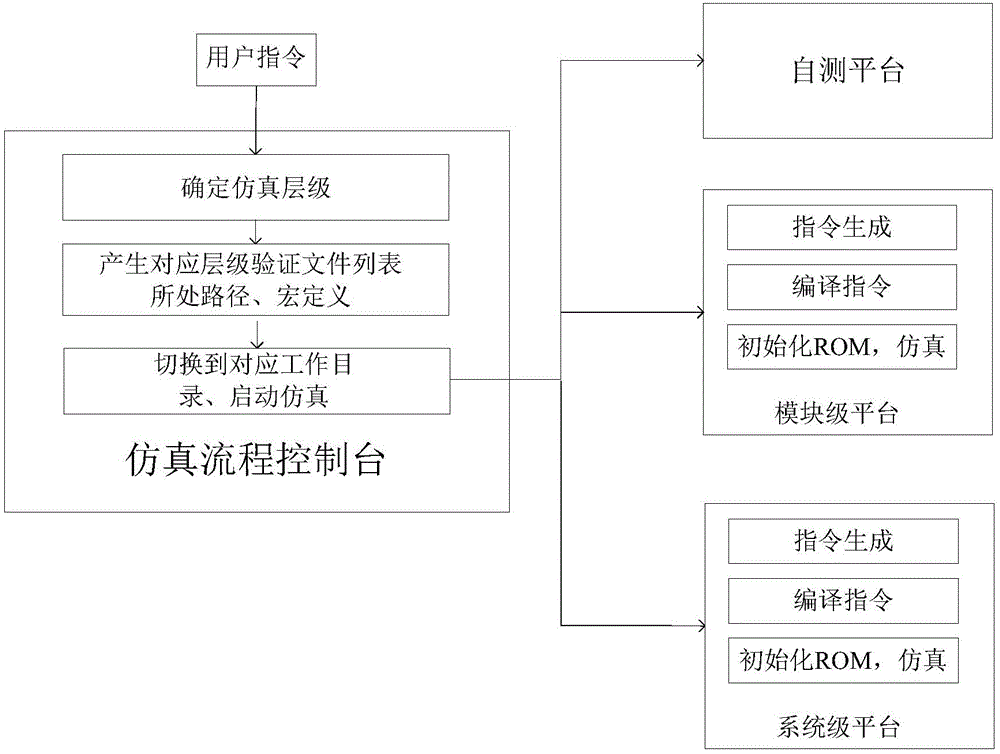

[0046] Please refer to figure 1 As shown, it is a module structure diagram of the simulation process realized by the present invention. In the figure, the simulation process console is responsible for establishing a self-test platform, a module-level verification platform or a system-level verification platform. The simulation process console determines the simulation level according to user instructions, and generates a list of corresponding level verification files, paths and macro definitions; and then performs The working directory is converted, and the simulation is started; the verification ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More