Rapid configuration and test method for programmable logic device in system programming

A programming logic and rapid configuration technology, applied in the field of integrated circuits, can solve problems such as error-prone, low test coverage, time-consuming and labor-intensive, etc., to achieve the effect of improving efficiency and quality, and improving test fault coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

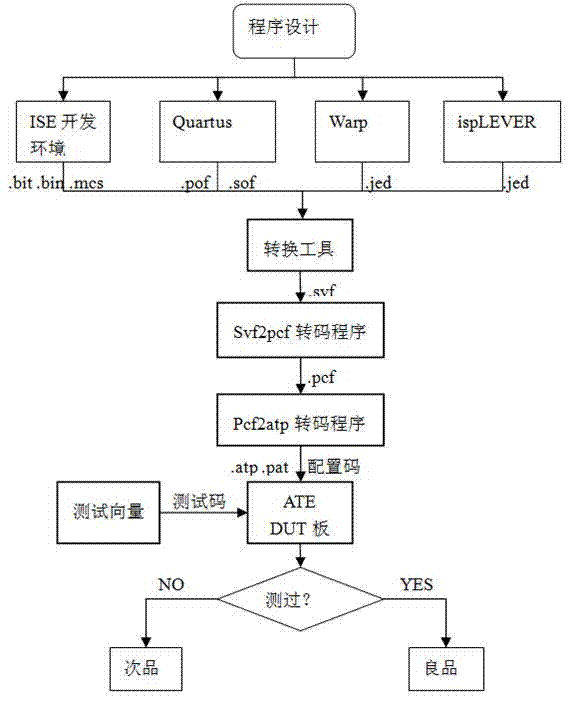

[0038] The present invention adopts the technical solution as a quick configuration and testing method for in-system programming of programmable logic devices, and the quick configuration and testing method obtains the configuration code of the ISP state machine through one programming and four transcoding processes;

[0039] The steps of the quick configuration and testing method are:

[0040] (1) Develop the test configuration program in the corresponding development environment of the programmable logic device, and obtain the original configuration code;

[0041] (2) Convert the original configuration code into an SVF file in serial vector format through a conversion tool; the conversion tools are: Xilinx's iMPACT tool, Altera's "Creat JAM, SVF, ISC" tool, Cypress's ISR tool, Lattice The company's ispVM tool.

[0042] (3) Convert SVF format files into PCF format files; the conversion tool is Svf2pcf transcoding program;

[0043] (4) Use the C language transcoding program ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More