System-in-package multi-chip interconnection test method and system-in-package multi-chip interconnection test device

A system-level packaging and testing method technology, applied in the field of integrated circuits, can solve problems affecting the accuracy of SIP chips and the interconnection testing of various bare chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

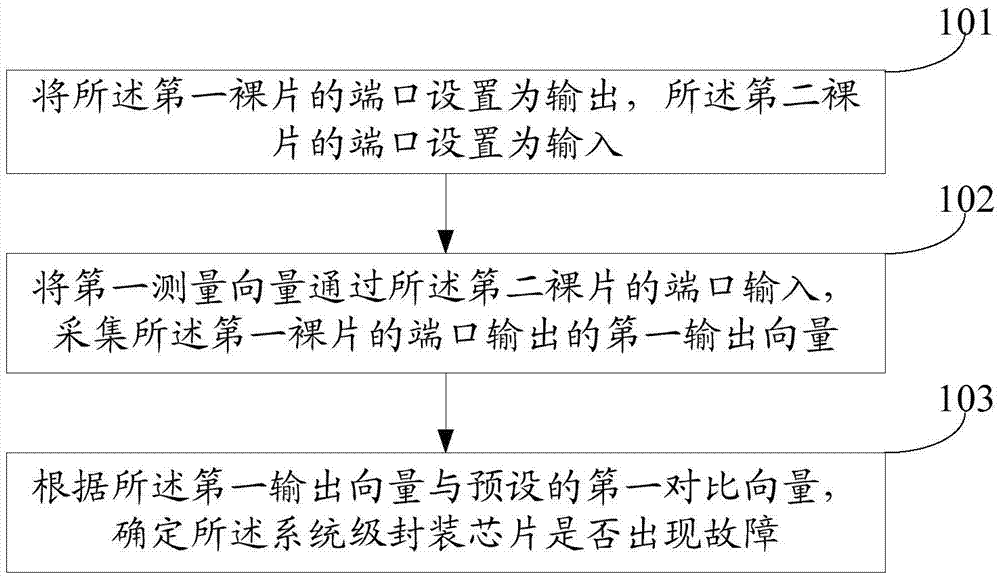

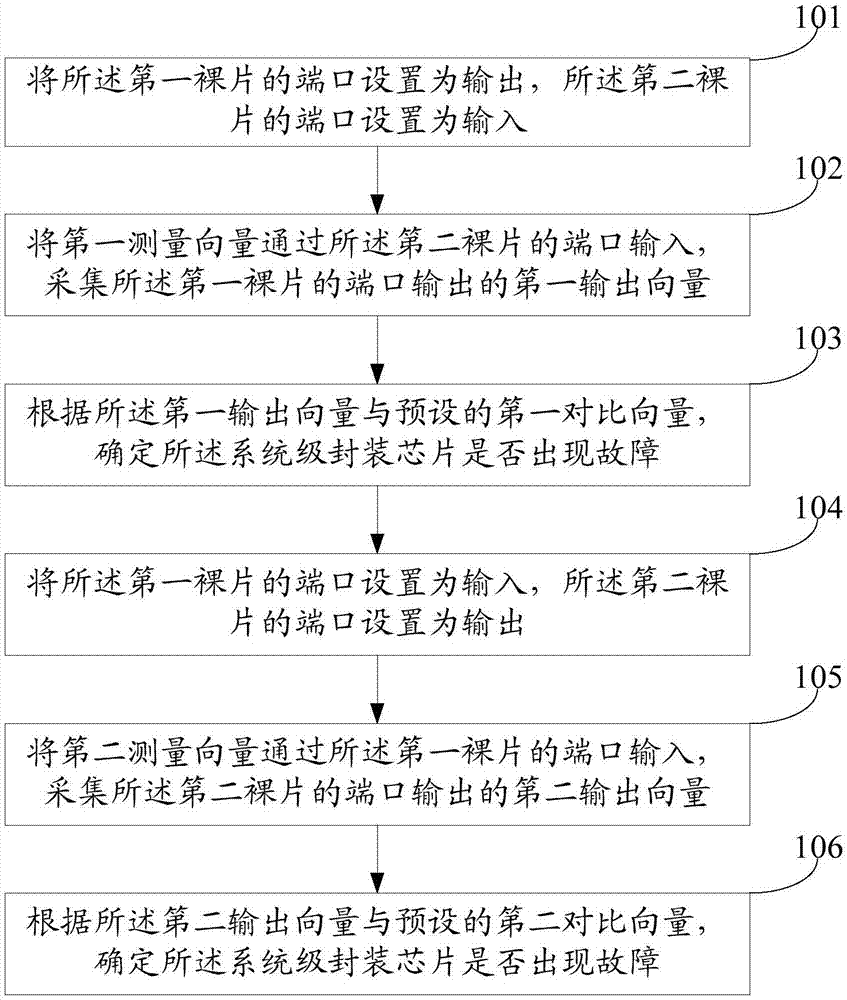

[0040] An embodiment of the present invention provides a system-in-package multi-chip interconnection testing method for a system-in-package chip, the system-in-package chip at least including a first die and a second die interconnected with the first die, Both the first die and the second die include a joint test working group JTAG interface, and the first die and the second die form a serial JTAG structure; the system-in-package chip can also be It is called a SIP chip. Such as figure 1 As shown, the system-in-package multi-chip interconnection testing method includes:

[0041] Step 101. Set the port of the first die as an output, and the port of the second die as an input.

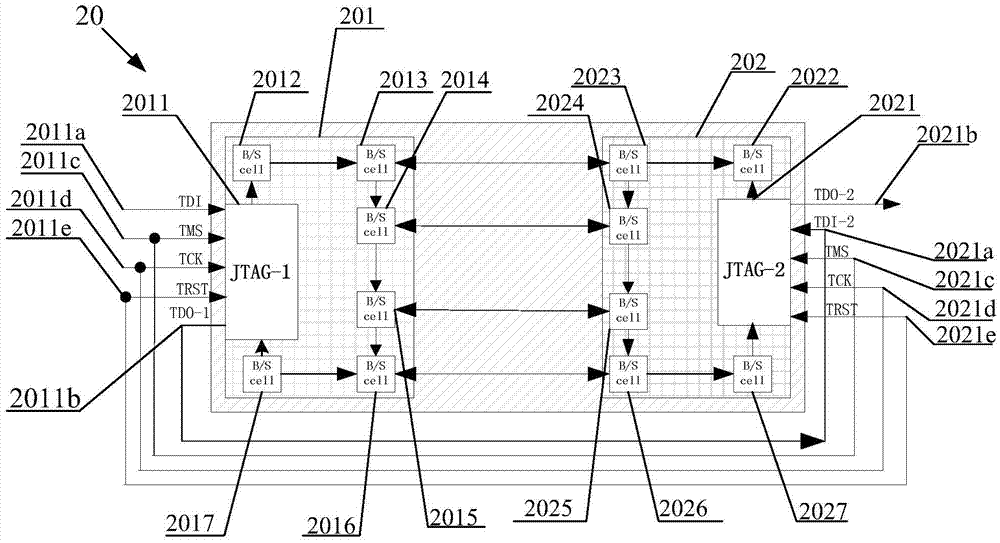

[0042] example, such as figure 2 As shown, the system-in-package chip 20 may include a first di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More