Automatic generating device for module-level UVM (unified voltage modulation) verification platform based on AMBA bus

A verification platform, module-level technology, used in functional inspection, detection of faulty computer hardware, software testing/debugging, etc., can solve difficult problems, shorten the cycle, reduce requirements, and improve quality and efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

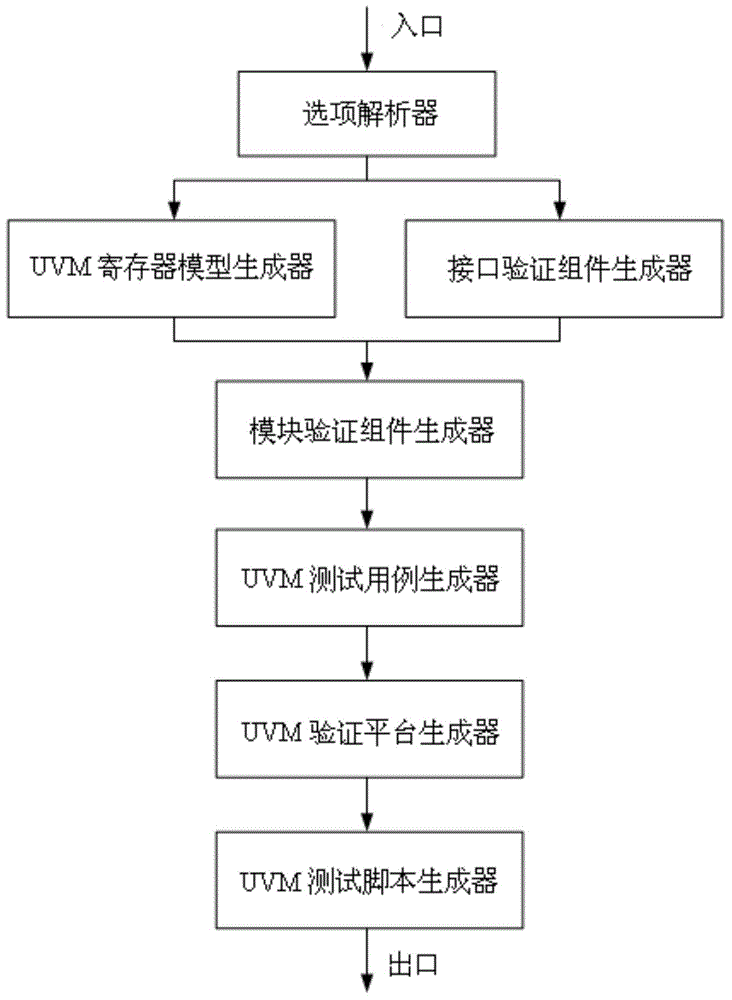

[0019] Referring to the accompanying drawings, in the following embodiments, the automatic generation device (hereinafter referred to as "device") of the modular-level UVM verification platform based on the AMBA bus includes:

[0020] An option parser, which is responsible for parsing the input parameters of the device, including module name, AMBA bus type, interface bus name, and register list. The result of parameter parsing will be passed to other parts of the installation. The selection of the AMBA bus type can be specified at the entry of the device. The register list can be specified at the entry of the device.

[0021] A UVM register model generator, responsible for generating a UVM register model conforming to the UVM standard. The typical workflow is to first check the system settings of the EDA tool. If the Cadence EDA tool is valid and the register list format is EXCEL or IPXACT, first perform the corresponding format conversion and then call the Cadence process; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More