Delay circuit

A delay circuit and delay pin technology, applied in electrical components, electronic switches, pulse technology, etc., can solve the problems of power chips without delay function and inconvenience

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Below in conjunction with accompanying drawing and preferred embodiment the present invention is described in further detail:

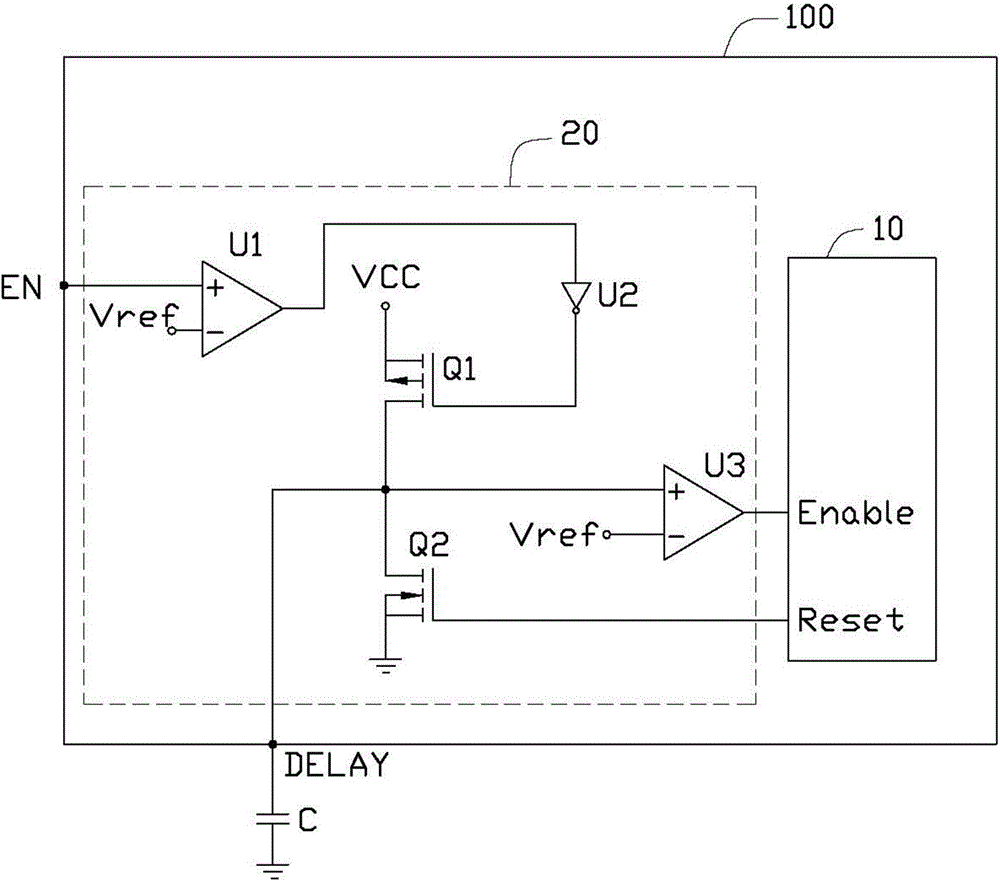

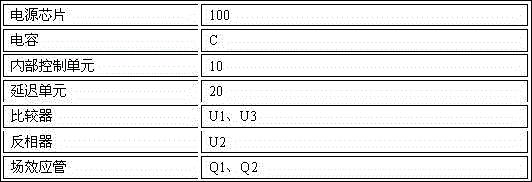

[0015] Please refer to figure 1 A preferred embodiment of the delay circuit of the present invention includes a power chip 100 and a capacitor C, the power chip 100 is provided with an enabling pin EN and a delay pin DELAY, and the delay pin DELAY of the power chip 100 ground through the capacitor C.

[0016] In this embodiment, the power chip 100 includes an internal control unit 10 and a delay unit 20 .

[0017] The internal control unit 10 is provided with an enabling pin Enable and a reset pin Reset. When the enable pin Enable receives a high level signal, the internal control unit 10 starts to work. When the enable pin Enable receives a low level signal, the internal control unit 10 does not work.

[0018] The delay unit 20 includes two comparators U1, U3, two electronic switches (field effect transistors Q1, Q2 in this embodiment) and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com