Constant-temperature instruction level self-testing method for testing time delay faults in inner heating manner

A self-test, instruction-level technology, applied in the field of semiconductor technology, to achieve high fault coverage, avoid damage, and avoid the effect of loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments. This embodiment is carried out on the premise of the technical solution of the present invention, and detailed implementation and specific operation process are given, but the protection scope of the present invention is not limited to the following embodiments.

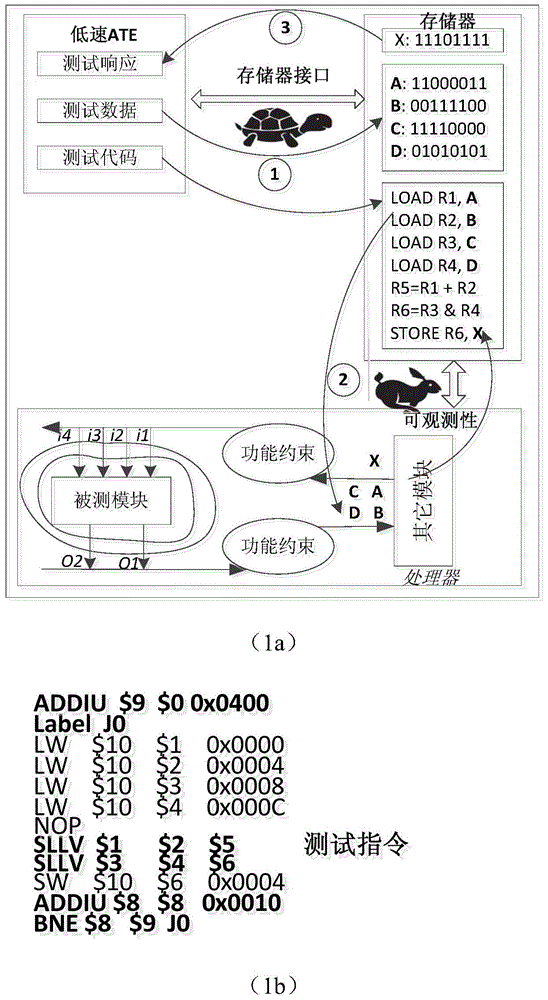

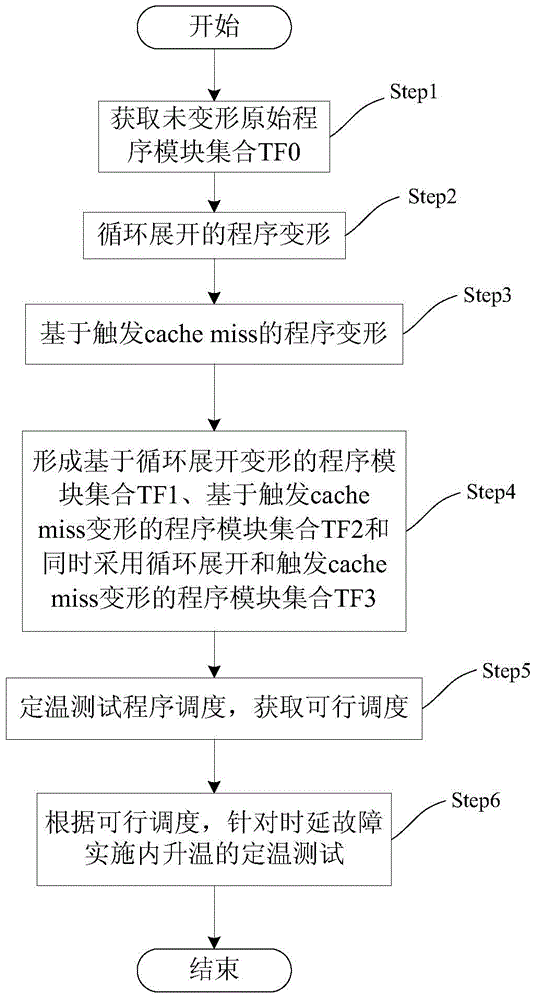

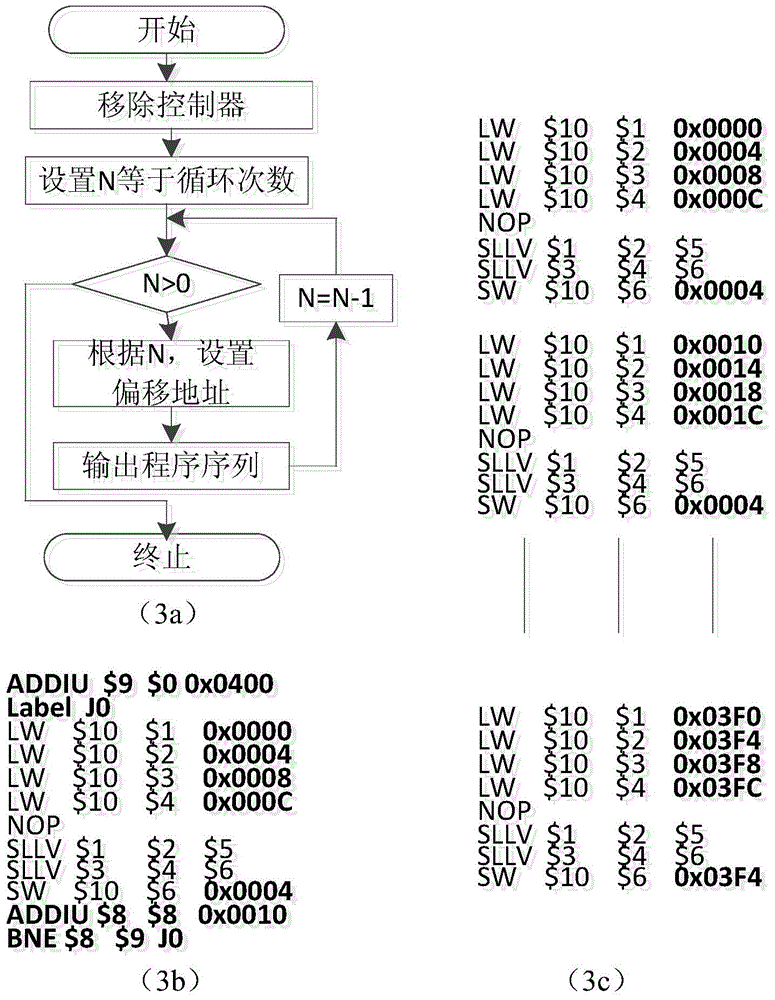

[0067] 1. Instruction-level self-test method

[0068] Instruction-level self-test method is a very promising processor test method, which can test two types of faults, fixed type and time delay, in functional mode by using normal program. When testing delay faults, the execution process of the instruction-level self-test program is as follows: figure 1 As shown, the signal line ① in the figure indicates downloading test code and test data, ② indicates executing test program, and ③ indicates uploading test response. In this example, the test vector pairs for delay faults are first lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More