Memorizer apparatus and memorizer control method

A control method and memory technology, applied in static memory, read-only memory, digital memory information and other directions, to achieve the effect of eliminating capacitive coupling effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the purpose, features and advantages of the present invention more comprehensible, specific embodiments of the present invention are listed below, together with the attached drawings, for detailed description as follows.

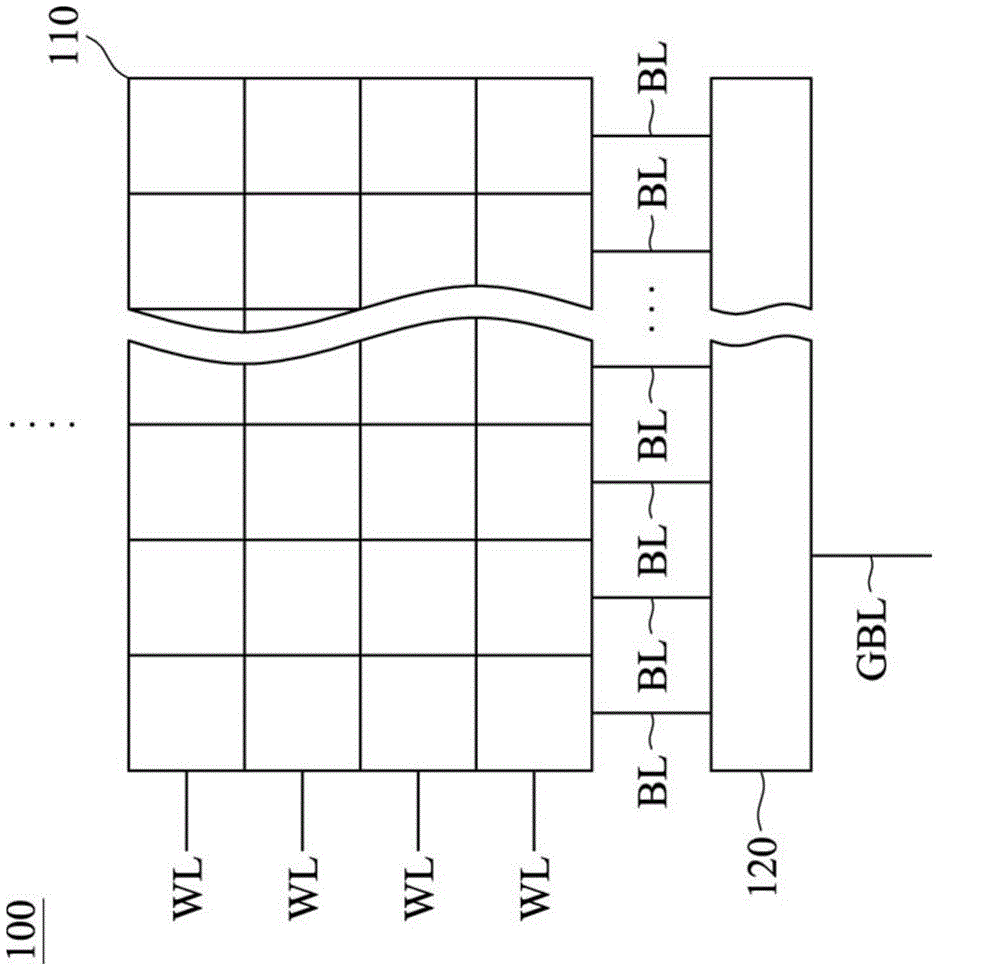

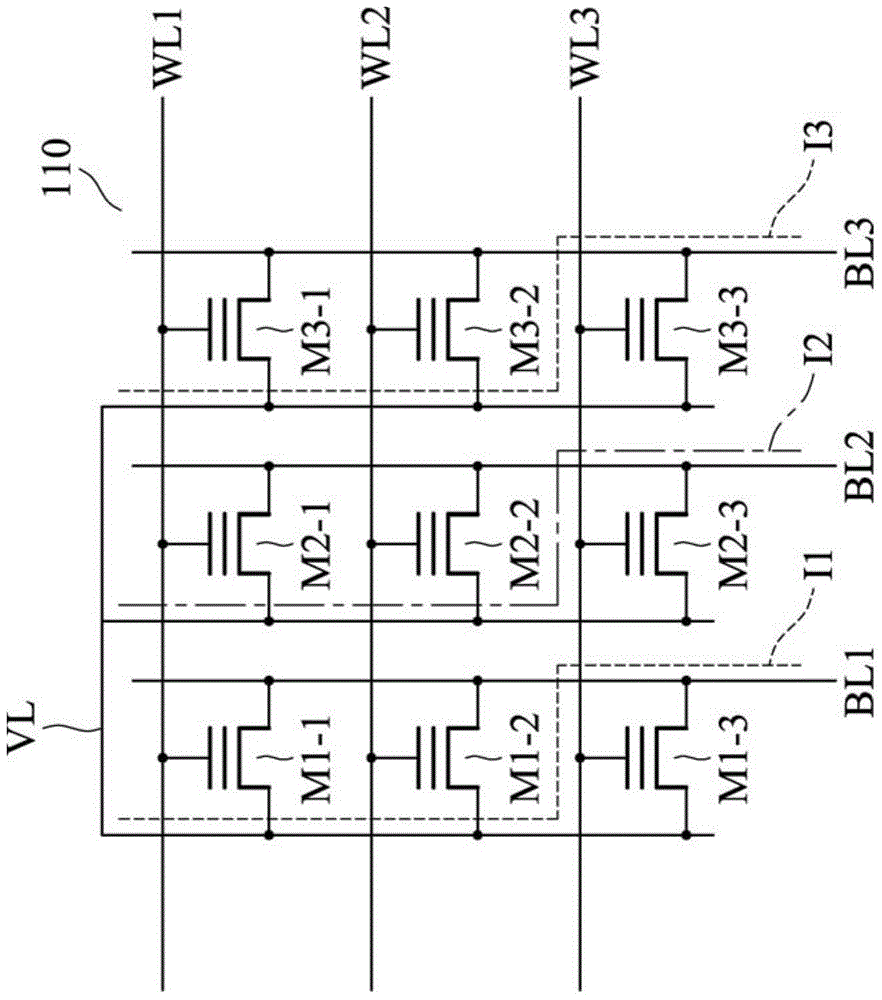

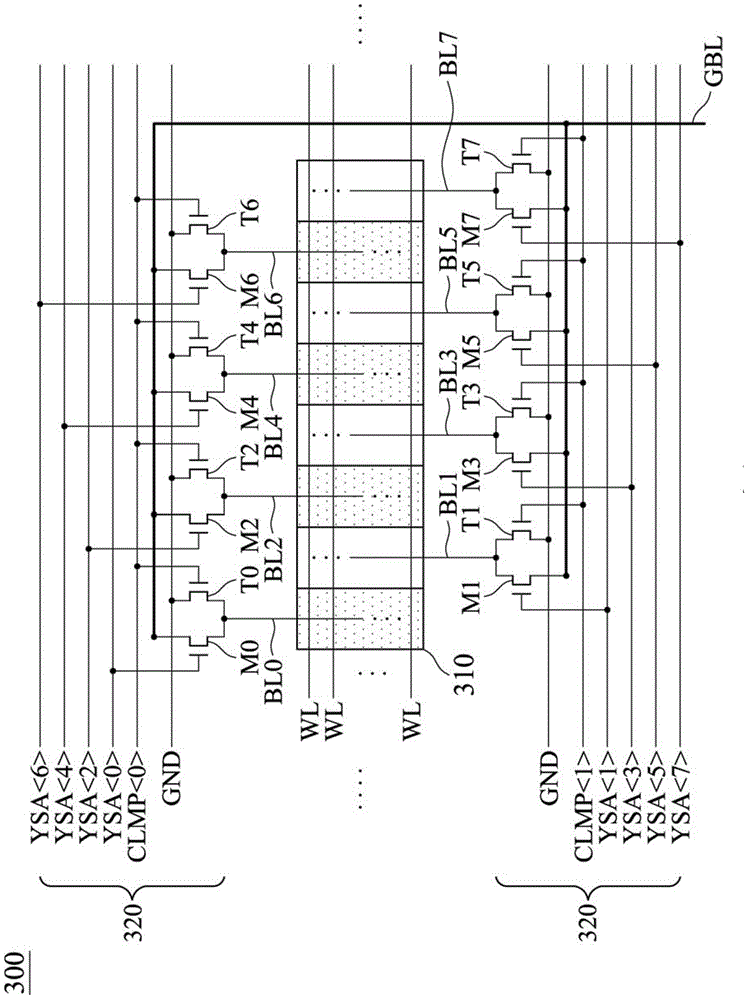

[0039] image 3 A schematic diagram of a memory device 300 according to an embodiment of the invention is shown. The memory device 300 may be a flash memory (Flash Memory), such as a NOR flash memory. Such as image 3 As shown, the memory device 300 includes at least a memory cell array (Memory Cell Array) 310 and a column decoder (Column Decoder) 320 . It must be understood that the memory device 300 may also include other components, such as a driver, a row decoder, and a sense amplifier (SA). To simplify the drawing, some elements of the memory device 300 are omitted and not shown in image 3middle. The memory cell array 310 may include a plurality of memory cells (Memory Cell). In some embodiments, the memory cell array 310 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More