Patents

Literature

50results about How to "Reduce capacitive coupling effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

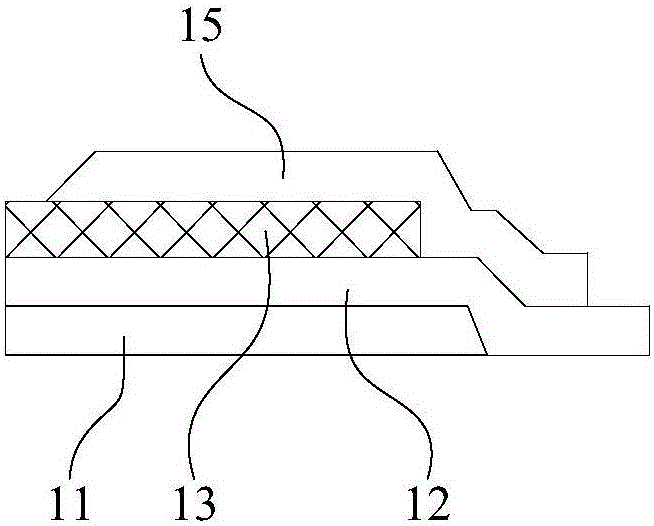

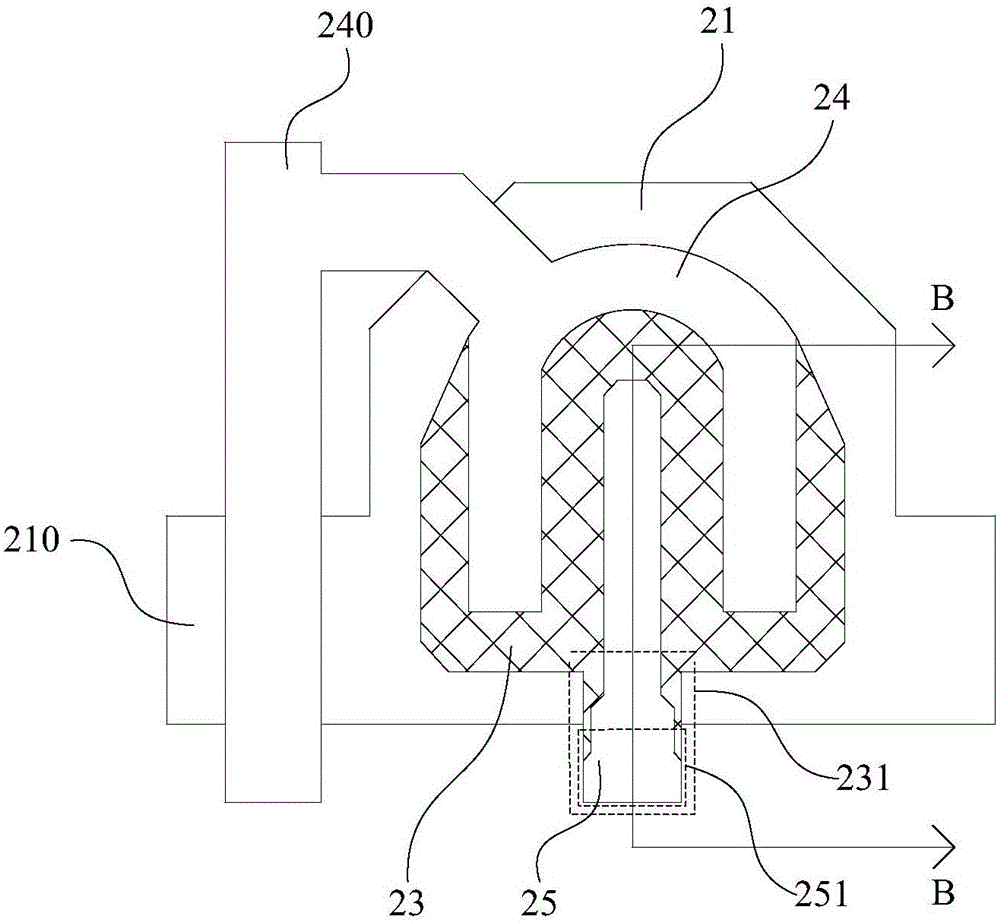

Capacitive distance sensor

ActiveCN102954753ASimple measurement circuitReduce thermal noiseUsing electrical meansElectric/magnetic depth measurementCapacitive couplingPhysics

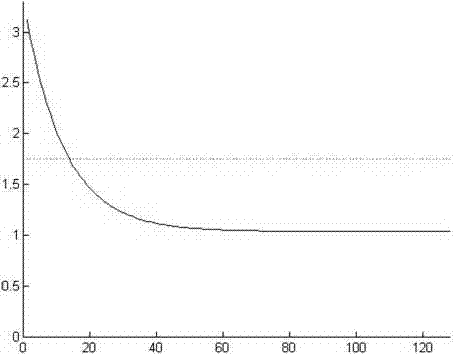

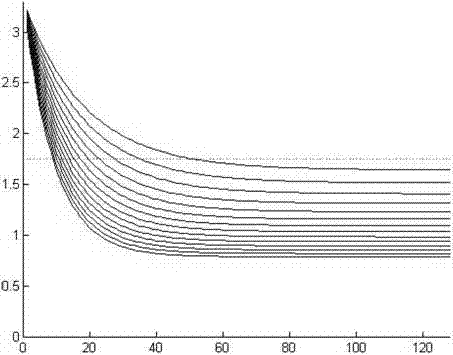

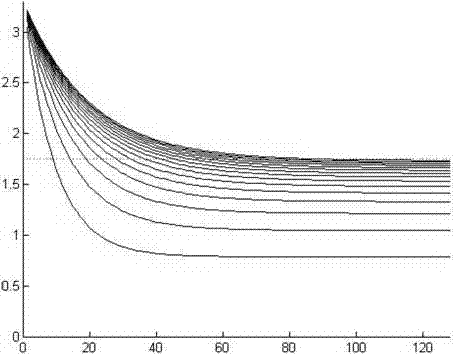

The invention provides a capacitive distance sensor. The capacitive distance sensor is on the basis of the physical principle that the value of a capacitor is inversely proportional to the distance between capacitor plates; and once a coupling capacitor is generated between the surface of a detected conductor and a capacitance measuring plate on the single side of the surface of a sensor, the distance from the capacitance measuring plate to the surface of the detected conductor can be calculated by measuring the value of the coupling capacitor. The capacitive distance sensor provided by the invention has a circuit structure, and comprises the capacitance measuring plate, a reference capacitor, a capacitor coupling plate, a reference capacitor charging circuit, a capacitance measuring plate discharging circuit, a charge neutralization circuit, a programmable level generator 1, a programmable level generator 2 and a voltage comparator. The capacitive distance sensor has the characteristics of linearization, resistance to shifting, and low noise.

Owner:MICROARRAY MICROELECTRONICS CORP LTD

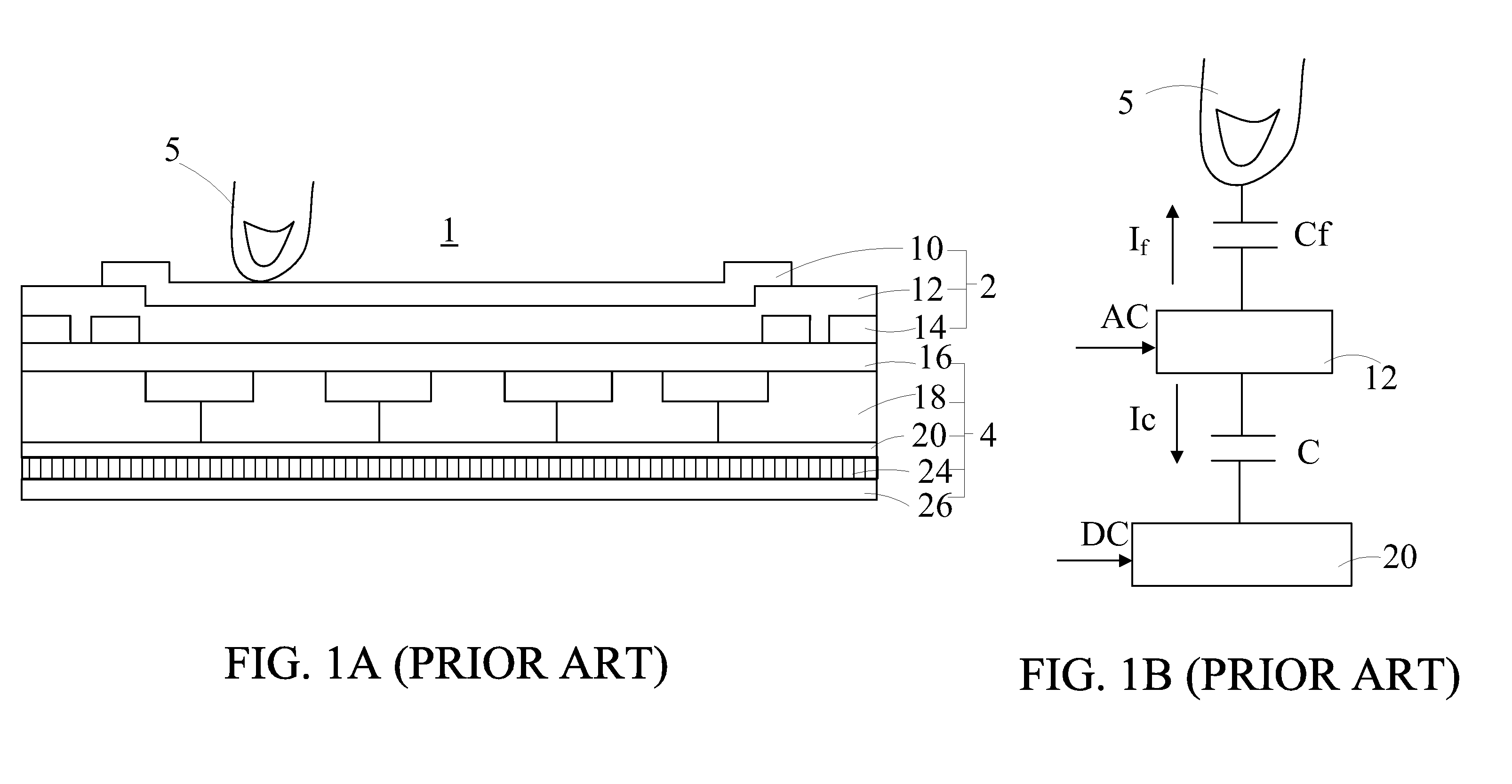

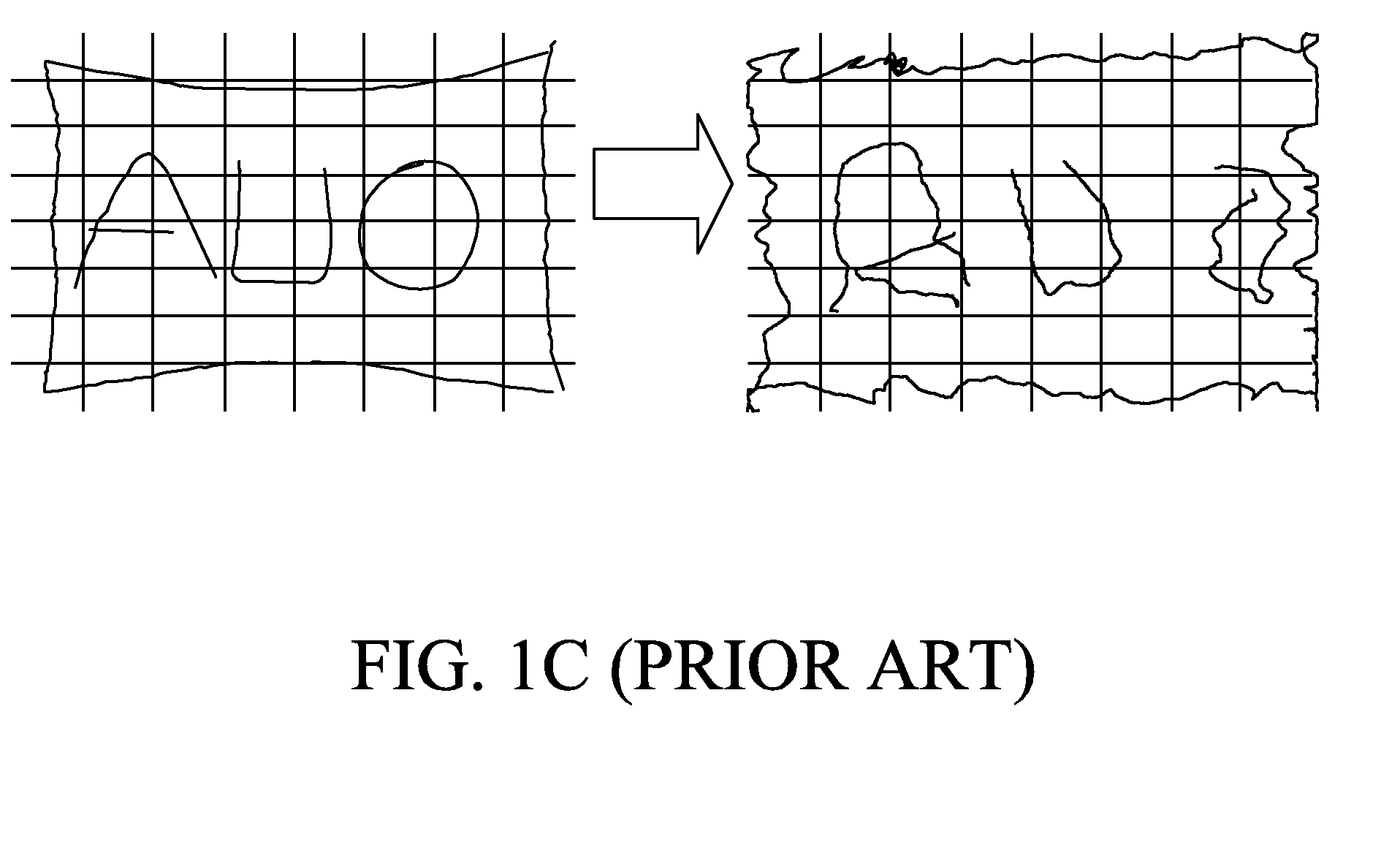

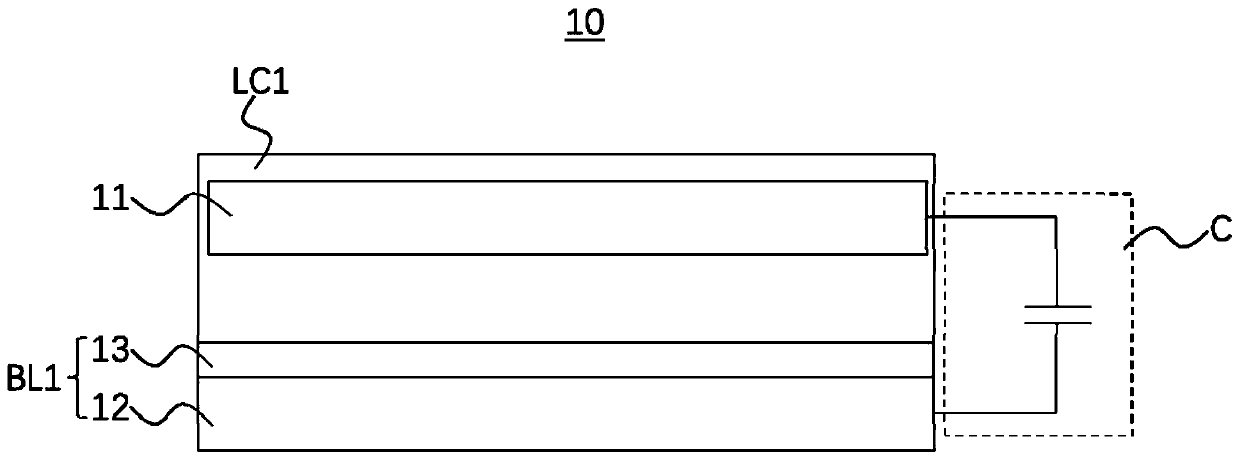

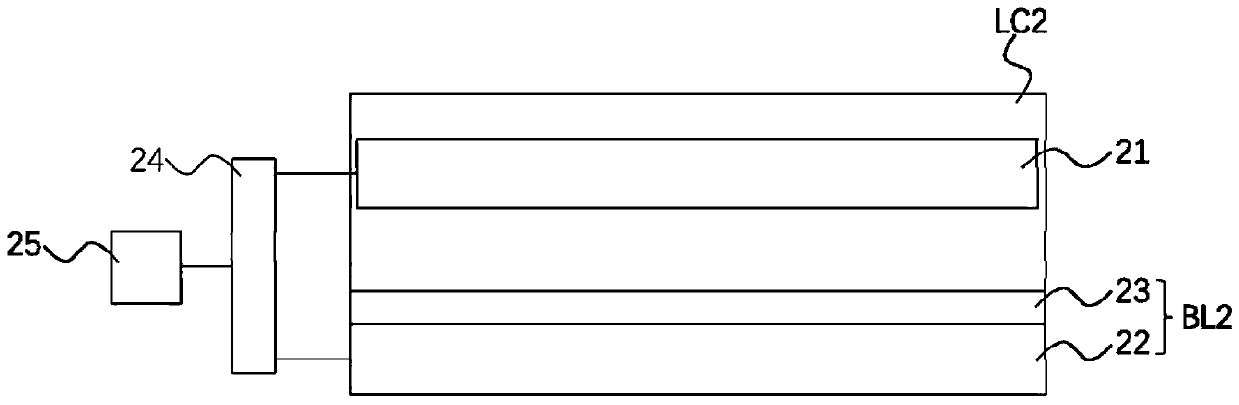

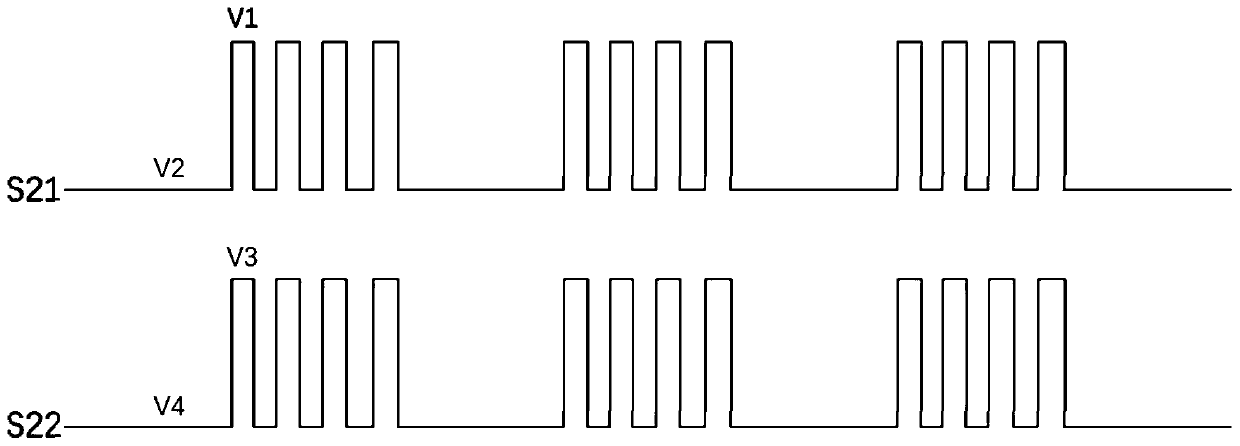

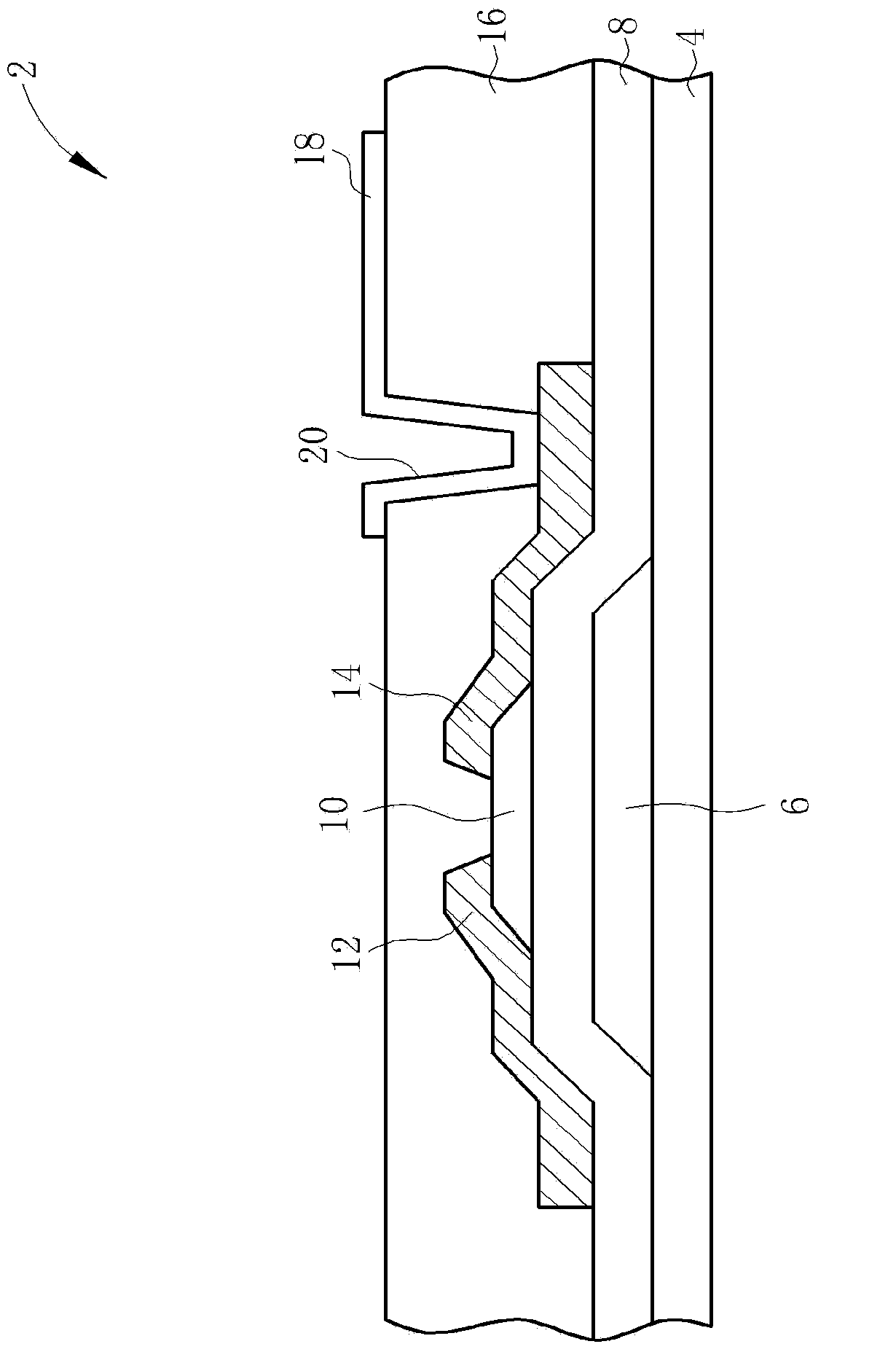

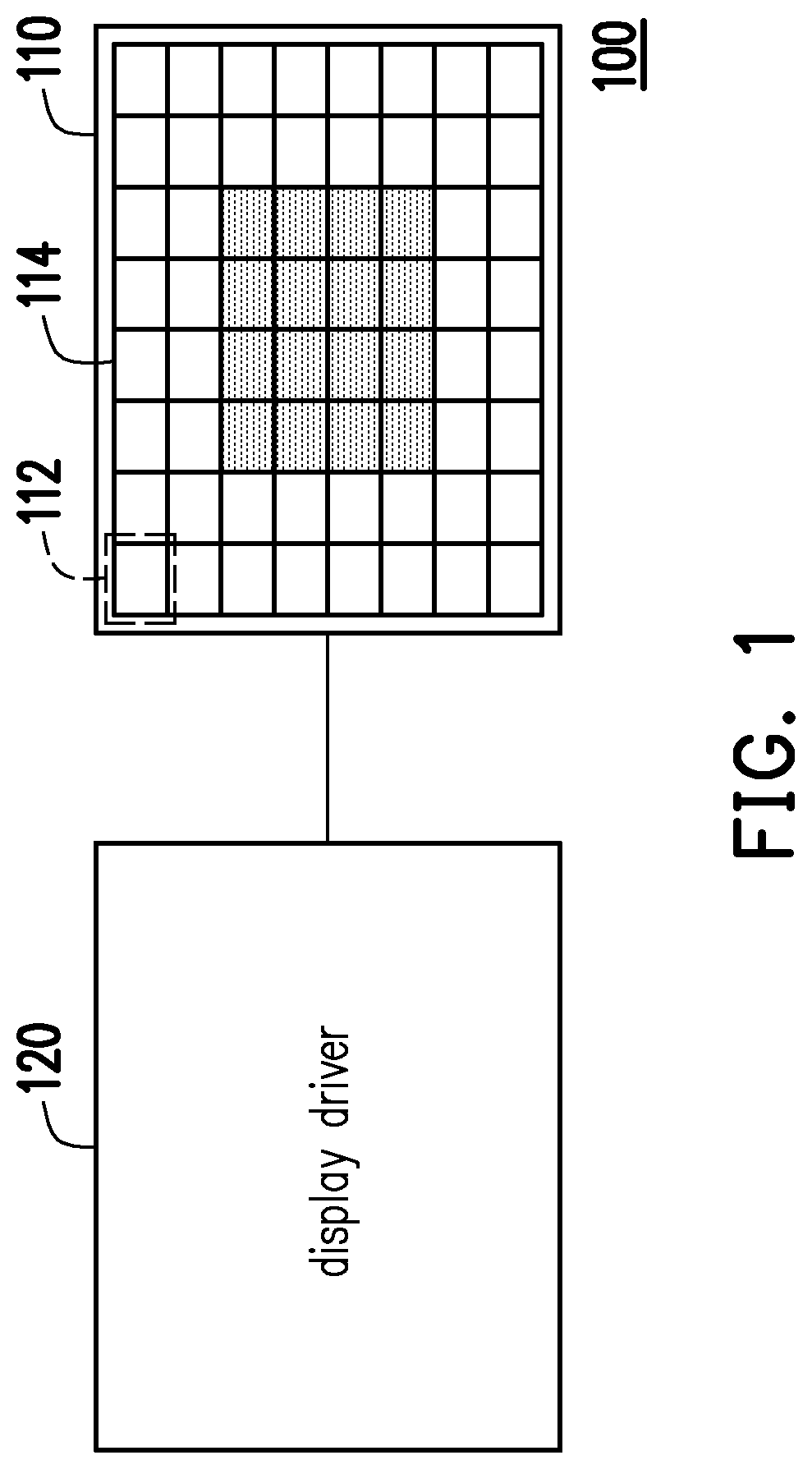

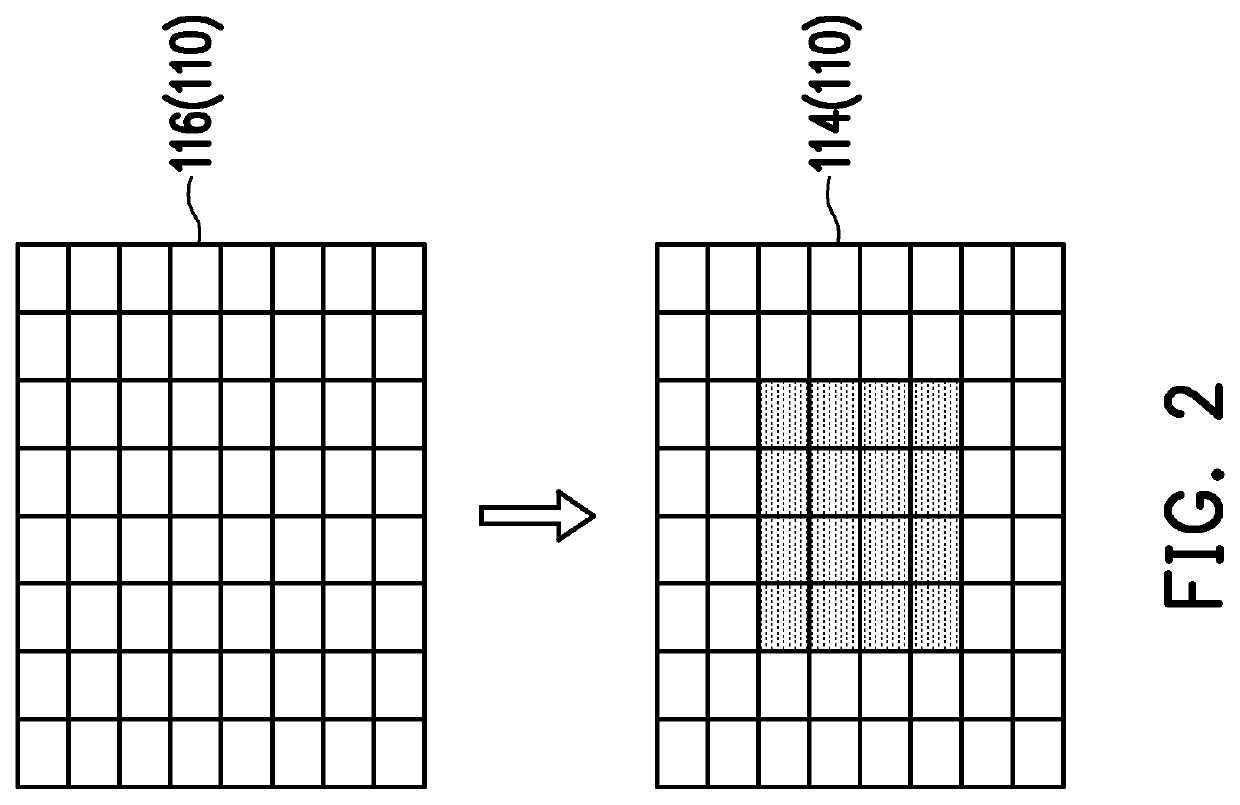

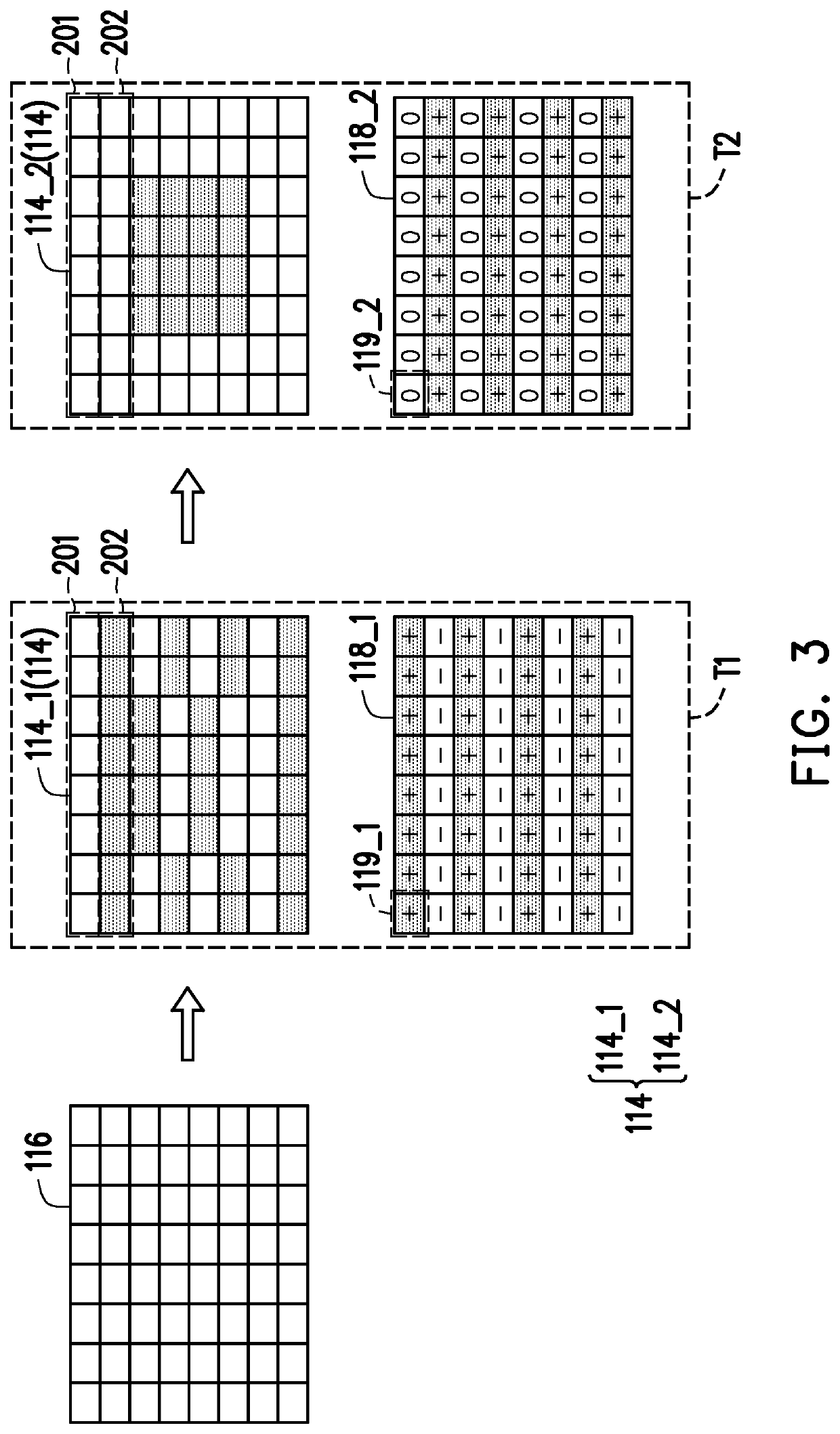

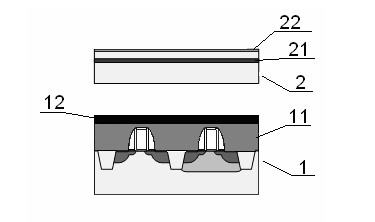

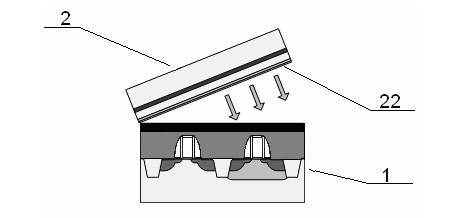

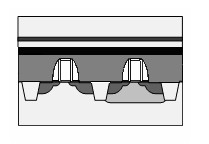

Display device and method of applying the same

InactiveUS20100315374A1Reduce capacitive coupling effectsImprove touch sensitivityInput/output processes for data processingCapacitanceLiquid-crystal display

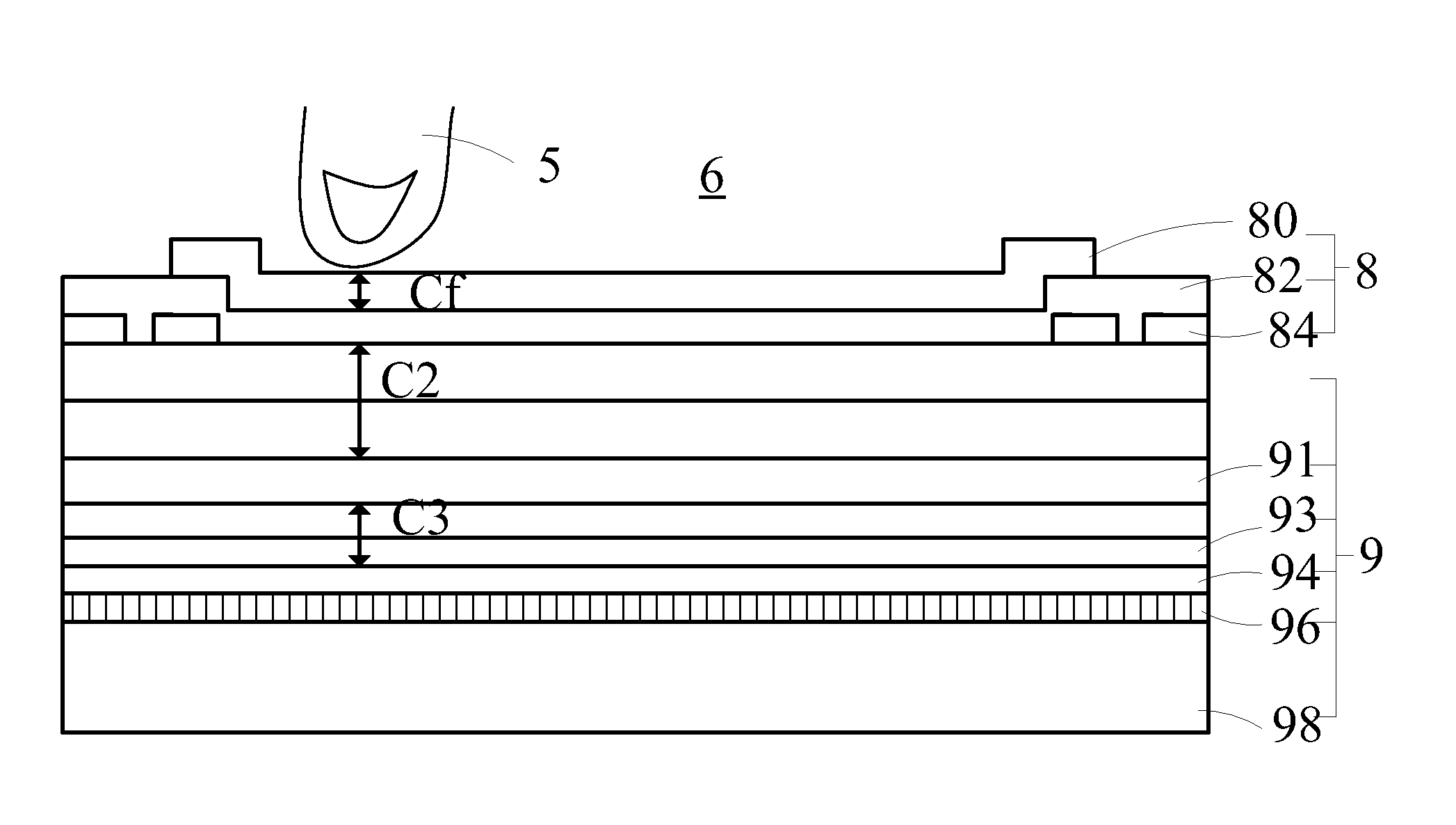

A display device and a method of applying the same are introduced herein. A shielding layer is utilized to interpose between a transparent conductive layer of a touch element and a common electrode layer of a liquid crystal display (LCD) panel. With controlling variances of a first and a second control signals, a coupling current between the transparent conductive layer and common electrode layer can approach none, whereby influences of capacitive coupling effect between the common electrode layer or shielding layer and the transparent conductive layer of the touch element can be reduced. Thus, high touch accuracy of the touch element can be achieved and the noise can be eliminated simultaneously.

Owner:AU OPTRONICS CORP

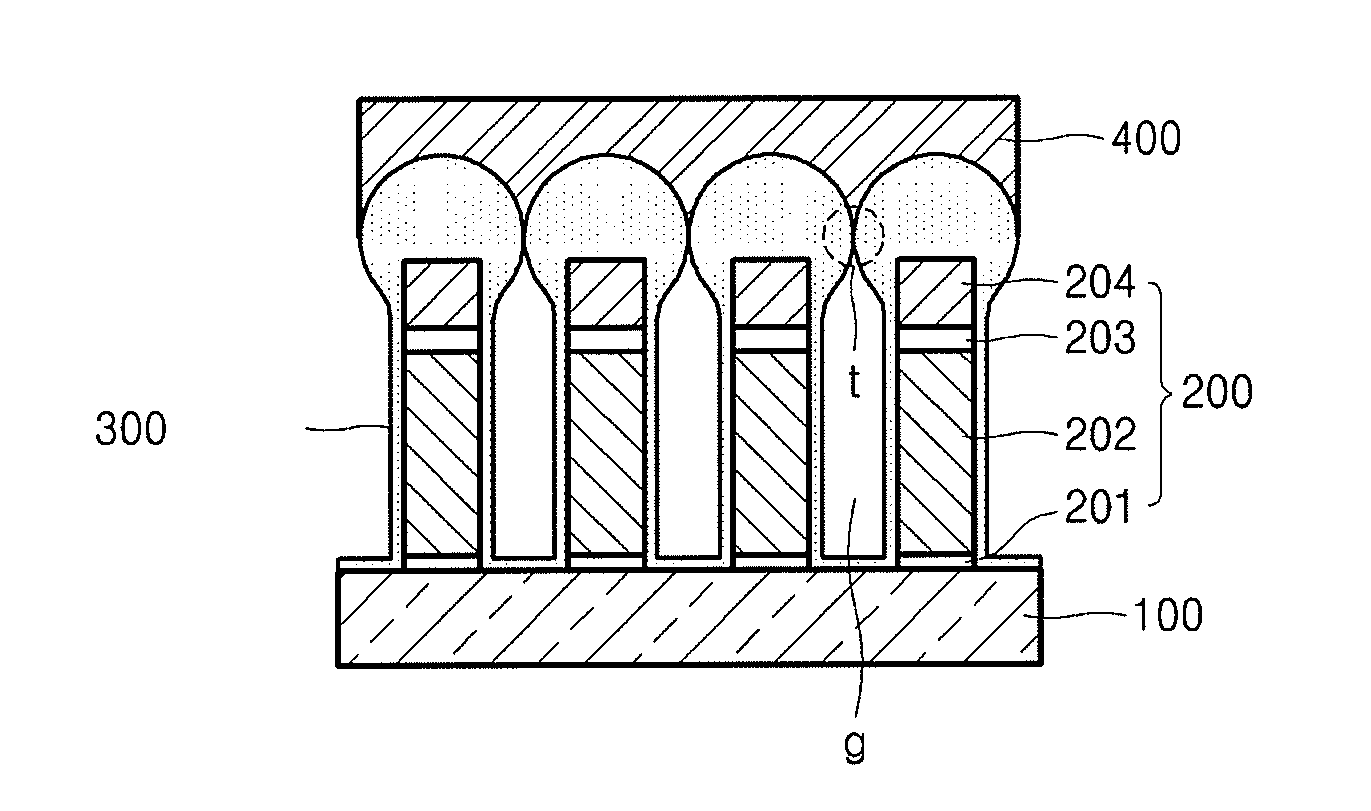

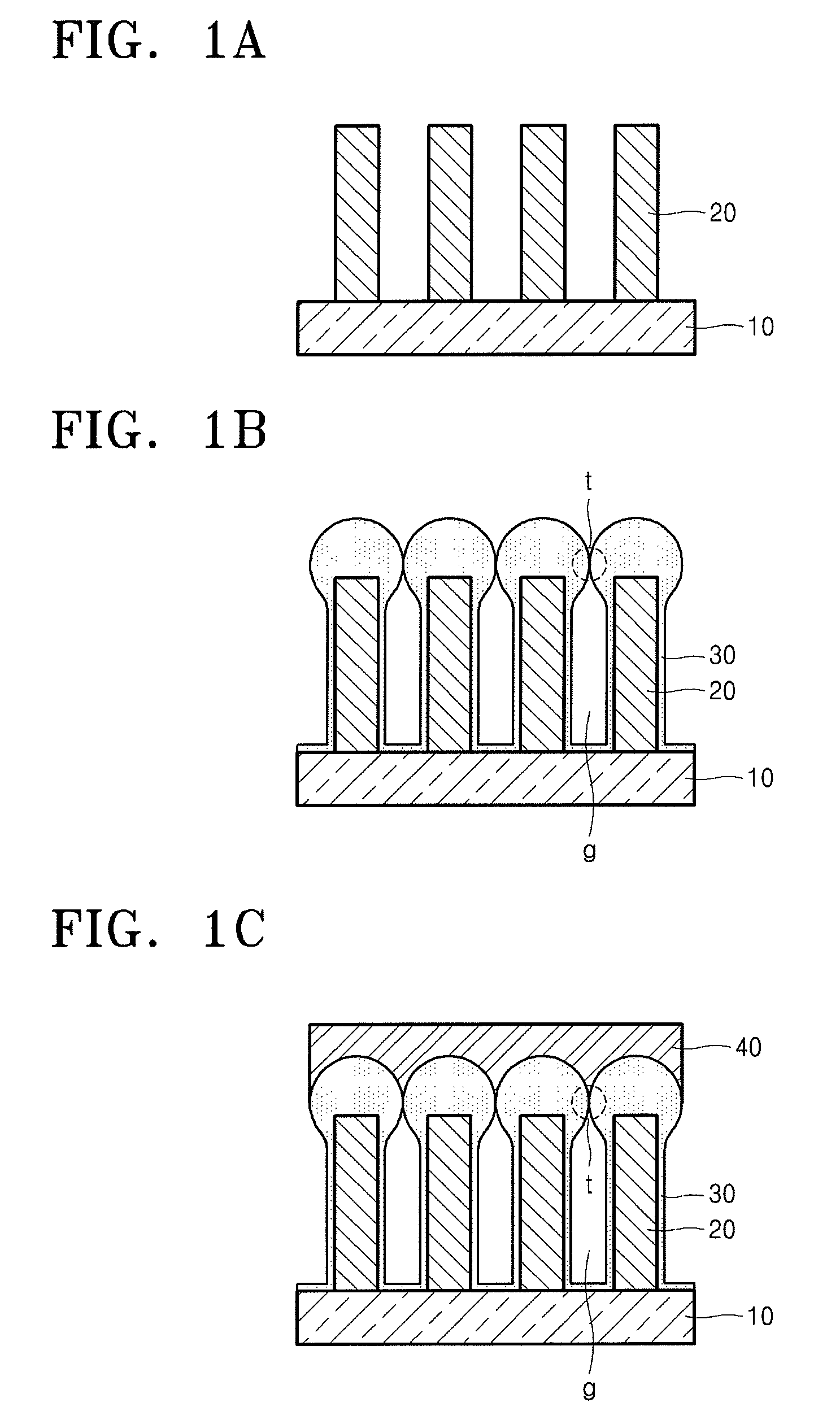

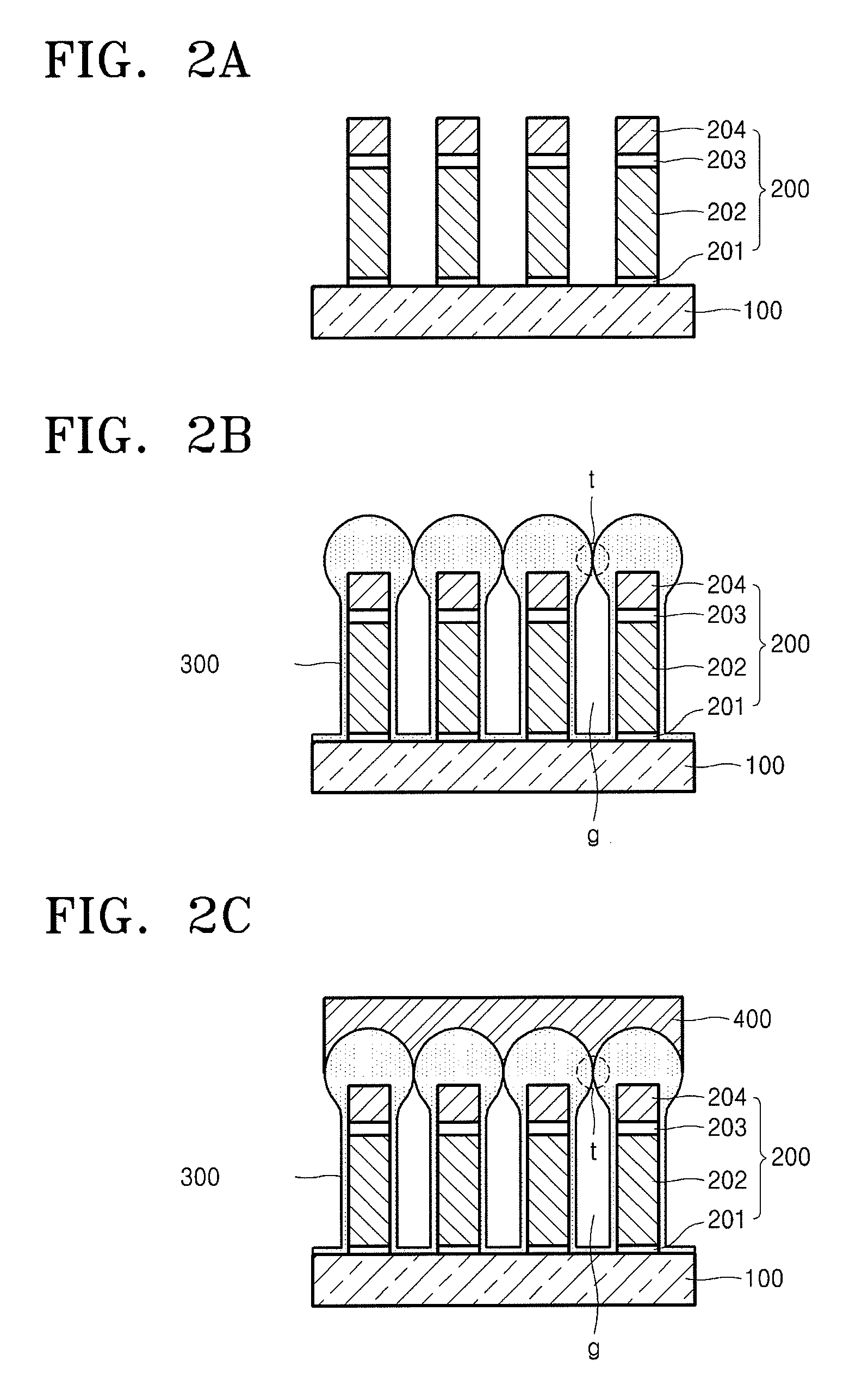

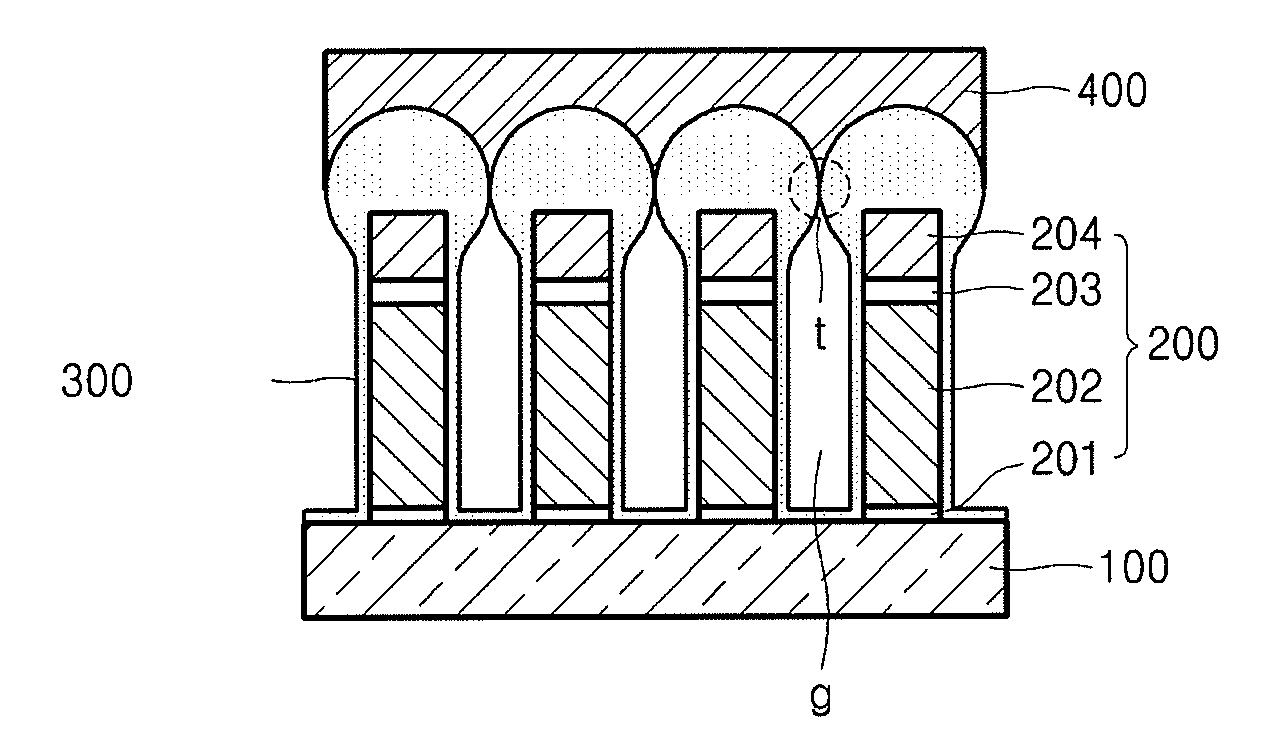

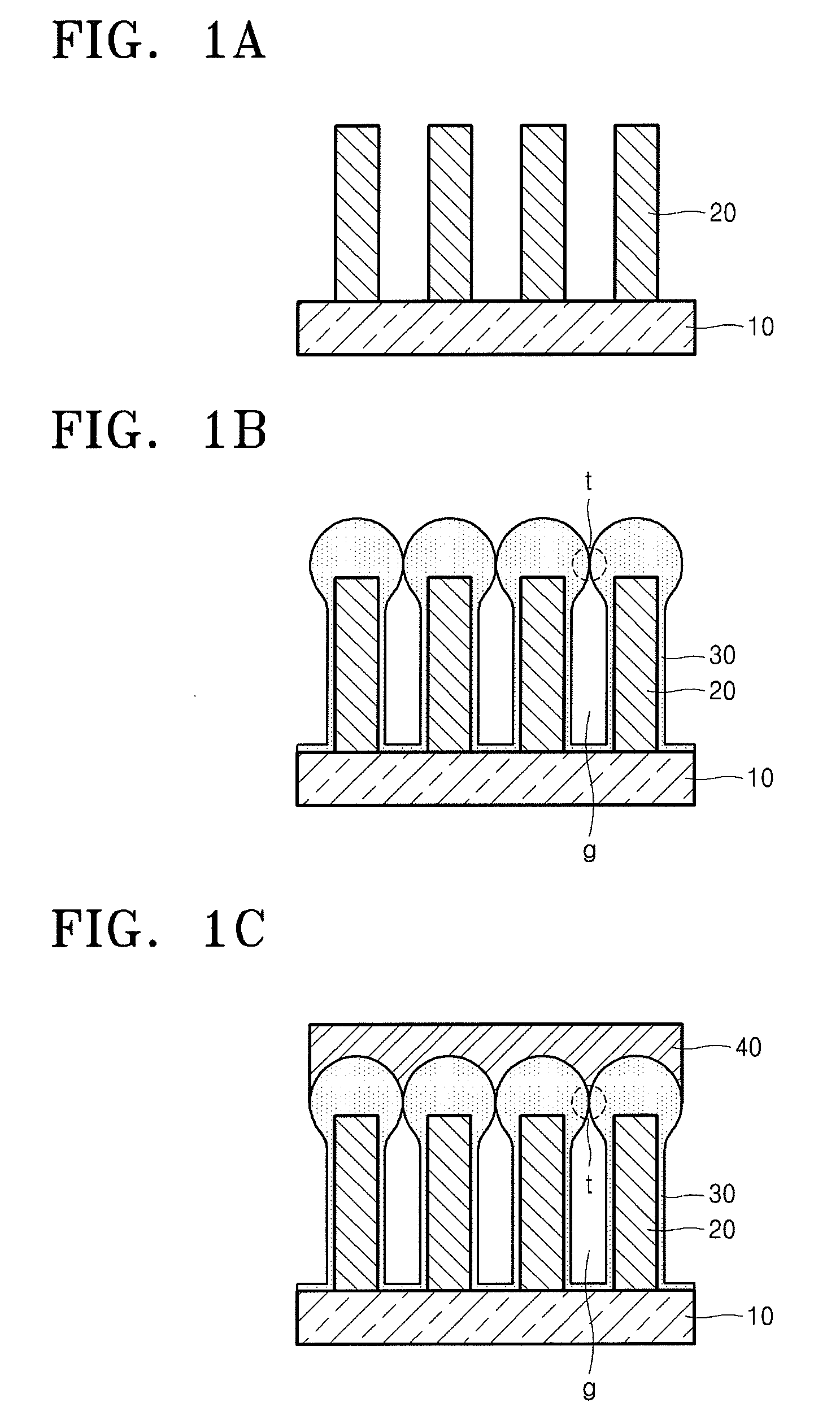

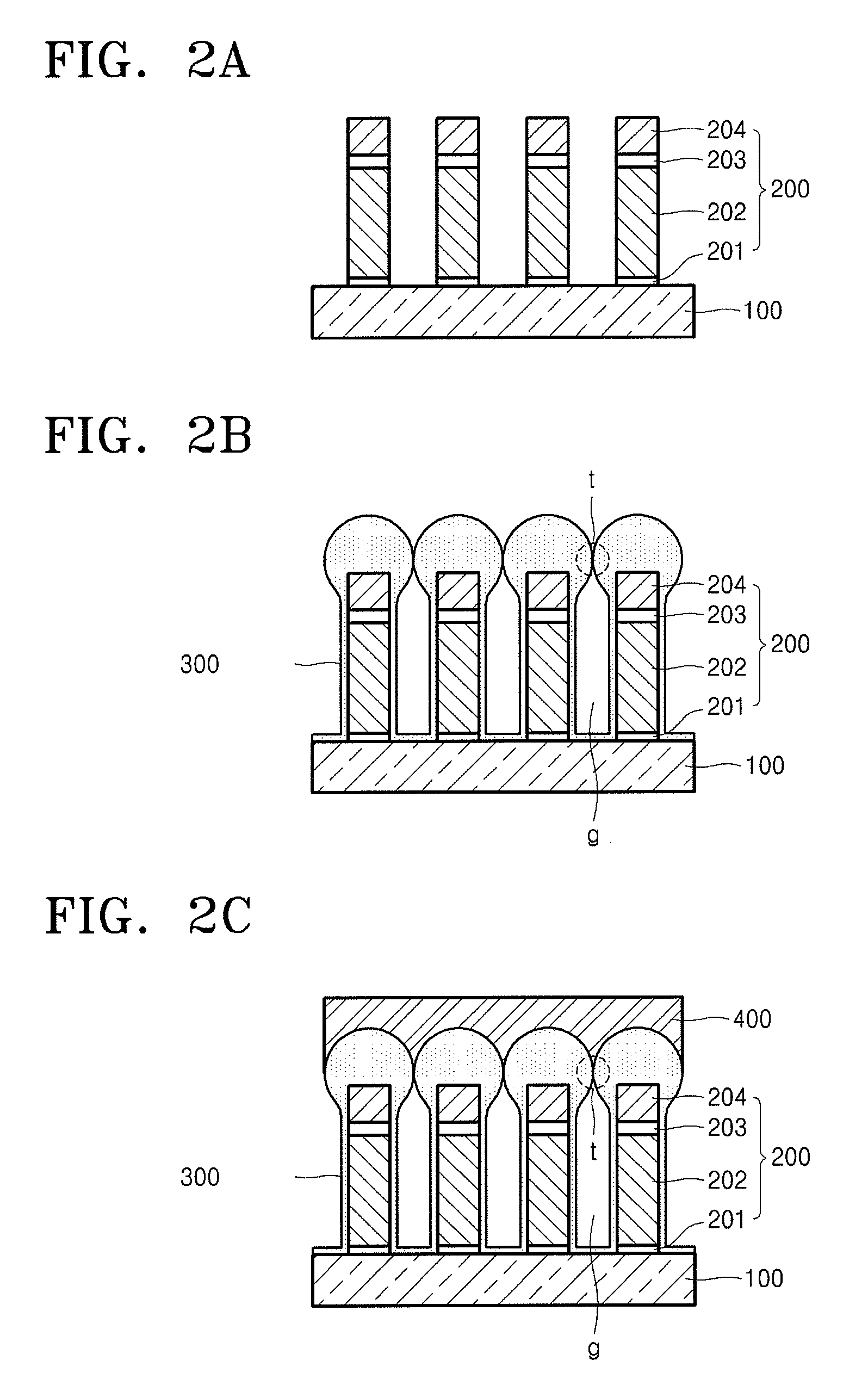

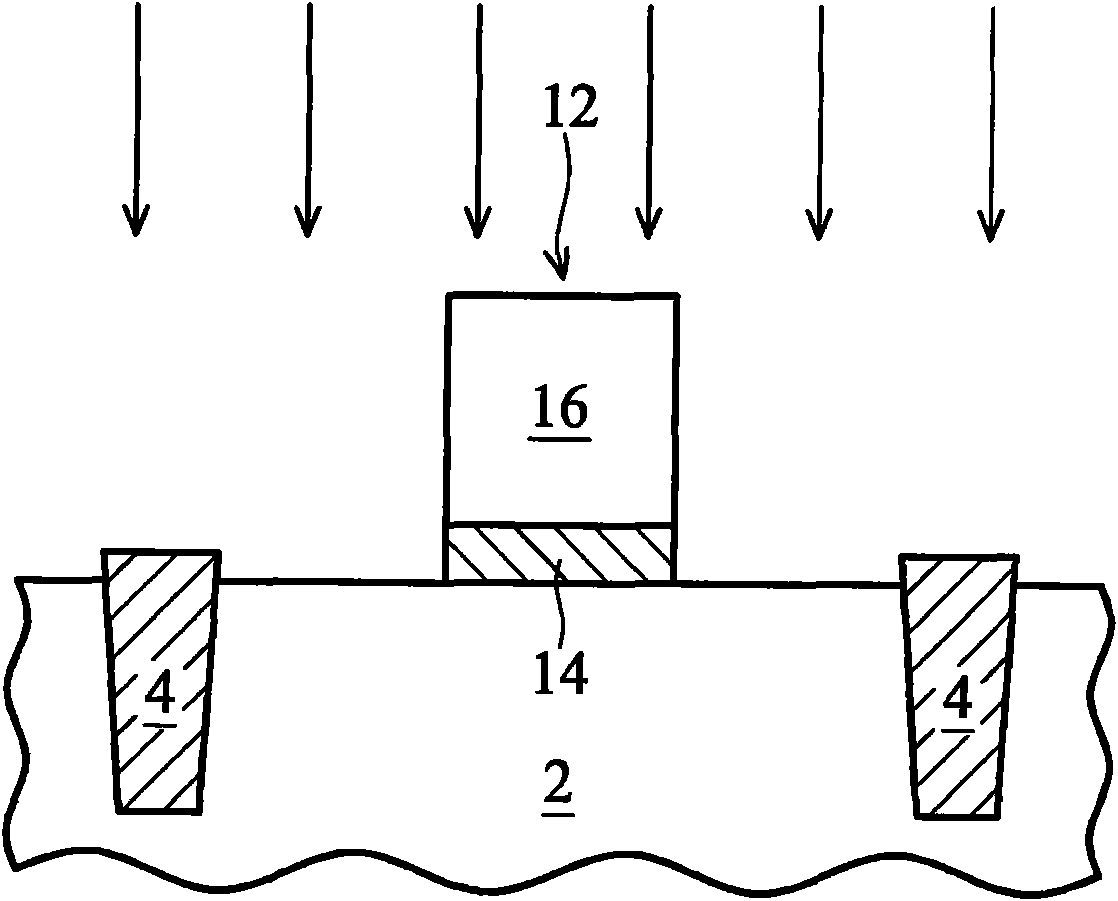

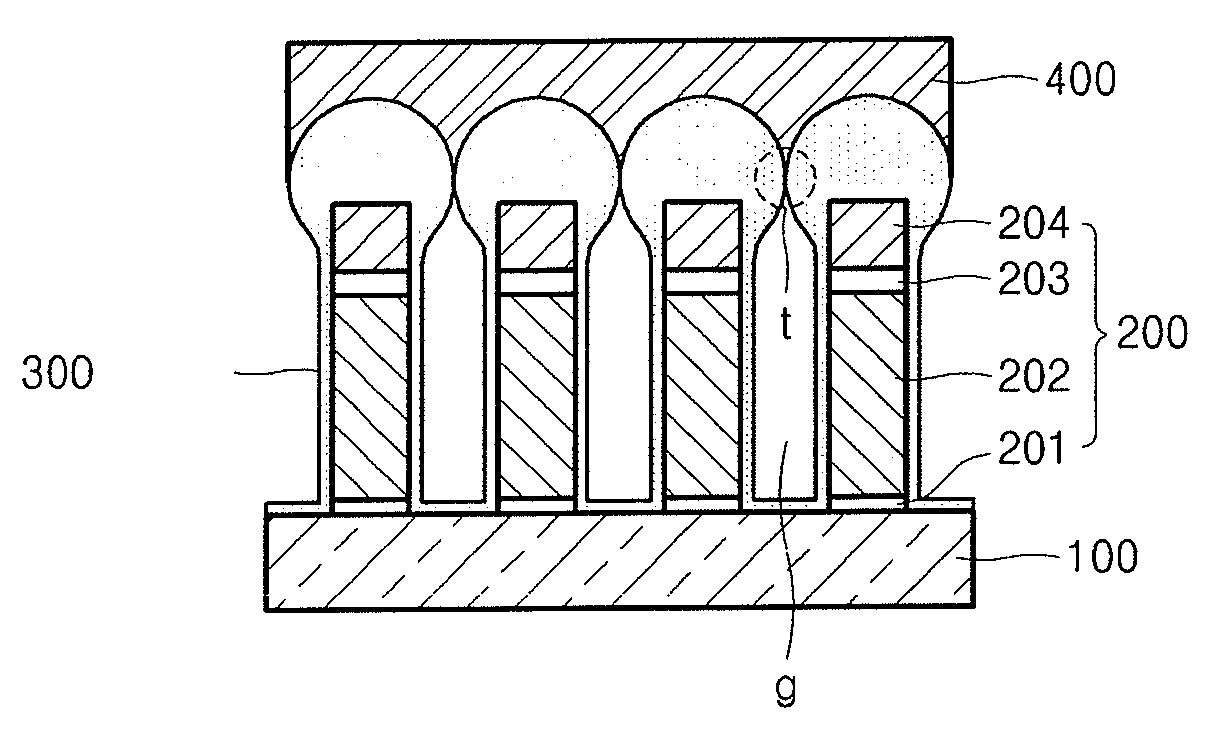

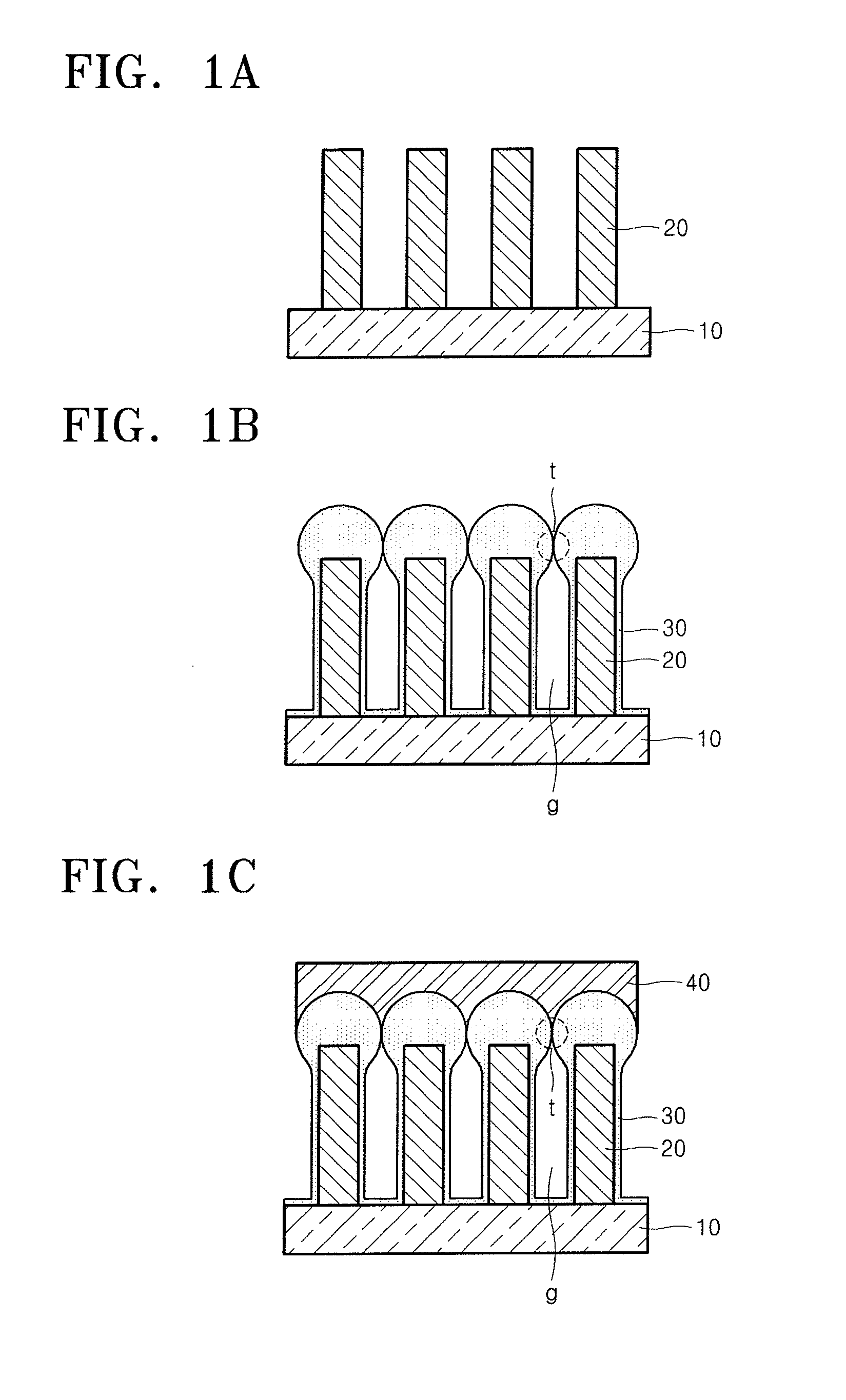

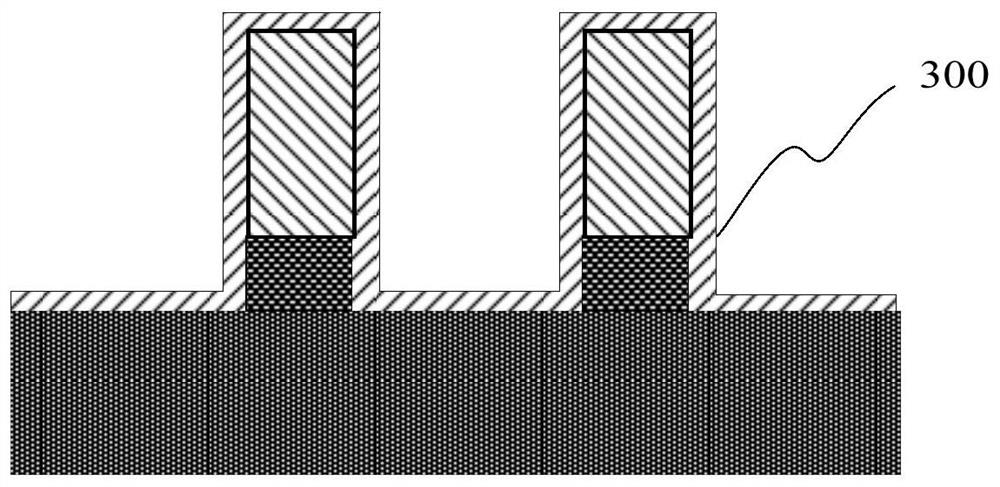

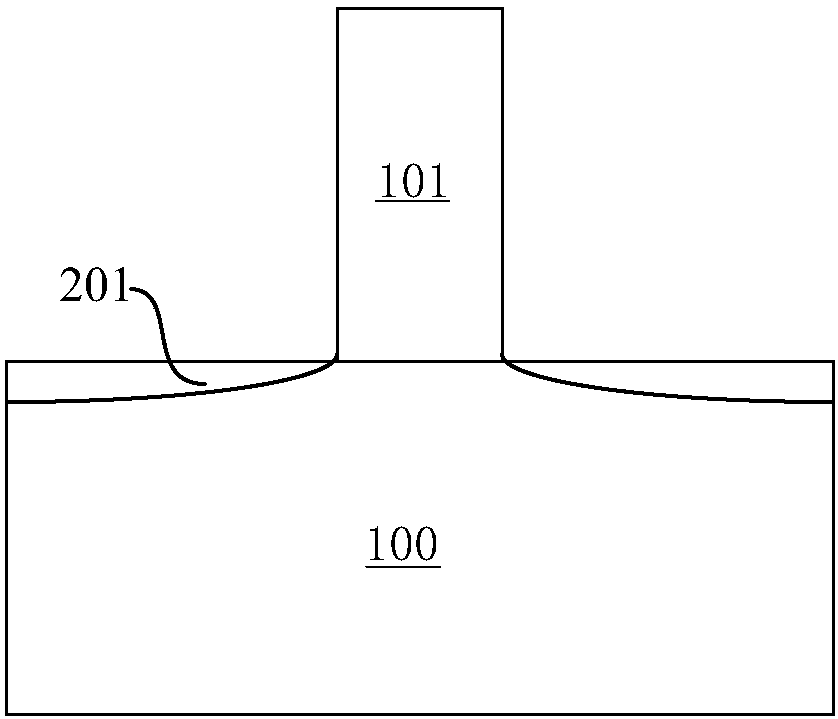

Method of fabricating a semiconductor device

ActiveUS8129264B2Reduce capacitive coupling effectsReduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceThermal chemical vapor deposition

A method of forming a dielectric layer having an air gap to isolate adjacent wirings or a gate stack of the semiconductor device is provided. A method of fabricating a semiconductor device includes providing a semiconductor substrate on which a plurality of wirings are formed adjacent to one another and forming a dielectric layer filling an upper portion of a space between the adjacent wirings to form air gaps by a thermal chemical vapor deposition method.

Owner:SAMSUNG ELECTRONICS CO LTD

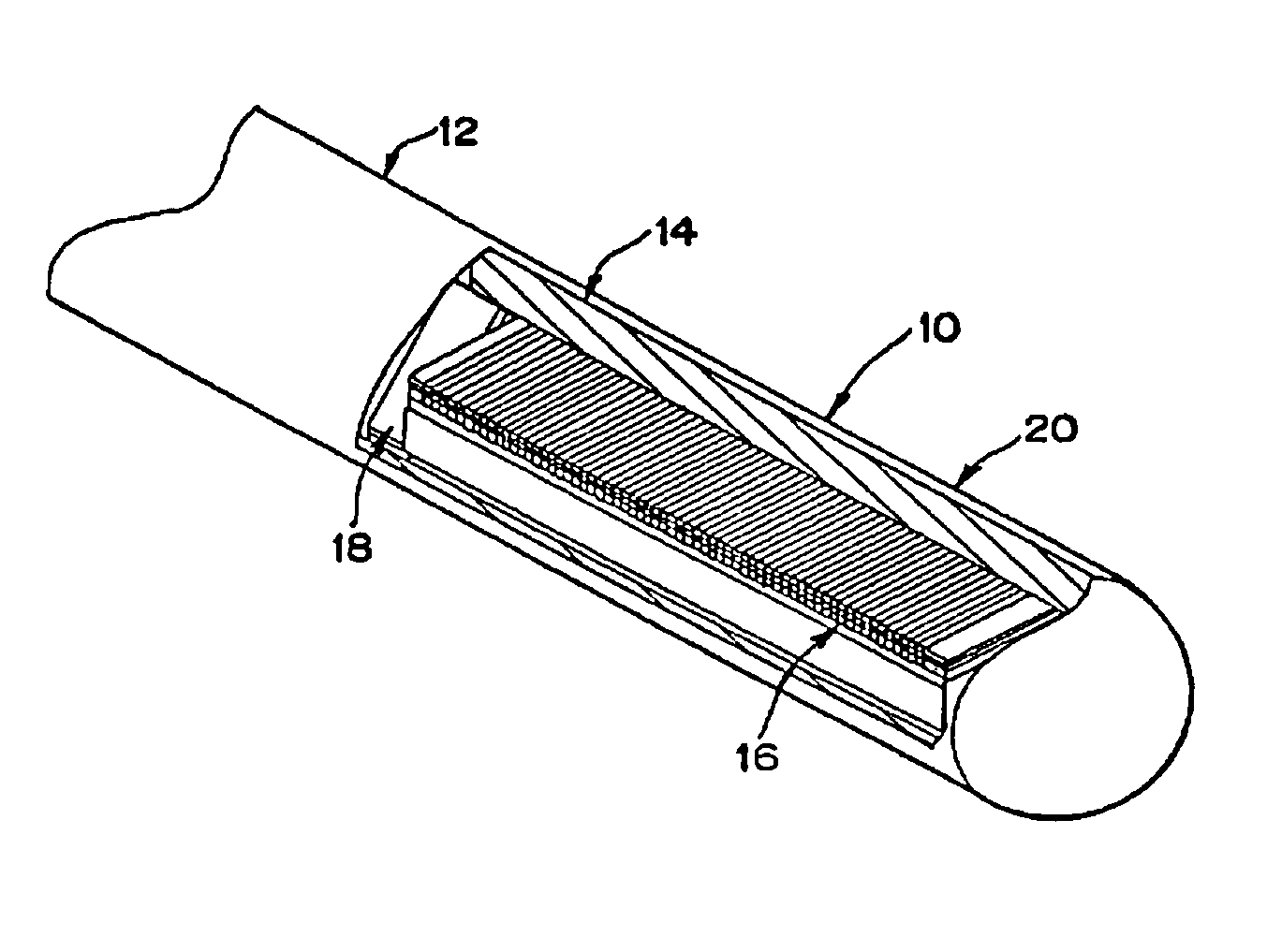

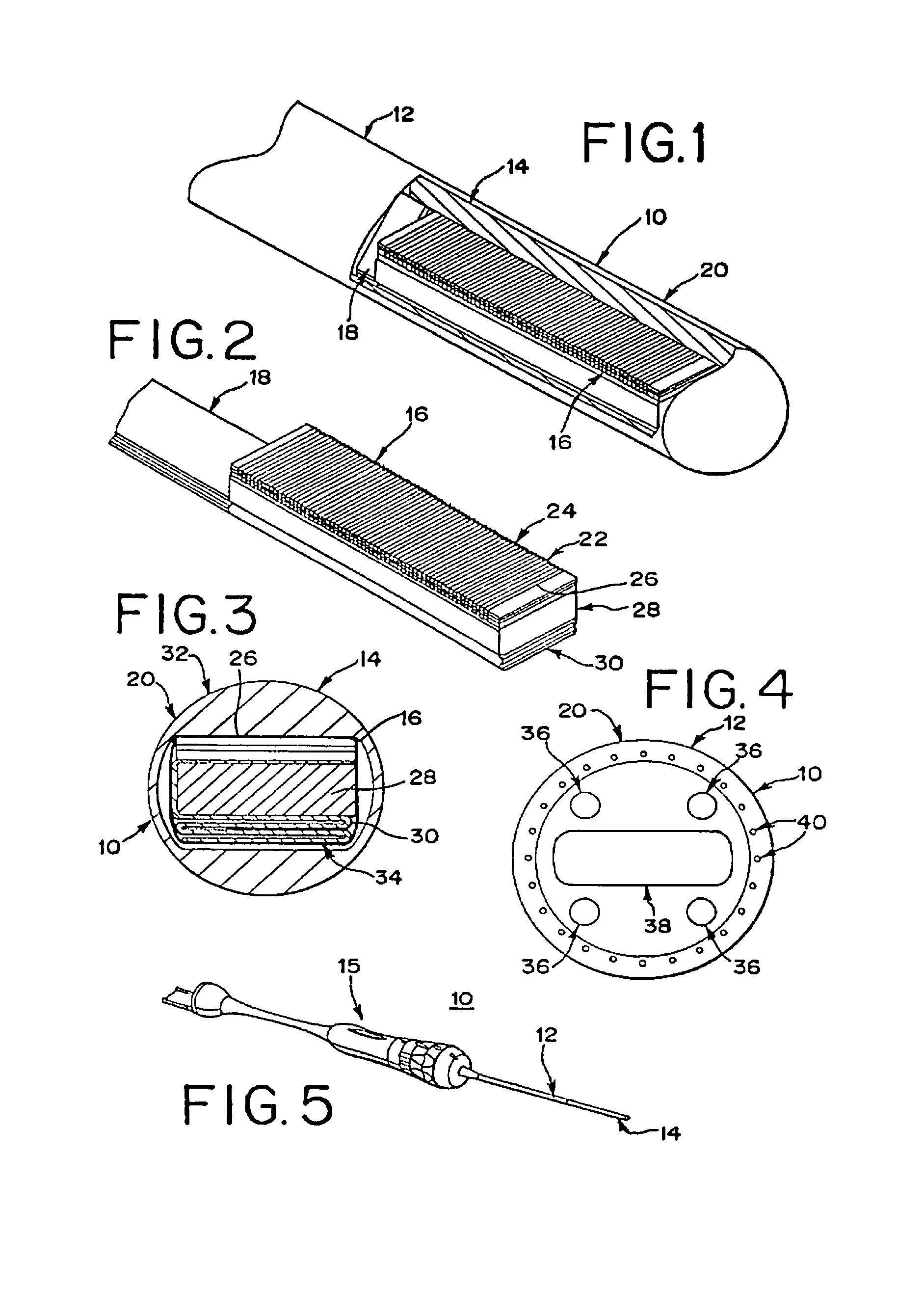

Medical diagnostic ultrasound catheter with dielectric isolation

InactiveUS7232433B1Improved dielectric withstand strengthReduce riskUltrasonic/sonic/infrasonic diagnosticsMulti-lumen catheterPolyesterAcoustic energy

Medical diagnostic ultrasound catheters are provided with improved materials for dielectric withstand strength. In one aspect, the catheter includes a braid of non-conductive material. The non-conductive braid reduces the capacitive: coupling effects and allows smaller catheters or a greater number of conductors. The non-conductive braid provides both compressive and tensile strength to transmit the torque applied to the catheter. The non-conductive braid also allows fusing of components while decreasing the risk of defective manufacture. In another aspect, a dielectric film, such as a polyester film, is positioned between the transducer and any lens or window. The dielectric film allows thinner window lenses to be used, allowing smaller catheters or larger transducers. The dielectric film may also increase the sensitivity of the transducer to acoustic energy. The dielectric film prevents the lens or window material from filling kerfs in the transducer, which may eliminate the need for filling the kerfs of the transducer.

Owner:SIEMENS MEDICAL SOLUTIONS USA INC

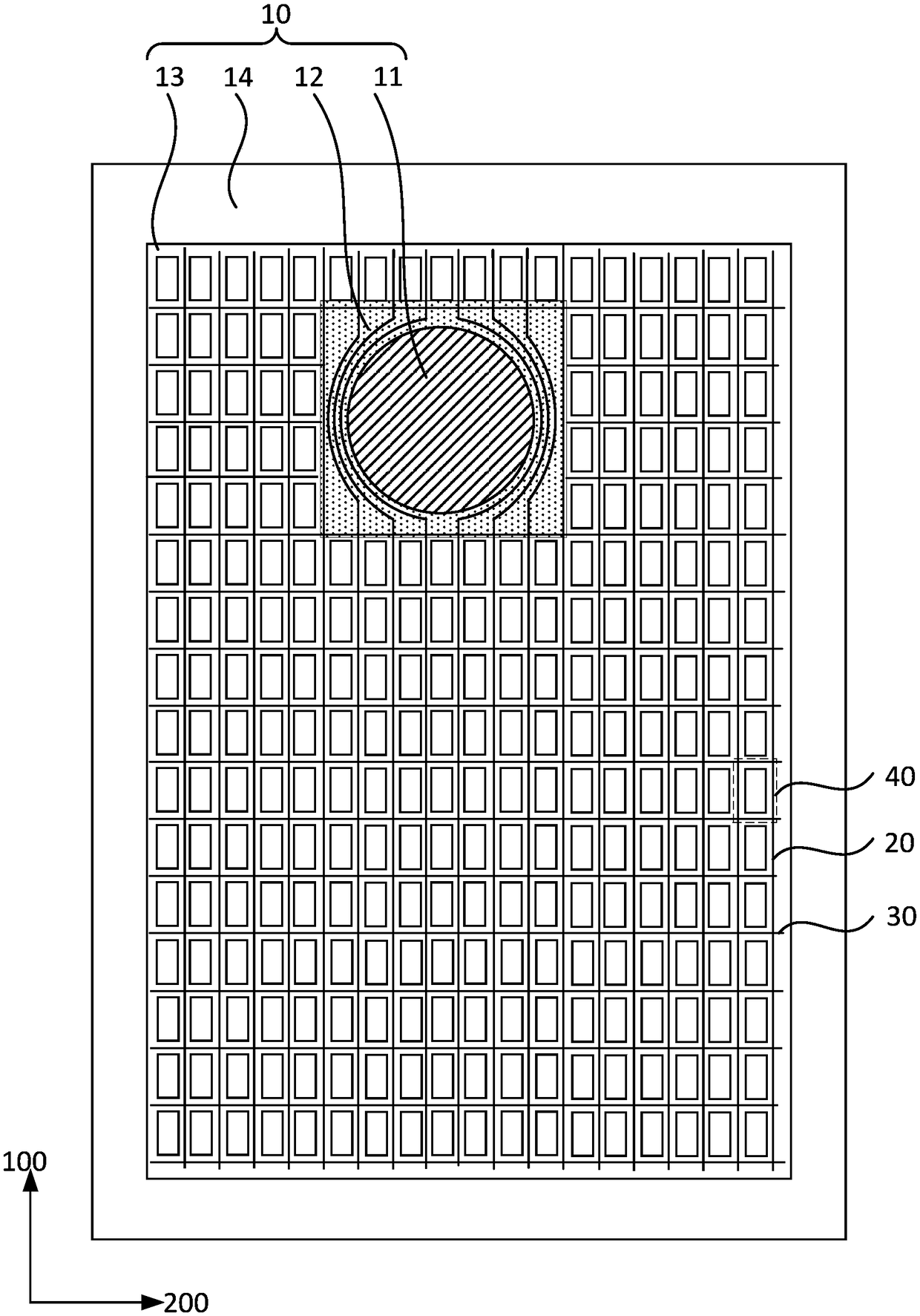

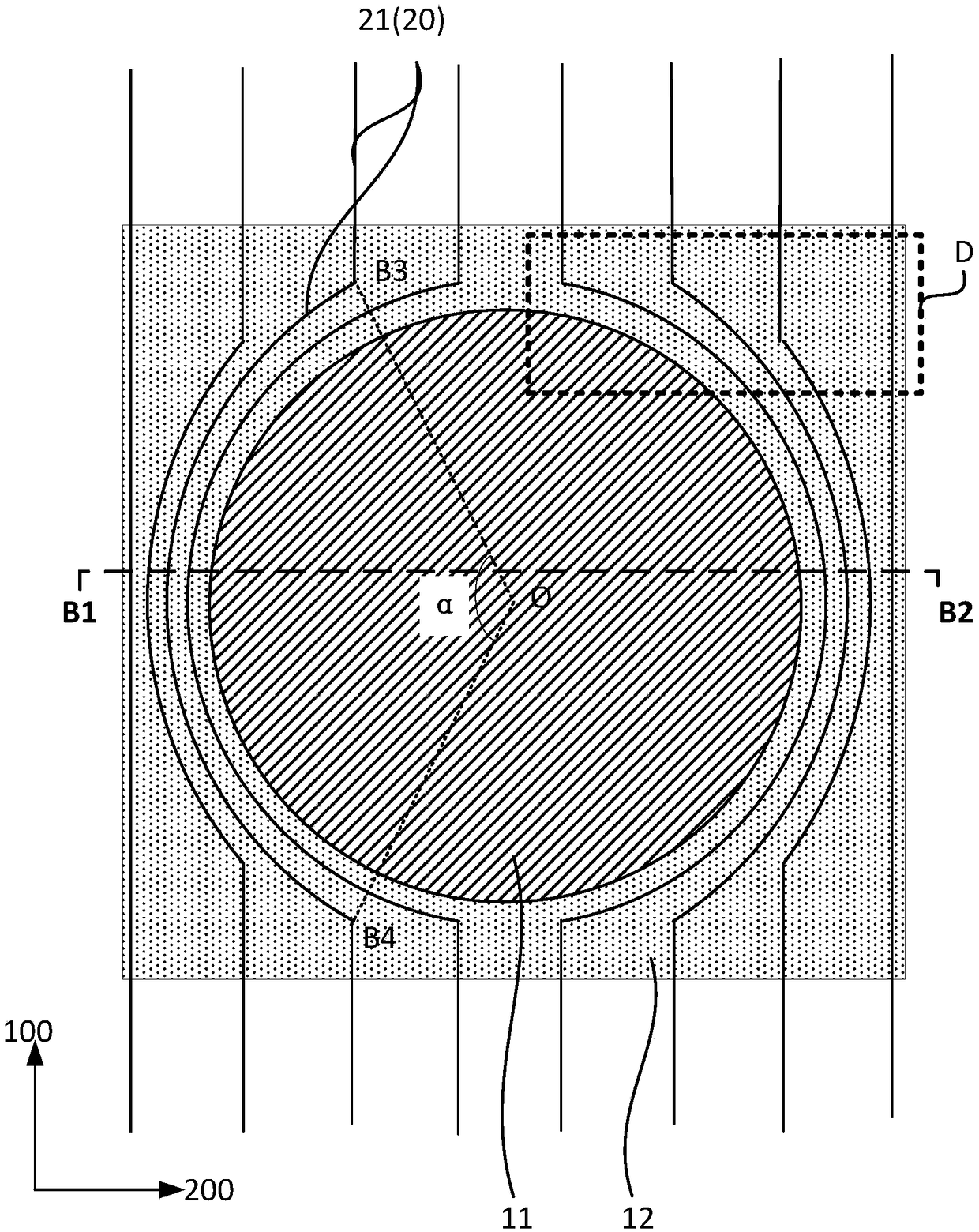

Display panel and display device

ActiveCN108806513AReduce areaNormal installation and useIdentification meansDisplay deviceLarge size

The invention discloses a display panel and a display device. A substrate of the display panel includes a device setting area, a first non-display area, a display area and a second non-display area, wherein the first non-display area surrounds the device setting area, and the display area surrounds the first non-display area; a plurality of data lines formed on the substrate; and a first metal layer, a second metal layer and a third metal layer formed on the substrate, all data lines include first trace parts which are located in the second metal layer; part of the data lines passing through the first non-display area also include first jumper parts, all of which are located in the third metal layer; or all first jumper parts are located in the first metal layer; or part of the first jumper parts are located in the third metal layer and other first jumper parts are located in the first metal layer. The display panel has the advantage that devices of large sizes can be normally installed and used when ensuring relatively high display panel screen ratio.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

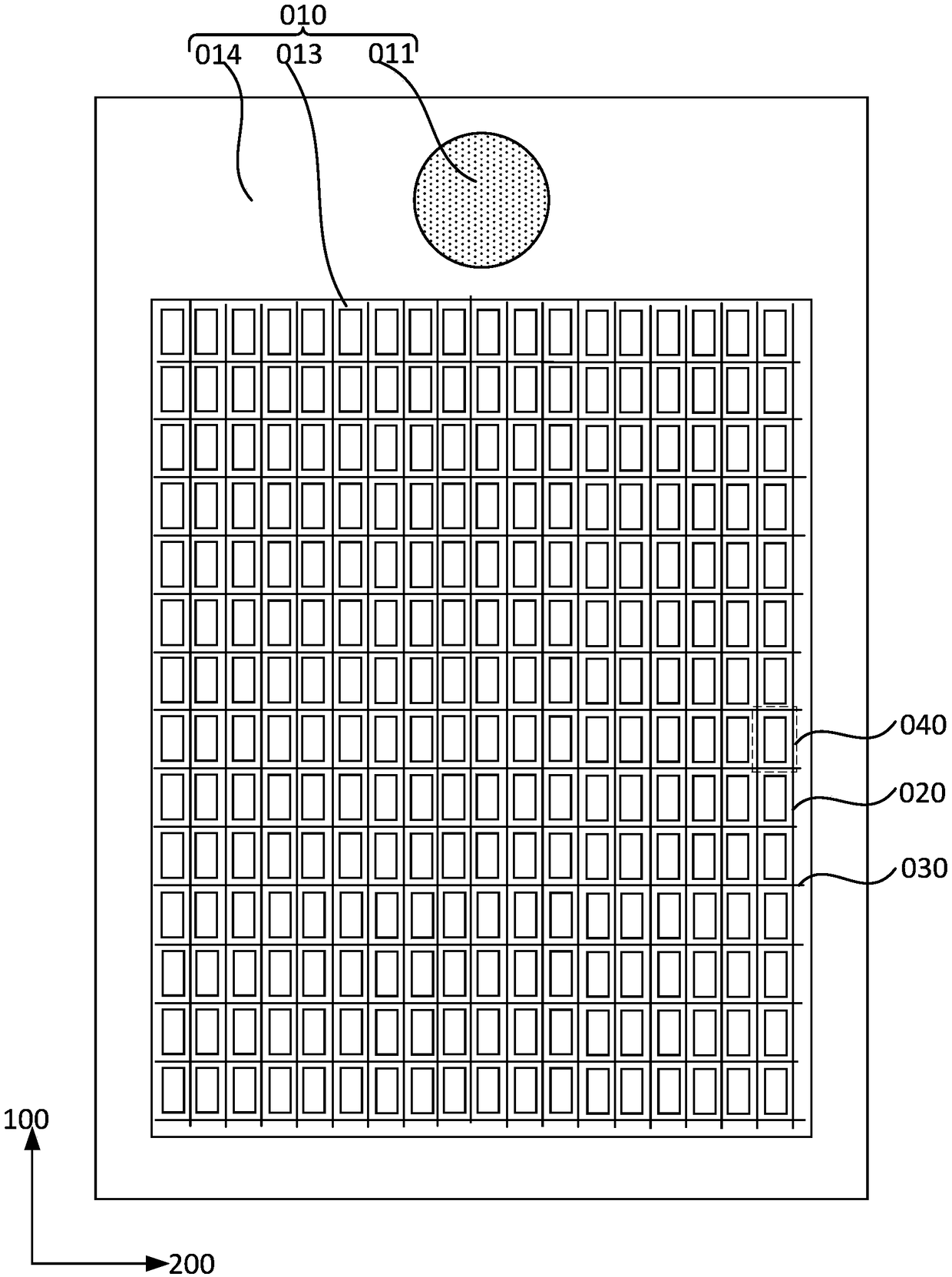

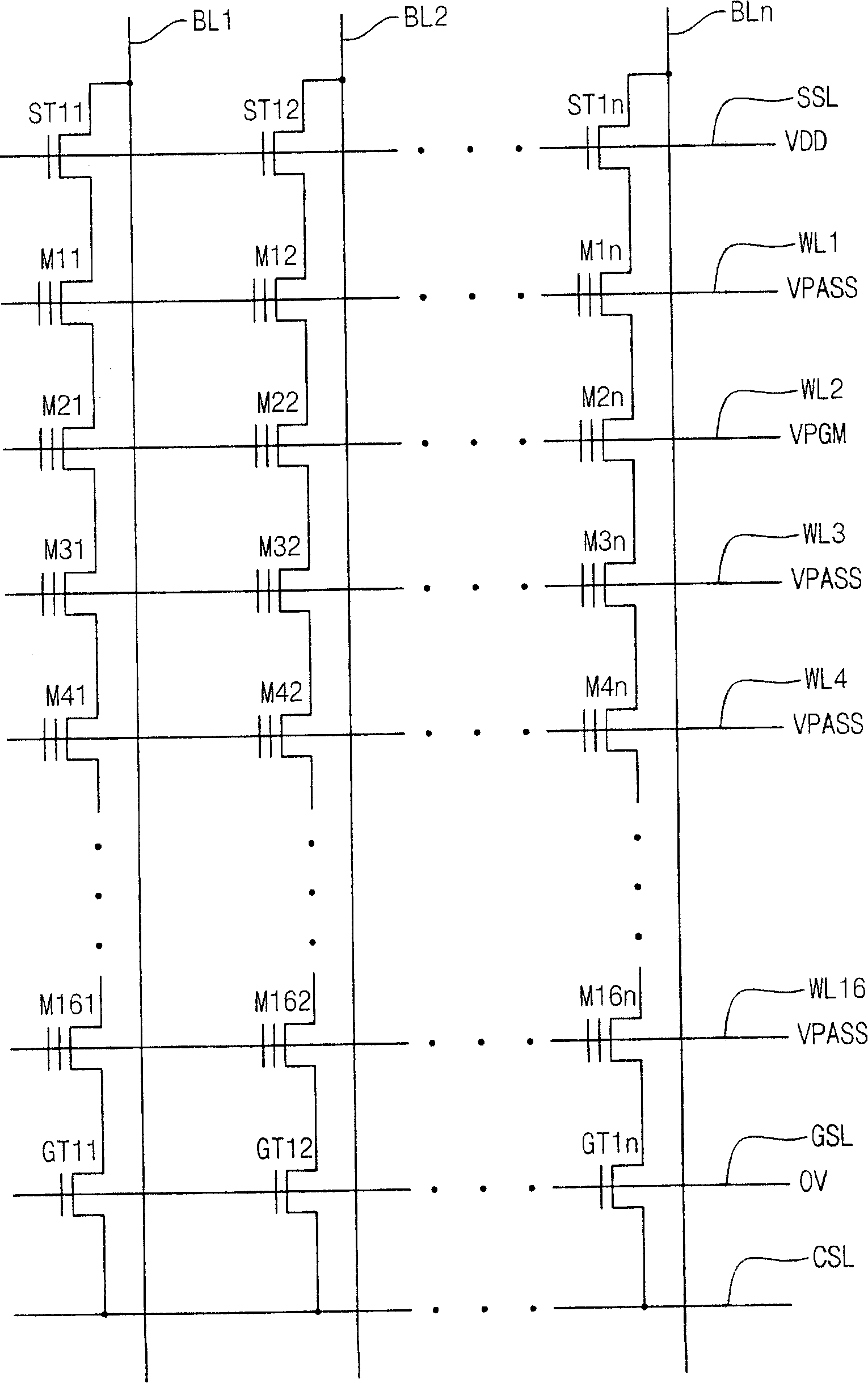

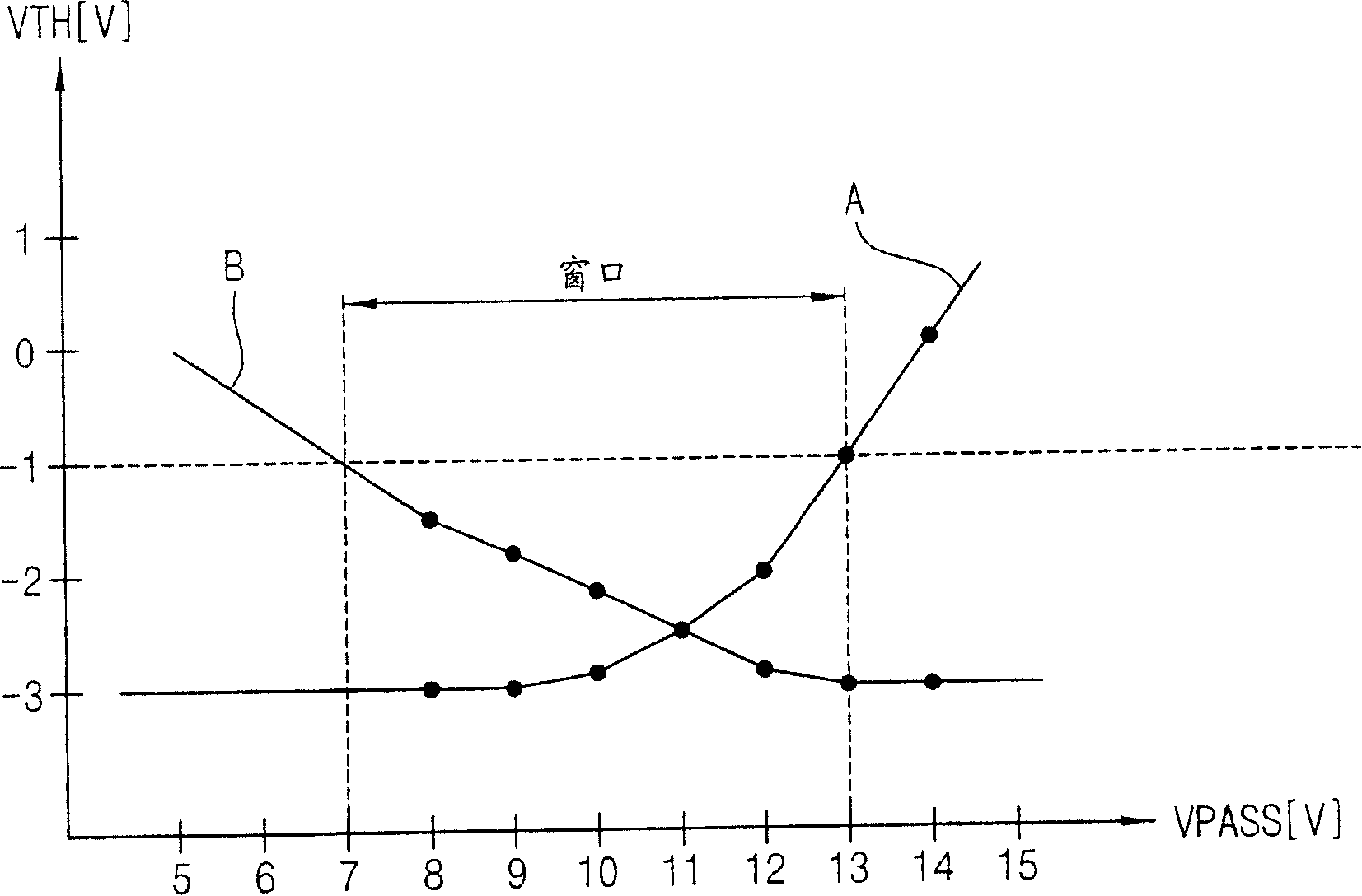

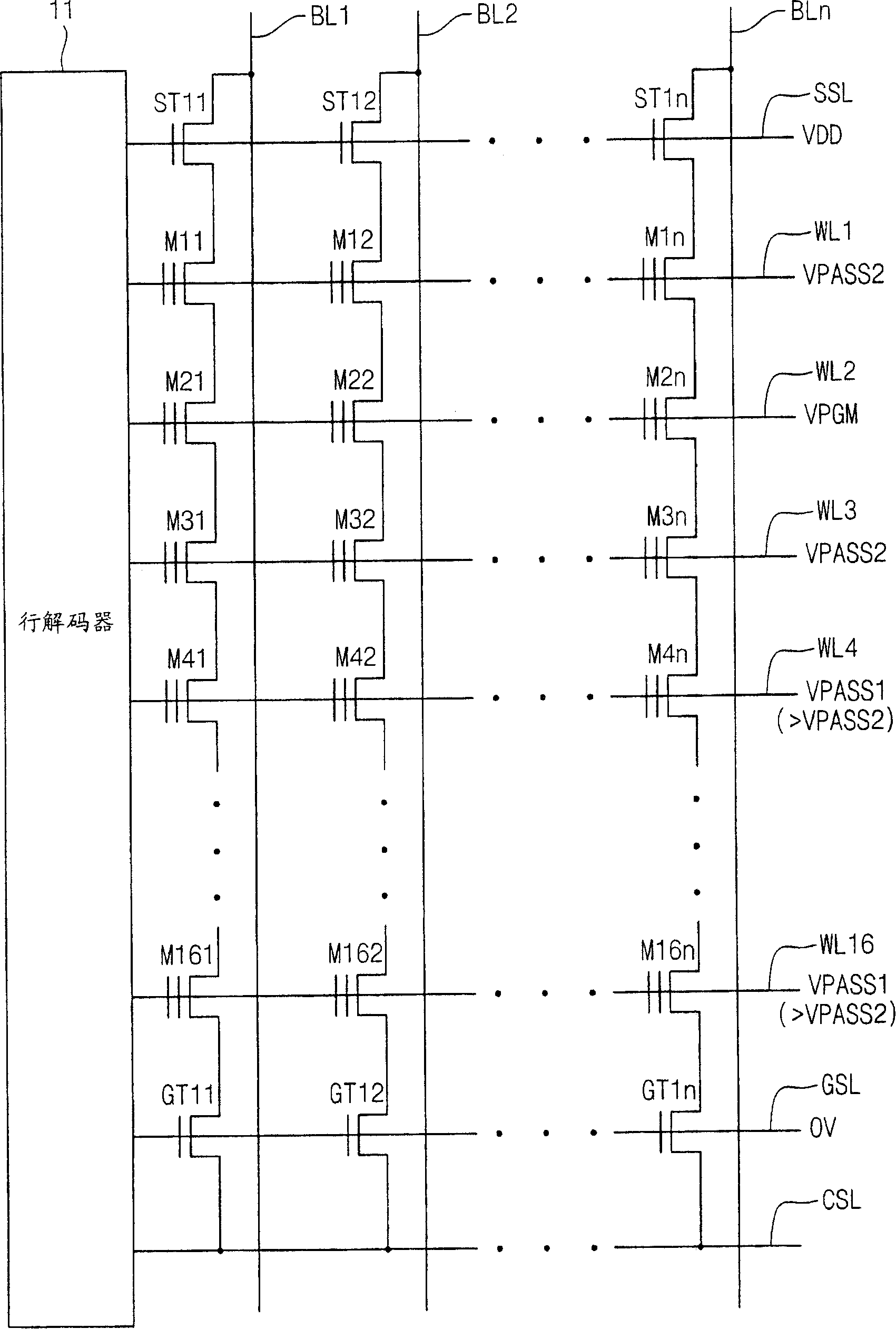

Non-volatile memory devices and methods of programming the same

ActiveCN101162609AReduce capacitive coupling effectsRead-only memoriesDigital storageSemiconductor memoryNon-volatile memory

A non-volatile semiconductor memory device and method of programming the non-volatile semiconductor memory device are disclosed. The non-volatile semiconductor memory device includes a selected word-line and unselected word-lines including at least one unselected word-line to which a first voltage signal is applied. The selected word-line is coupled to a selected memory transistor and receives a program voltage signal in response to a program voltage enable signal. A first voltage signal is applied to the at least one unselected word-line. The first voltage signal has a voltage level of a reduced pass voltage signal before the program voltage enable signal is activated and has a voltage level of a pass voltage signal while the program voltage enable signal is activated.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of fabricating a semiconductor device

ActiveUS20090042383A1Improve reliabilityEnhanced Vapor DepositionSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialThermal chemical vapor deposition

A method of forming a dielectric layer having an air gap to isolate adjacent wirings or a gate stack of the semiconductor device is provided. A method of fabricating a semiconductor device includes providing a semiconductor substrate on which a plurality of wirings are formed adjacent to one another and forming a dielectric layer filling an upper portion of a space between the adjacent wirings to form air gaps by a thermal chemical vapor deposition method.

Owner:SAMSUNG ELECTRONICS CO LTD

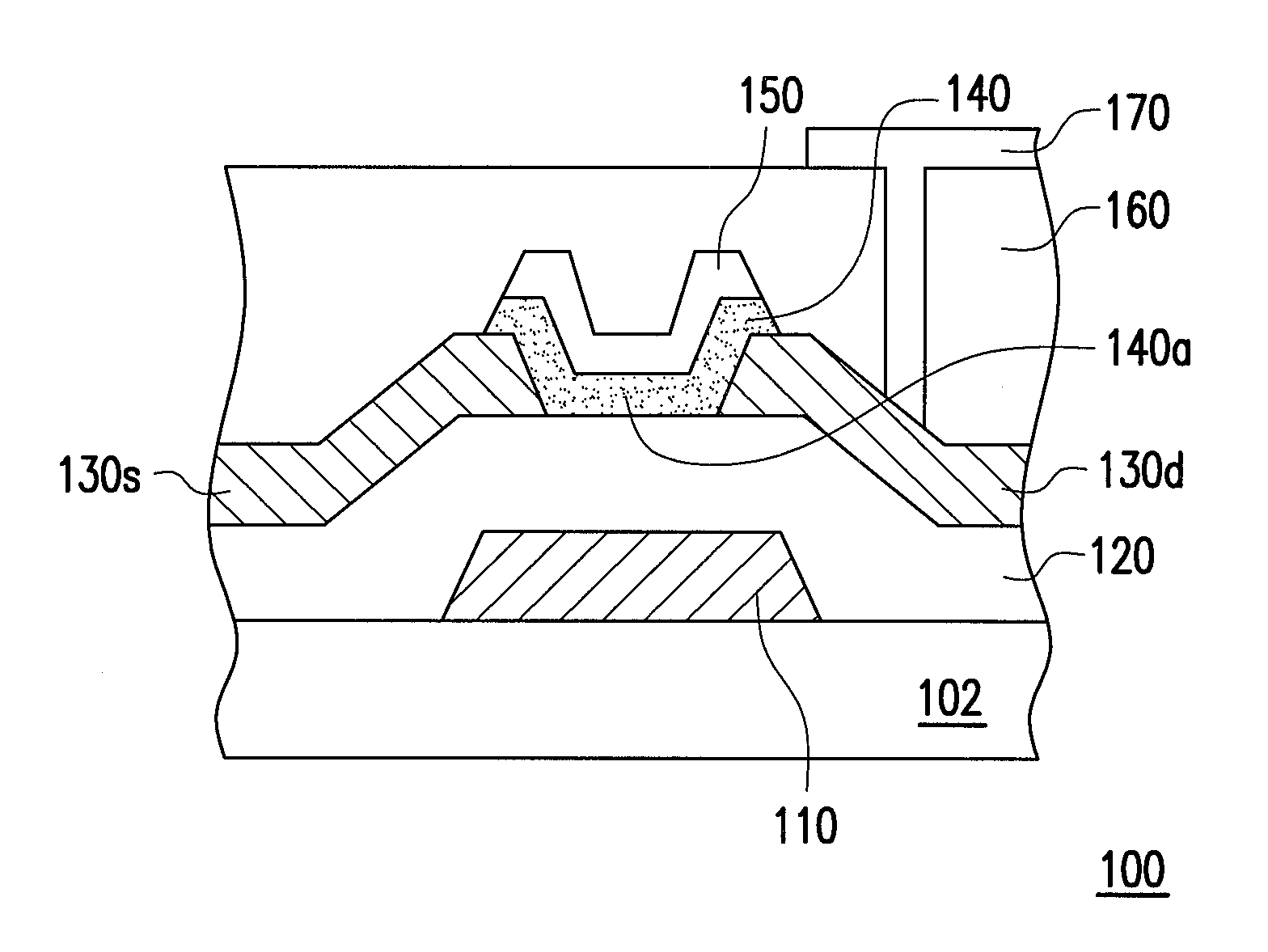

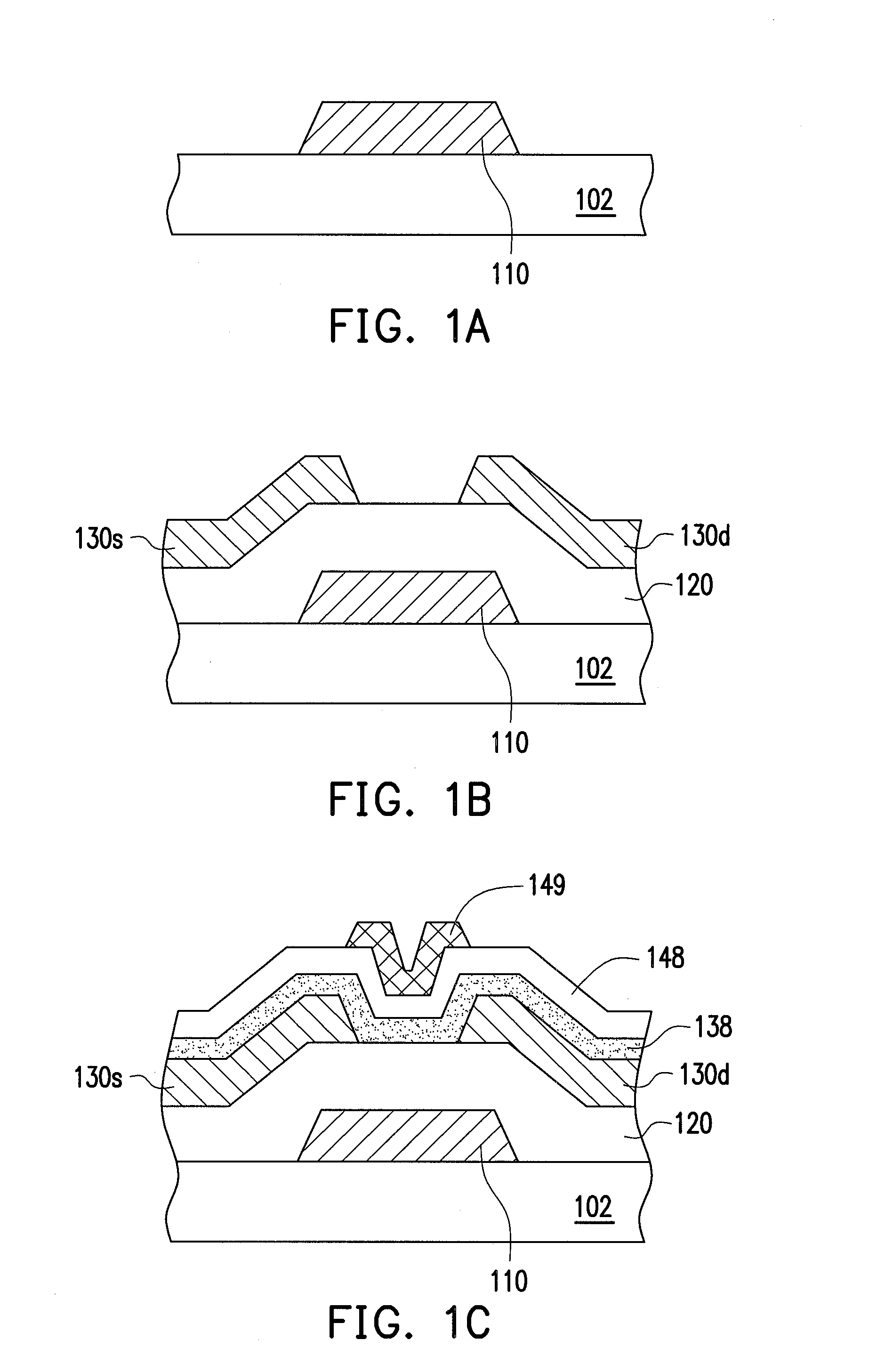

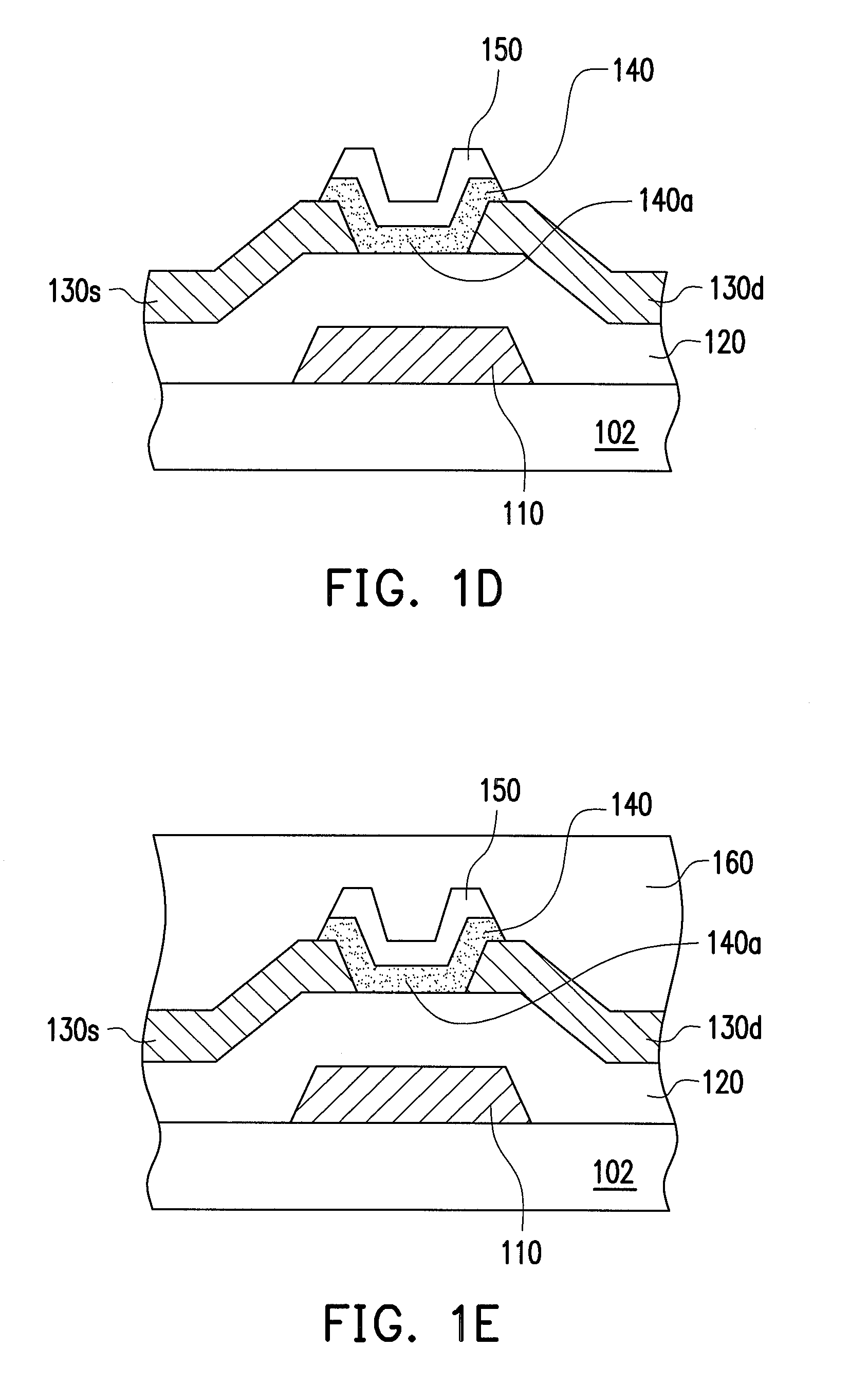

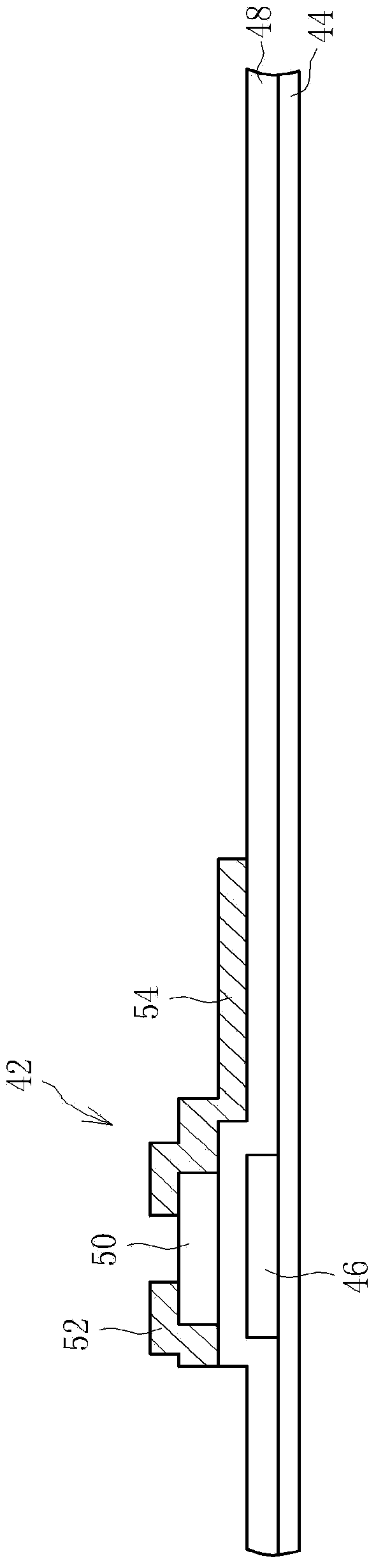

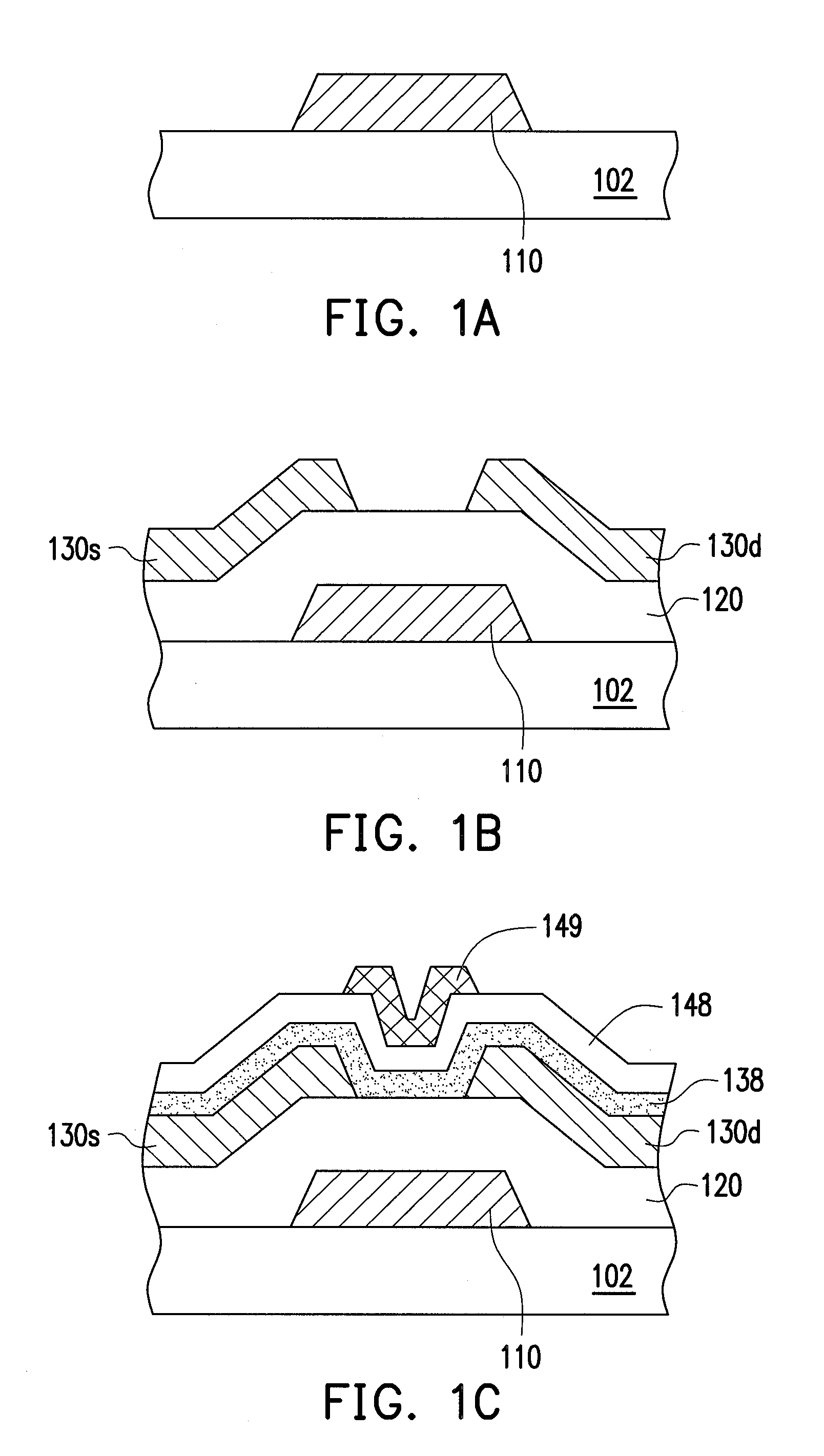

Thin film transistor and fabrication method thereof

ActiveUS20120267621A1Improve stabilityShorten production timeTransistorSemiconductor/solid-state device manufacturingMetalTransistor

A thin film transistor is provided. The thin film transistor includes a substrate, a gate, a gate insulating layer, a source and a drain, a channel layer, and first and second patterned passivation layers. The gate is disposed on the substrate. The gate insulating layer is disposed on the gate. The source and the drain are disposed on the gate insulating layer. The channel layer is disposed above or under the source and the drain, wherein a portion of the channel layer is exposed between the source and the drain. The first patterned passivation layer is disposed on the portion of the channel layer, wherein the first patterned passivation layer includes metal oxide, and the first patterned passivation layer has a thickness ranging from 50 angstroms to 300 angstroms. The second patterned passivation layer covers the first patterned passivation layer, the gate insulating layer, and the source and the drain.

Owner:AU OPTRONICS CORP

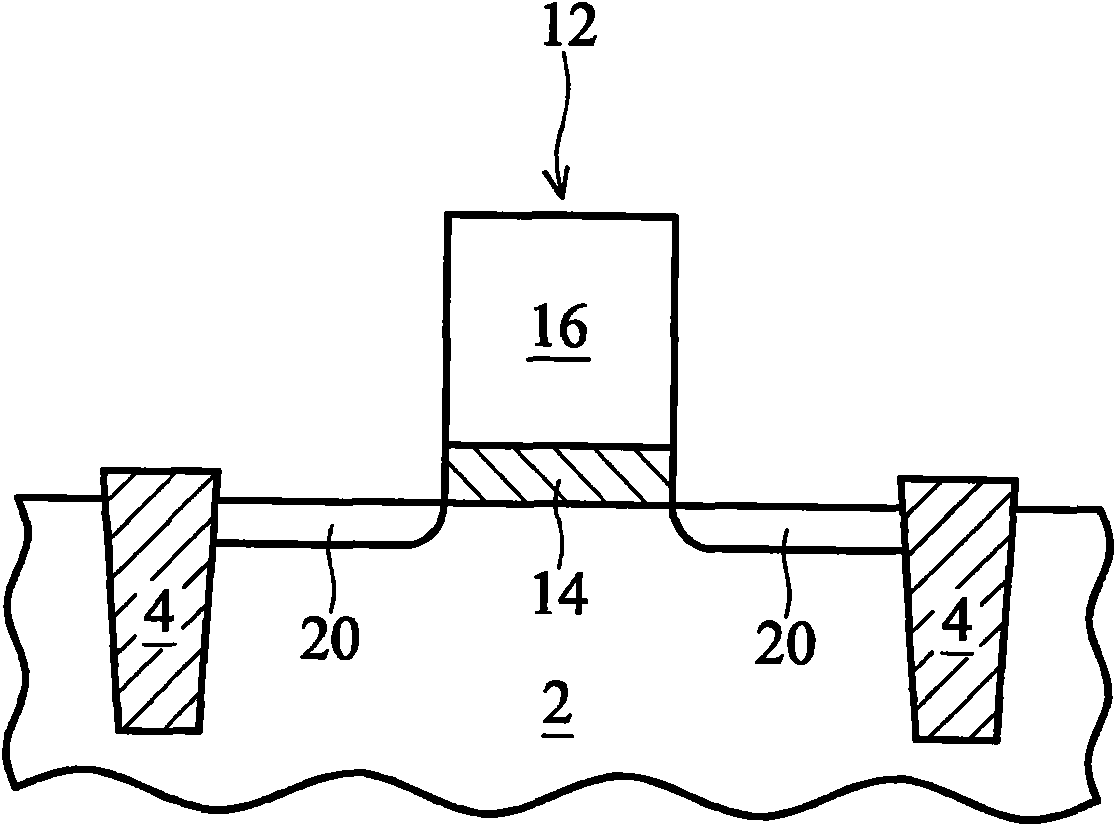

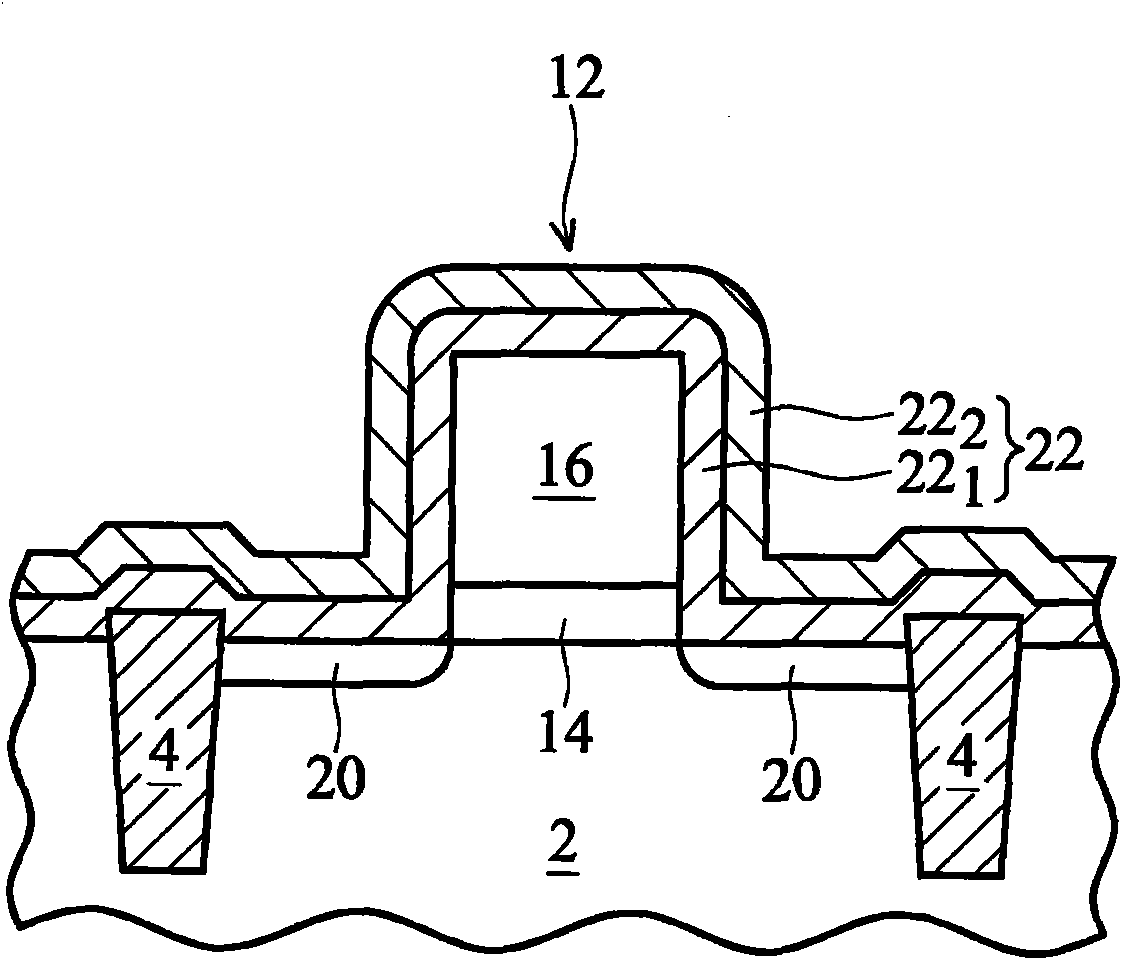

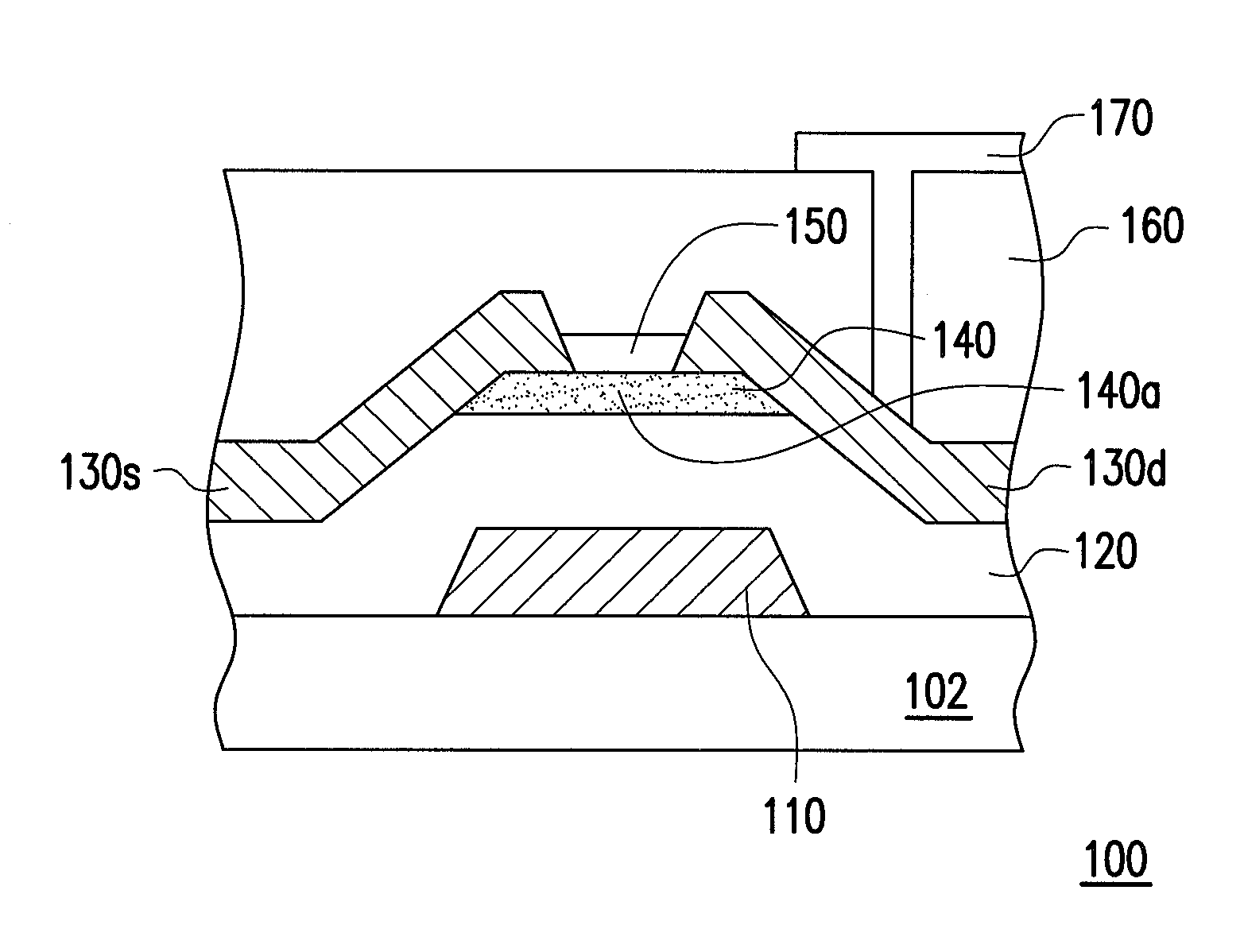

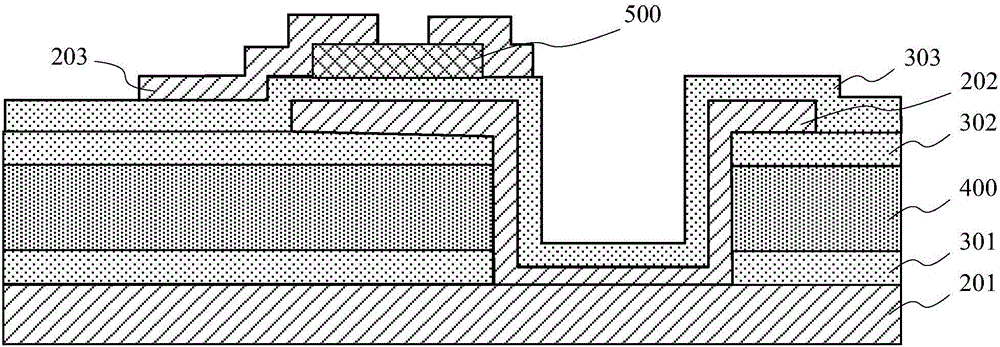

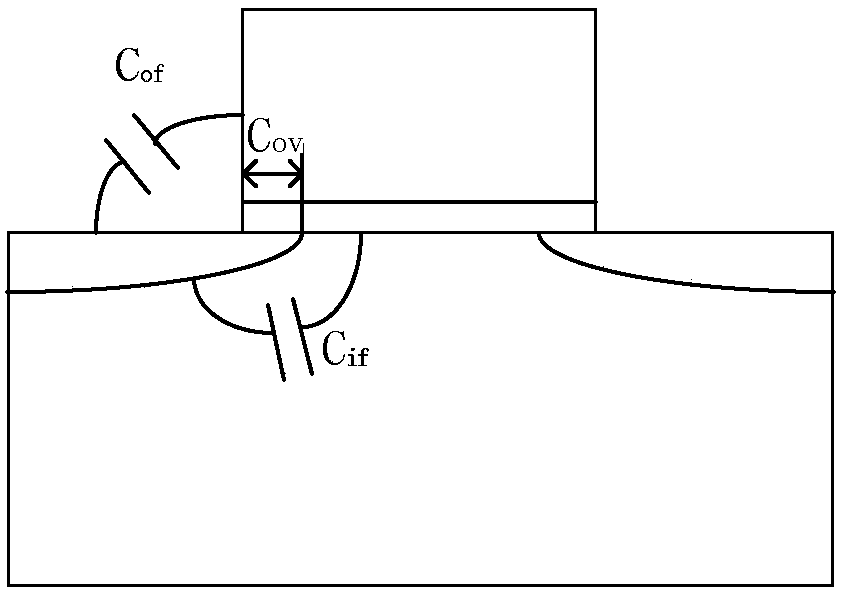

Semiconductor device

ActiveCN102214693AReduce capacitive coupling effectsSemiconductor devicesDielectricPower semiconductor device

The invention provides a semiconductor device, which comprises a substrate having shallow trench isolation and source / drain regions located therein, a gate stack located on the substrate between the source / drain regions, a first gate spacer on the sidewall of the gate stack, and a second gate spacer on the sidewall of the first gate spacer. The dielectric constant of the first gate spacer is smaller than the dielectric constant of the second gate spacer. The dielectric constant of gate spacers, that is the capacitive coupling between the LDD regions and the gate, is reduced.

Owner:TAIWAN SEMICON MFG CO LTD

Touch display device and touch display

InactiveCN110471558AImprove touch sensitivityImprove qualityOptical light guidesNon-linear opticsCapacitive couplingControl signal

The invention provides a touch display device and a touch display. The touch display device comprises a touch electrode and a backlight module opposite to the touch electrode. The backlight module comprises a backlight film material and a backlight iron frame for supporting the backlight film material. The backlight film material is arranged between the touch electrode and the backlight iron frame. The touch control electrodes and the backlight iron frame are electrically connected with a touch control signal end together. The touch control signal end is used for transmitting touch control signals to the touch control electrodes and the backlight iron frame. The touch electrodes and the backlight iron frame receive the same touch signals, so that the capacitive coupling effect between thetouch electrodes and the touch iron frame is eliminated. The touch sensitivity is improved. The vibration noise of the backlight film material is eliminated. The touch display provided by the invention comprises the touch display device, so that the touch display has the advantages of the touch display device.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

TFT (Thin Film Transistor) and display device

InactiveCN105895706AEasy to shapeReduce parasitic capacitanceTransistorNon-linear opticsTablet computerInsulation layer

The invention discloses a TFT (Thin Film Transistor) and a display device, belongs to the technical field of display and can reduce stray capacitance between a first metal layer and a second metal layer and increase the display quality of an LCD (Liquid Crystal Display). The TFT comprises a grid electrode, a grid electrode insulation layer, a semiconductor layer, a source electrode and a drain electrode, wherein the grid electrode insulation layer covers the grid electrode; the semiconductor layer is formed on the grid electrode insulation layer; the source electrode and the drain electrode are formed on the semiconductor layer; the semiconductor layer is provided with an extension part; a planar projection of the extension part exceeds the edge of the grid electrode, and the drain electrode covers the extension part. The TFT disclosed by the invention can be applied to high-PPI (Pixel Per Inch) display devices such as a mobile phone and a tablet computer.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Thin-film transistor array substrate

ActiveCN104347641AImprove electrical performanceHigh precisionSolid-state devicesNon-linear opticsInsulation layerScan line

Owner:HANNSTAR DISPLAY CORPORATION

Thin film transistor having a patterned passivation layer

ActiveUS8643006B2Improve stabilityShorten production timeTransistorSemiconductor/solid-state device manufacturingTransistorPhysics

Owner:AU OPTRONICS CORP

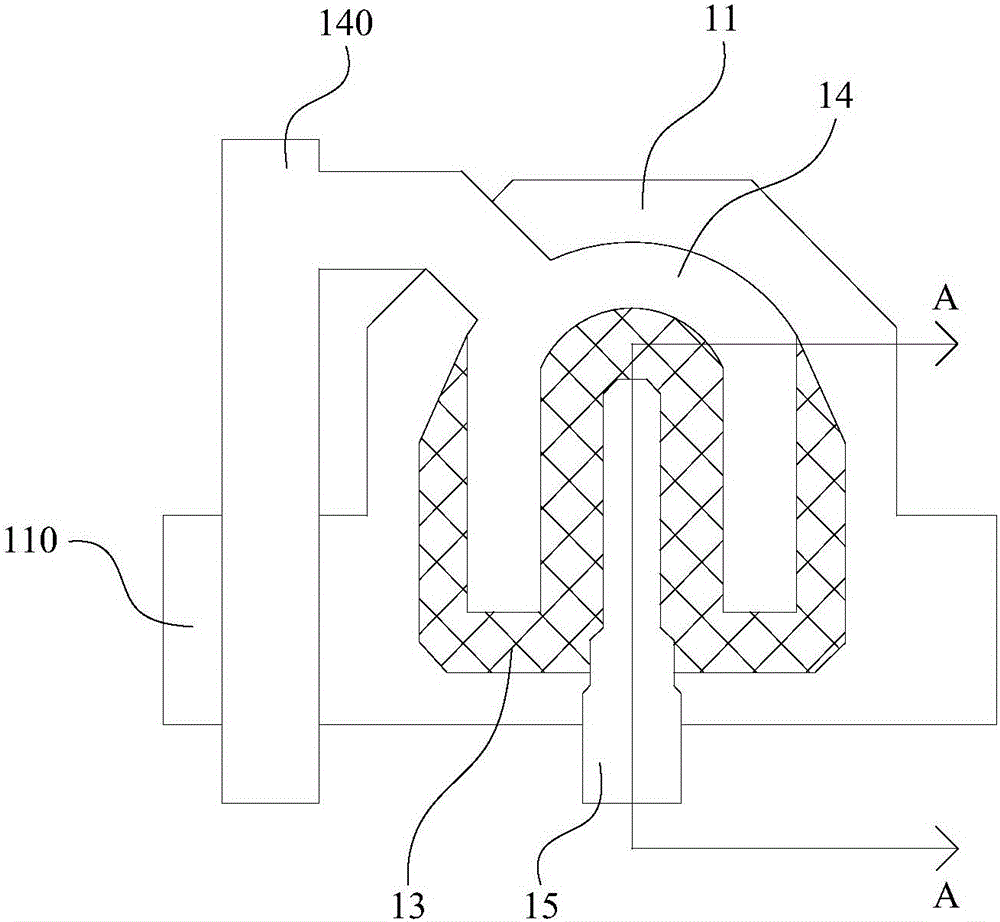

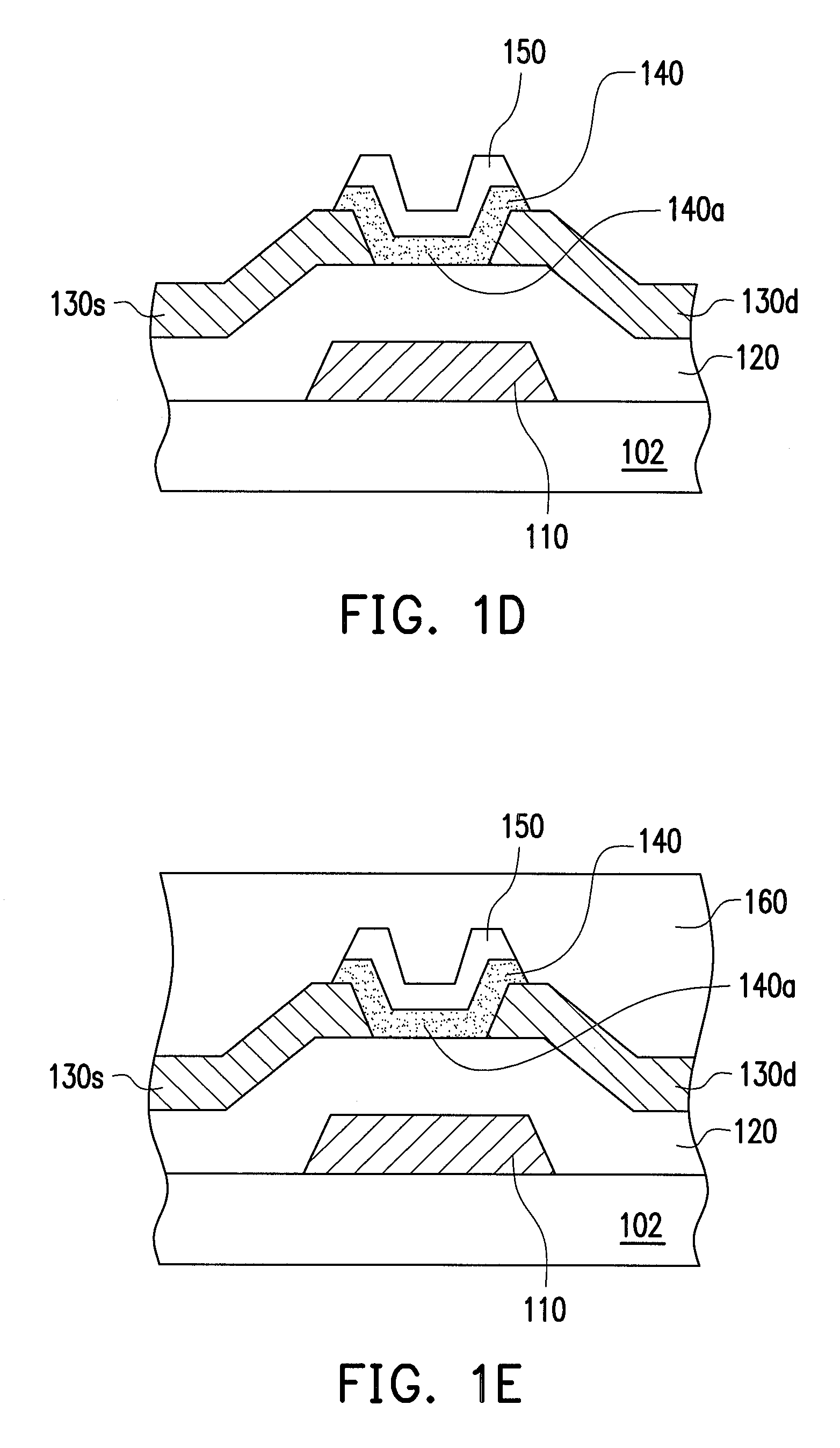

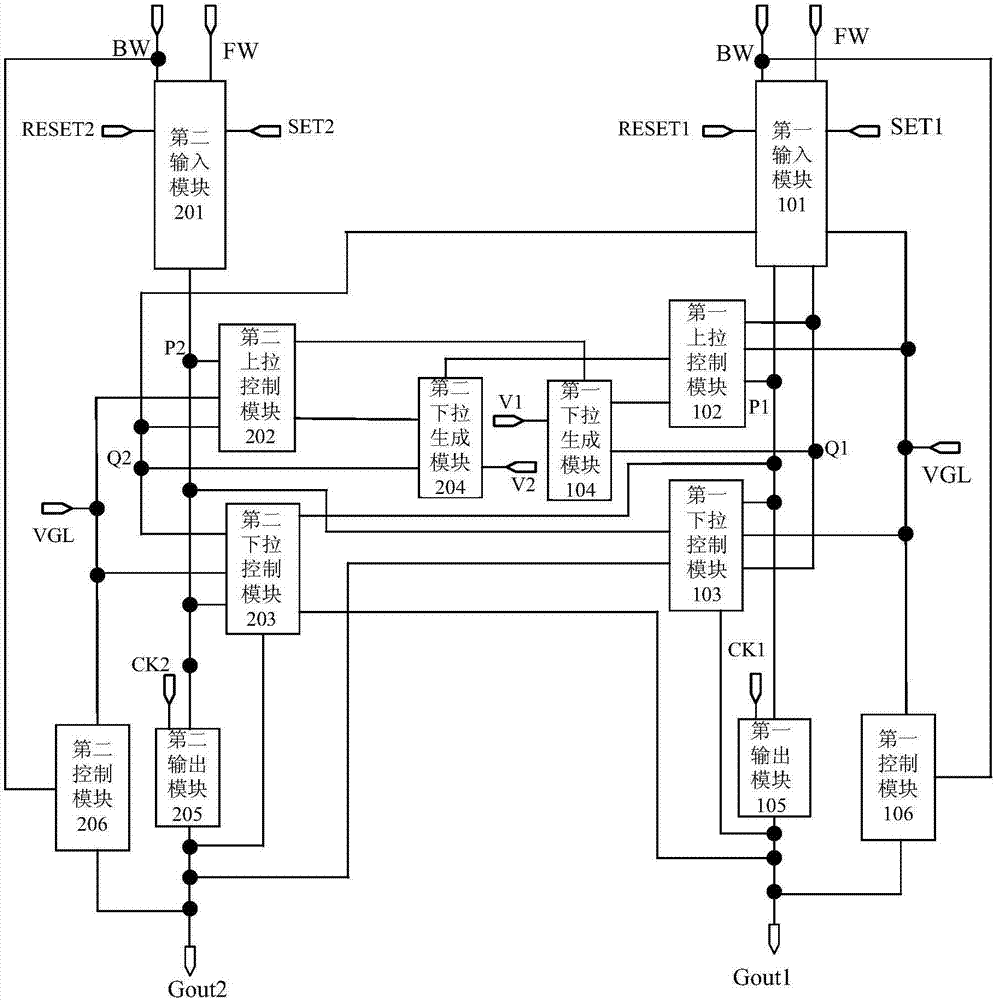

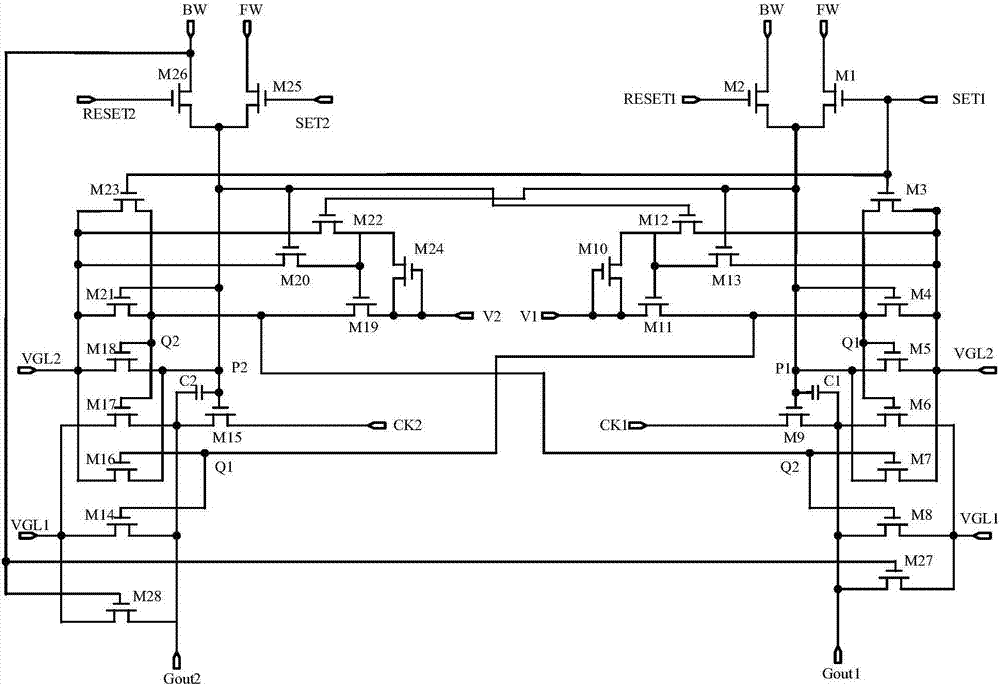

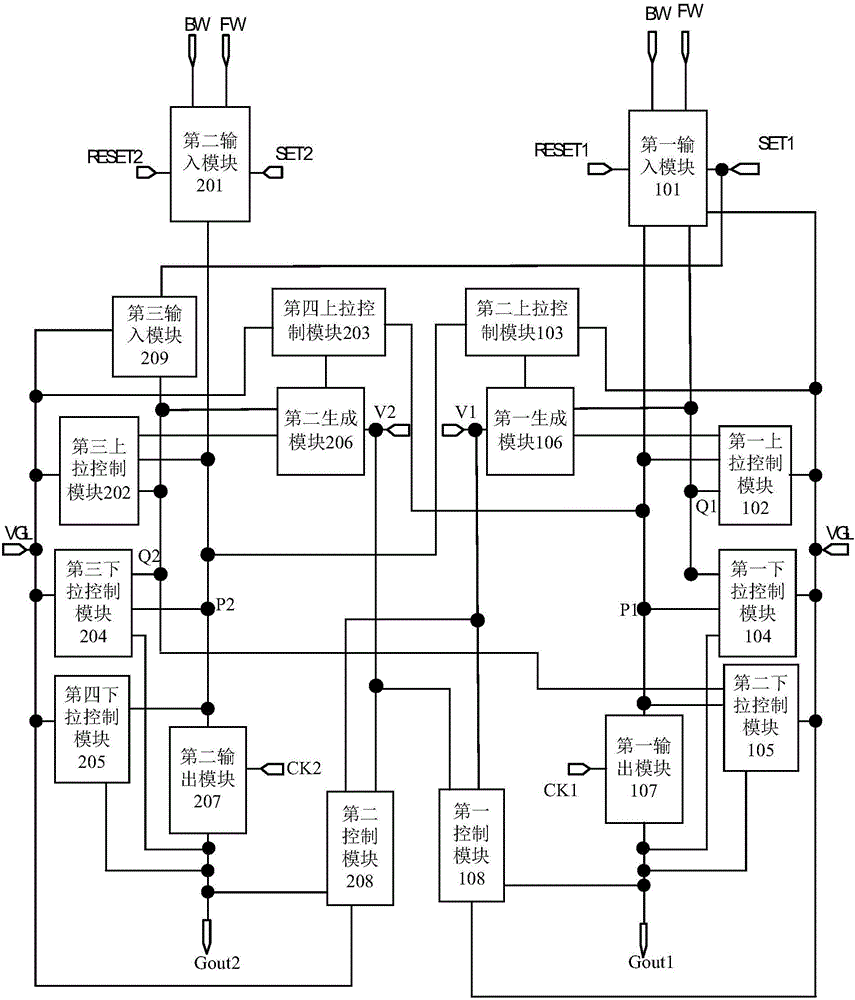

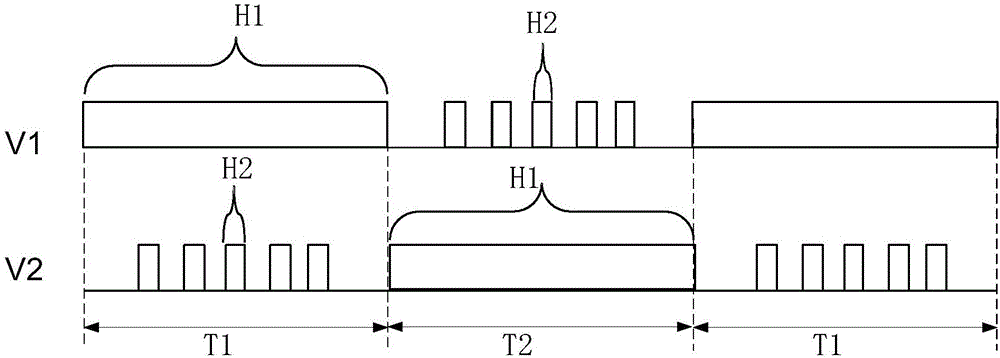

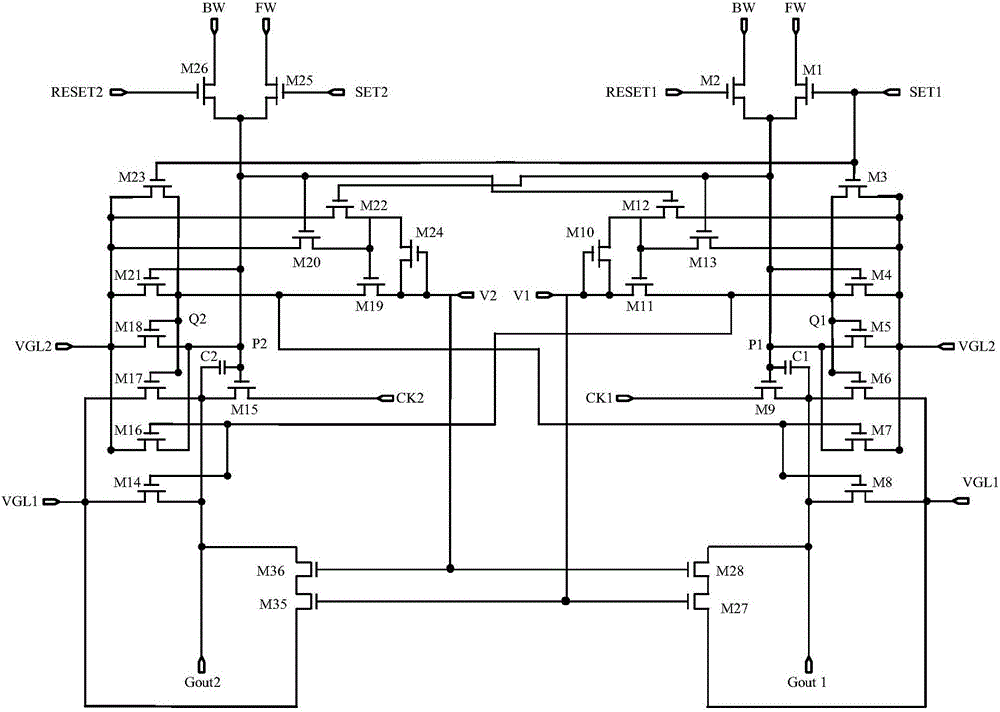

Grid driving circuit

InactiveCN107134247ANormal display functionReduce capacitive coupling effectsStatic indicating devicesInput/output processes for data processingCapacitanceCapacitive coupling

The invention discloses a grid driving circuit. In a display stage, in response to a low potential of a second voltage end, first and second control modules disconnect a third voltage end from a first output end; in a touch control stage, in response to a high potential of the second voltage end, the first and second control modules connect the third voltage end with the first output end; and thus, each scanning unit is provided with the first and second control modules, in the touch control stage, the first control module keeps the first output end in the low potential and the second control module keeps a second output end in the low potential, so that a capacitive coupling effect between grid lines and touch control electrodes in a touch control display panel used by the grid driving circuit is weakened, the precision of touch control detection is improved, added lines are short and narrow, an occupied frame is small in the area, and a narrow frame can be realized.

Owner:SHANGHAI AVIC OPTOELECTRONICS

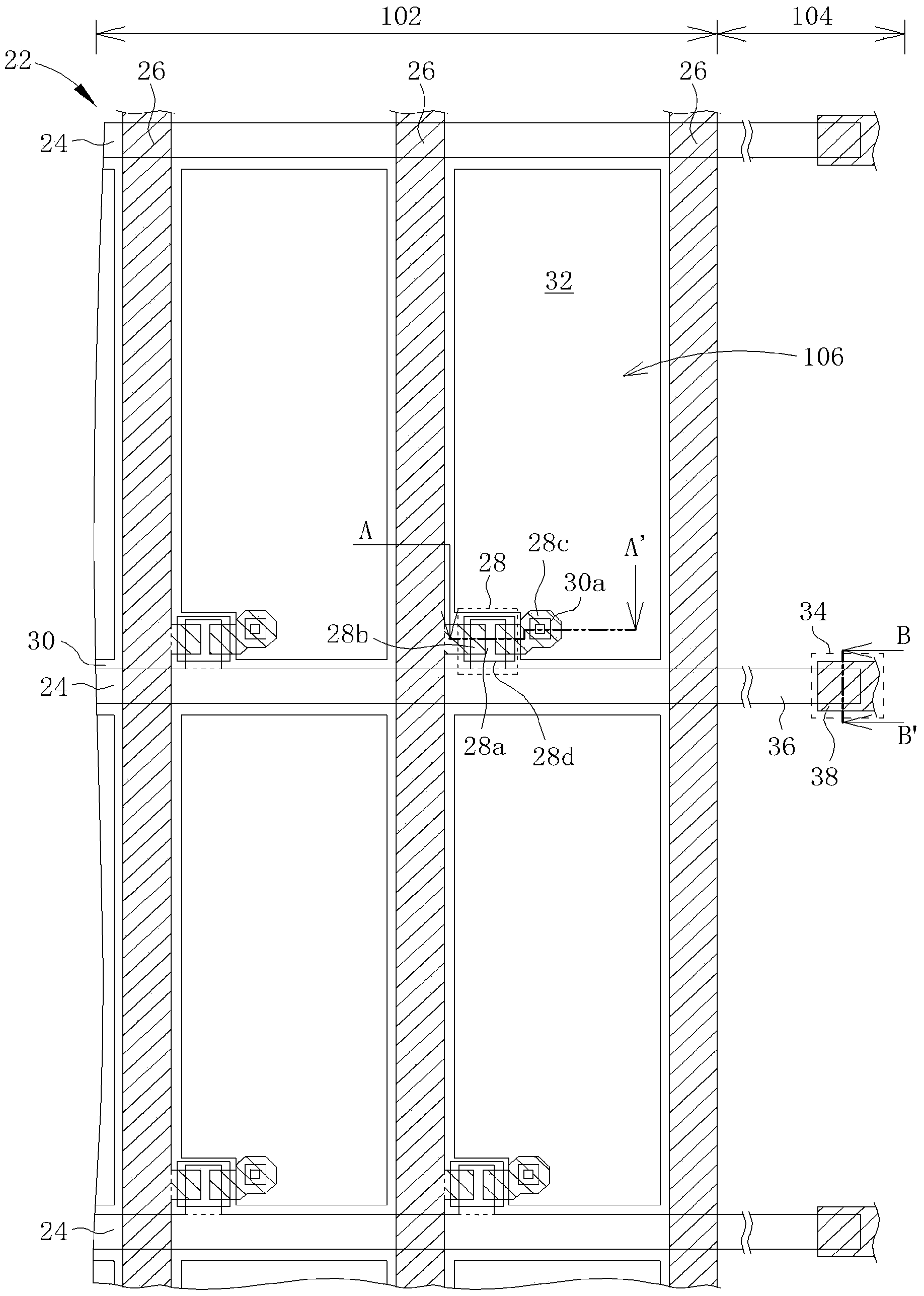

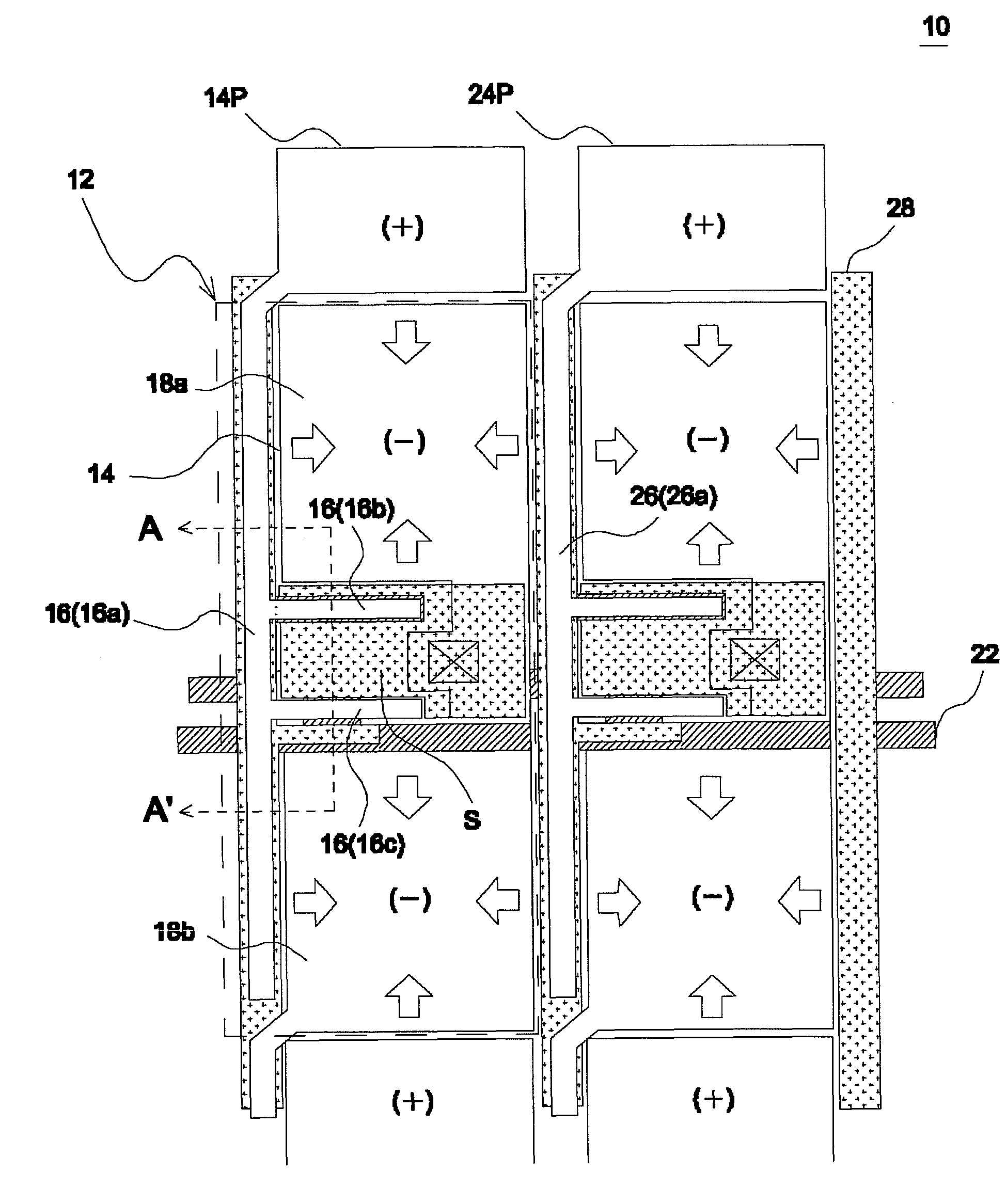

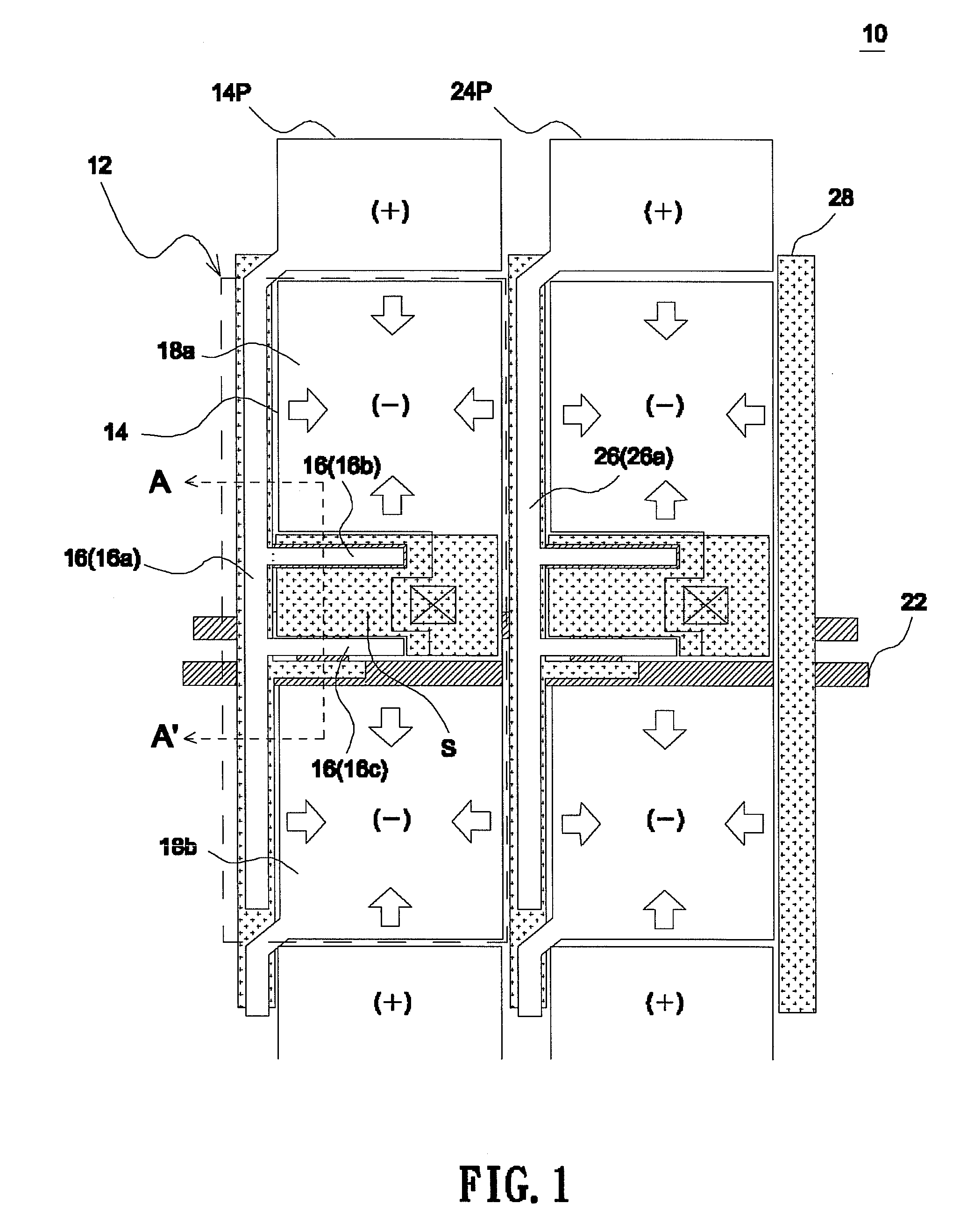

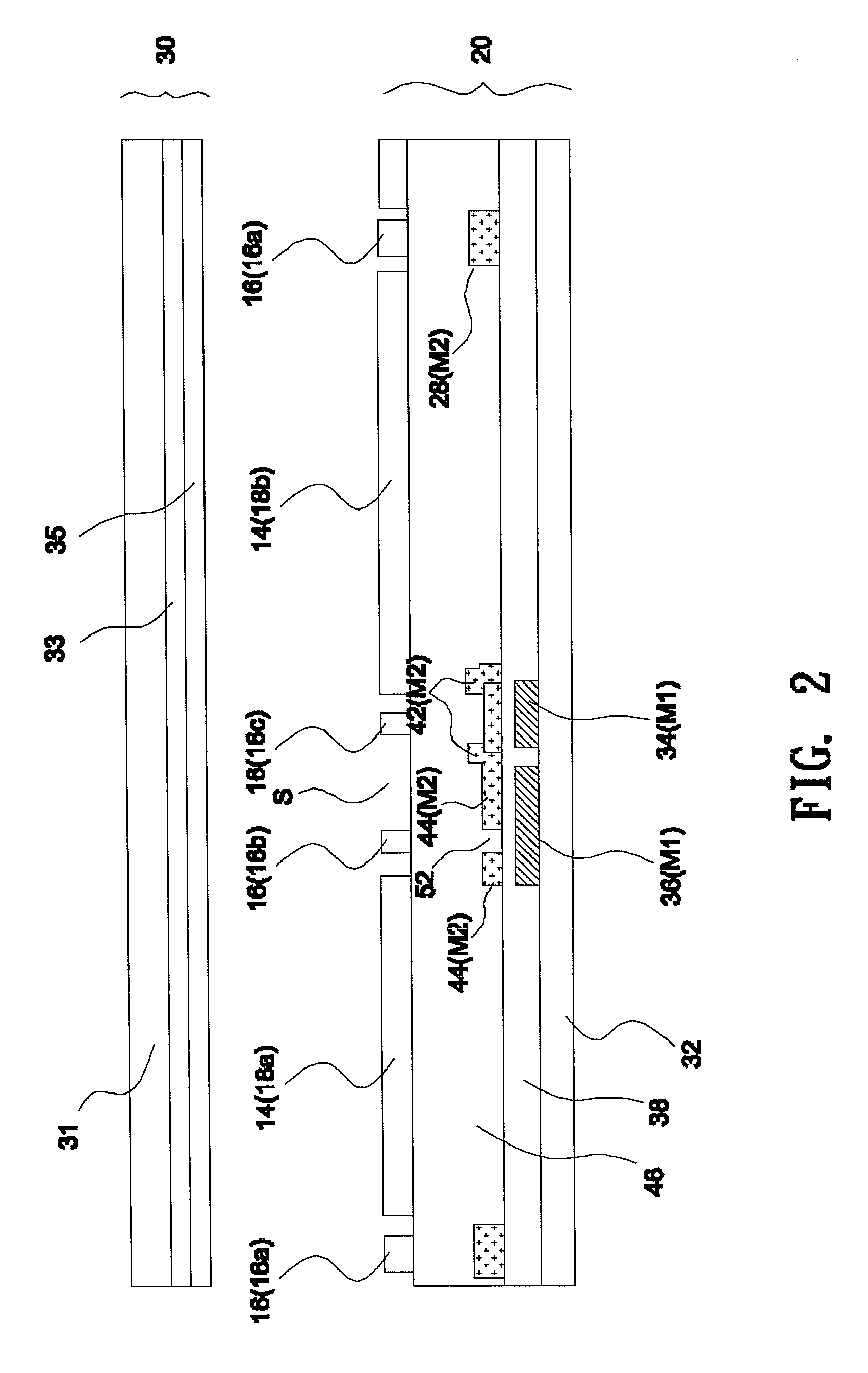

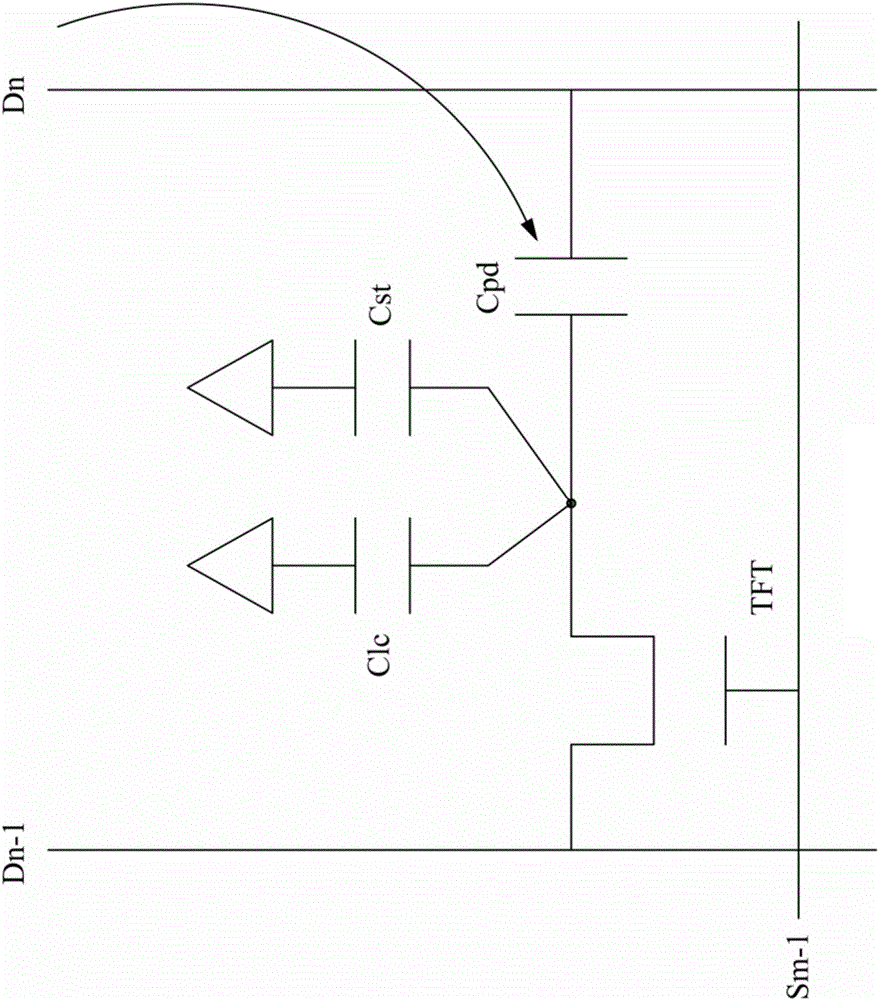

Multi-domain liquid crystal display and array substrate thereof comprising a storage capacitor having an auxiliary electrode controlled by a preceding scan line or signal line

InactiveUS7978271B2Improve pixel aperture ratioReduce capacitive coupling effectsStatic indicating devicesNon-linear opticsLiquid-crystal displayScan line

A multi-domain liquid crystal display includes a first and a second transparent substrates, a liquid crystal layer interposed between them, a common electrode, a first and a second metal layers, a first and a second dielectric layer, multiple pixel electrodes and multiple auxiliary electrodes. The second metal layer is formed on the first dielectric layer, and the second dielectric layer is formed on the first dielectric layer and covers the second metal layer. The pixel electrodes are formed on the second dielectric layer, each of the pixel electrodes having at least one opening to divide itself into a plurality of sections. The auxiliary electrodes are formed on the second dielectric layer, and each of the auxiliary electrodes extends into the opening of the pixel electrode. The second metal layer is hollowed out at a position overlapping the auxiliary electrode to form at least one opening.

Owner:WINTEK CORP +1

Gate drive circuit

ActiveCN106652883AReduce capacitive coupling effectsImprove touch detection accuracyStatic indicating devicesInput/output processes for data processingCapacitanceCapacitive coupling

According to the embodiment, the invention discloses a gate drive circuit. In the gate drive circuit, first control modules respond to signals of first signal en and second signal ends, and in a touch control stage, third voltage ends and first output ends are conducted by virtue of the first control modules; second control modules respond to the signals of the first signal ends and the second signal ends, and in the touch control stage, the third voltage ends and the second output ends are conducted by virtue of the second control modules; therefore, by arranging the first and the second control modules in various canning units, in the touch control stage, the first output ends are controlled at a low potential by virtue of the first control modules, and meanwhile, the second output ends are controlled at a low potential by virtue of the second control modules, so that a capacity coupling action between various gate lines and a touch control electrode in a touch control display panel applied to the gate drive circuit is weakened, and touch control detection precision is enhanced; and an added cable is relatively short, relatively narrow and relatively small in occupied bezel area; therefore, the gate drive circuit is conducive to implementation of a narrow bezel.

Owner:SHANGHAI AVIC OPTOELECTRONICS

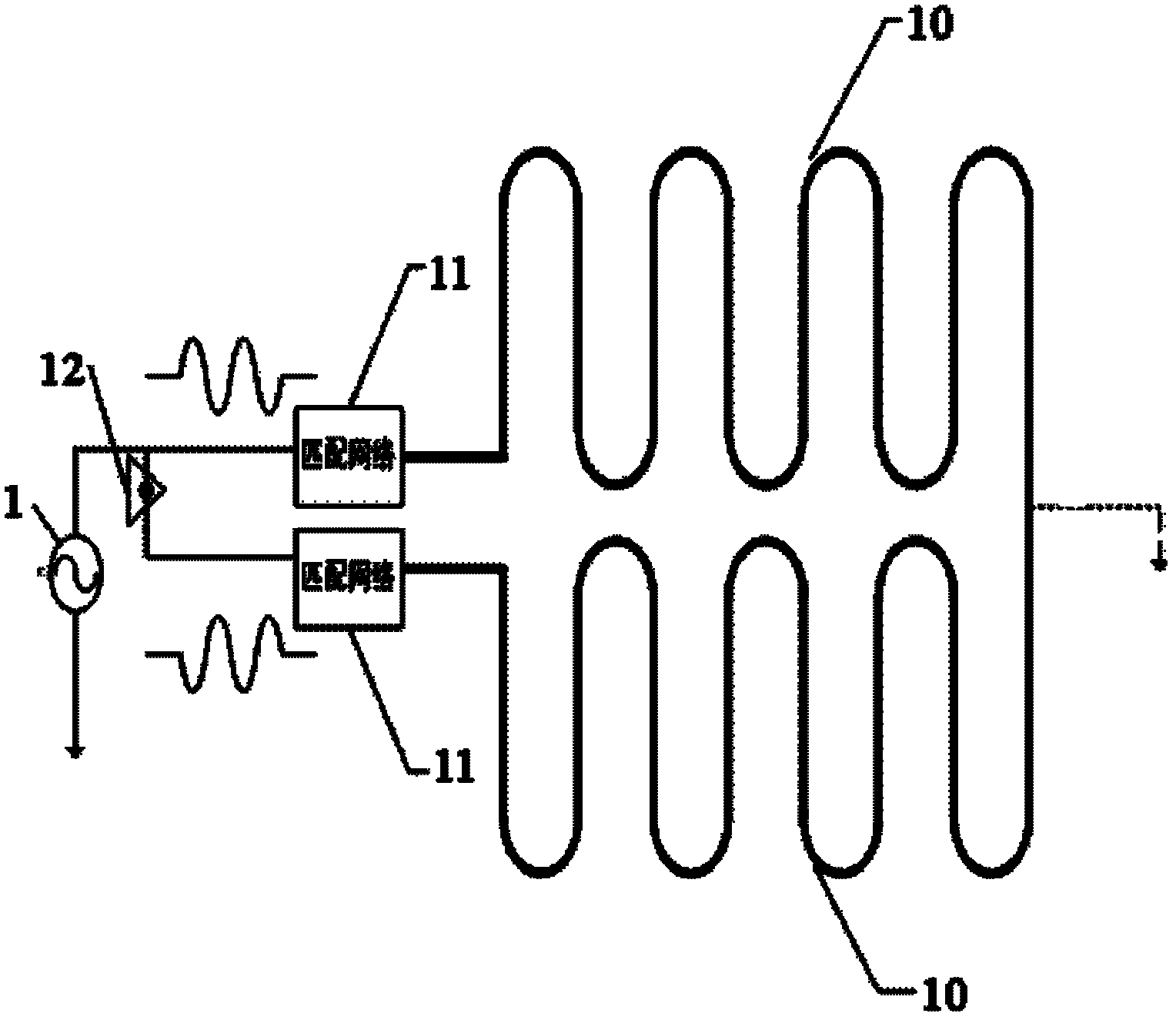

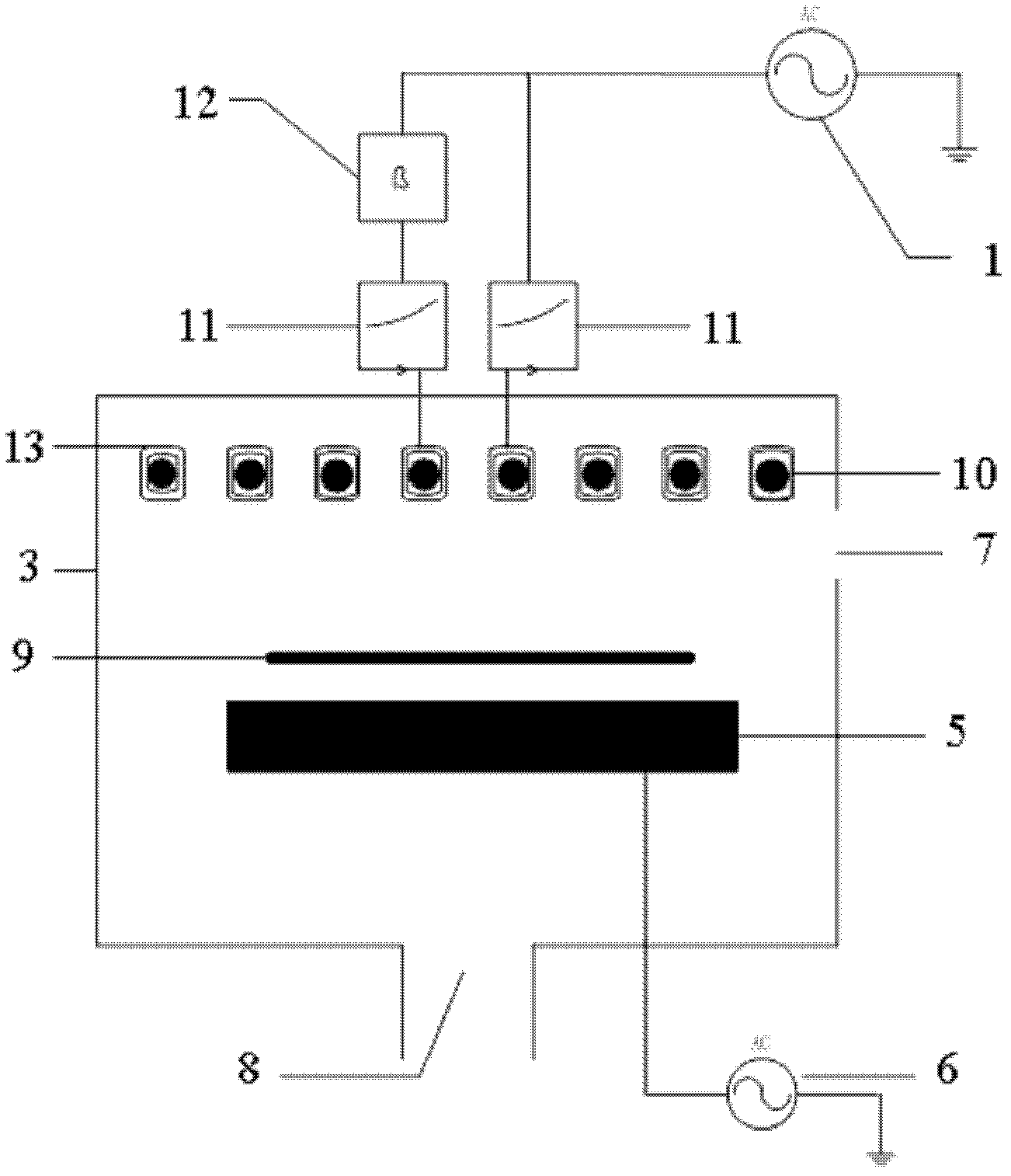

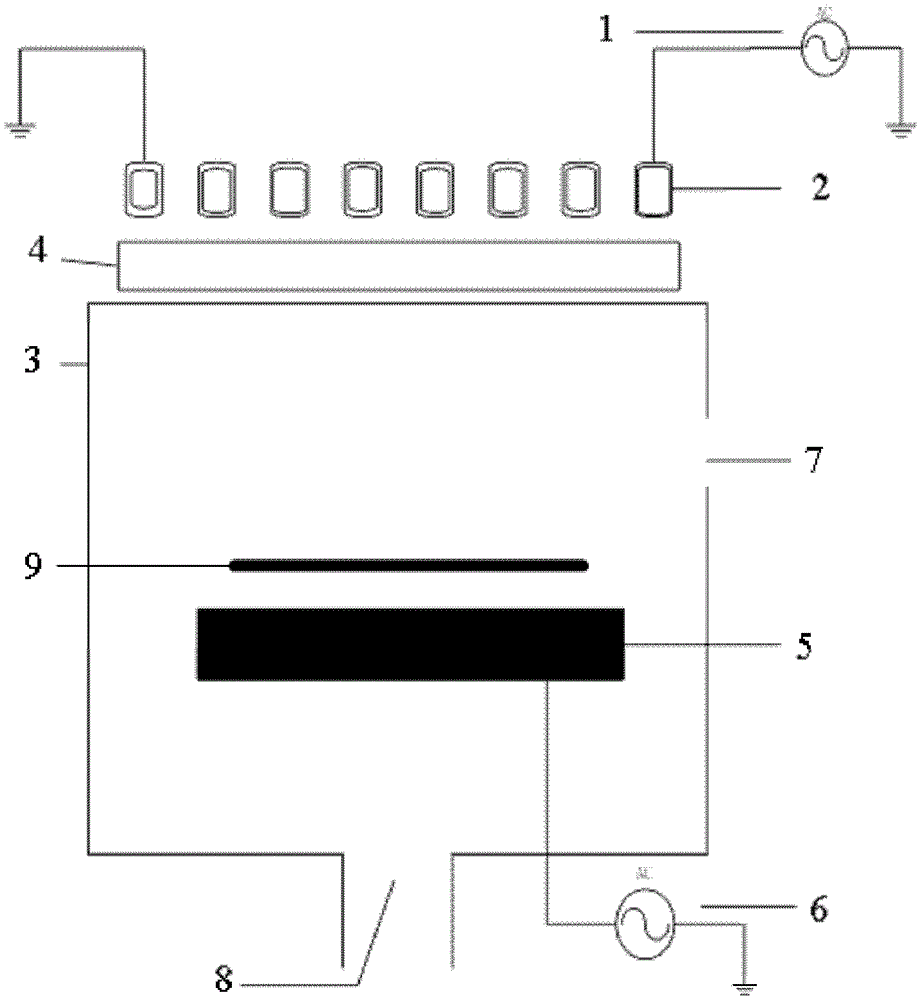

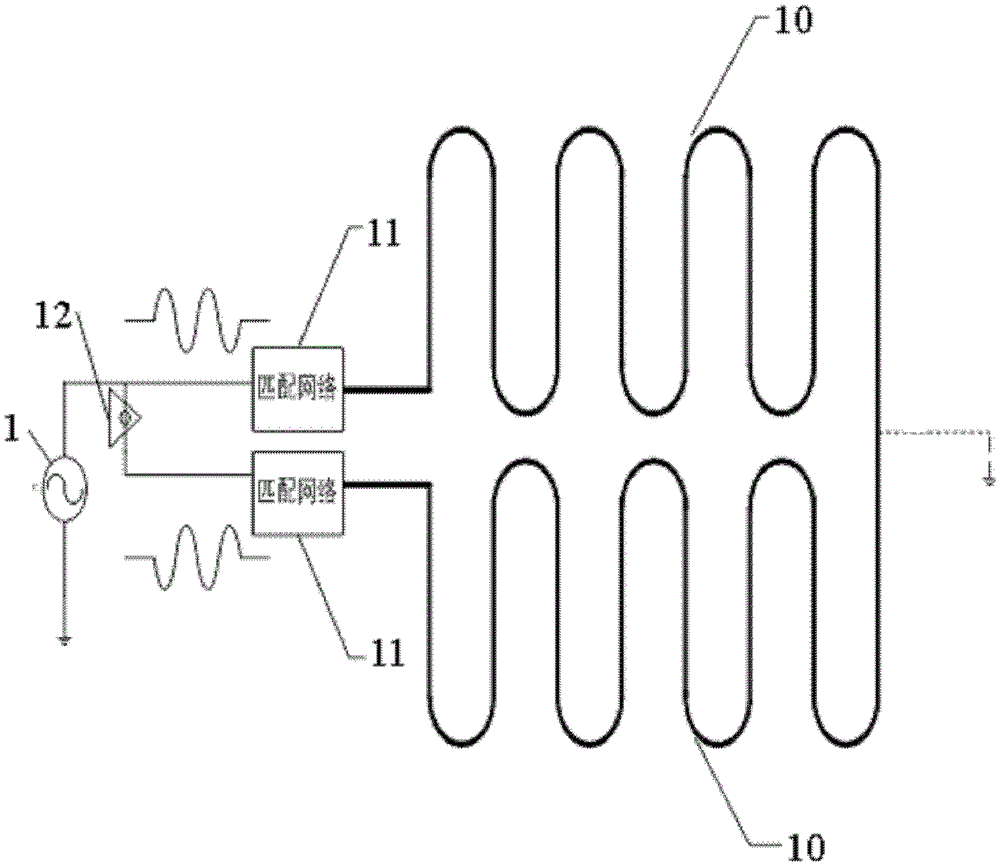

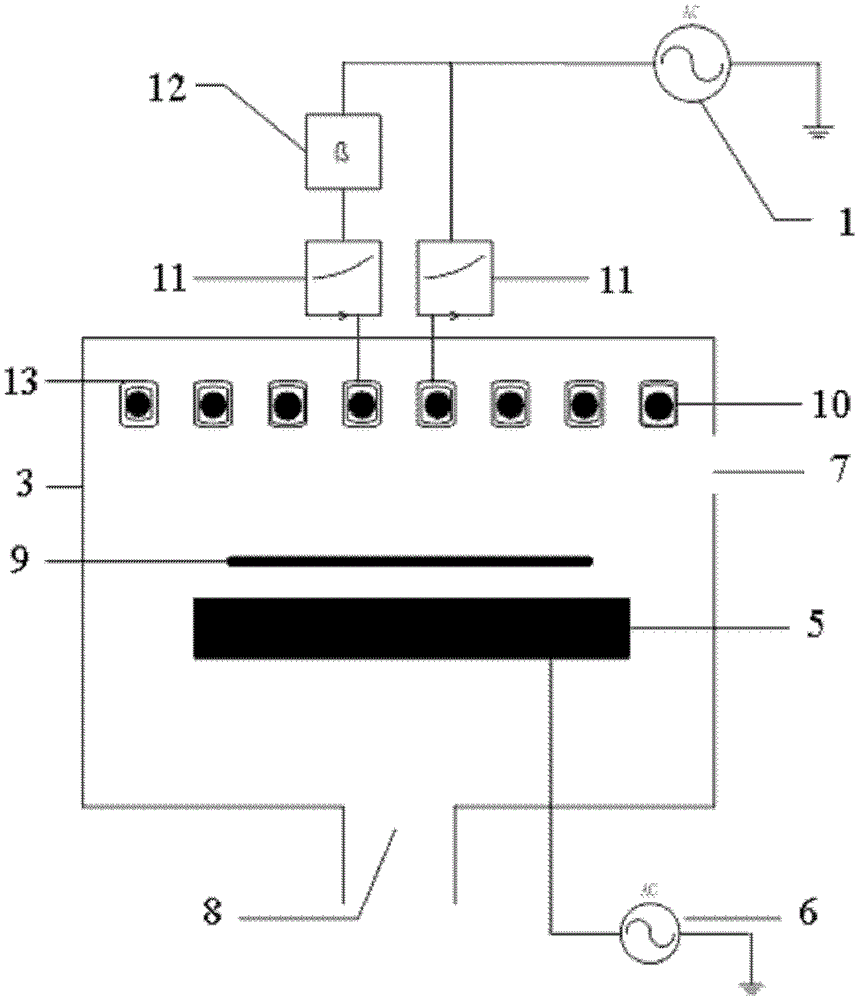

Inductive coupling plasma coil and plasma injection device

ActiveCN103165382AShorten the lengthReduce inductanceElectric discharge tubesInductively coupled plasmaImpedance matching

The invention discloses an inductive coupling plasma coil which comprises two groups of radio-frequency coils formed in a back-bending mode. A plane S-shaped parallel connection way is adopted in space structures of two groups of the radio-frequency coils, and two groups of the radio-frequency coils are strictly symmetrical in space distribution so that the directions of radio frequency current of the same coil position are the same. The invention further discloses an inductive coupling plasma injection device provided with the inductive coupling plasma coil. According to the inductive coupling plasma coil and the injection device, on one hand, standing wave effect in the coil can be reduced and uniformity of plasma can be increased, and on the other hand, impedance matching can be well achieved, coupling effect of the plasma is increased, the probability of chip pollution caused by sputtering of a quartz window due to over-high voltage is lowered, the uniform high-density plasma of a large area can be generated in a reaction cavity of a large area, and therefore requirements of laboratory rooms and industry in the micro electronics field are met.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

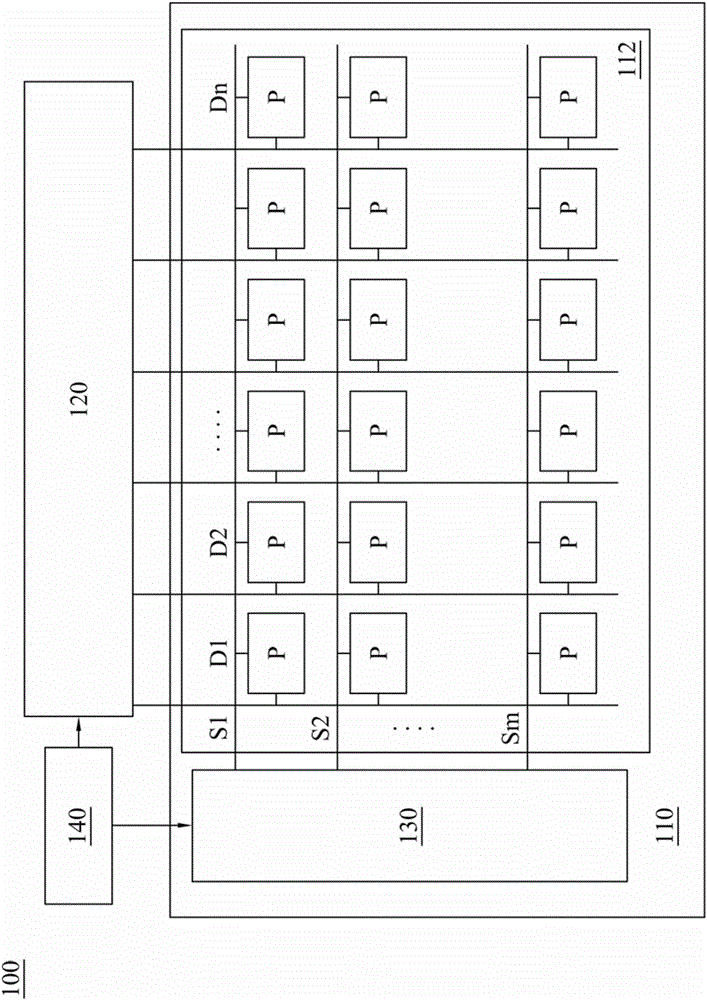

Display device

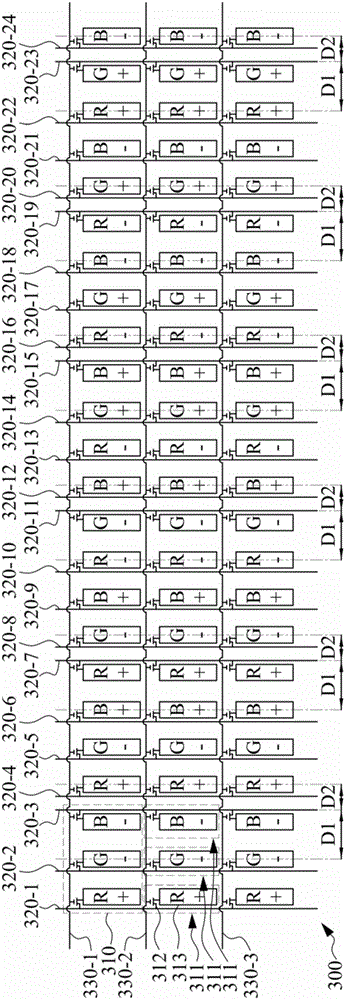

InactiveCN106611589AReduce capacitive coupling effectsImprove display unevennessStatic indicating devicesNon-linear opticsDisplay deviceComputer science

A display device. The display device has a display panel and a drive circuit. The display panel has a pixel array formed by a plurality of pixel electrodes. The drive circuit has a plurality of data lines to drive the pixel electrodes of the pixel array. The pixel electrode of the (N-1)th row in the pixel array of the Mth column and the data line driving the pixel electrode of the Nth row have a first distance D1, the pixel electrodes of the (N+1)th row in the pixel array of the Mth column and the data line driving the pixel electrodes of the Nth row have a second distance D2, and the first distance D1 is larger than the second distance D2.

Owner:AU OPTRONICS CORP

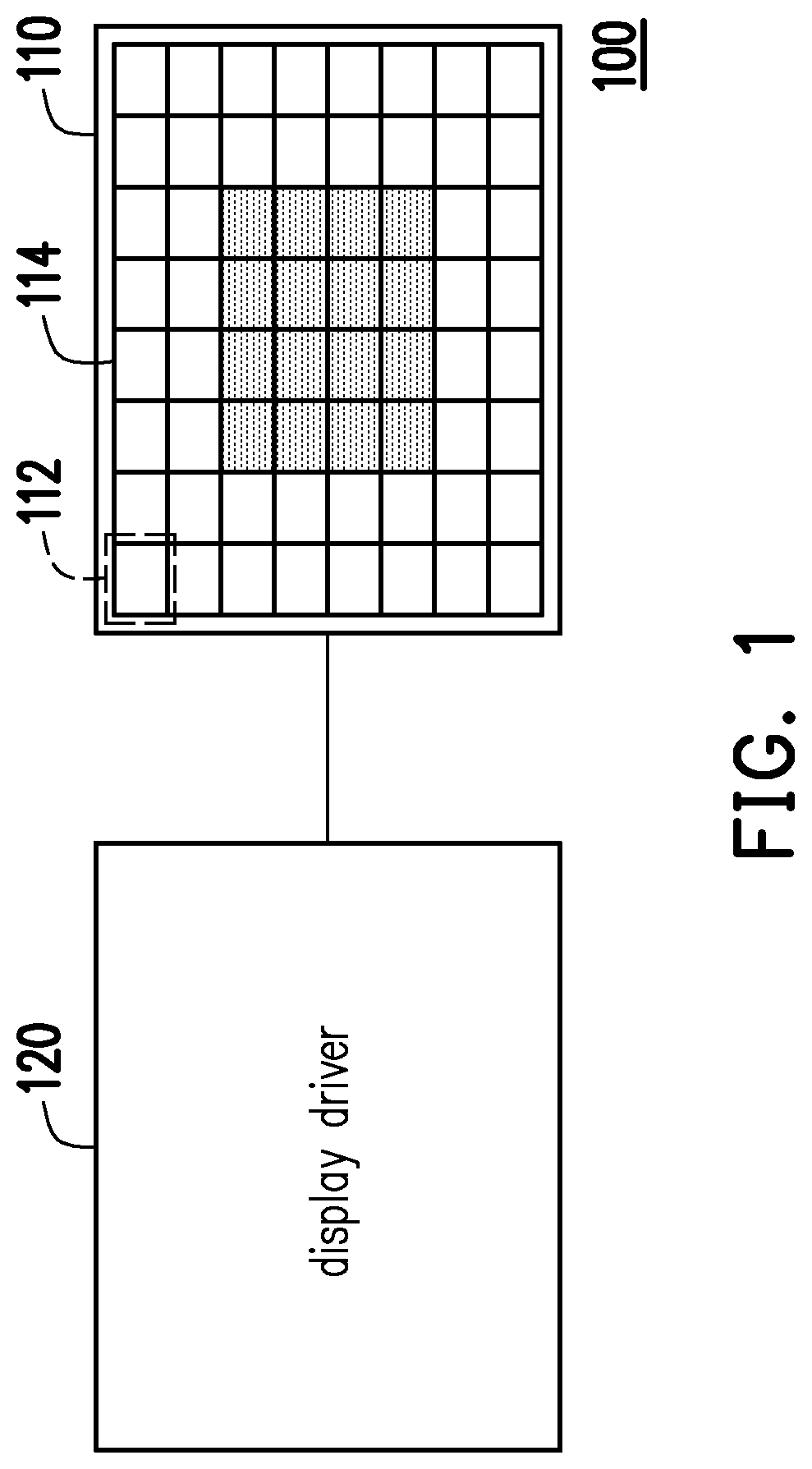

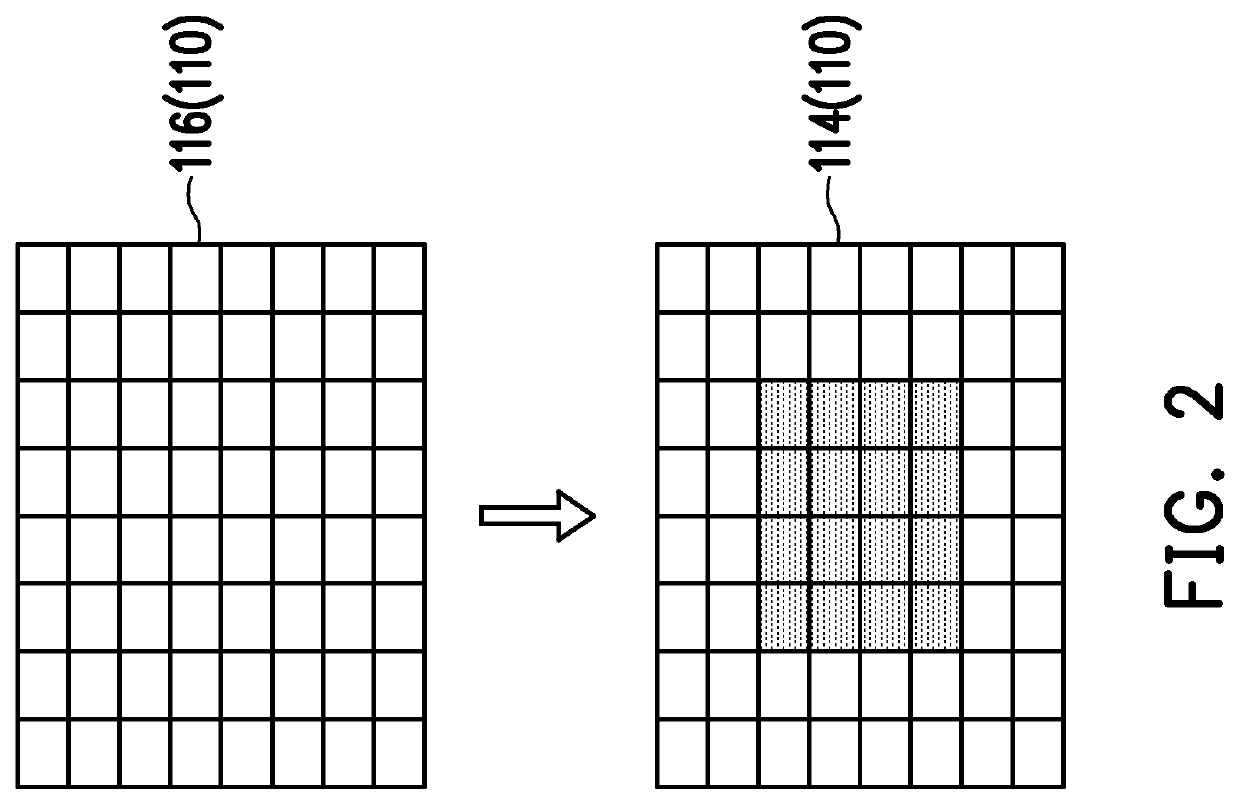

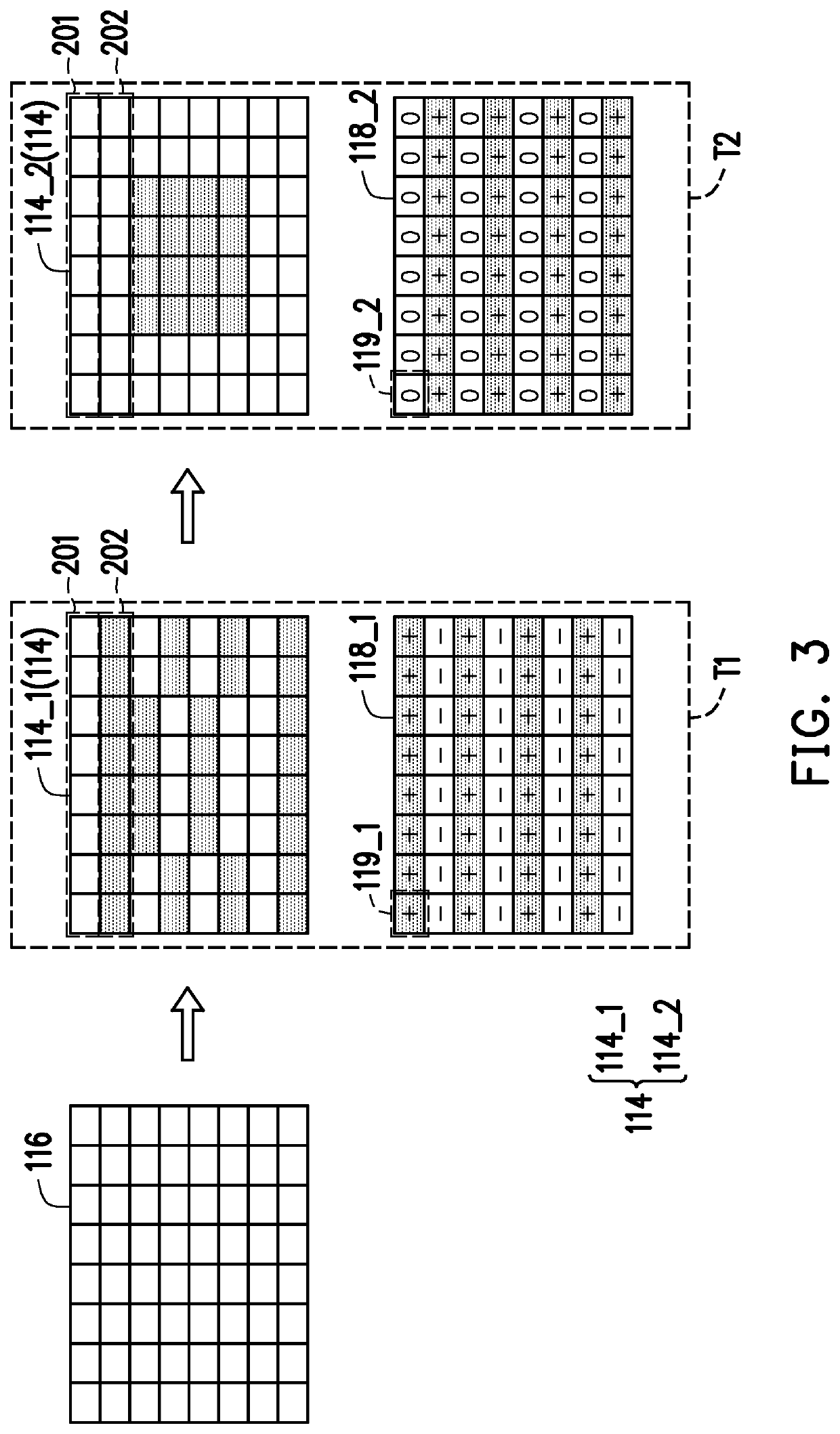

E-paper display device and a method for driving an E-paper display panel

ActiveUS11508324B2Reduce coupling effectReduce capacitive coupling effectsStatic indicating devicesDigital data processing detailsComputer hardwareElectronic paper

An E-paper display device including an E-paper display panel and a display driver is provided. The E-paper display panel displays an image. The image includes a first frame and a second frame. The display driver is coupled to the E-paper display panel. The display driver drives the E-paper display panel to display the image. The display driver drives a first pixel group of the E-paper display panel in a first polarity and drives a second pixel group of the E-paper display panel in a second polarity to display the first frame during a first frame period. The first pixel group and the second pixel group are arranged in interlacing. The display driver drives the second pixel group of the E-paper display panel in the first polarity to display the second frame during a second frame period. Moreover, a method for driving an E-paper display panel is also provided.

Owner:E INK HLDG INC

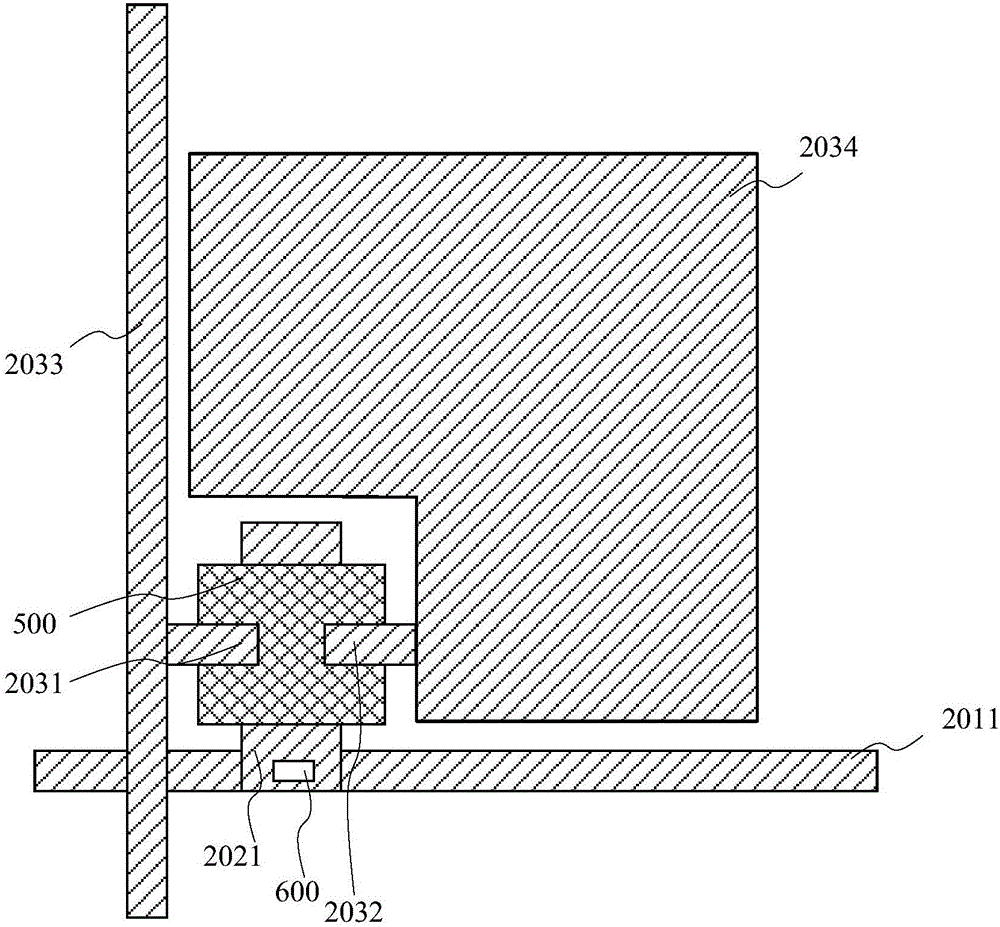

Film transistor panel structure and manufacturing method thereof

ActiveCN106340522AIncreased electrode spacingReduce noiseSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmScan line

The invention provides a film transistor panel structure and a manufacturing method thereof. The structure comprises a first metallic layer as a scan line, a first passivation layer on the first metallic layer, an organic film on the first passivation layer, a second passivation layer on the organic film, through holes passing through the first passivation layer, the organic film and the second passivation layer, a second metallic layer which contacts with the first metallic layer through the through holes and serves as a grid electrode, a third passivation layer covering the grid electrode, a semiconductor active layer on the third passivation layer, and a third metallic layer which serves as a data line, a source electrode, a drain electrode and a pixel electrode. The distance between the two poles of a flat parasitic capacitor and a parallel parasitic capacitor in pixels can be increased, the parasitic capacitance is reduced, pixel noise is also reduced, and the pixel performance is improved.

Owner:IRAY IMAGE TECH TAICANG CO LTD

Method of fabricating semiconductor device

ActiveUS20120129356A1Reduce capacitive coupling effectsReduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceThermal chemical vapor deposition

A method of forming a dielectric layer having an air gap to isolate adjacent wirings or a gate stack of the semiconductor device is provided. A method of fabricating a semiconductor device includes providing a semiconductor substrate on which a plurality of wirings are formed adjacent to one another and forming a dielectric layer filling an upper portion of a space between the adjacent wirings to form air gaps by a thermal chemical vapor deposition method.

Owner:SAMSUNG ELECTRONICS CO LTD

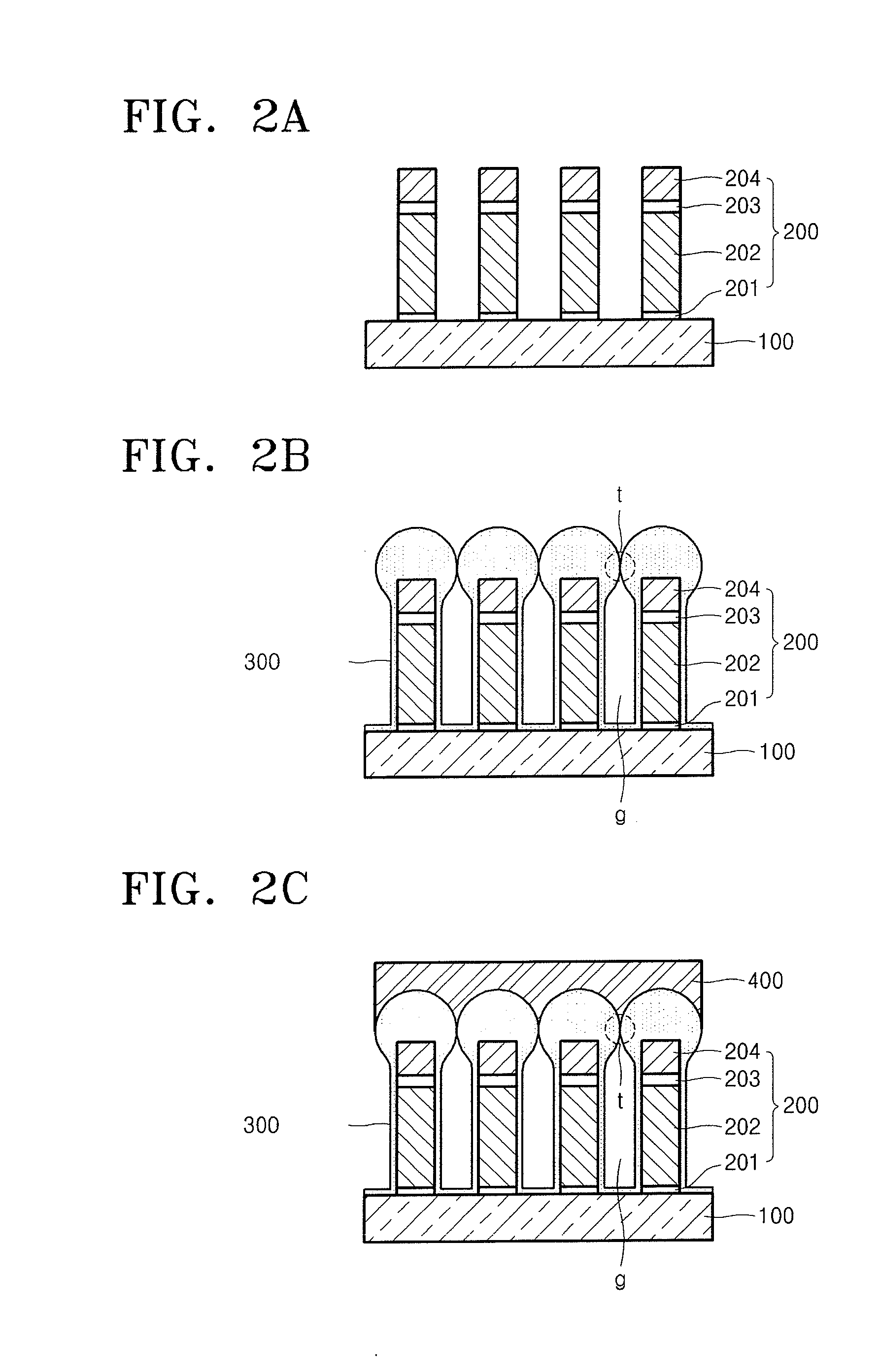

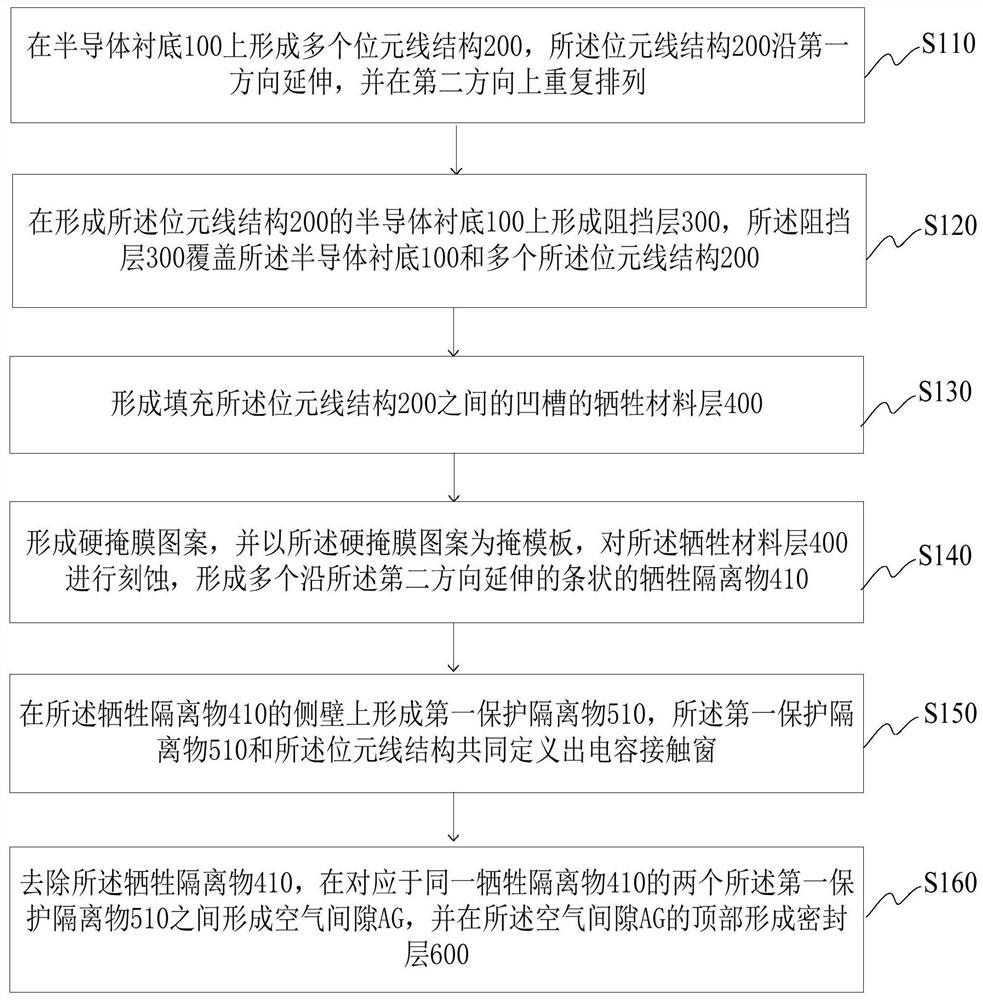

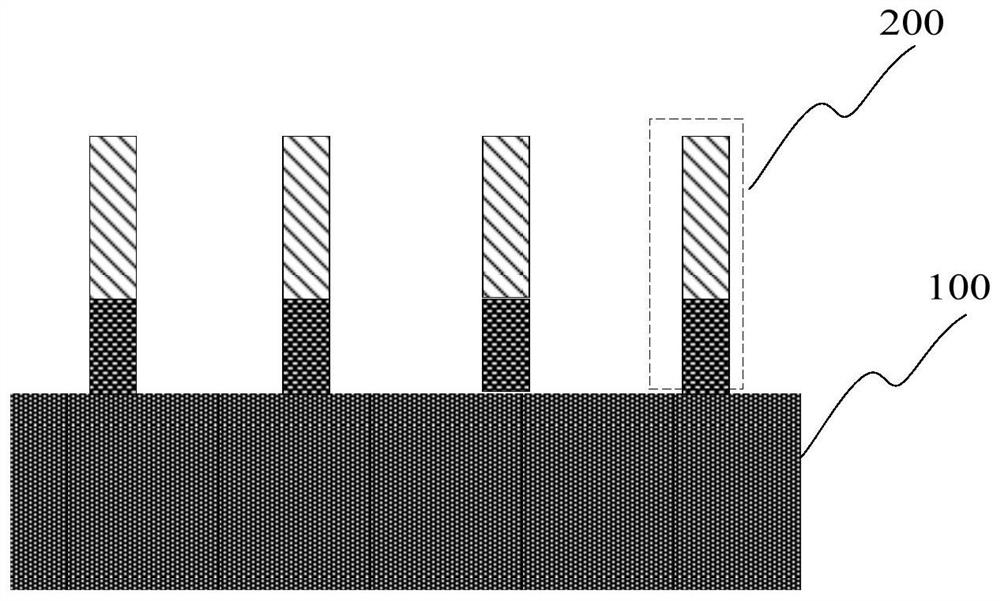

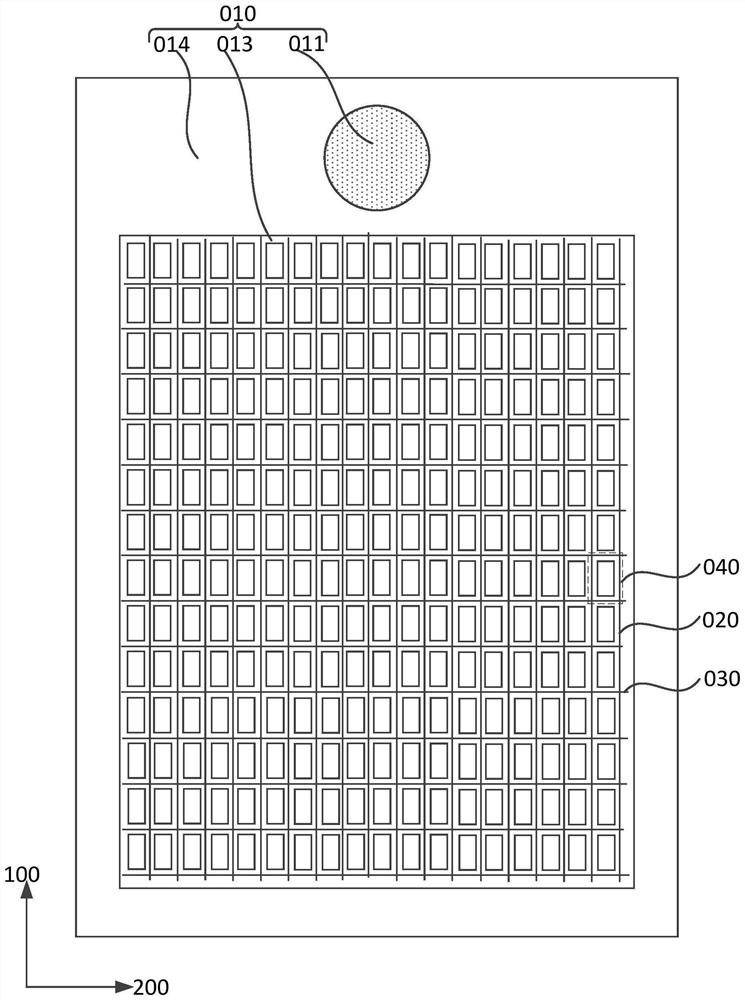

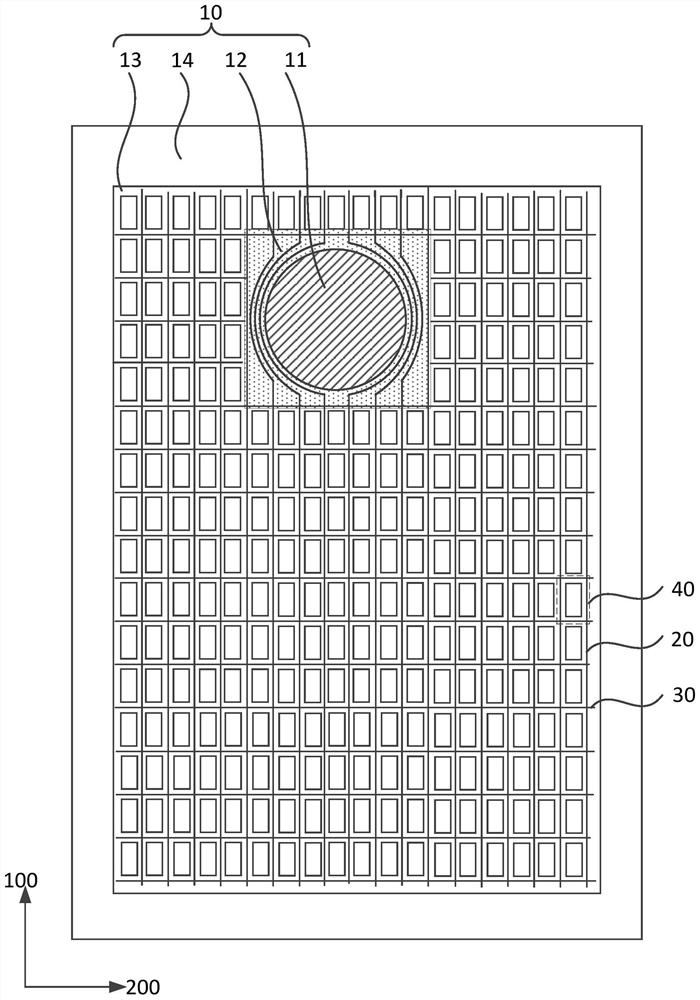

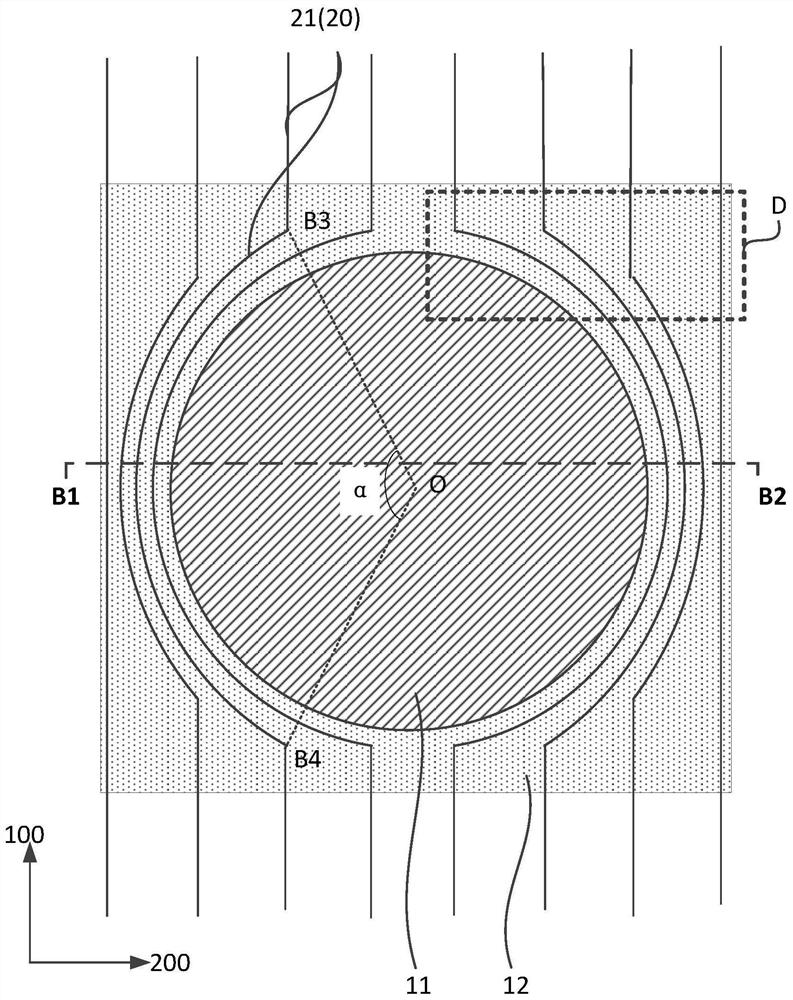

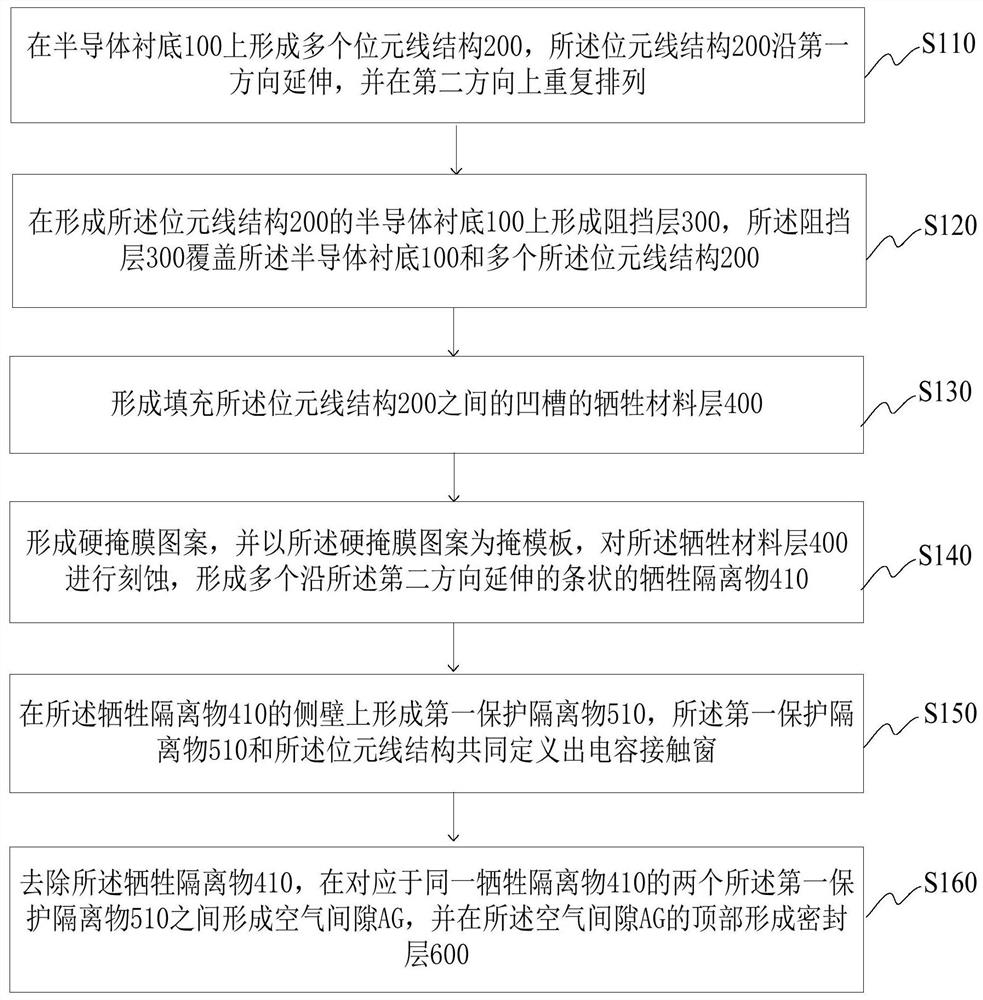

Manufacturing method of semiconductor memory

ActiveCN112563207ASimple processReduce capacitive coupling effectsSemiconductor/solid-state device manufacturingBit lineCapacitance

The invention relates to a manufacturing method of a semiconductor memory. The manufacturing method comprises the steps of forming a plurality of bit line structures on a semiconductor substrate, extending the bit line structures in the first direction, and repeatedly arranging thebit line structures in the second direction; forming a barrier layer on the semiconductor substrate on which the bit line structures are formed, wherein the barrier layer covers the semiconductor substrate and the plurality of bit line structures; forming a sacrificial material layer filling the grooves between the bit line structures; forming a hard mask pattern, and etching the sacrificial material layer by taking the hard mask pattern as a mask plate to form a plurality of strip-shaped sacrificial spacers extending along a second direction; forming a first protection isolator on the side wall of the sacrificial isolator, wherein the first protection isolator and the bit line structure define a capacitor contact window together; and removing the sacrificial spacers, forming an air gap between the two first protection spacers corresponding to the same sacrificial spacer, and forming a sealing layer at the top of the air gap.

Owner:CHANGXIN MEMORY TECH INC

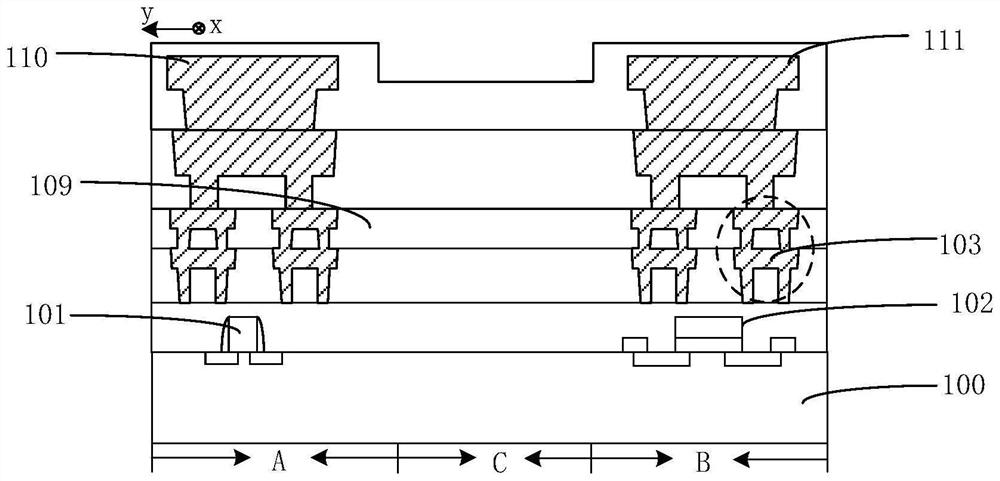

Method for producing two layers of semiconductor devices with half empty structure

ActiveCN102623406AHighly integratedSimple processSemiconductor/solid-state device manufacturingCapacitanceCapacitive coupling

According to the invention, the methods of low-temperature bonding and low-temperature exfoliation are utilized to achieve the layer transfer of an upper semiconductor layer above a lower semiconductor device layer, then an upper semiconductor device is produced in the upper semiconductor layer, and finally, the processes for an upper contact hole and a lower contact hole are completed in one time to realize isolation in production of the upper and the lower layers of semiconductor devices. The method provided by the invention has the advantage of simple process. The integration level of the semiconductor devices is increased effectively. Additionally, a half empty isolation structure of an empty layer and the lower contact hole is produced between the upper and the lower layers of the semiconductor devices to effectively reduce the capacitance coupling effect between the upper and the lower layers of the semiconductor devices.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Inductively Coupled Plasma Implantation Device

ActiveCN103165382BShorten the lengthReduce inductanceElectric discharge tubesImpedance matchingInductively coupled plasma

The invention discloses an inductive coupling plasma coil which comprises two groups of radio-frequency coils formed in a back-bending mode. A plane S-shaped parallel connection way is adopted in space structures of two groups of the radio-frequency coils, and two groups of the radio-frequency coils are strictly symmetrical in space distribution so that the directions of radio frequency current of the same coil position are the same. The invention further discloses an inductive coupling plasma injection device provided with the inductive coupling plasma coil. According to the inductive coupling plasma coil and the injection device, on one hand, standing wave effect in the coil can be reduced and uniformity of plasma can be increased, and on the other hand, impedance matching can be well achieved, coupling effect of the plasma is increased, the probability of chip pollution caused by sputtering of a quartz window due to over-high voltage is lowered, the uniform high-density plasma of a large area can be generated in a reaction cavity of a large area, and therefore requirements of laboratory rooms and industry in the micro electronics field are met.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

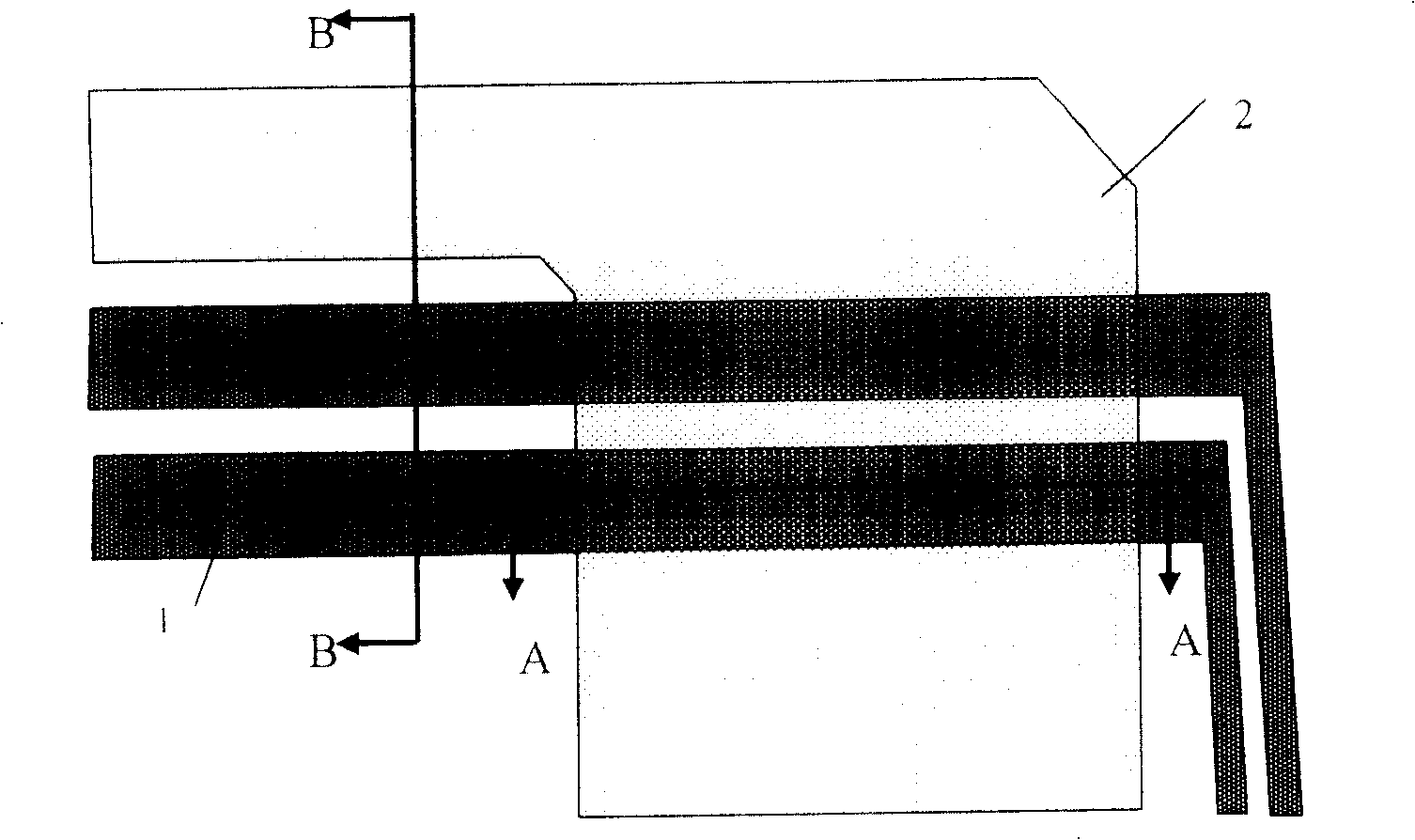

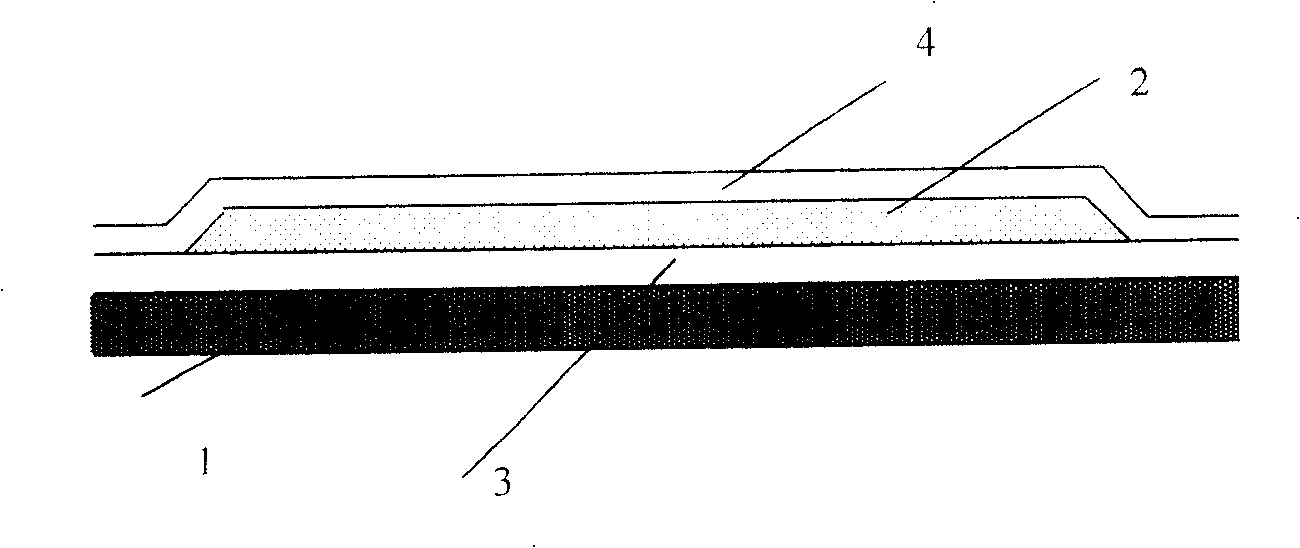

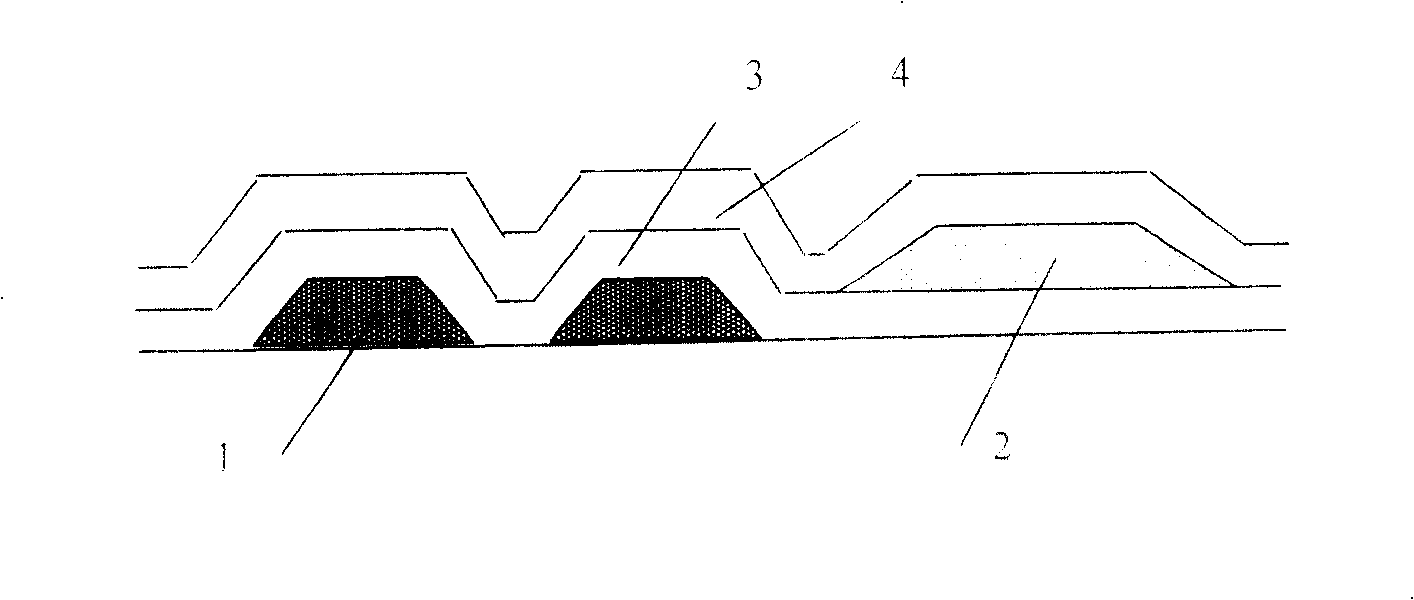

TFT LCD array substrate peripheral wiring structure and its producing method

ActiveCN100423275CMeet the requirements of normal repairReduce overlap areaSemiconductor/solid-state device detailsSolid-state devicesInsulation layerEngineering

This invention discloses a surrounding routing structure of a TFT LCD array base plate including: a base plate and an array structure formed on it, a repairing line formed on the base plate, a grid insulation layer formed on the line, a surrounding public electrode routing formed on the grid insulation layer and overlapped with the repairing wire, in which, the surrounding public electrode routing is in a net structure with the repairing wire crossover region. This invention also discloses another TFT LCD array base plate surrounding routing structure and a manufacturing method for the structure.

Owner:BOE TECH GRP CO LTD +1

A kind of manufacturing method of mos transistor

ActiveCN104733318BLow dielectric constantReduce capacitive coupling effectsSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic capacitanceGate stack

The invention provides a method for manufacturing a MOS transistor, comprising: a. providing a semiconductor substrate, dummy gate stacks, spacers, and source-drain regions; b. forming a first interlayer dielectric layer whose height is less than that of the dummy gate The height of the stack; c. remove the part of the first interlayer dielectric layer located at both ends away from the dummy gate stack to form a first vacancy; d. fill the second interlayer dielectric layer in the first vacancy, which The top is located between the top of the first interlayer dielectric layer and the top of the gate stack; e. forming a third interlayer dielectric layer to cover the first interlayer dielectric layer and the second interlayer dielectric layer; f. forming a through hole exposing the first interlayer dielectric layer in the interlayer dielectric layer; g. removing the first interlayer dielectric layer through the through hole to form a second vacancy; h. forming a cap layer to fill the through hole hole. The invention effectively reduces the gate parasitic capacitance and improves device performance.

Owner:北京中科微投资管理有限责任公司

E-paper display device and a method for driving an e-paper display panel

ActiveUS20210398495A1Reduce coupling effectReduce capacitive coupling effectsStatic indicating devicesDigital data processing detailsComputer hardwarePaper sheet

An E-paper display device including an E-paper display panel and a display driver is provided. The E-paper display panel displays an image. The image includes a first frame and a second frame. The display driver is coupled to the E-paper display panel. The display driver drives the E-paper display panel to display the image. The display driver drives a first pixel group of the E-paper display panel in a first polarity and drives a second pixel group of the E-paper display panel in a second polarity to display the first frame during a first frame period. The first pixel group and the second pixel group are arranged in interlacing. The display driver drives the second pixel group of the E-paper display panel in the first polarity to display the second frame during a second frame period. Moreover, a method for driving an E-paper display panel is also provided.

Owner:E INK HLDG INC

Display panel and display device

ActiveCN108806513BReduce areaNormal installation and useIdentification meansComputer hardwareComputer graphics (images)

The embodiment of the invention discloses a display panel and a display device. In the display panel, the base substrate includes a device setting area, a first non-display area, a display area and a second non-display area, the first non-display area surrounds the device setting area, and the display area surrounds the first non-display area; formed on the substrate A plurality of data lines on the substrate; the first metal layer, the second metal layer and the third metal layer formed on the base substrate, each data line includes a first wiring part, and the first wiring part is located on the second metal layer layer; part of the data lines passing through the first non-display area also includes a first jumper, and each first jumper is located in the third metal layer; or, each first jumper is located in the first metal layer or, part of the first bridging portion is located in the third metal layer, and part of the first bridging portion is located in the first metal layer, the above-mentioned display panel can make each size larger on the premise of ensuring a higher screen ratio of the display panel The device is installed and used normally.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Manufacturing method of semiconductor memory device

ActiveCN112563207BSimple processReduce capacitive coupling effectsSemiconductor/solid-state device manufacturingBit lineCapacitance

The invention relates to a manufacturing method of a semiconductor memory. The manufacturing method includes: forming a plurality of bit line structures on a semiconductor substrate, the bit line structures extending along a first direction and repeatedly arranged in a second direction; forming barriers on the semiconductor substrate on which the bit line structures are formed layer, the barrier layer covers the semiconductor substrate and a plurality of bit line structures; forms a layer of sacrificial material filling the grooves between the bit line structures; forms a hard mask pattern, and uses the hard mask pattern as a mask plate to sacrificially The material layer is etched to form a plurality of strip-shaped sacrificial spacers extending along the second direction; a first protective spacer is formed on the sidewall of the sacrificial spacer, and the first protective spacer and the bit line structure jointly define a Capacitive contact window; removing the sacrificial spacer, forming an air gap between two first protective spacers corresponding to the same sacrificial spacer, and forming a sealing layer on top of the air gap.

Owner:CHANGXIN MEMORY TECH INC

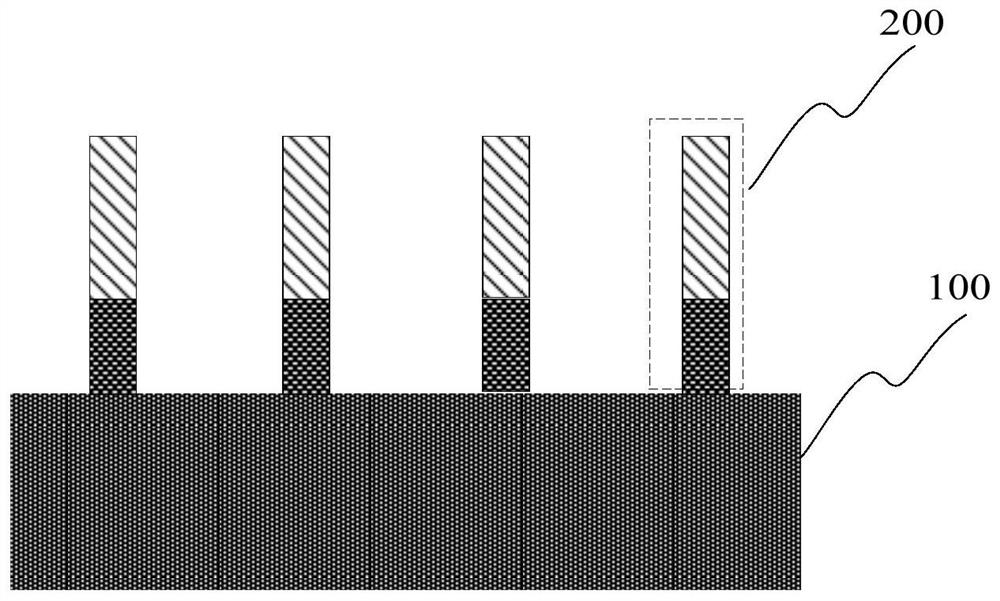

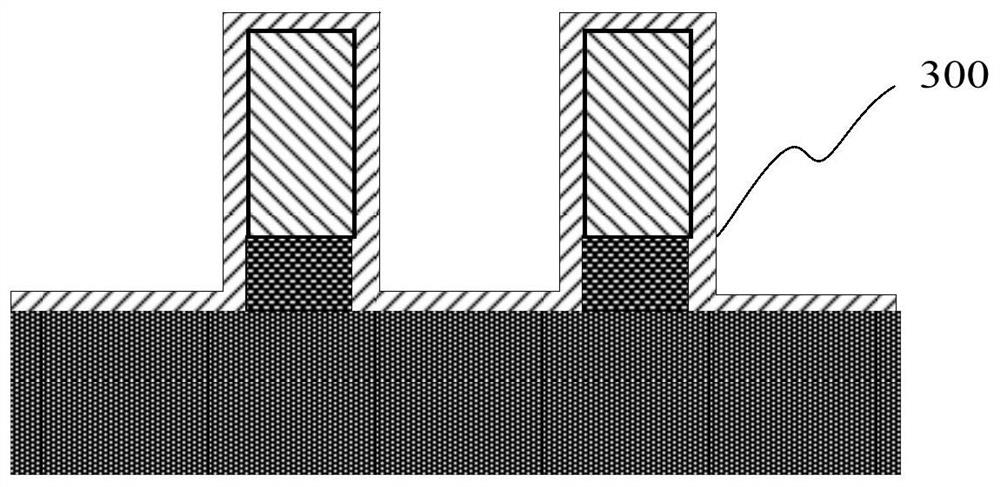

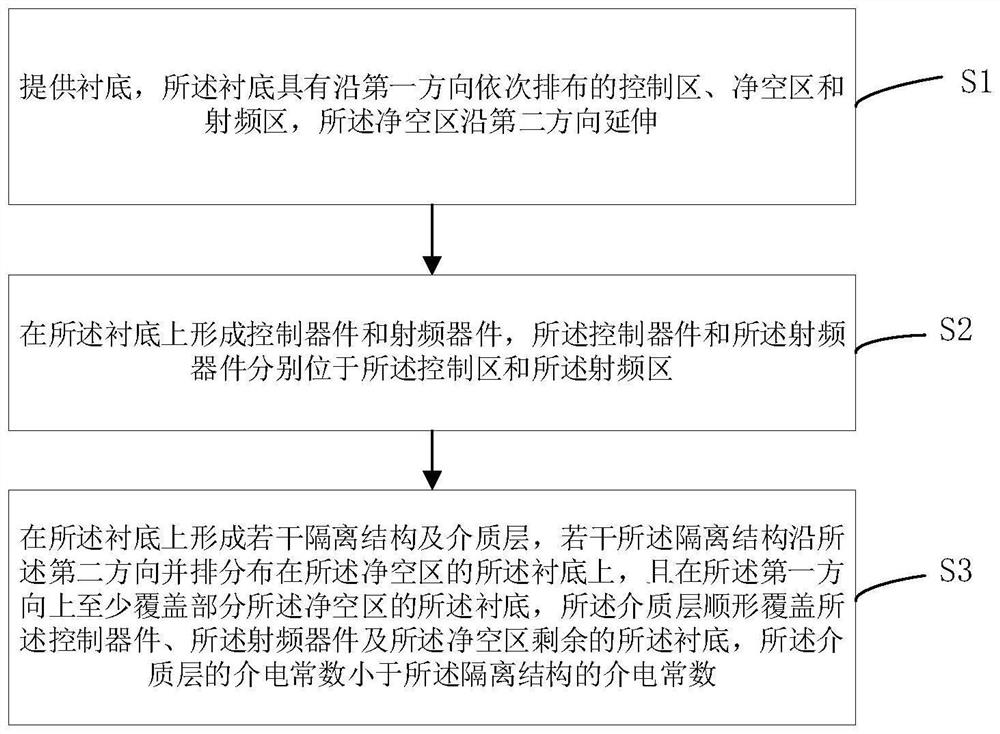

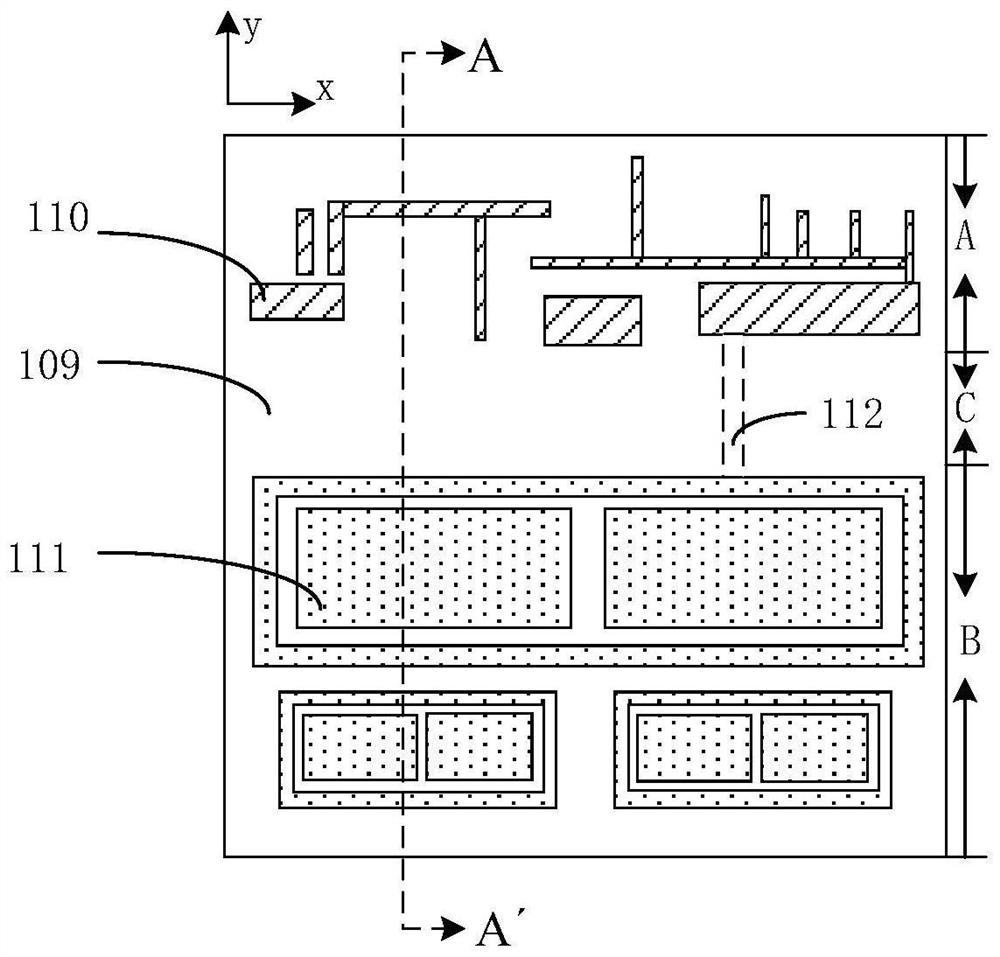

Radio frequency switch and preparation method thereof

PendingCN114823663ASmall sizeReduce crosstalkSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceCapacitive coupling

The invention provides a radio frequency device and a preparation method thereof, and the device comprises a substrate which is provided with a control region, a clearance region and a radio frequency region which are sequentially arranged in a first direction, and the clearance region extends in a second direction; the control device and the radio frequency device are respectively positioned on the substrate in the control area and the radio frequency area; the plurality of isolation structures are distributed on the substrate in the clearance area side by side along the second direction; the dielectric layer is located on the substrate and covers the control device, the radio frequency device and the remaining substrate in the clearance area in a conformal mode, and the dielectric constant of the dielectric layer is larger than that of the isolation structure. According to the isolation structure, the capacitive coupling effect between the control device and the radio frequency device can be reduced, so that crosstalk between signals is reduced, and a good isolation effect on the signals is achieved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP