Thin-film transistor array substrate

A technology of thin film transistors and array substrates, which is applied in the field of display panels and can solve the problems of limited pixel aperture ratio of liquid crystal display panels

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

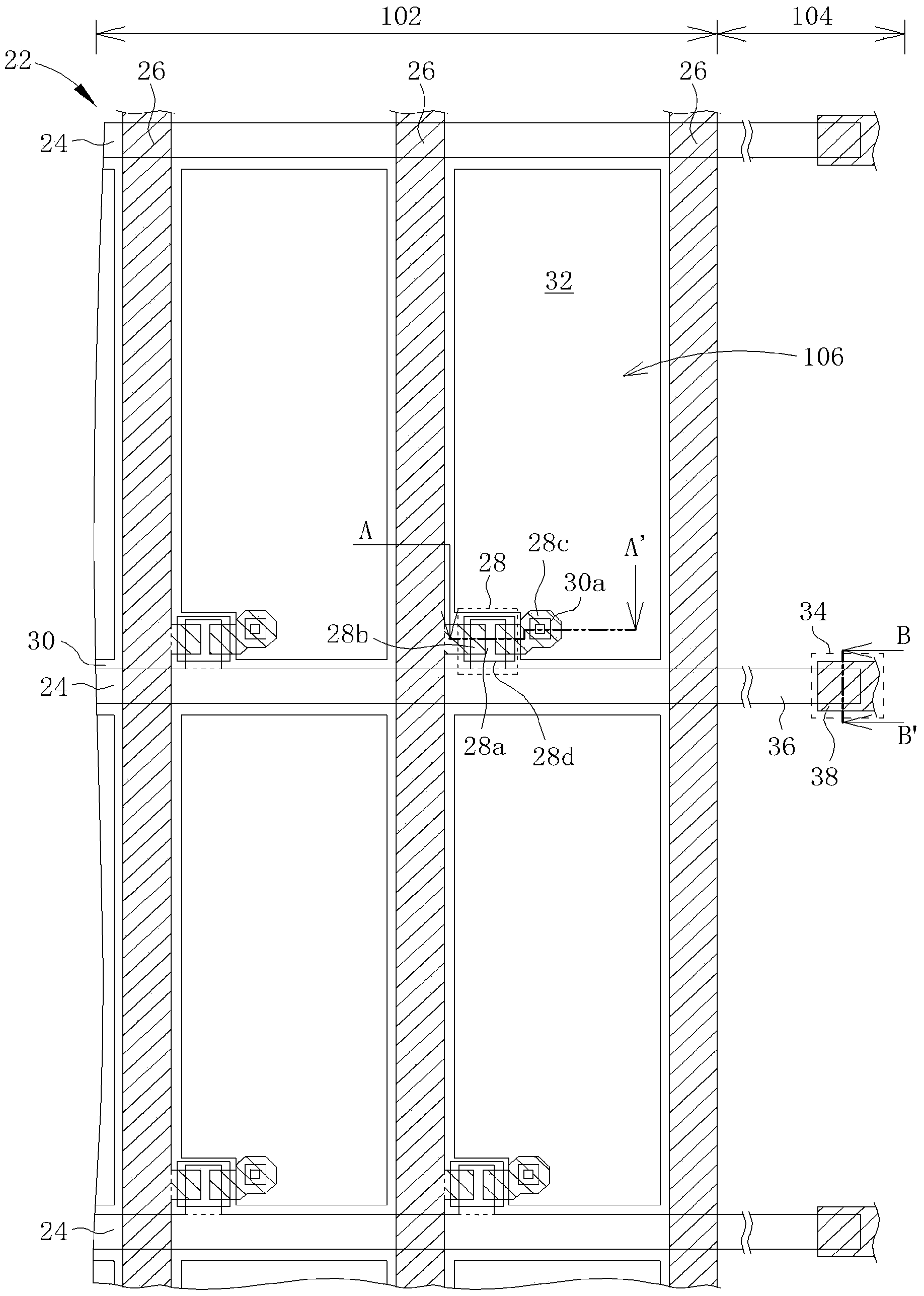

[0023] figure 2 A schematic bottom view showing a thin film transistor array substrate according to an embodiment of the present invention. The TFT array substrate 22 includes a display area 102 and a fan-out area 104 . In the display area 102 , there are a plurality of scan lines 24 , a plurality of data lines 26 , a plurality of thin film transistors 28 , a common electrode 30 and a plurality of pixel electrodes 32 . The data lines 26 and the scan lines 24 intersect, so that any two adjacent data lines 26 and any two adjacent scan lines 24 surround a pixel region 106 , and the pixel regions 106 are arranged in an array. Each thin film transistor 28 is respectively disposed corresponding to each pixel region 106, and each thin film transistor 28 includes a gate 28a, a source 28b, and a drain 28c, and also includes a gate insulating layer (not shown) and a semiconductor layer 28d. Moreover, the gate electrode 28 a is electrically connected to the corresponding scan line 24 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More