Method for producing two layers of semiconductor devices with half empty structure

A semiconductor and semi-hollow technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as increasing parasitic capacitance of semiconductor devices, limiting circuit response speed, increasing process complexity, etc., achieving simple process, The effect of increasing the degree of integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

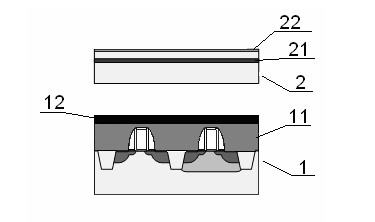

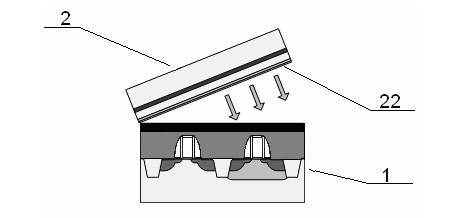

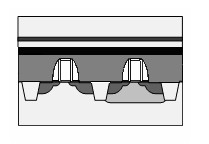

[0039] The invention provides a method for preparing a two-layer semiconductor device and a semiconductor device prepared by the method, Figure 1~Figure 11 A schematic flow diagram of the preparation of a two-layer semiconductor device in one embodiment of the present invention is given; below, with reference to the accompanying drawings, the present invention will be introduced and described in detail through specific embodiments, so as to better understand the content of the present invention, but it should be understood Yes, the following examples do not limit the scope of the present invention.

[0040]

[0041] In this embodiment, a planar CMOS FET structure is taken as an example, but various semiconductor devices may also be used.

[0042]

[0043] step 1

[0044] refer to figure 1 , the lower supporting sheet 1 has been patterned, and the supporting sheet 1 is selected from a bulk silicon wafer, and may also be an SOI silicon wafer, or other semiconductor wafers s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More