Heterogeneous confusion hierarchical memory device

A hierarchical and mixed technology, applied in the direction of memory address/allocation/relocation, etc., can solve the problems of limited number of writes, low static power consumption, non-volatile memory characteristics can not be fully utilized, etc., to avoid Shock, high technical value effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

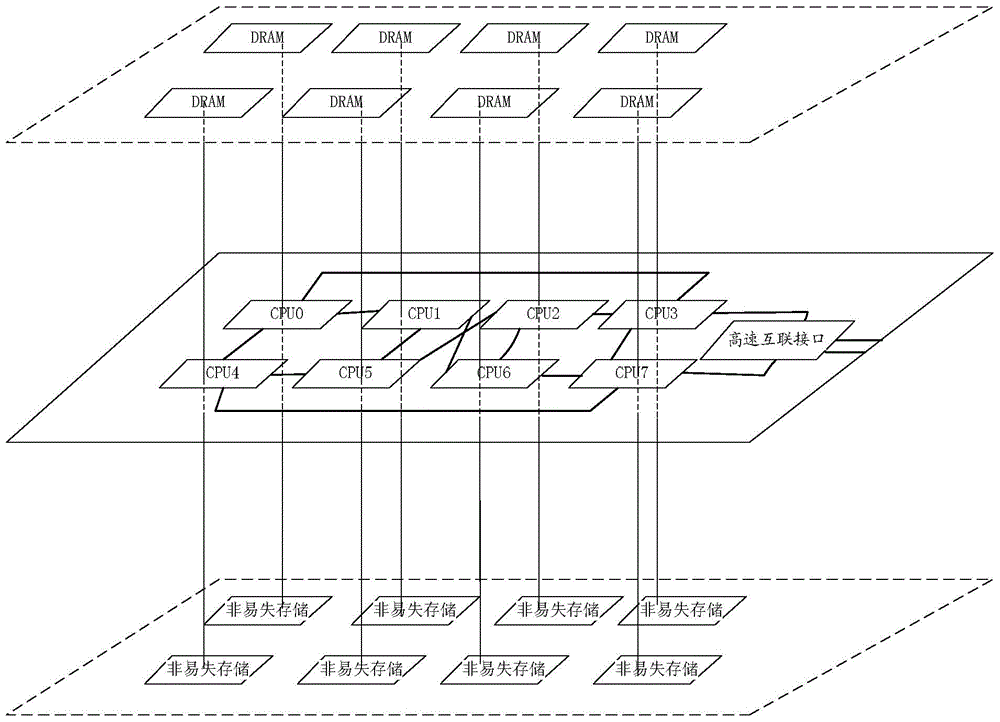

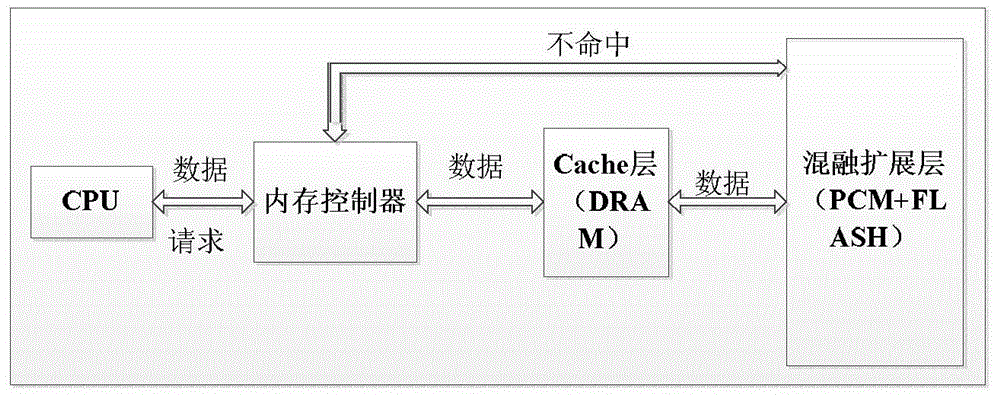

[0017] The architecture of the heterogeneous hybrid hierarchical memory device proposed by the present invention will be described in detail below with reference to the accompanying drawings. figure 2 , the solution proposed by the present invention is based on the effective combination of DRAM, PCM and Flash three media, so that the respective advantages can be brought into play to the greatest extent, and the roles of the three media are assigned, and DRAM acts as a cache cache for non-volatile storage , the non-volatile storage mentioned here refers to PCM and Flash. Non-volatile memory, as the back-end expansion memory of DRAM, provides the scalability support of the hierarchical memory architecture, so that the respective advantages can be maximized To get full play, and avoid their own disadvantages, to provide a hybrid memory system with excellent overall performance.

[0018] See also attached figure 2 , The heterogeneous hybrid hierarchical memory device architectu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More