Chip packaging method and chip packaging structure

A chip packaging and chip technology, applied in the field of chip packaging method and chip packaging structure, can solve the problems of packaging quality and packaging structure integration degree to be improved, and achieve the effect of avoiding the problem of alignment deviation, simple forming process and stable combination.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] As mentioned in the background, the packaging quality of the existing fan-out wafer level packaging method and the integration degree of the formed packaging structure still need to be improved.

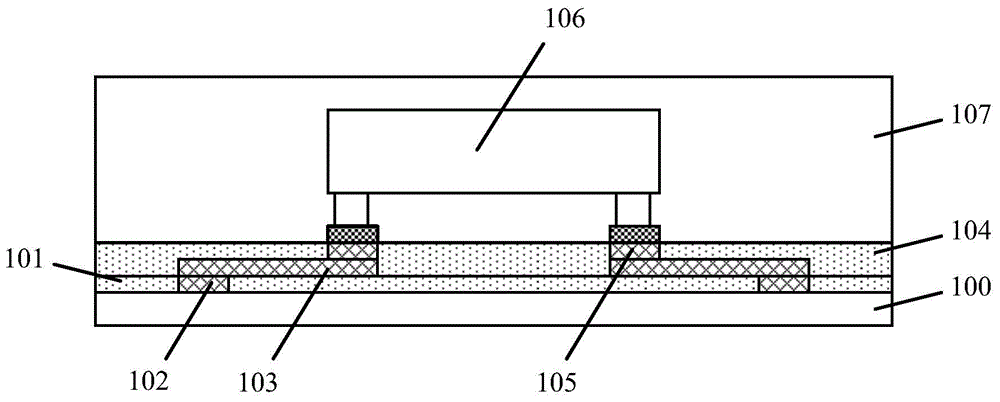

[0043] Please refer to figure 1 , figure 1 It is an embodiment of a fan-out wafer level packaging structure, including: a carrier 100; a release film and a first dielectric layer 101 located on the surface of the carrier 100; a first opening located in the first dielectric layer 101; a first opening located in the first dielectric layer 101; The substrate end metal electrode 102 in the opening; the wiring layer 103 located on the surface of the first dielectric layer 101; the second dielectric layer 104 located on the surface of the wiring layer 103, the substrate end metal electrode 102 and the first dielectric layer 101, the There is a second opening in the second dielectric layer 104; the chip-side metal electrode 105 positioned in the second opening; the functional surfac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More