Write message prospect processing method and device facing board-level high-speed bus

A high-speed bus and processing method technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems that cannot really eliminate the delay of write request message verification, increase the complexity of hardware design, etc., and achieve the reduction of message processing delay , the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

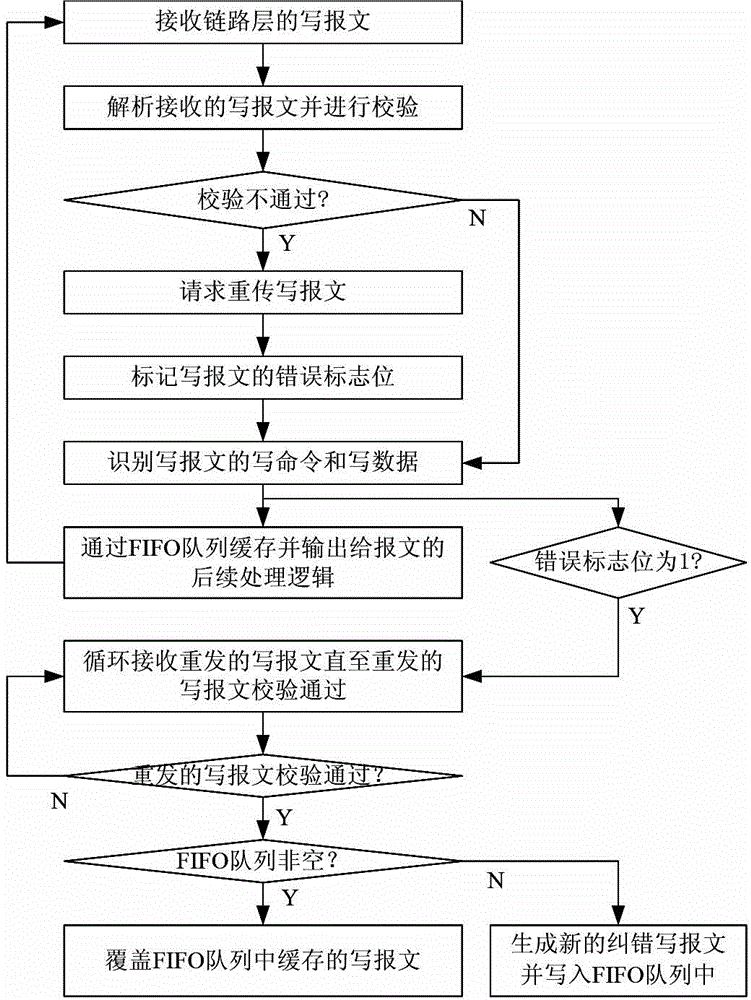

[0033] Such as figure 1 As shown, the steps of the forward-looking processing method for writing messages oriented to the board-level high-speed bus in this embodiment include:

[0034] 1) Receive the write message of the link layer, analyze the received write message and perform verification, if the verification fails, request retransmission of the write message, and mark the error flag Error of the write message as 1;

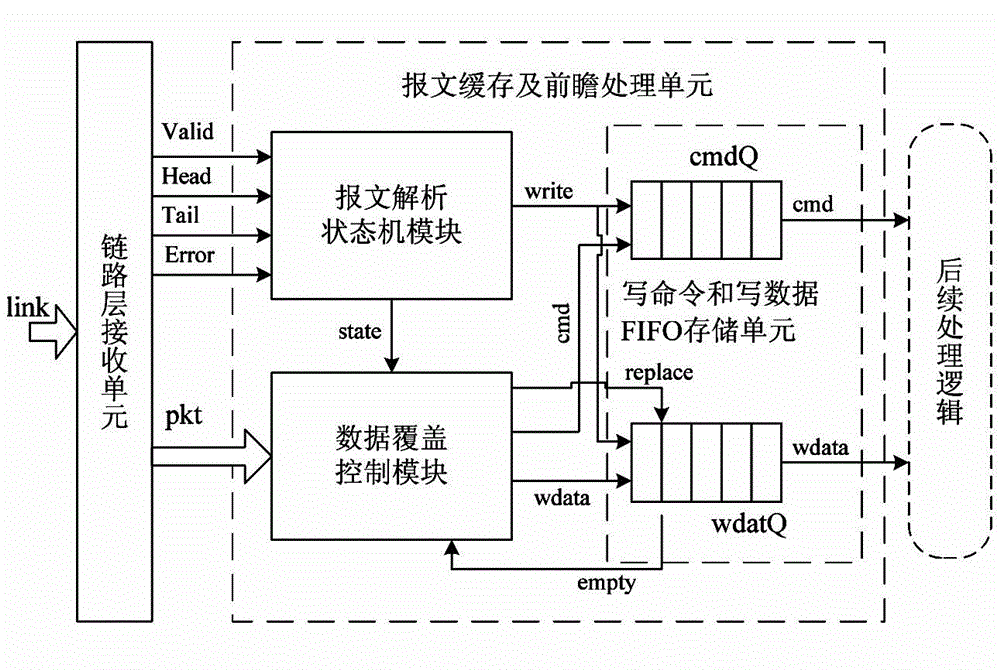

[0035] 2) Perform boundary judgment on the received write message, identify the write command cmd and write data wdata of the write message, and directly cache and output the write command cmd and write data wdata through the FIFO queue without distinguishing whether the message has passed the verification For the follow-up processing logic of the message; at the same time, the error flag bit Error of the write message is detected. If the error flag bit Error is 1, the retransmitted write message is received in a loop until the retransmitted write message pas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More