A clock control method and device

A clock control and clock technology, applied in the direction of data processing power supply, signal generation/distribution, etc., can solve problems such as increasing software complexity and affecting chip performance, achieving the effect of increasing reusability, improving processing performance, and reducing software complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

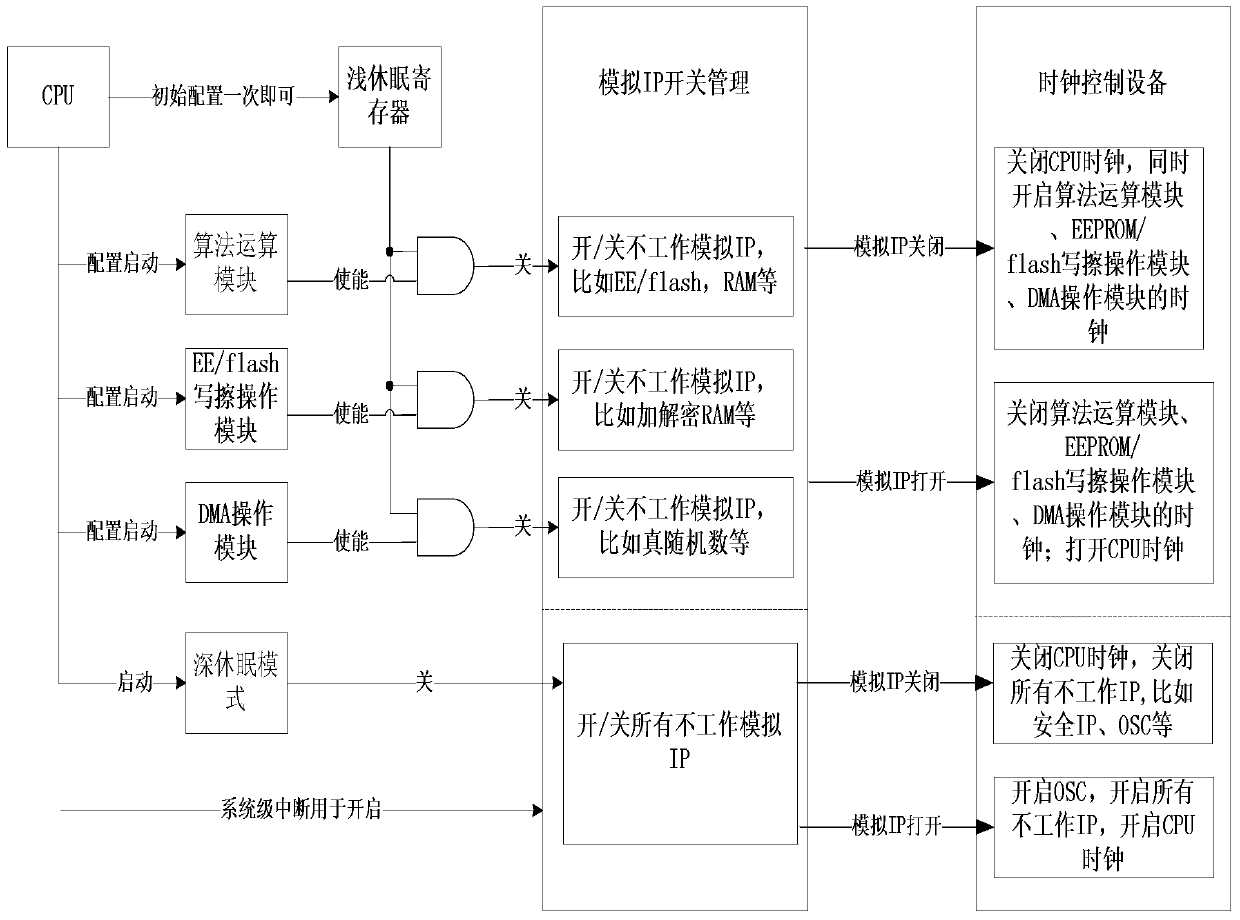

[0026] Hereinafter, the present invention will be described in detail with reference to the drawings and examples. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

[0027] like image 3 As shown, it includes: CPU, shallow sleep register, algorithm operation module, EEPROM / flash write and erase operation module, DMA (Direct Memory Access, memory direct access) operation module, deep sleep mode, analog IP switch management, clock control device.

[0028] Pre-configure the clock control strategy in the shallow sleep register;

[0029] When the business module is running, the clock control device closes the non-working analog IP in the light sleep mode according to the clock control strategy obtained from the light sleep register;

[0030] Turning off the analog IP that does not work in shallow sleep mode includes: turning off the CPU clock, turning on the clock o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More