Array substrate, preparation method thereof and display device

A technology of an array substrate and a manufacturing method, which is applied in the field of display, can solve problems such as potential differences, and achieve the effects of slowing down the flow speed, enhancing the blocking effect, and preventing ESD phenomena

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

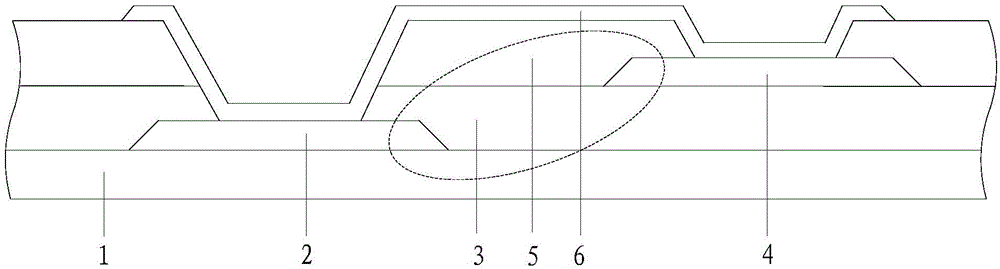

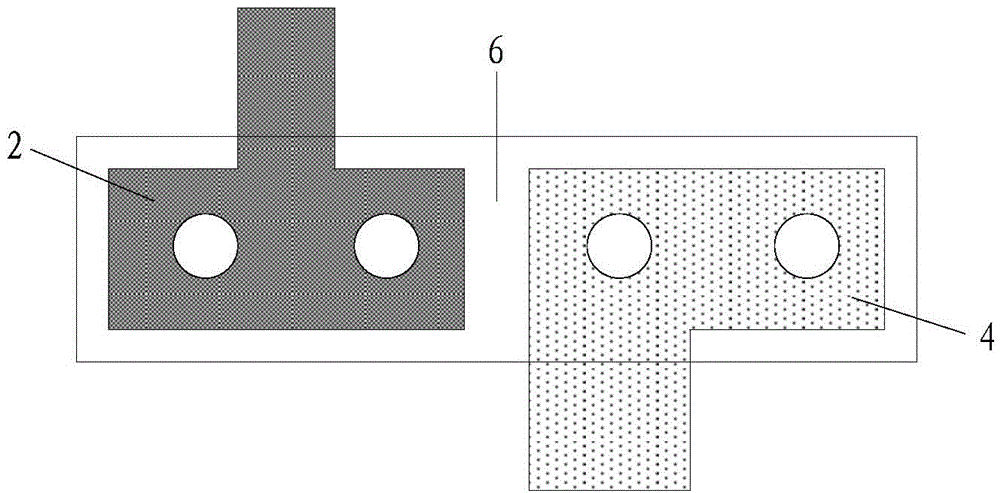

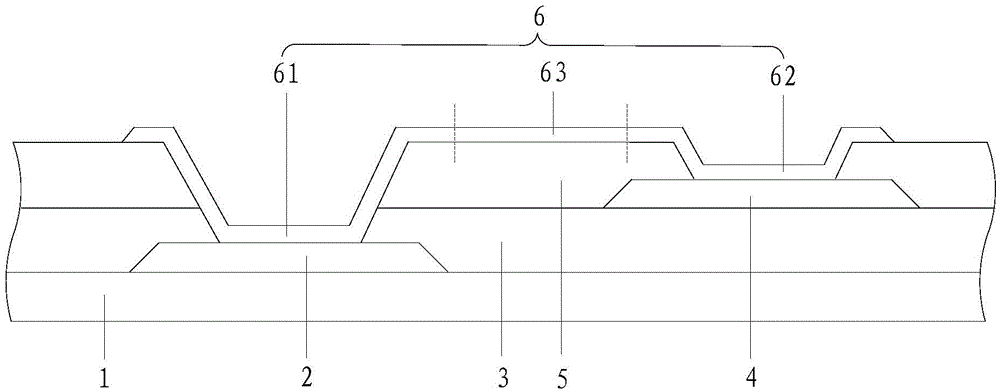

[0048] This embodiment provides an array substrate, such as Figure 2a and 2b As shown, it includes: a base substrate 1 , and a gate electrode layer, a first insulating layer 3 , a source-drain electrode layer, a second insulating layer 5 and a transparent conductive layer stacked on the base substrate 1 in sequence. The gate electrode layer includes a gate connection portion 2 , the source-drain electrode layer includes a source-drain connection portion 4 , and the transparent conductive layer includes a bridging portion 6 .

[0049] Wherein, the bridging portion 6 includes: a first electrode 61 electrically connected to the gate connecting portion 2; a second electrode 62 electrically connected to the source-drain connecting portion 4; a connecting electrode 63, one end of which connecting electrode 63 is electrically connected to the first electrode 61. connected, and the other end is electrically connected to the second electrode 62.

[0050] Taking the surface perpendic...

Embodiment 2

[0066] Based on the technical solution provided by Embodiment 1, in this embodiment, a compensation electrode electrically connected to the bridge portion 6 is provided to enhance the connection between the gate connection portion 2 and the source-drain connection portion 4 after the electrostatic charge in the source-drain connection portion 4 is released. The conductive performance between the parts 4 compensates for the loss of the conductive performance between the gate connection part 2 and the source-drain connection part 4 caused by increasing the resistance of the bridge part 6 .

[0067] Specifically, such as Figure 3a and Figure 3b As shown, the array substrate provided in this embodiment further includes: a third insulating layer 9 covering the transparent conductive layer; a third via hole 11 penetrating through the third insulating layer 9 and located above the first electrode 61; penetrating through the third insulating layer 9 and the fourth via hole 12 locat...

Embodiment 3

[0073] Based on Embodiment 1, in this embodiment, a part of the source-drain electrode layer pattern to be connected in the source-drain electrode layer is used as the source-drain connection part, or a part of the gate electrode layer pattern to be connected in the gate electrode layer is used as the gate connection part, The occupied area of the pattern in the gate electrode layer and the pattern in the source-drain electrode layer that are electrically connected is reduced, and the structure of the array substrate is simplified.

[0074] The scheme of using a part of the pattern of the source-drain electrode layer to be connected as the source-drain connection part can specifically be as follows: Figure 4 As shown, the source-drain electrode layer also includes: a source-drain electrode layer pattern 13 to be connected, the source-drain electrode layer pattern 13 to be connected includes a source, a drain and a data line, and the second via hole 8 is located at the source...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More