Method for preventing punch through voltage between bit lines from decreasing and semiconductor memory

A punch-through voltage and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problems of reducing the punch-through voltage and not finding it, and achieve the effect of increasing the resistance and avoiding the reduction of the punch-through voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

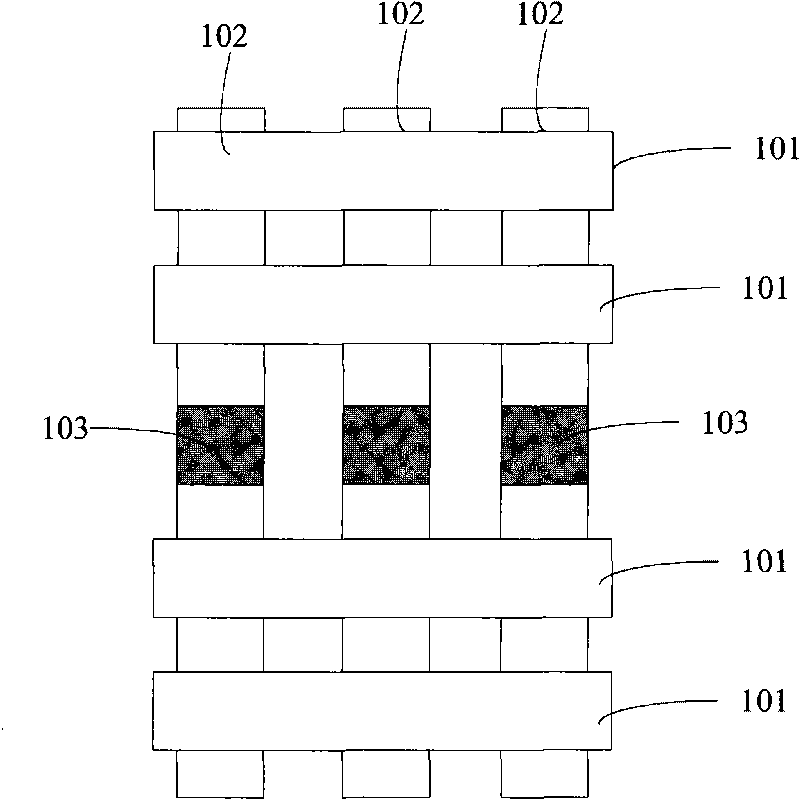

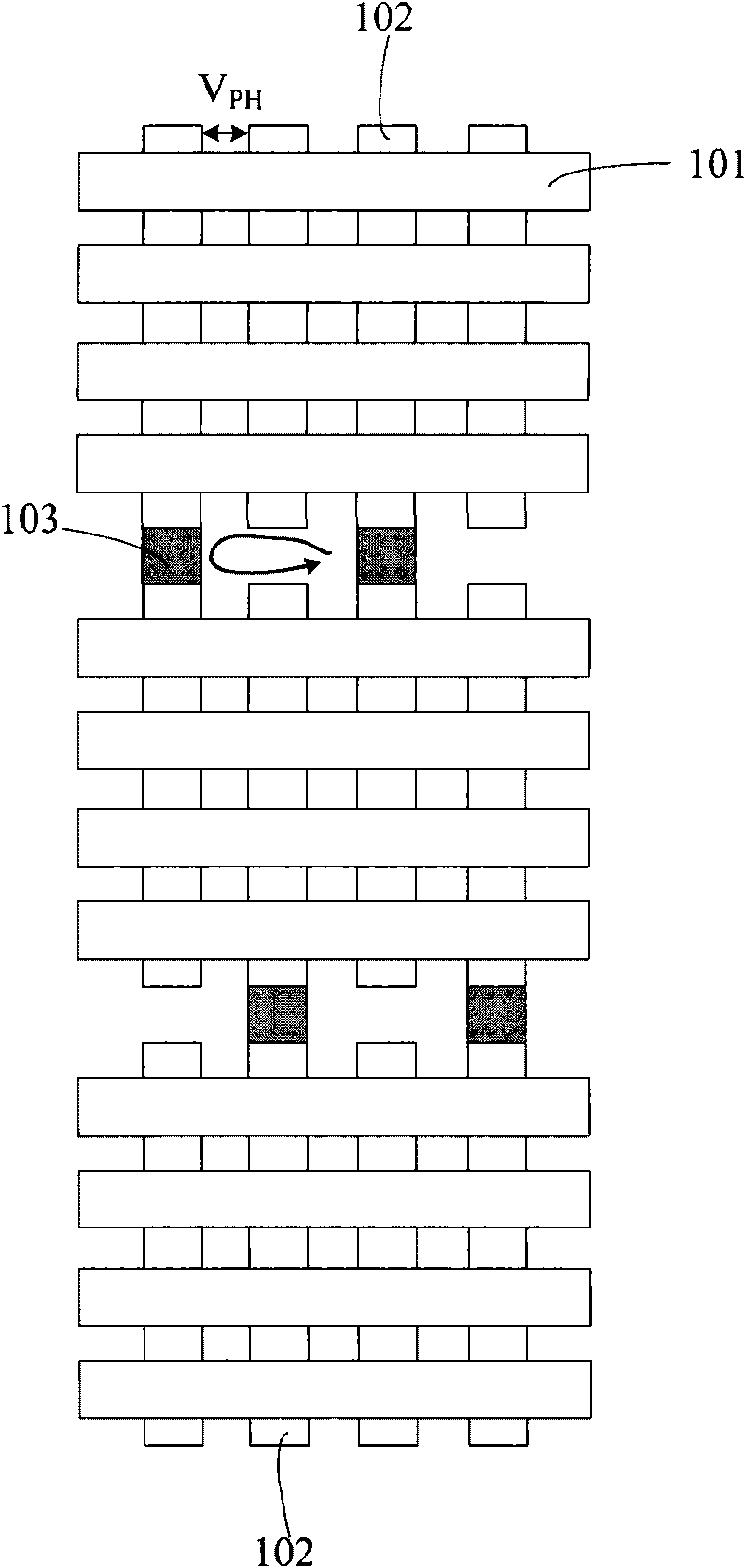

[0032] The present invention increases the doping concentration in the semiconductor substrate of the ion-doped region by forming an ion-doped region opposite to the conductivity type of the source / drain in the region between the closest word lines in the adjacent memory array , and the resistance between the bit lines in the semiconductor substrate is increased, thereby avoiding the defect that leakage current channels appear in the contact hole area of the bit lines in the prior art, thereby reducing the punch-through voltage between adjacent bit lines.

[0033] Below by describing specific embodiment in detail according to accompanying drawing, above-mentioned object and advantage of the present invention will be clearer:

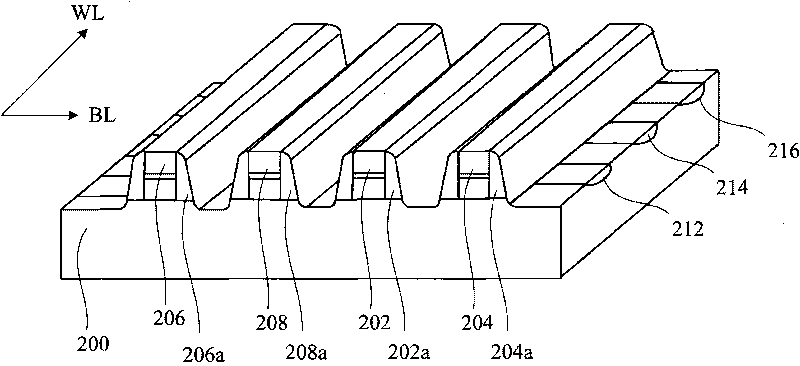

[0034] The present invention firstly provides a method for preventing the drop-through voltage between the bit lines of the memory, referring to Figure 4 , comprising: performing step S11, providing a semiconductor substrate, in which word lines are f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More