Method and system for implementing 10gbase-x4 PCS architecture using 20bits data interface

A data interface and data technology, applied in the field of network communication, can solve the problems of high clock frequency, increase chip power consumption, etc., and achieve the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0080] The present invention will be described in detail below in conjunction with specific embodiments shown in the accompanying drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

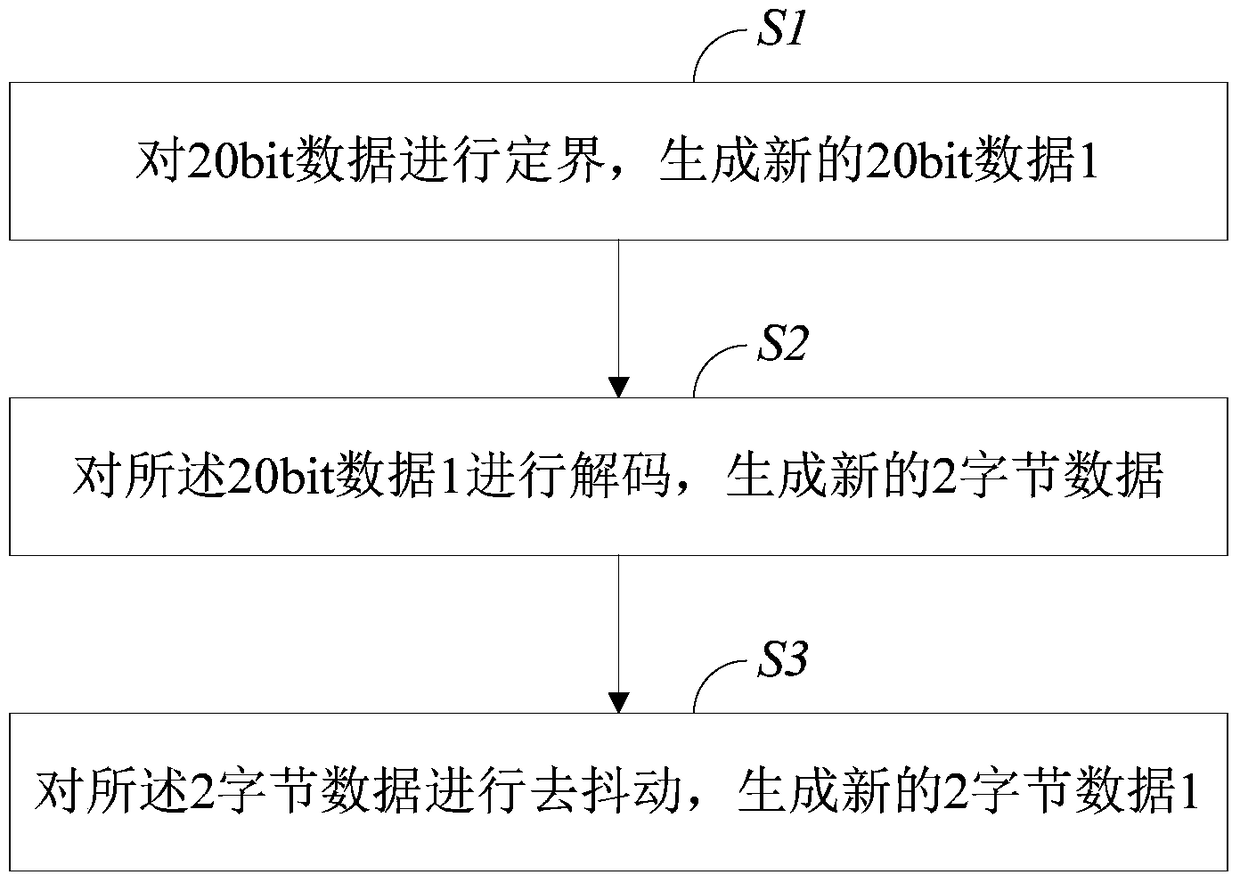

[0081] Such as Figure 1A , Figure 1B As shown, in an embodiment of the present invention, a method for implementing a 10GBase-X4 PCS architecture using a 20bits data interface is provided.

[0082] The working clock of the 10GBase-X4 PCS framework of the present invention is 156.25MHz.

[0083] In this embodiment, the method includes:

[0084] In the receive direction of data,

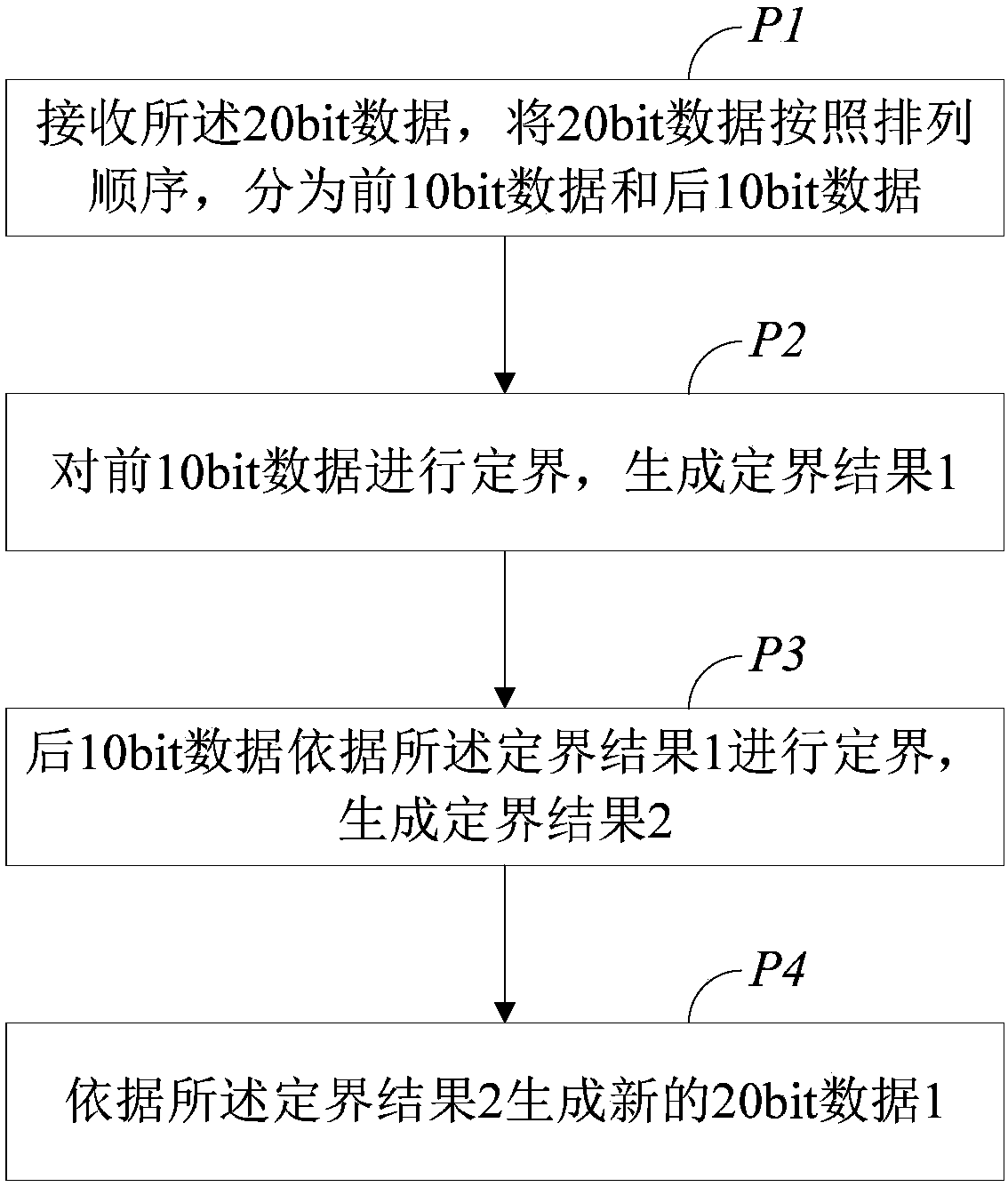

[0085] S1. Demarcate the 20bit data to generate new 20bit data 1;

[0086] S2. Decoding the 20-bit data 1 to generate new 2-byte data;

[0087] S3. De-jittering the 2-byte data to generate new 2-byte data 1;

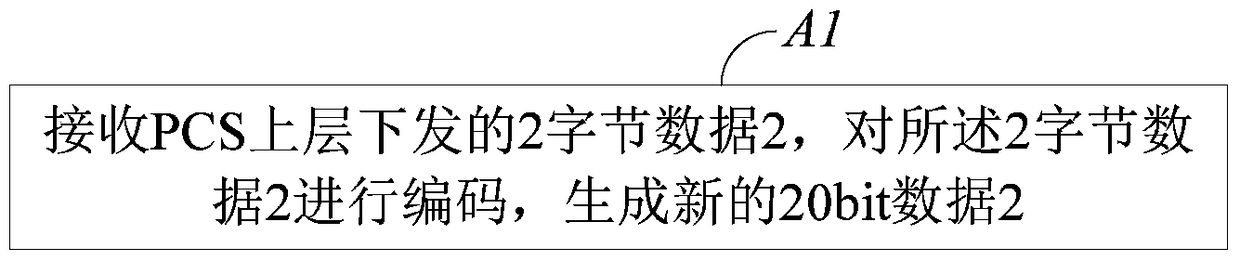

[0088] In...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com