ESD detection method and device, and ESD debugging method and device

A detection method and technology of detection device, which are applied in the direction of measurement device, electronic circuit test, measurement of electricity, etc., can solve the problems of low detection efficiency and long time, and achieve the effect of shortening detection time, fast circuit characteristics, and saving detection time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In the prior art solution, the ESD detection of the chip is usually performed at the device level of the chip. Because the chip contains a lot of devices, the current cutting-edge chip can include more than 1,000,000,000 devices, so it takes a very long time to complete the ESD detection of the whole chip, and the detection efficiency is low. In addition, if the input file is not completely pre-tested before the test is performed, or problems such as program hanged occur during the test, it will further cause unnecessary waste of test time.

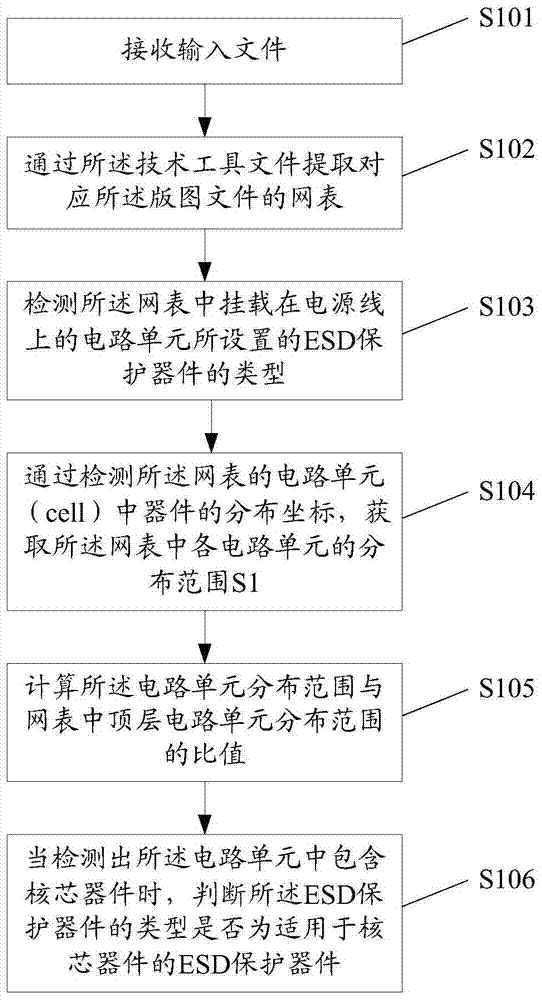

[0046] In the embodiment of the present invention, by detecting the distribution range of each circuit unit in the netlist and the top-level circuit unit, such as the comparison of the area, the detection at the circuit unit level is used instead of the detection at the device level, and it is possible to quickly determine whether the currently loaded circuit unit is Including core devices, the detection time can be reduced exponen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More