Method of forming mos transistor and method of forming cmos transistor

A MOS transistor and transistor technology, applied in the formation of MOS transistors and CMOS transistors, can solve the problems of performance degradation of semiconductor devices and differences in threshold voltages of different MOS transistors, and prevent the generation of pollutants, low electron temperature, and damage small effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

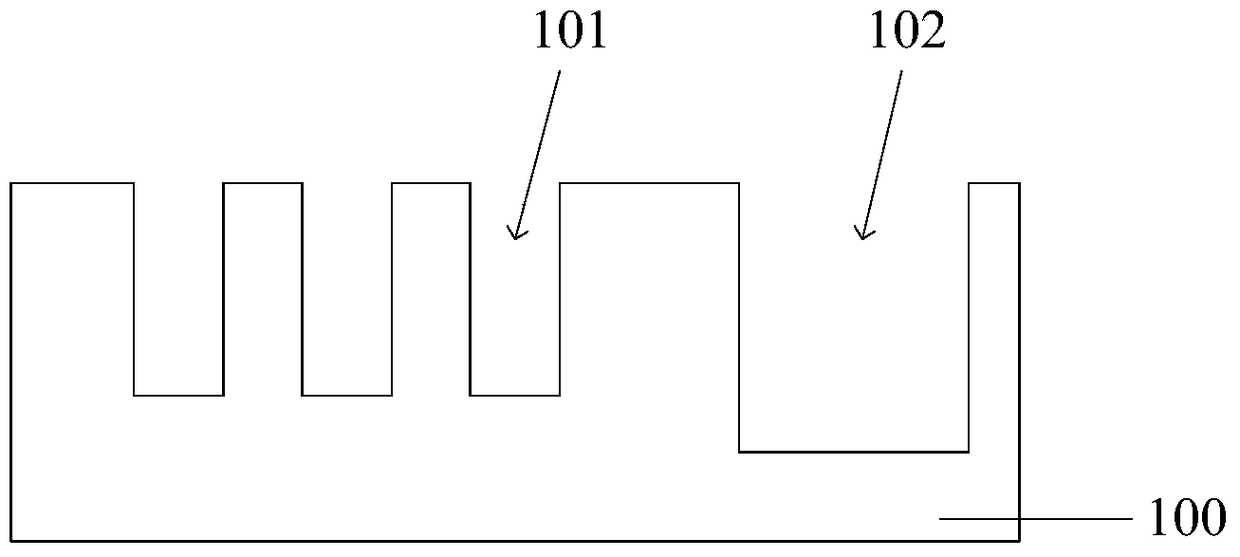

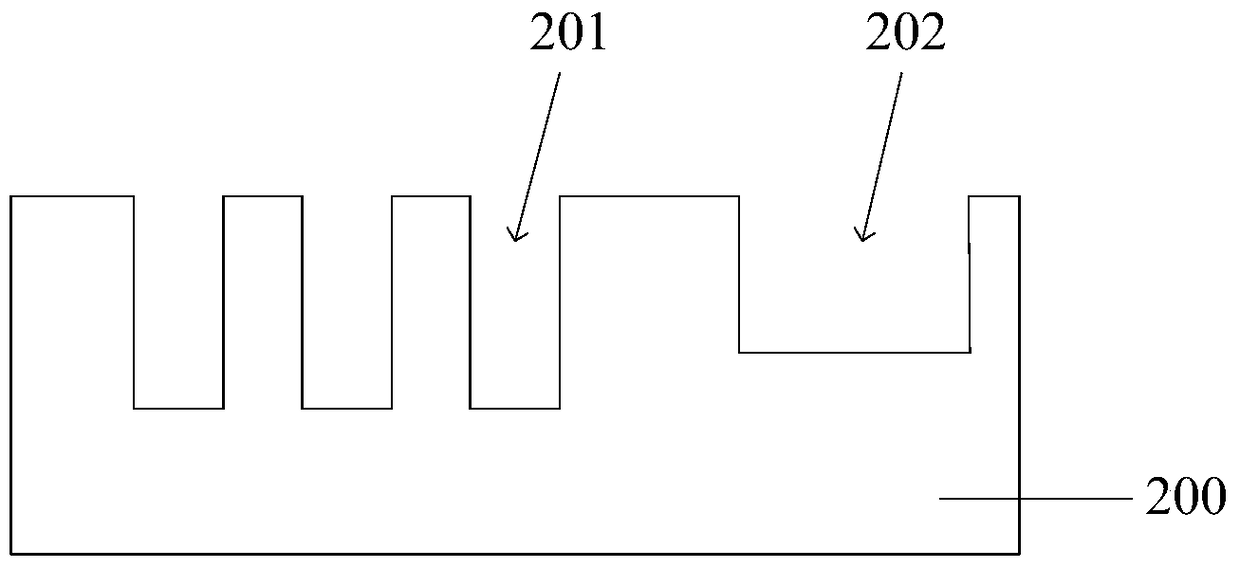

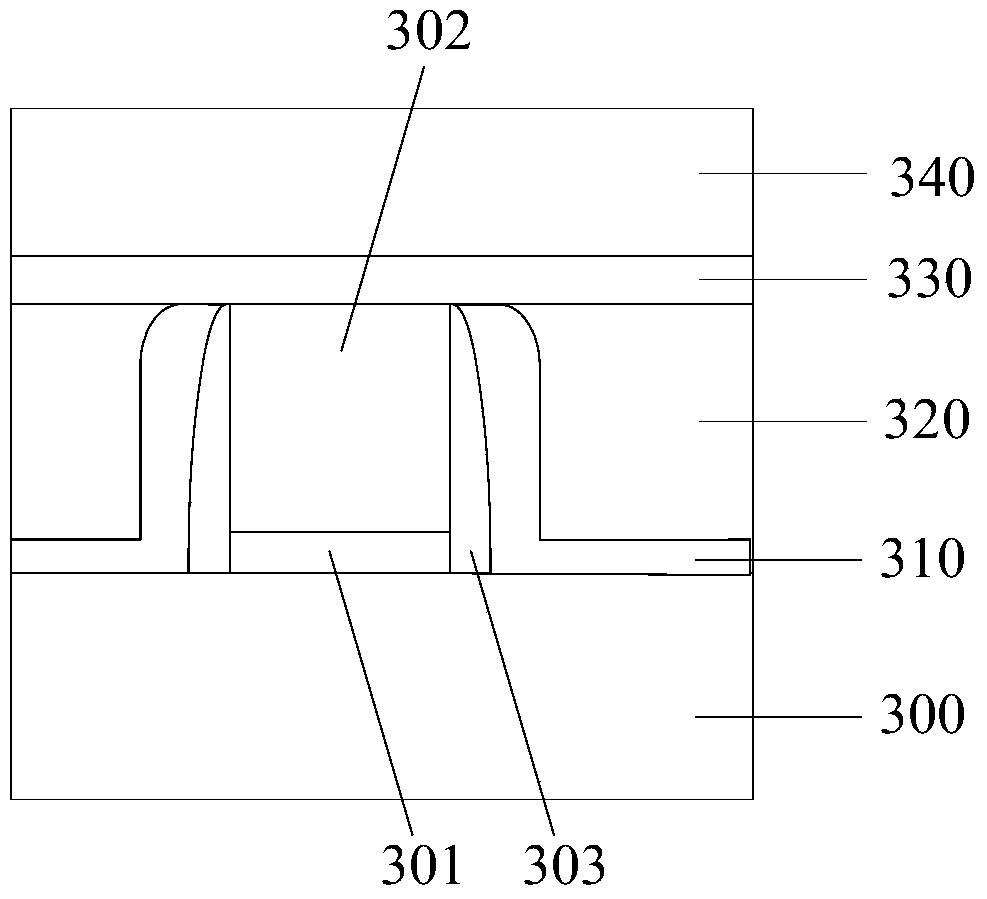

[0052] As described in the background art, the existing method uses a continuous wave plasma etching process to remove the dummy gate. Since the continuous wave plasma has different etching rates for dummy gates of different widths, the formed opening depths are different. Various problems, such as unclean removal of the dummy gate in some locations, and damage to the structure under the dummy gate in some locations, occur.

[0053] For this reason, the present invention proposes to adopt a pulse plasma etching process to remove the dummy gate to form an opening. Since the pulse plasma is etched at a certain frequency, there is a short pause time after each etching. During the pause time, the etching product It can be evenly dispersed and provide the same environment for the next frequency of etching, thereby ensuring that the formed openings have the same depth.

[0054] In order to make the above-mentioned objects, features and advantages of the present invention more obvious and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More