Three-dimensional laminated semiconductor structure and manufacturing method thereof

A semiconductor and stacking technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as bending and collapse of composite layer columns

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

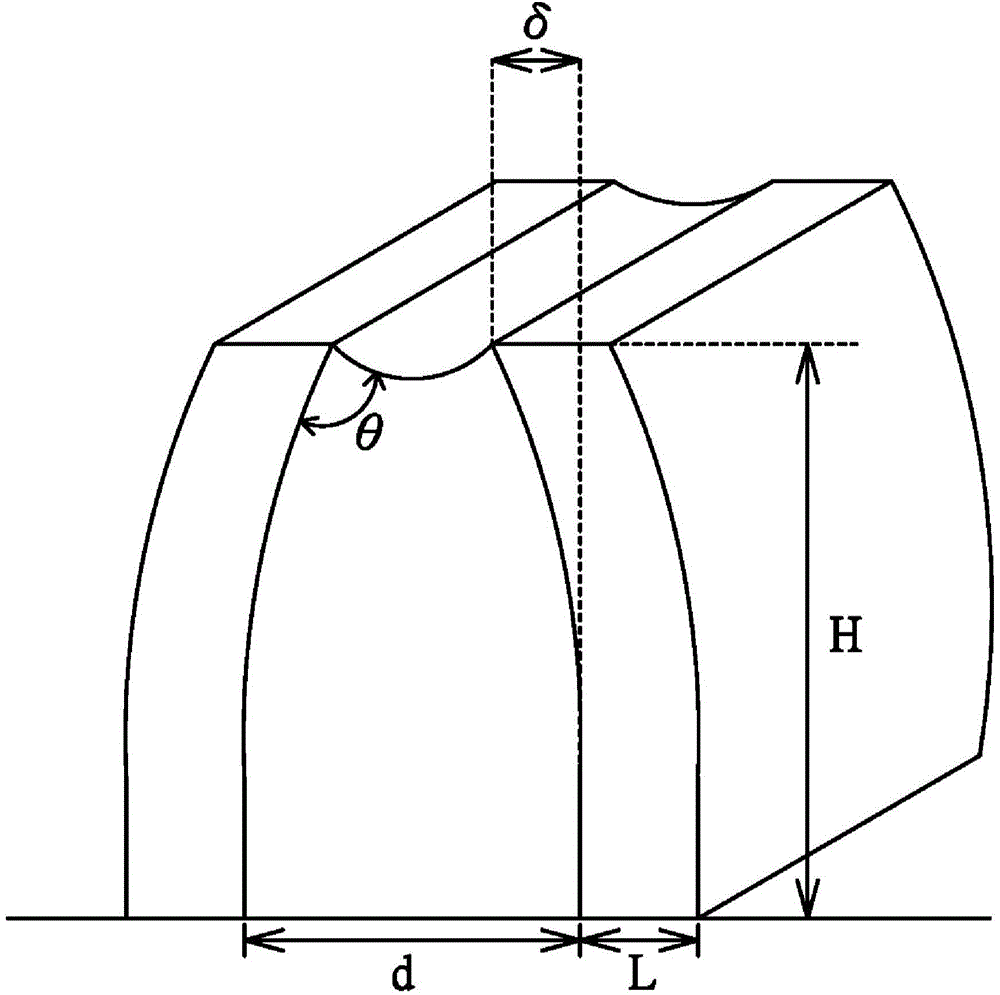

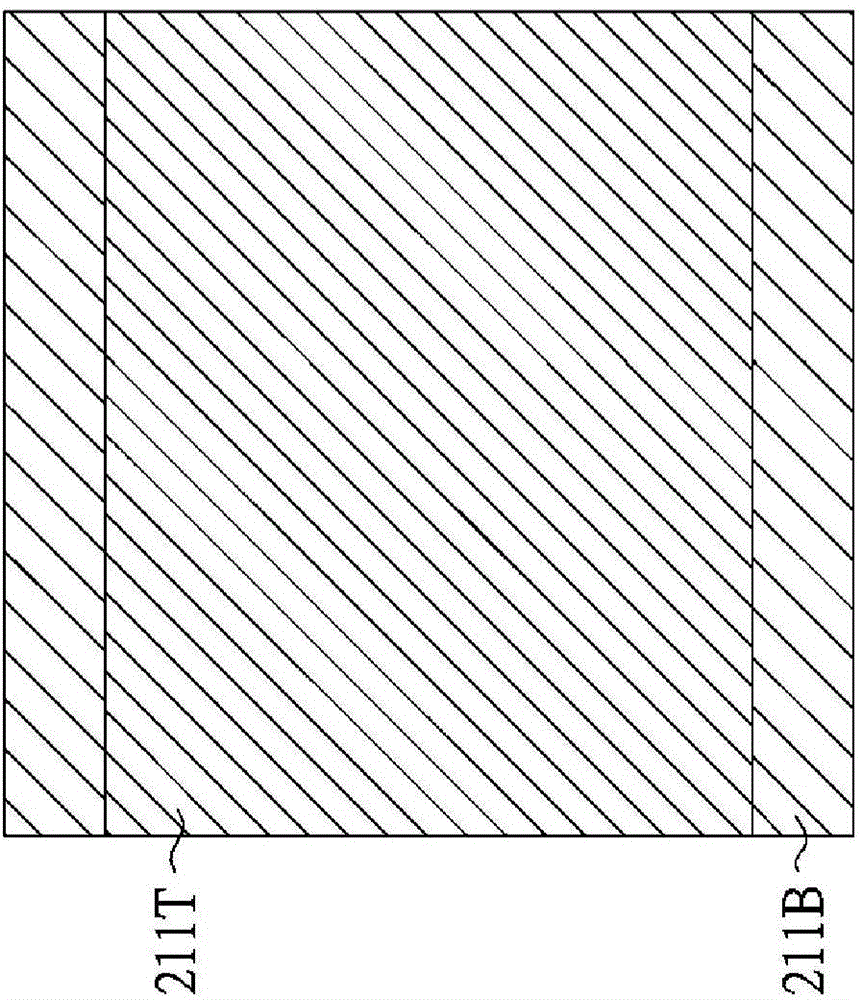

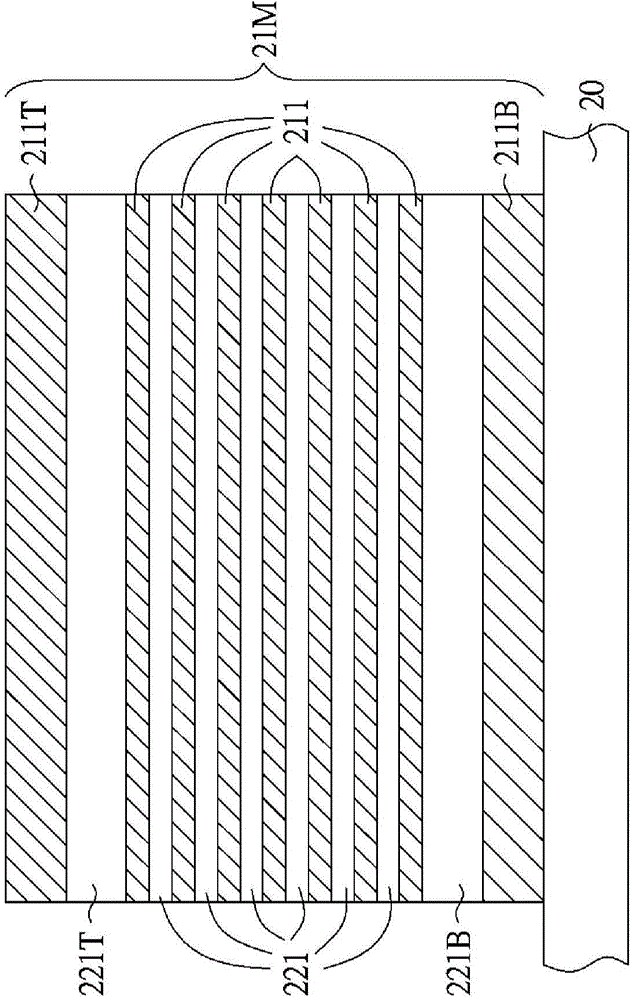

[0058]In the embodiments of the present invention, a method for manufacturing a three-dimensional stacked semiconductor structure and the resulting structure are proposed. In the manufacturing method of the three-dimensional stacked semiconductor structure proposed in the embodiment, a multi-layer (amulti-layer) includes a plurality of first dielectric layers and a plurality of second dielectric layers alternately stacked on a substrate, and then patterned Composite layers to form a plurality of first patterned stacks and a plurality of spaces between the first patterned stacks. In an embodiment, the first dielectric layer is compressive layers with compressive stress, and the second dielectric layer is tensile layers with tensile stress. A portion of the second dielectric layer of one of the first patterned stacks is then removed, and the removed portion is replaced with a conductor. The three-dimensional stacked semiconductor structure manufactured by the manufacturing meth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More