Fabrication method of multi-layer printed circuit board (PCB) and multi-layer PCB

A manufacturing method and inner layer technology, which are applied in the directions of multi-layer circuit manufacturing, printed circuit manufacturing, printed circuit, etc., can solve the problems of high-density interconnection PCB design of difficult-to-socket components, and achieve convenient high-density interconnection PCB, The effect of reducing manufacturing cost and increasing wiring area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

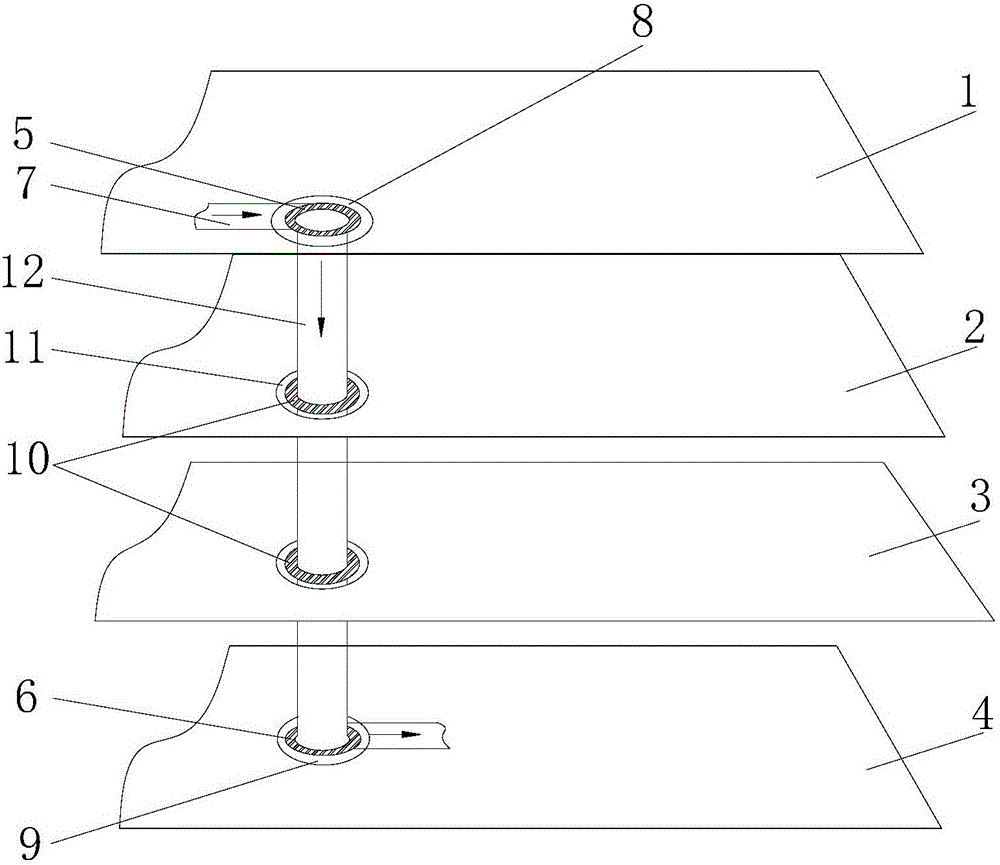

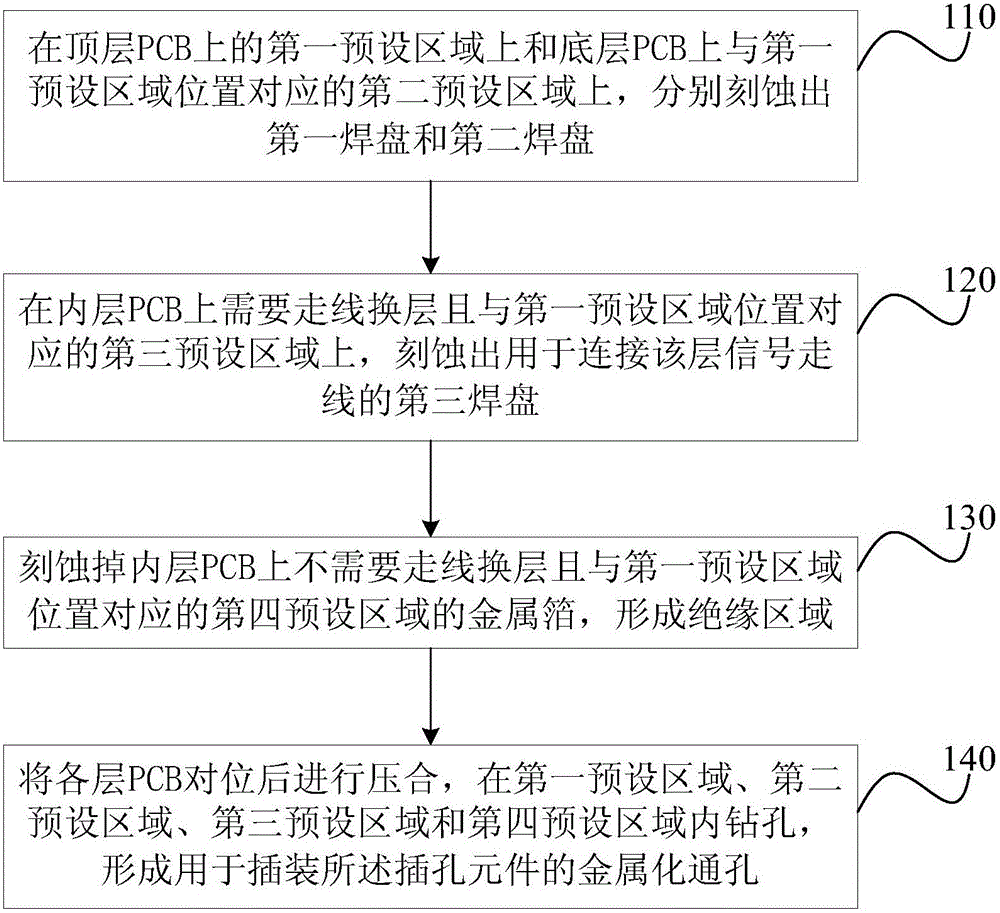

[0026] figure 2 It is a schematic flowchart of the manufacturing method of the multi-layer PCB provided by Embodiment 1 of the present invention. This method is suitable for making four-layer, six-layer and eight-layer multi-layer single-sided or double-sided PCBs, such as figure 1 As shown, the method includes:

[0027] Step 110 , respectively etching a first pad and a second pad on the first predetermined area on the top layer PCB and on the second predetermined area on the bottom PCB corresponding to the position of the first predetermined area.

[0028] Exemplarily, a plurality of PCBs with metal foils of a preset size are provided according to the customer's requirements, the graphics required by the customer are transferred to the PCB, the graphics include circuit graphics and pad graphics, and non-graphic parts are etched away. Specifically, on the first predetermined area on the top PCB and on the second predetermined area corresponding to the position of the first ...

Embodiment 2

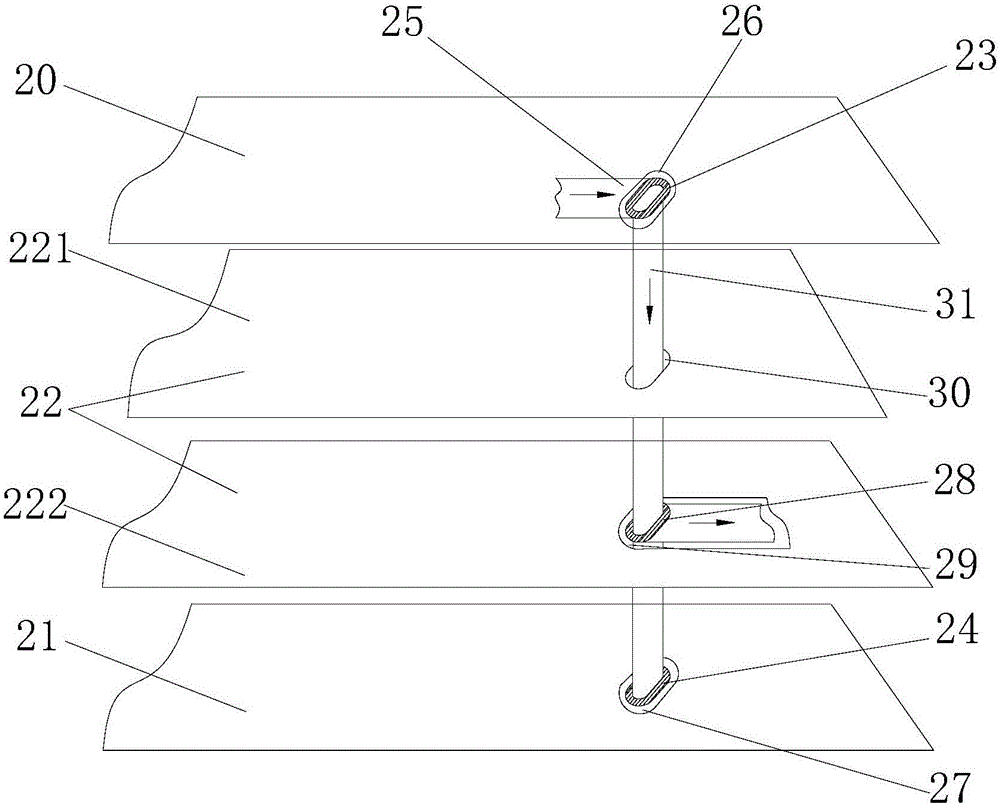

[0045] image 3 It is a schematic diagram of the three-dimensional structure of the multilayer PCB provided by Embodiment 2 of the present invention. This embodiment takes a four-layer PCB as an example for illustration, as image 3 As shown, the multilayer PCB includes a top layer PCB20, an inner layer PCB22 and a bottom layer PCB21;

[0046] Wherein, the first preset area on the top layer PCB20 and the second preset area corresponding to the position of the first preset area on the bottom layer PCB21 are respectively etched with a first pad 23 and a second pad 24, the first pad 23 and the second pad 24 are used for soldering the pins of the jack element, or for soldering the pins of the jack element and the signal trace 25 connecting the layer where the first pad 23 and the second pad 24 are located, the first A first insulating gap 26 and a second insulating gap 27 are respectively formed around the pad 23 and the second pad 24;

[0047] Located on the inner layer PCB22,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More