DFI standard DDR3 controller based on FPGA

A technology of controller and protocol controller, which is applied in the direction of instruments, electrical digital data processing, etc., to achieve the effect of reducing risks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

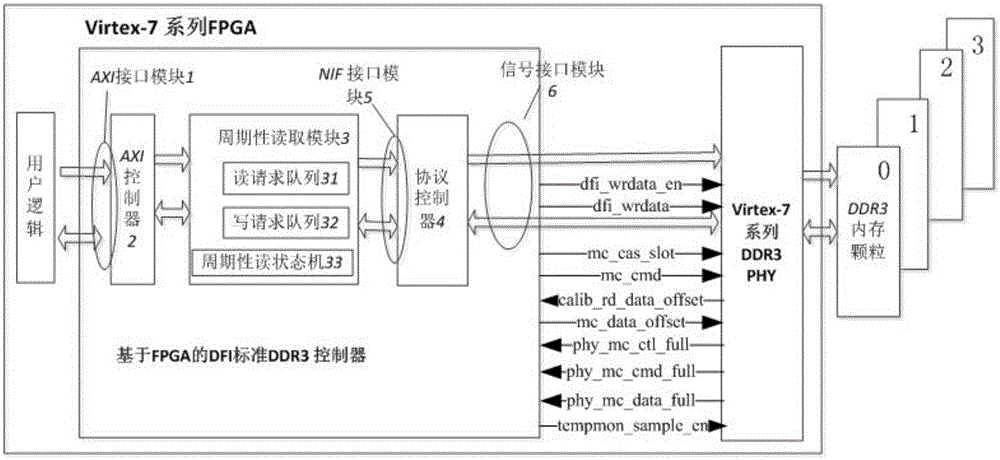

[0031] Such as figure 1 As shown, an FPGA-based DFI standard DDR3 controller includes an AXI interface module 1, an AXI controller 2, a periodic reading module 3, a protocol controller 4 and a signal interface module 6:

[0032] The AXI interface module 1, the AXI controller 2, the periodic reading module 3, the protocol controller 4 and the signal interface module 6 are electrically connected in sequence. The AXI controller 2 is a high-performance bus protocol (AdvancedeXtensibleInterface, AXI) controller. Optionally, the periodic reading module 3 and the protocol controller 4 are electrically connected through a NIF interface module.

[0033] The AXI interface module 1 is used to receive the user logic sent by the FPGA, and send the user logic to the AXI controller 2; it is also used to receive the DDR3 memory data forwarded by the AXI controller 2, and send the memory data to the FPGA.

[0034] The AXI controller 2 is used to convert the user logic into data in the AXI pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More