The realization method of image super-resolution based on fpga

A super-resolution and implementation method technology, applied in image data processing, image data processing, instruments, etc., can solve the problems of unsatisfactory super-resolution image effect, high complexity of high-order interpolation method and inconvenient hardware implementation, etc., to improve the image quality. Processing rate, achieve super-resolution effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

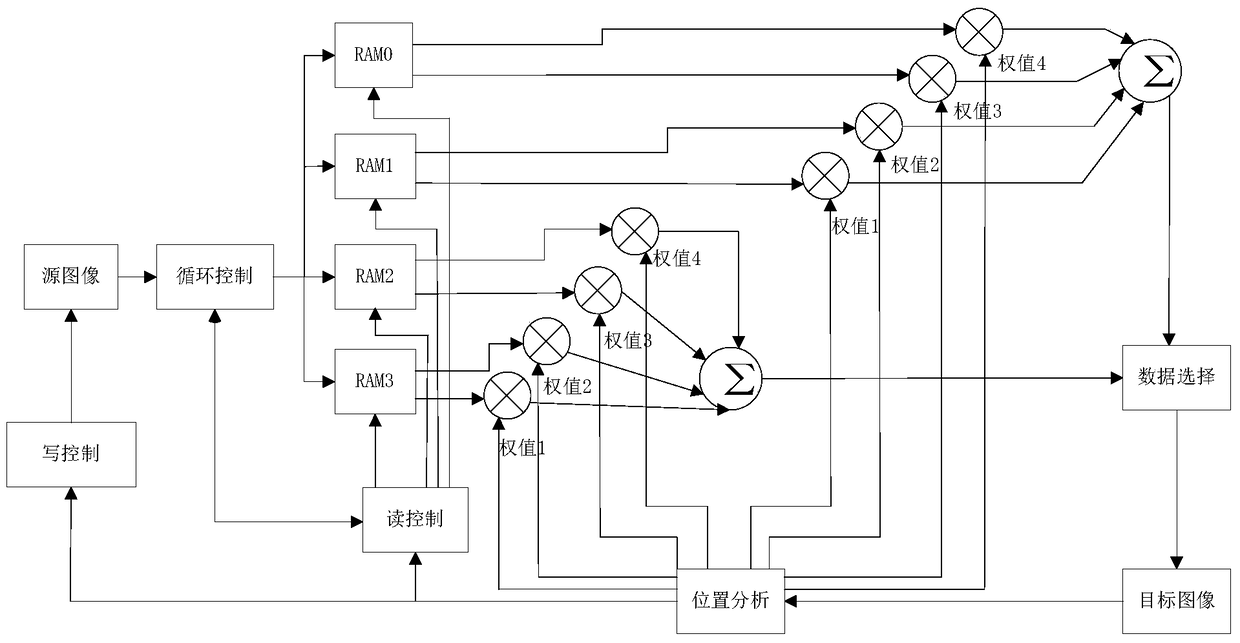

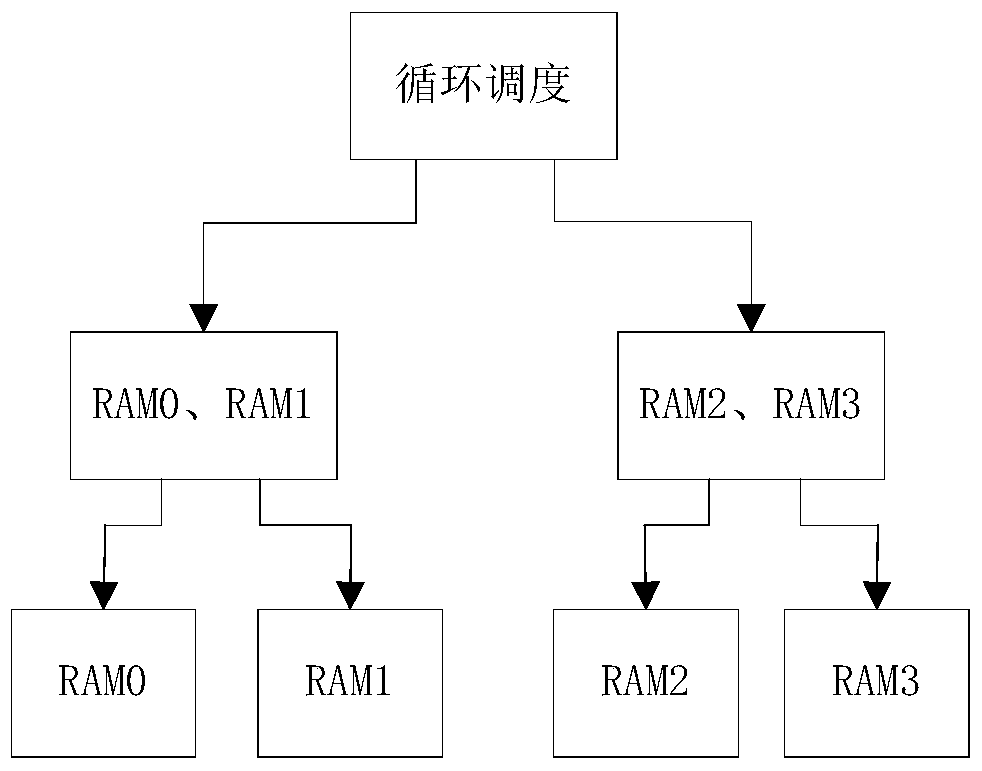

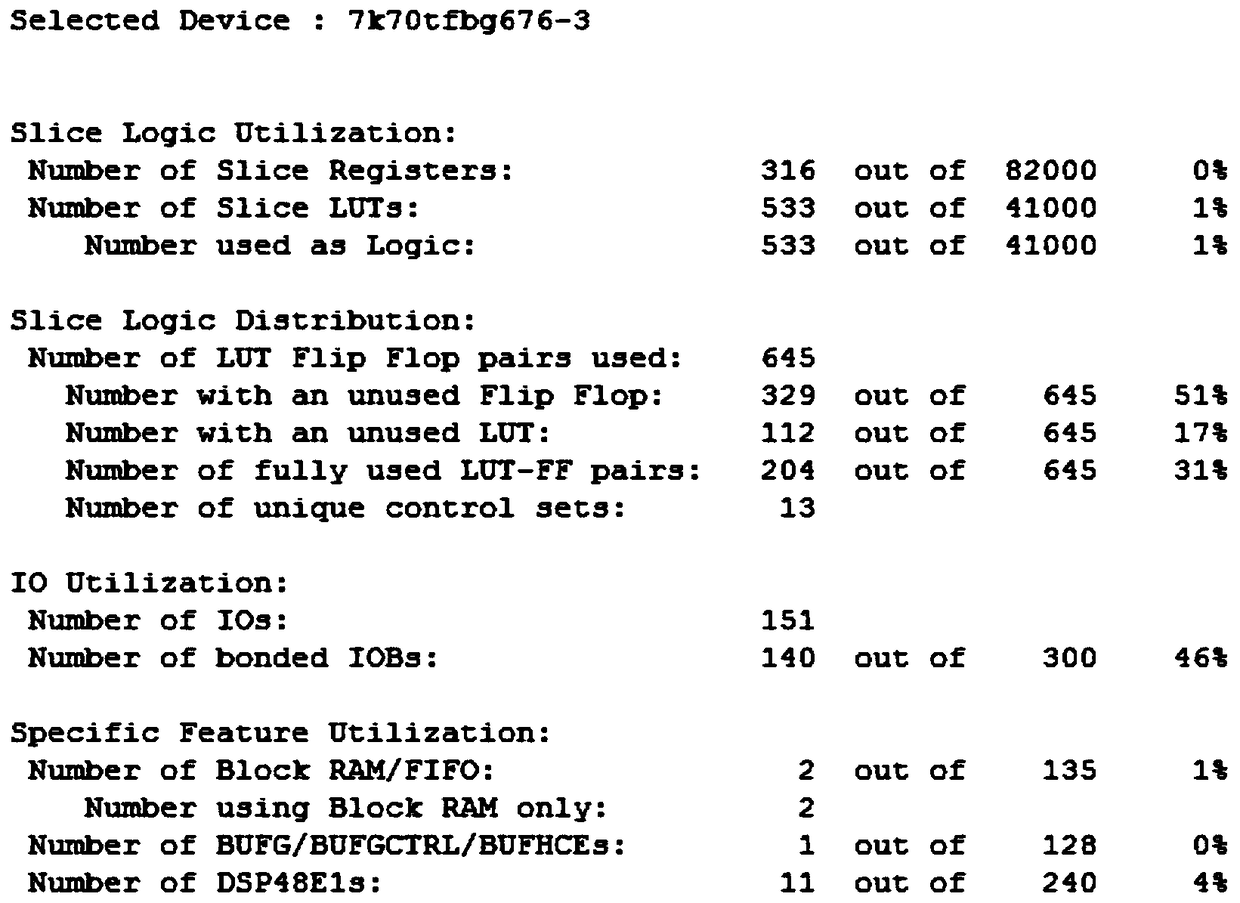

[0025] FPGA has two opposing performances: (1) It has parallel processing and pipeline technology, which can achieve high-performance processing, but M times the performance consumes M times logic; (2) has multiplexing technology, which can reduce logic, but control Complexity rises. Based on the functional characteristics of FPGA, the present invention proposes a two-level cycle scheduling mechanism based on single-input dual-output port RAM buffer to realize shared resource allocation and parallel pipeline processing. At the same time, Xilinx's FPGA is based on the LUT structure, which can realize floating-point operations and multiplication operations, but it will cause a serious waste of resources. In this paper, all floating-point numbers are integerized, and data operations are performed in the field of integers.

[0026] Bilinear interpolation determines a plane through four points, which is an over-constrained problem, so first-order interpolation on a rectangular gri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More