Wafer-level capacitive acceleration meter automatic testing system

An automatic test system and accelerometer technology, applied in the direction of speed/acceleration/shock measurement, test/calibration of speed/acceleration/shock measurement equipment, measurement device, etc. Test methods, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

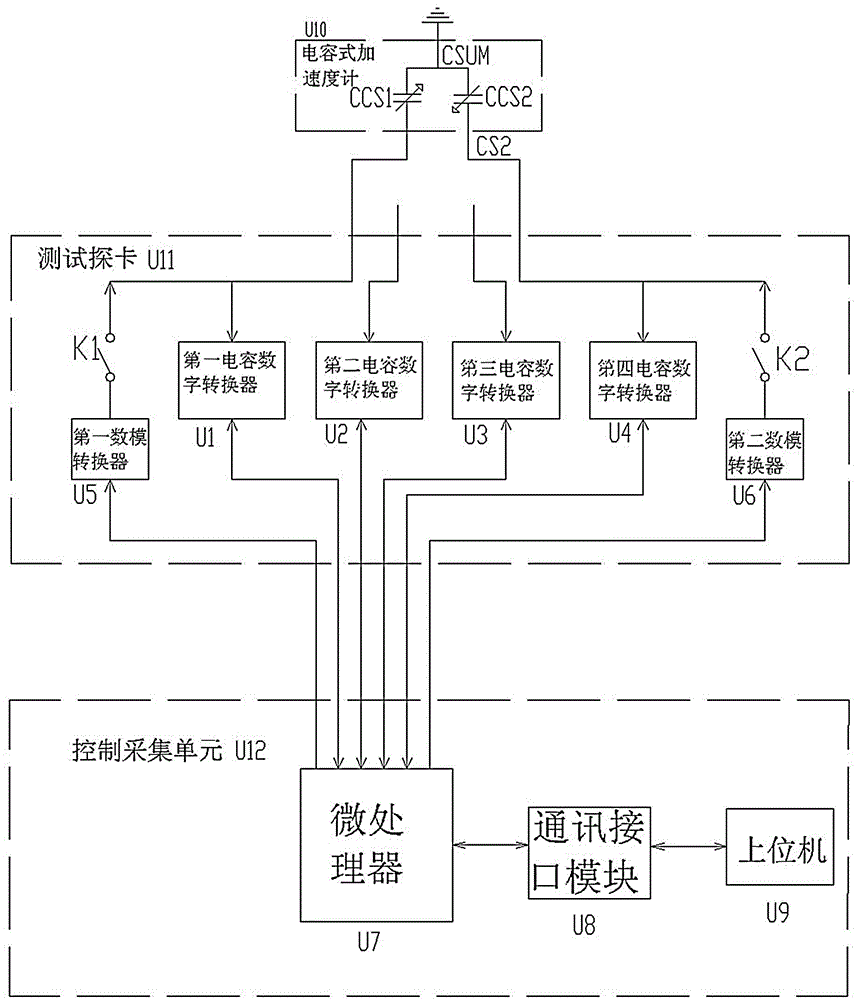

[0012] Such as figure 1 As shown, the present invention provides a wafer-level capacitive accelerometer automatic test system, including a microprocessor U7 and an upper computer U9 connected to the microprocessor U7 through a communication interface module U8, the microprocessor U7, the communication interface module U8 and the upper computer The machine U9 constitutes the control acquisition unit U12; the system also includes four capacitance-to-digital converters, that is, the first capacitance-to-digital converter U1, the second capacitance-to-digital converter U2, the third capacitance-to-digital converter U3, and the fourth capacitance-to-digital converter converter U4, the system also includes a first digital-to-analog converter U5, a second digital-to-analog converter U6, a first relay K1 and a second relay K2; the first relay K1 and the second relay K2 are respectively controlled by the microprocessor The switch U7 controls the on-off, that is, the output interface of...

Embodiment 2

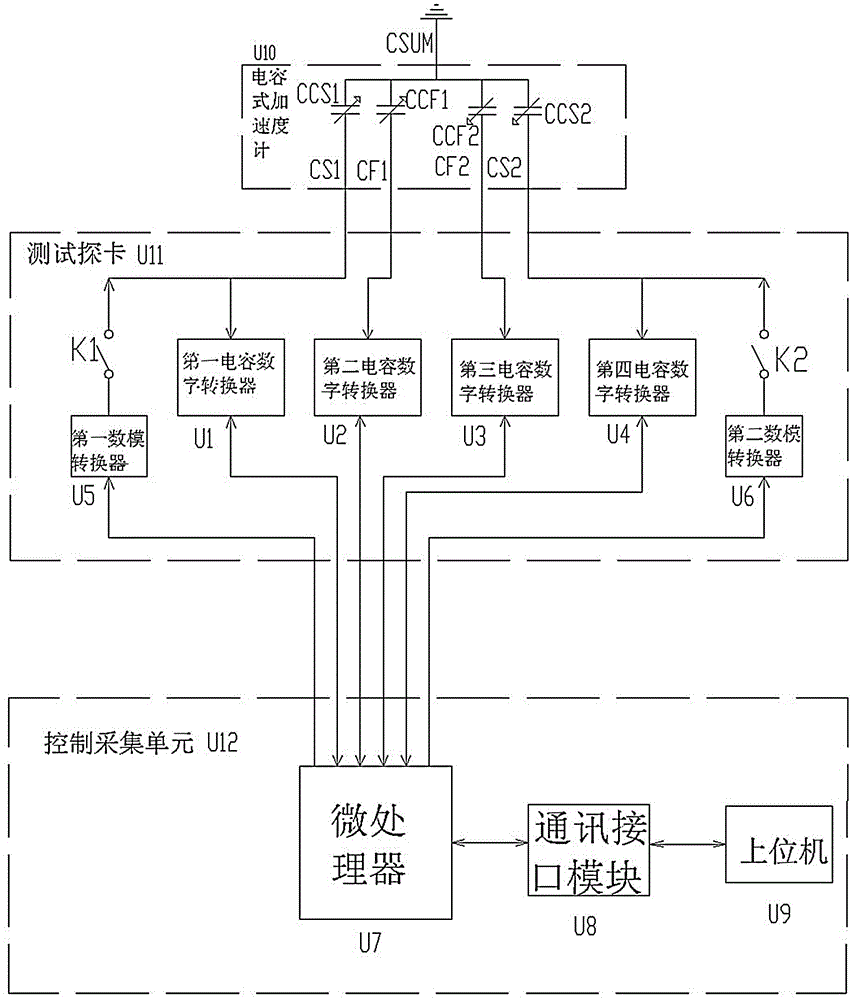

[0017] Such as figure 2 As shown, the structure of the wafer-level capacitive accelerometer automatic test system in this embodiment is basically the same as that in Embodiment 1, and also includes a microprocessor U7, a first capacitance-to-digital converter U1 to a fourth capacitance-to-digital converter U4, a second capacitance-to-digital converter A digital-to-analog converter U5, a second digital-to-analog converter U6, a first relay K1 and a second relay K2; the first relay K1 and the second relay K2 are respectively controlled on and off by the microprocessor U7, that is, the microprocessor The U7 output interface is respectively connected to the coils of the first relay K1 and the second relay K2 (not shown in the figure); the output interface of the microprocessor U7 is respectively connected to the input of the first digital-to-analog converter U5 and the second digital-to-analog converter U6 Interface, the output interface of the first digital-to-analog converter U...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More