A dual-bus memory controller

A memory controller, dual-bus technology, applied in instruments, electrical digital data processing, etc., can solve problems such as bus congestion and reduce memory access efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] It should be noted that, in the case of no conflict, the embodiments of the present invention and the features in the embodiments can be combined with each other.

[0038] The DFI mentioned in the present invention refers to DDR PHY Interface.

[0039] The present invention will be described in detail below with reference to the accompanying drawings and examples.

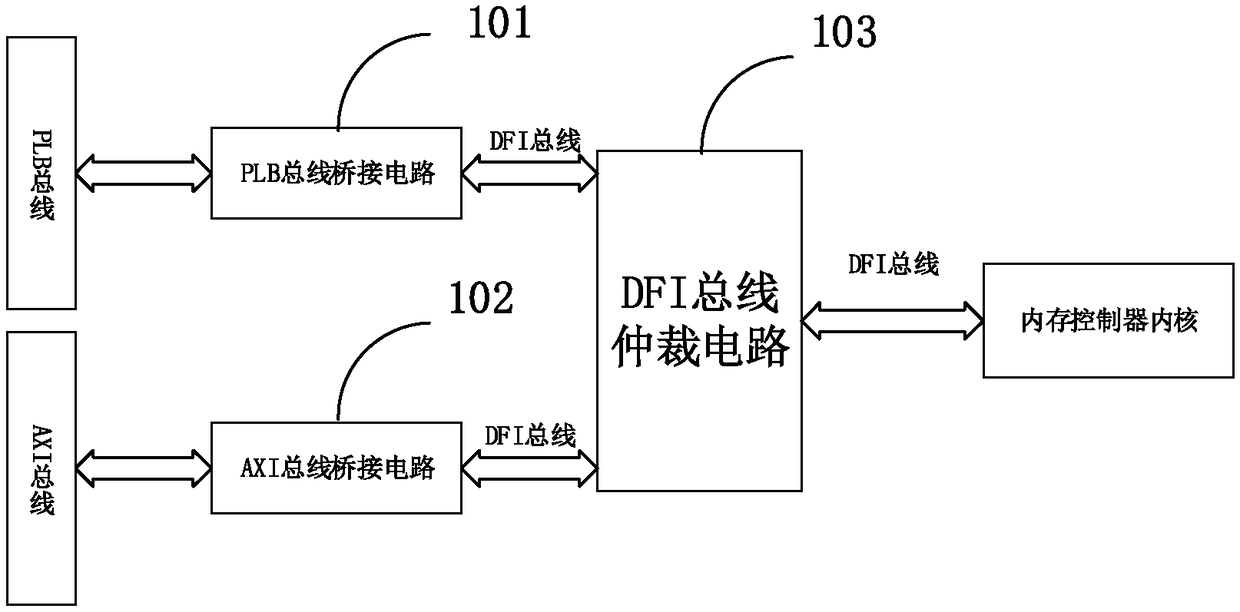

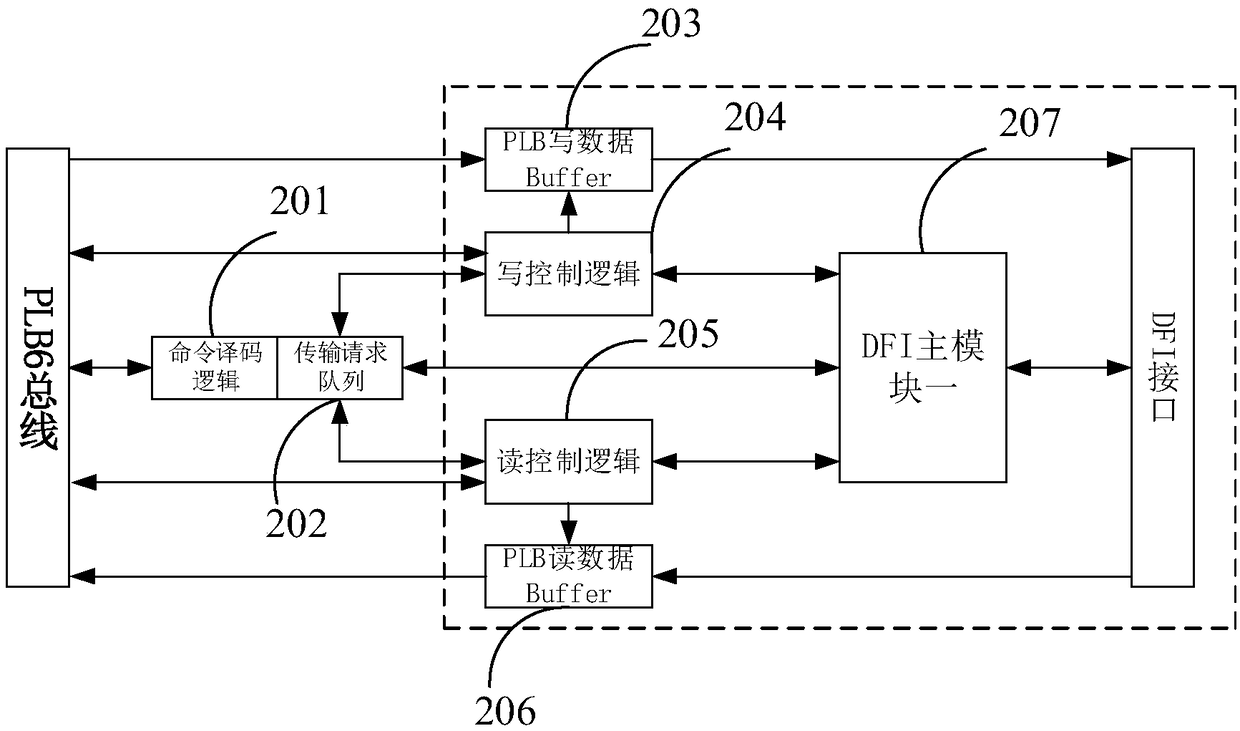

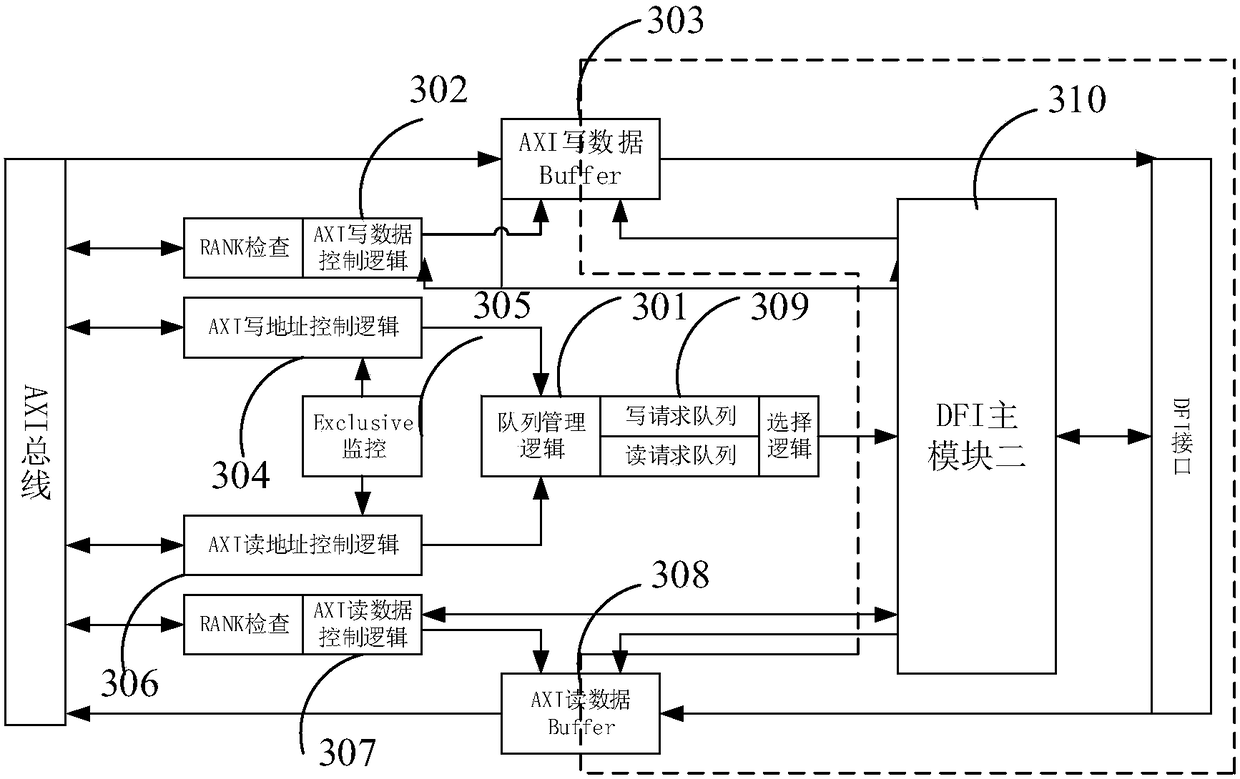

[0040] A dual-bus memory controller such as figure 1 As shown, it includes a PLB bus bridge circuit 101, an AXI bus bridge circuit 102, a DFI bus arbitration circuit 103 and a memory controller core MCP, the PLB bus bridge circuit 101 receives an access request of the PLB bus, and converts the request into a DFI bus standard Request; the AXI bus bridge circuit 102 receives the access request of the AXI bus, and converts the request into a DFI bus standard request; the DFI bus arbitration circuit 103 receives the DFI bus standard output by the PLB bus bridge circuit 101 and the AXI bus bridge circuit 102 Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More