Connecting method and system for communication between rate configurable FPGA chips

A connection system and connection method technology, applied in FPGA communication and FPGA fields, can solve the problems of long verification period and low verification efficiency, achieve strong versatility and practicability, save costs, and shorten the design verification cycle.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Embodiments of the present invention are described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

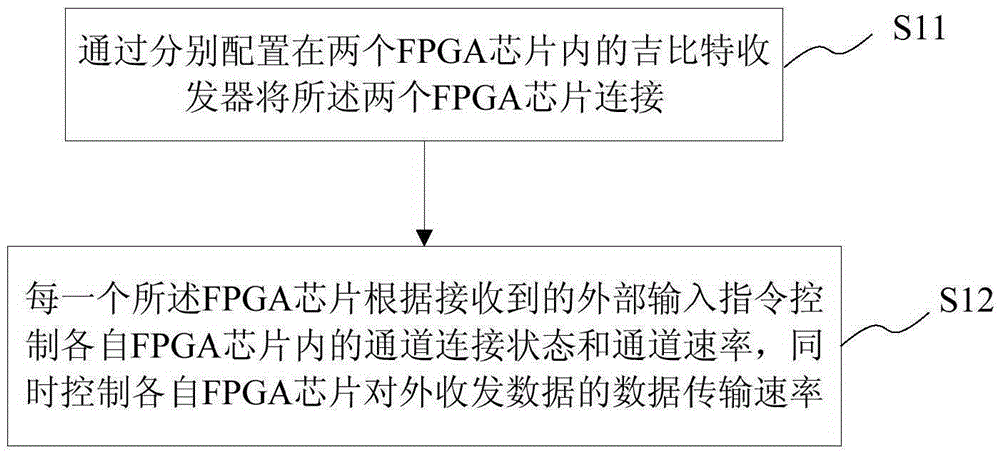

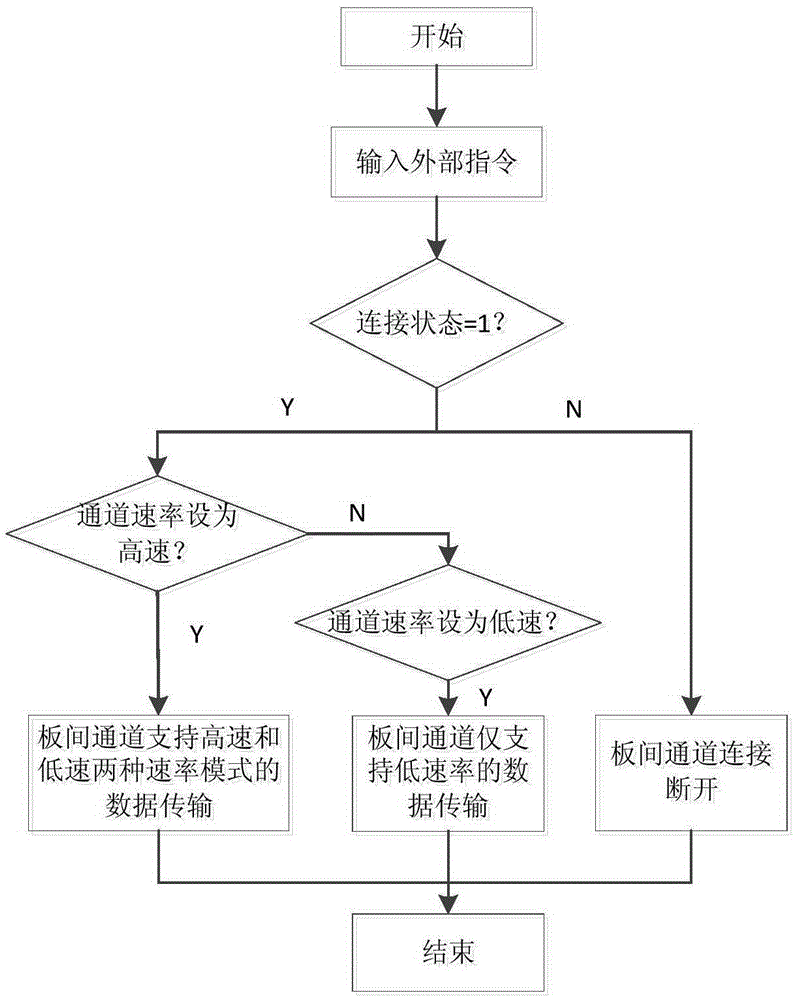

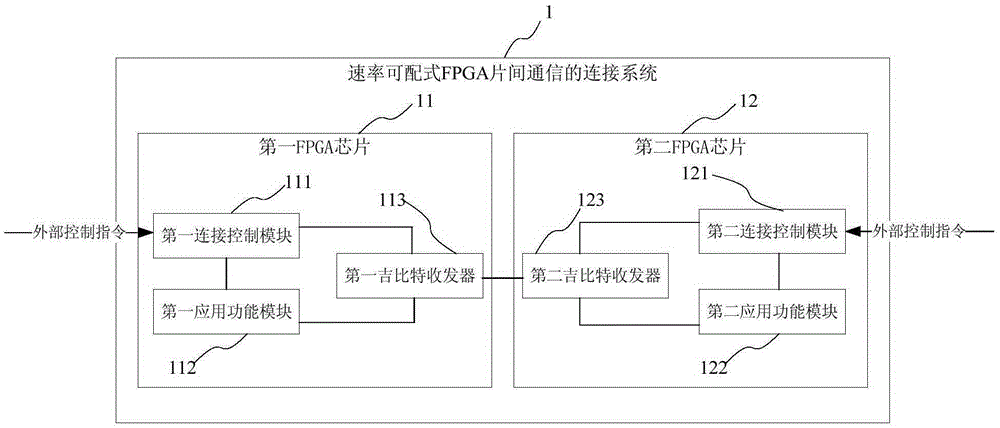

[0036] The purpose of this embodiment is to provide a rate-configurable FPGA inter-chip communication connection method and system, which are used to solve the problems of long FPGA testing and verification period and low verification efficiency in the prior art. The principle and implementation of a connection method and system for rate-configurable FPGA inter-chip communication of this embodiment will be described in detail below, so...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More