An automatic simulation test method for SOC chips based on image acceleration processing

A simulation test and chip technology, applied in electrical digital data processing, error detection/correction, detection of faulty computer hardware, etc., can solve problems such as slow comparison of results, low efficiency of the image processing module test process, and difficulty in locating error points.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 2

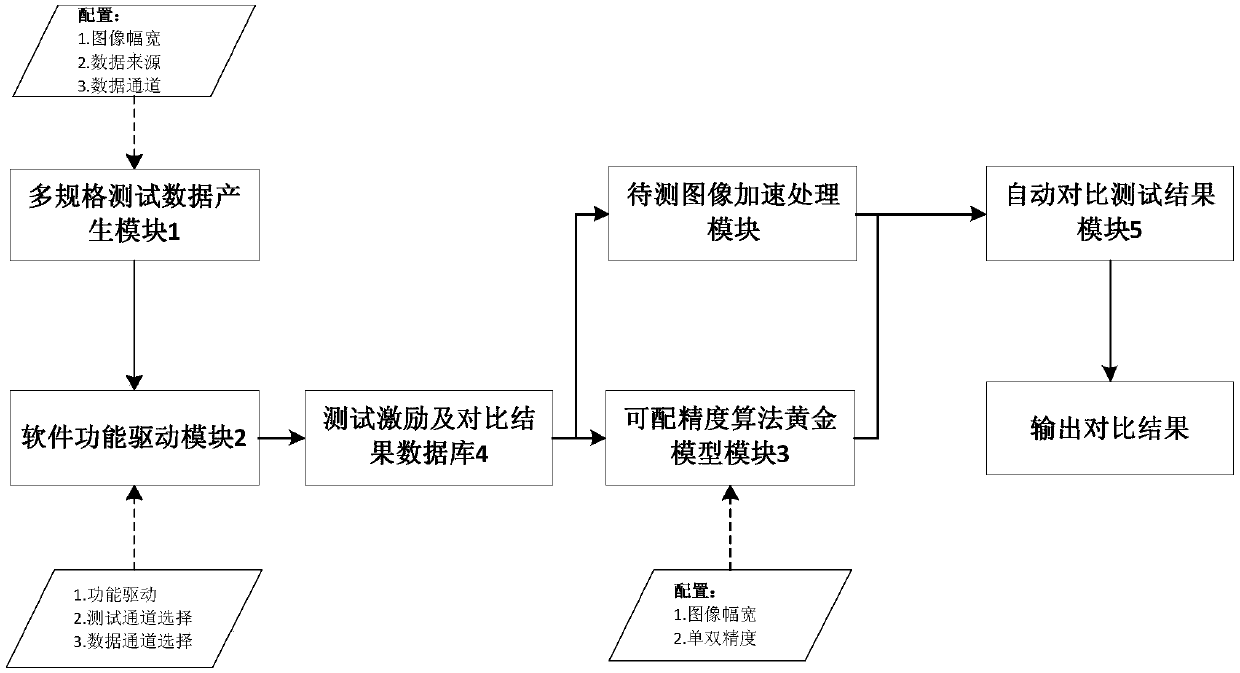

[0053] An SoC chip automatic simulation test system for image acceleration processing, including: multi-standard test data generation module 1, software function driver module 2, configurable precision algorithm golden model module 3, test incentive and comparison result database 4 and automatic comparison test Results module 5.

[0054] The function of the multi-standard test data generation module 1 is: generate image data of various widths, and generate test data in corresponding storage formats according to the bit widths of different storage areas of the SoC chip;

[0055] The functions of the software function driver module 2 are: perform driver configuration according to the functional requirements of the image acceleration processing module to be tested, select and configure linear or nonlinear correction, Gaussian, gradient or median filtering;

[0056] The function of module 3 of the golden model of configurable precision algorithm is: to construct the golden model o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More