Multilayer circuit board expansion and shrinkage coefficient obtaining method and manufacturing method of multilayer circuit board

A technology of expansion and contraction coefficient and acquisition method, which is applied in multilayer circuit manufacturing, printed circuit manufacturing, printed circuit, etc., can solve problems such as difficult alignment, achieve accurate expansion and contraction coefficient, and improve alignment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Embodiments of the present invention are described in detail below:

[0025] The multilayer circuit board expansion and contraction coefficient acquisition method of the present invention comprises the following steps:

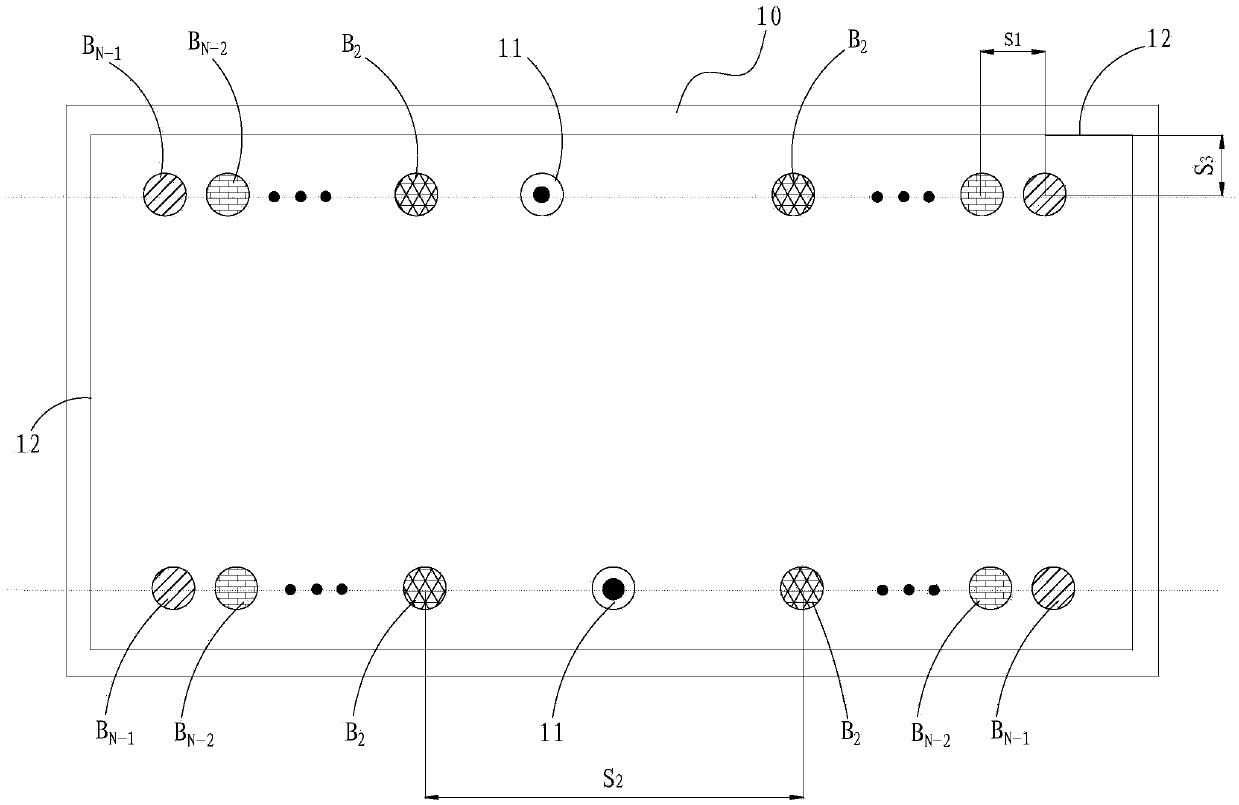

[0026] Provide N-2 inner boards and outer boards 10 to be laminated, add targets on the four top corners of each inner board, and make the targets between the inner boards staggered; please refer to figure 1 , figure 1 A schematic structural diagram of the projection of the targets on the N-2 inner boards onto the outer board 10 is shown. After the targets between the boards are staggered and set, the N-2 inner boards can be drilled by the X-Ray target drilling machine. The target position information on the layer boards is obtained at the same time, so the expansion and contraction coefficients of the inner layer boards can be obtained according to the target position information on each inner layer board.

[0027] The N-2 inner layer boards and the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More