Alignment mark for contact hole alignment and forming method thereof

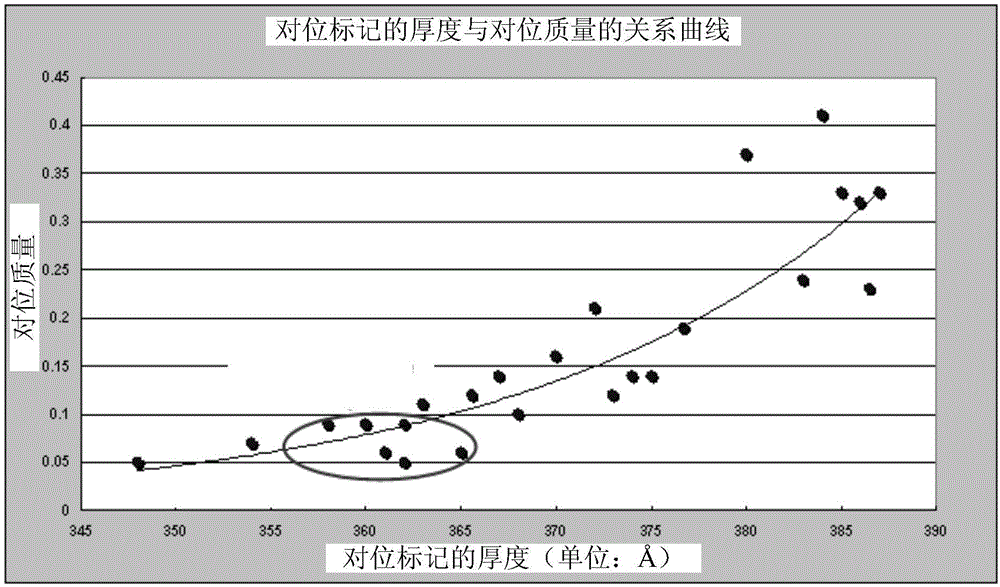

An alignment mark and contact hole technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of decreased alignment quality, difficult to meet requirements, small thickness, etc., to improve alignment quality and increase effective thickness. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] An embodiment of the present invention provides a method for forming an alignment mark (mark) for contact hole (CT) alignment, and the method includes the following steps:

[0041] Provide semiconductor substrates;

[0042] forming shallow trench isolation on both sides of the region of the semiconductor substrate where an alignment mark for contact hole alignment is to be formed;

[0043] An alignment mark is formed on a region of the semiconductor substrate where an alignment mark for contact hole alignment is to be formed, wherein the alignment mark has the same material as the semiconductor substrate.

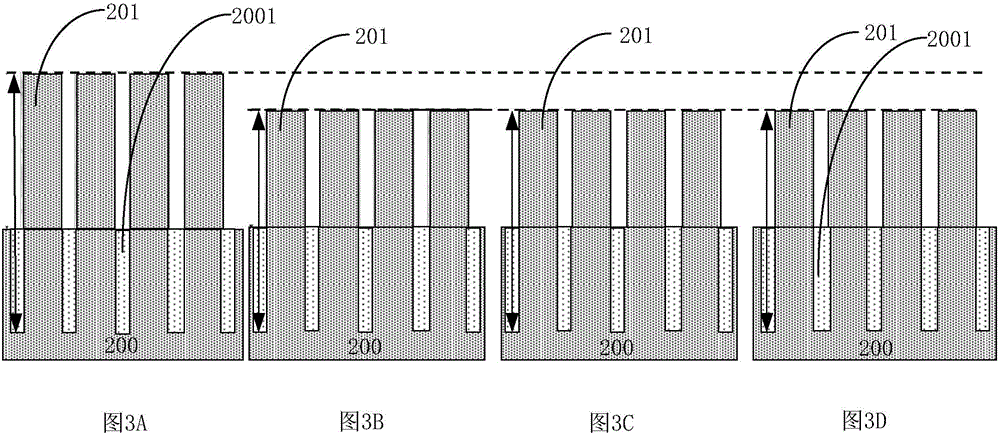

[0044] in, image 3 A specific example of a method for forming an alignment mark for contact hole alignment according to an embodiment of the present invention is shown. Such as image 3 As shown, this specific example includes the following steps:

[0045] Step A1: Provide a semiconductor substrate 200, and form shallow trench isolation (STI) 2001 on both sides of...

Embodiment 2

[0067] An embodiment of the present invention provides an alignment mark for contact hole alignment, which is manufactured by the method described in the first embodiment above.

[0068] Such as Figure 5 As shown, the alignment mark 201 used for contact hole alignment in the embodiment of the present invention is formed on the semiconductor substrate 200, wherein the alignment mark 201 has the same material as the semiconductor substrate 200, and the inside of the semiconductor substrate 200 Shallow trench isolations 2001 located on both sides of the alignment mark 201 are formed.

[0069] Exemplarily, the material of the alignment mark 201 may be polysilicon or other suitable materials. The semiconductor substrate 200 may be a silicon substrate or other suitable substrates. The material of the shallow trench isolation (STI) 2001 can be silicon oxide or other suitable materials.

[0070] Wherein, the alignment mark 201 can be formed in the same process as the dummy gate of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More