Multistage serial-parallel conversion circuit

A technology for converting circuits and circuits, which is applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., which can solve the problem of large number of logic, large power consumption of shift register structure, and limitation of maximum operating speed, etc. problem, to achieve the effect of logic reduction, reduction of the number of triggers, and increase of reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

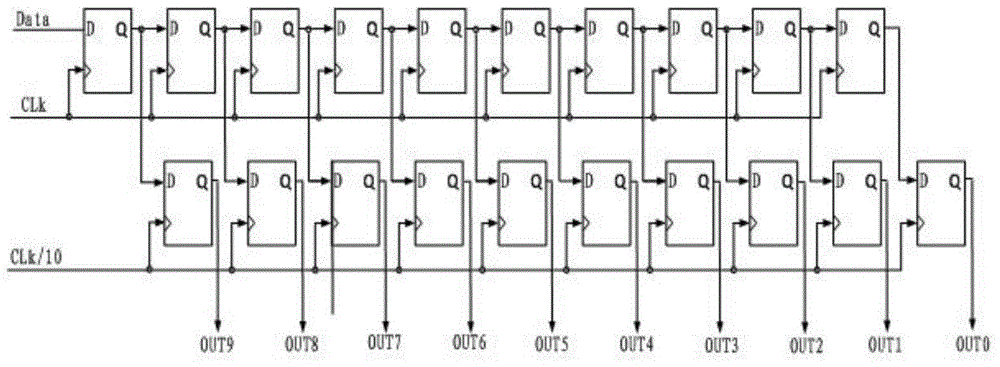

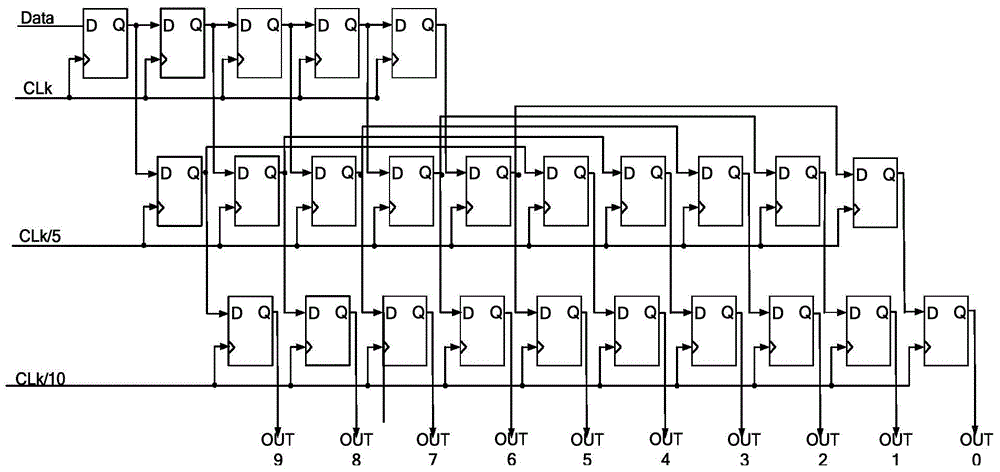

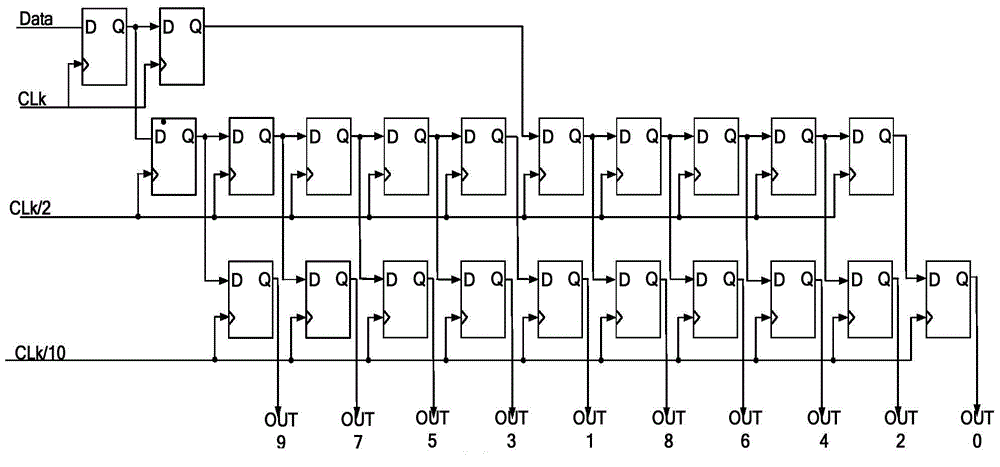

[0035] figure 2 It is a circuit diagram of a multi-stage serial-to-parallel converter in Embodiment 1 of the present invention, and the multi-stage serial-to-parallel converter circuit can be applied in a serializer / parallelizer interface.

[0036] Such as figure 2 As shown, the circuit of the multi-stage serial-to-parallel converter includes: at least three-stage D flip-flop groups;

[0037] The first-level D flip-flop group includes n cascaded D flip-flops (in this embodiment, 5 cascaded D flip-flops are taken as an example, that is, n=5), and the n cascaded D flip-flops have the same first clock signal CLK 1 , when the first clock signal CLK 1 When arriving, trigger all D flip-flops of the first-level D flip-flop group; The second-level D flip-flop group includes n×m cascaded D flip-flops (in this embodiment, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More