Processing layer data packet generation method, device and pci Express system

A technology for generating devices and data packets, applied in electrical digital data processing, instruments, etc., can solve problems such as increasing TLP transmission delay, achieve the effects of reducing circuit resource overhead, ensuring transmission bandwidth, and reducing transmission delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

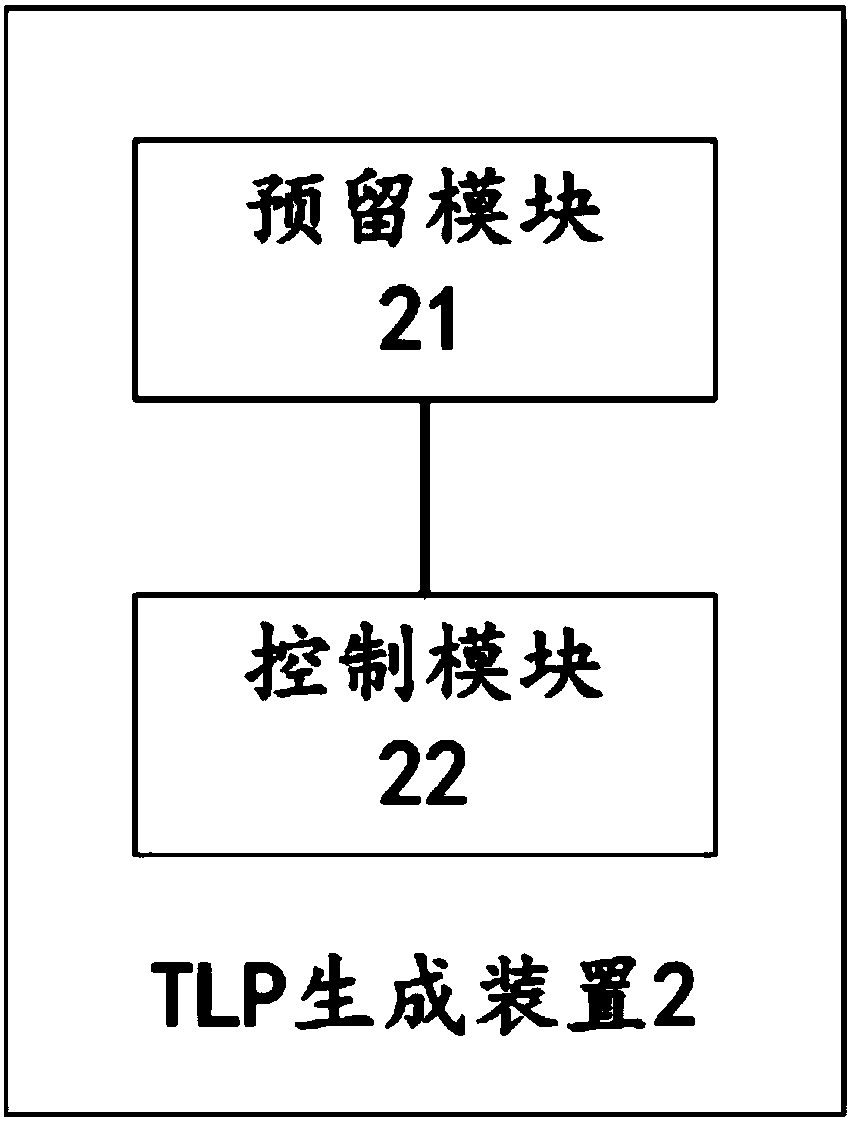

[0029] figure 2 A schematic structural diagram of the TLP generation device provided in the first embodiment of the present invention, consisting of figure 2 It can be seen that in this embodiment, the TLP generation device 2 provided by the present invention includes:

[0030] The reservation module 21 is used to control the processing layer to generate an initial TLP. The initial TLP includes a reserved field, a header field, a data field and a summary field, and the reserved field includes a blank start flag field, a sequence number field, an LCRC field, and an end flag field ;

[0031] The control module 22 is configured to control data link layer and physical layer calculations and fill in reserved fields to generate a final TLP.

[0032] In some embodiments, the control module 22 in the above embodiments is used to control the physical layer to fill in the start flag field and the end flag field, control the data link layer to fill in the sequence number field, and c...

no. 2 example

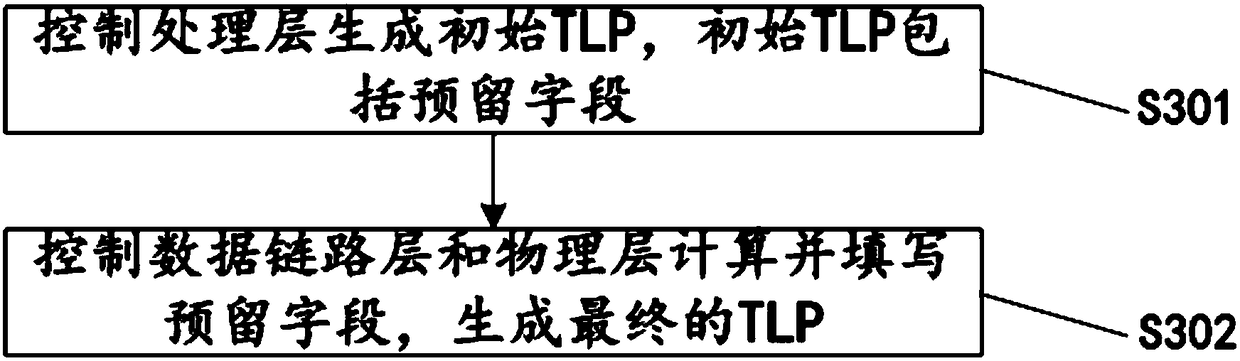

[0039] image 3 The flow chart of the TLP generation method that the second embodiment of the present invention provides, by image 3 It can be seen that, in this embodiment, the TLP generation method provided by the present invention includes the following steps:

[0040] S301: The control processing layer generates an initial TLP. The initial TLP includes a reserved field, a header field, a data field, and a summary field. The reserved field includes a blank start flag field, a sequence number field, an LCRC field, and an end flag field;

[0041] S302: Control the data link layer and the physical layer to calculate and fill in reserved fields to generate a final TLP.

[0042] In some embodiments, calculating and filling in the reserved fields in the foregoing embodiments to generate the final TLP includes: controlling the physical layer to determine and fill in the start flag field and the end flag field, controlling the data link layer to determine and fill in the sequence...

no. 3 example

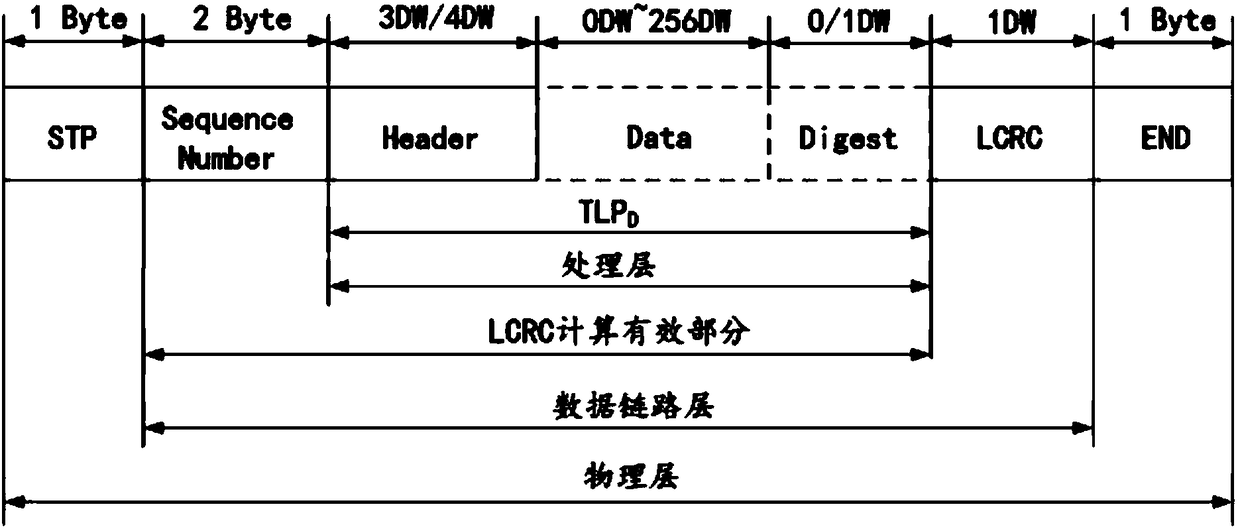

[0052] The LCRC value of the TLP in the existing PCI Express is added to the end mark of the TLP after the calculation of the LCRC circuit is completed, and the TLP shift alignment operation needs to be performed in this way, which will increase the transmission delay of the TLP; in the existing PCI Express When the LCRC circuit in PCI Express processes back-to-back TLP, two same LCRC circuits are used for calculation, and the resource overhead of the LCRC circuit is very large; when the LCRC circuit in the existing PCI Express processes back-to-back TLP, the internal data bit width is large, such as 128bit bit width , there is no published solution for the LCRC circuit.

[0053] In order to solve the above problems, the present embodiment reserves the position of the LCRC value and other additional values in the TLP in advance when processing the layer package TLP. Since the bit width of the TLP start mark and the TLP end mark are not fixed, the LCRC circuit needs It consis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More