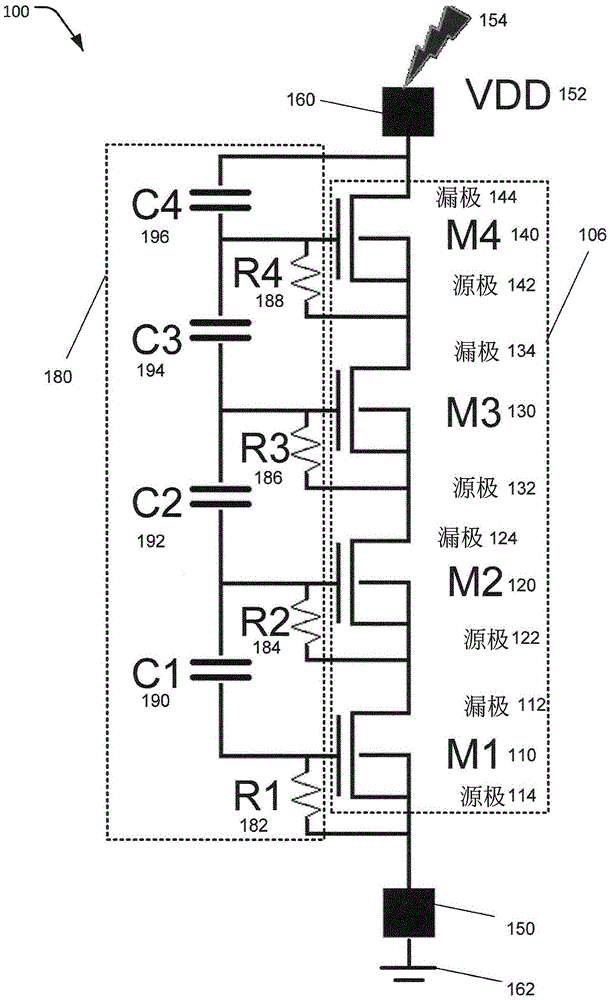

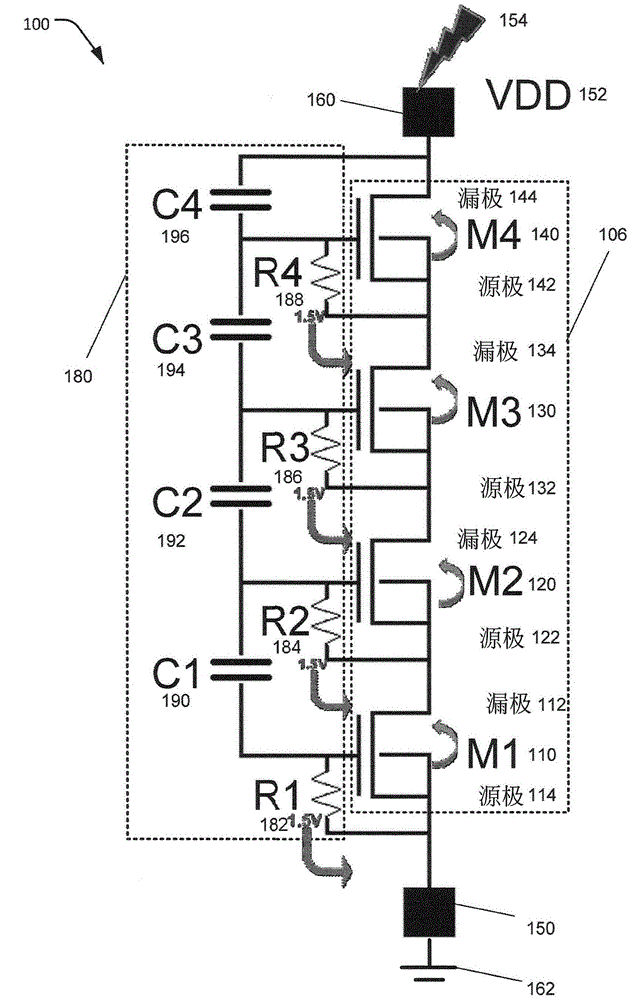

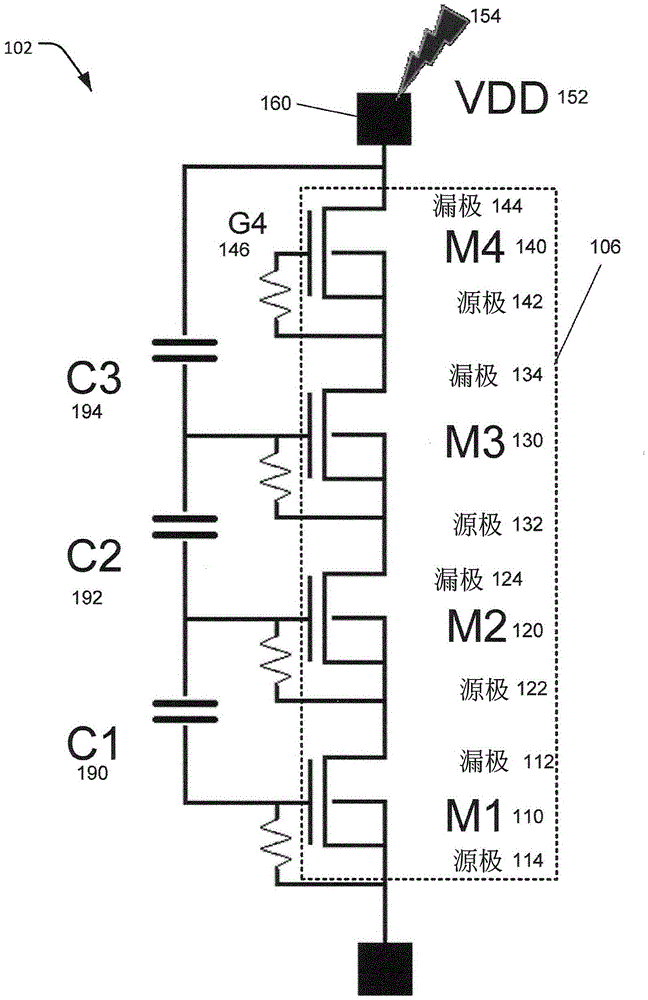

RC-stacked MOSFET circuit for high voltage (HV) electrostatic discharge (ESD) protection

A voltage and control circuit technology, applied in the field of integrated circuit devices, can solve problems such as inability to reach ESD devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The invention is set forth in the claims which are believed to be characteristic of the novel features. However, the invention itself and its preferred mode of use, objects and advantages thereof will be best understood by reference to the following detailed description of illustrative specific embodiments when read with the accompanying drawings. The functions of the various circuits, devices, or components described herein may be implemented as hardware (including discrete components, integrated circuits, and system-on-chips (SoCs)), firmware (including application-specific integrated circuits and programmable chips), and / or software or The combination depends on the application requirements.

[0027] Similarly, the functions used to form the mechanical elements, components and / or assemblies for assembling modules, subassemblies and assemblies according to the device structure can be performed using various materials and coupling techniques, depending on the applicati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More