Self-adaptive testing method and device of CPU cache memory

A test method and memory technology, applied in the direction of static memory, instrument, etc., can solve the problem of inability to adjust the EMA of different chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

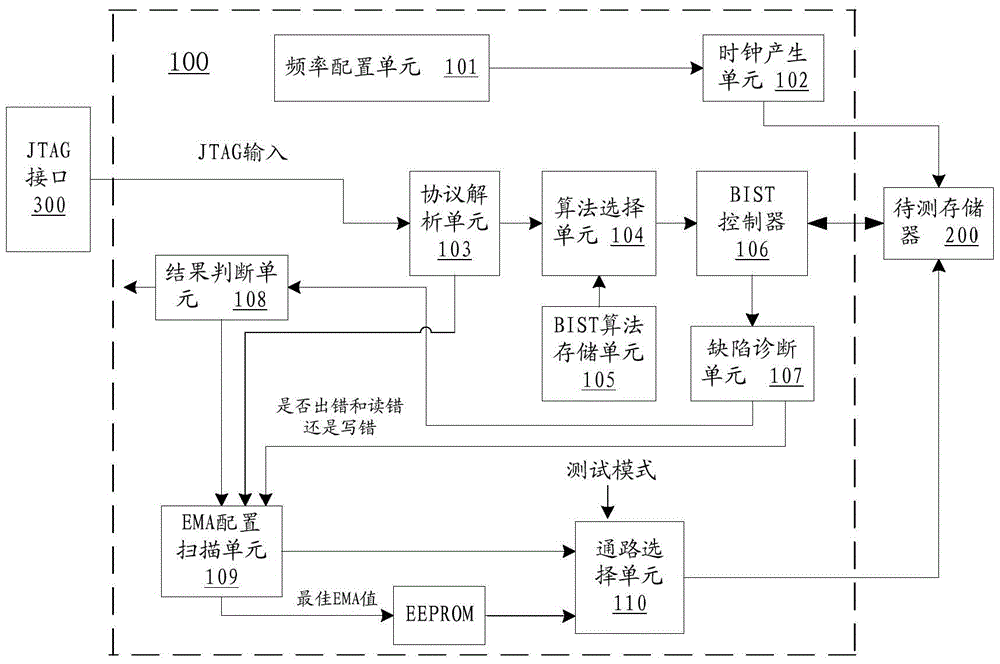

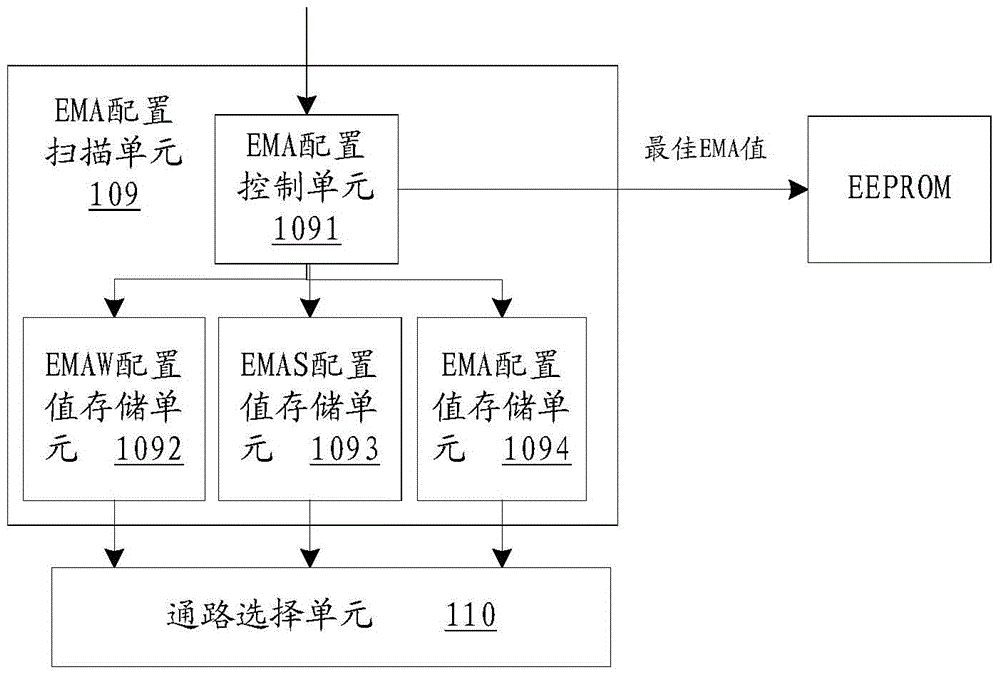

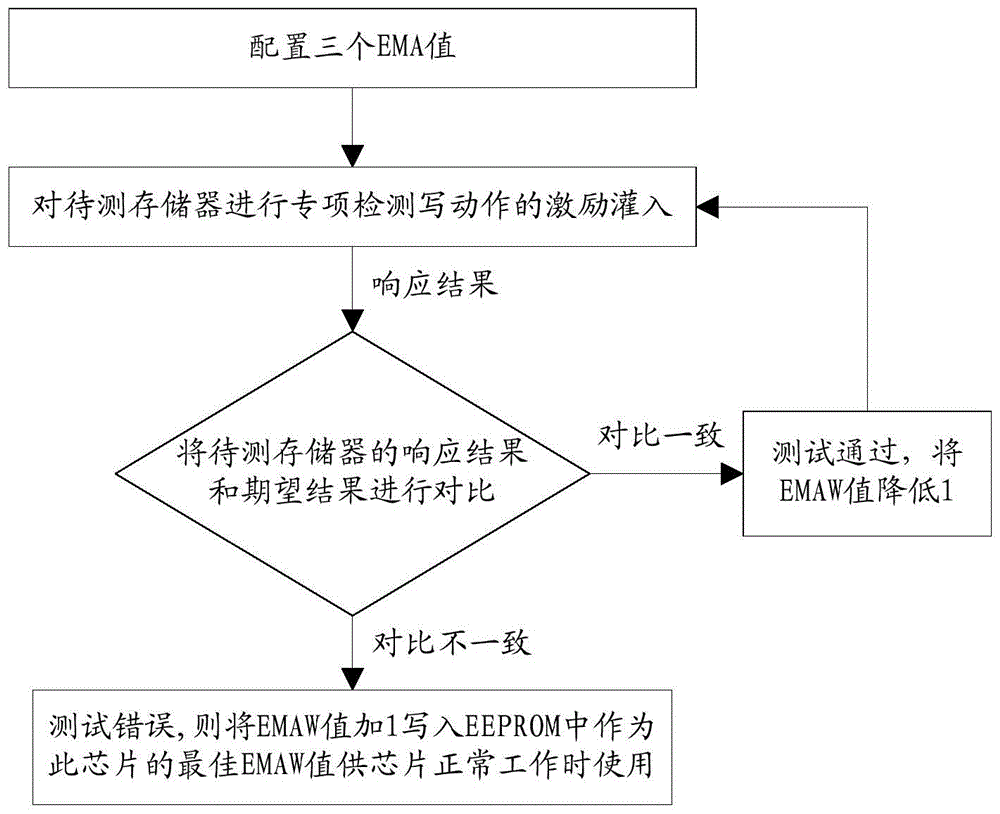

[0056] The self-adaptive testing method of CPUcache memory of the present invention is to set the frequency configuration corresponding to the test target frequency earlier before the test, and the frequency usually set is exactly the highest frequency that the storage unit may run to in practical applications; after starting the test, pass The jtag interface is poured into the bist start command; the jtag command is converted into a direct control signal after protocol analysis; the bist test process with EMA scanning is carried out through the direct control signal, if the best EMA is found in the bist test process, then It is judged that the test is passed, and the internal EEPROM will store the best EMA configuration value at this frequency for use when the chip enters the normal working mode; otherwise, it is judged that the test has failed, and the chip is classified as a chip that does not meet the requirements.

[0057] The adaptive testing method of the CPUcache memory...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More