Method of realizing PTP nanosecond precision based on hardware time stamp

A hardware timestamp and nanosecond-level technology, applied in electrical components, digital transmission systems, transmission systems, etc., can solve problems such as low precision, capacity limitations, and transmission distance limitations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

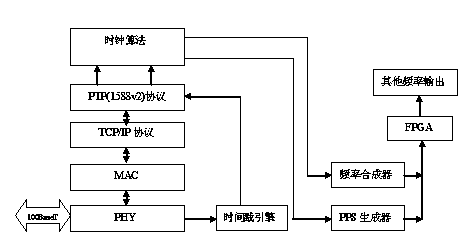

[0036] The present invention is an FPGA-based clock adjustment and phase-locking technology, which meets the requirements for clock accuracy of the time and equipment of subway systems, high-speed rail systems, power systems, transportation systems and other systems. Attached below figure 1 The present invention will be explained in detail.

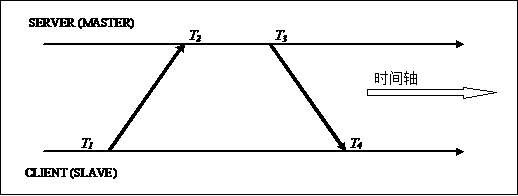

[0037] The technical problem to be solved by the present invention is to solve the time calibration problem of the PTP slave clock (or PTP client) to improve the accuracy of the recovery time of the PTP slave clock, and a PTP time recovery algorithm is developed.

[0038] The accuracy of PTP depends on the accuracy of the obtained time stamp. Some traditional PTP implementations based on software time stamp can only achieve sub-sub-sub-sub-sub-sub-sub-micron accuracy. This paper proposes a method to realize PTP nanosecond precision based on hardware time stamp.

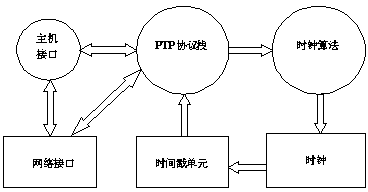

[0039] This method mainly includes PTP protocol stack, clock algorithm, network in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More