Network-on-chip interconnection method and device

An on-chip network and interconnection system technology, applied in the field of on-chip network interconnection methods and devices, can solve problems such as low access efficiency and long frame length, and achieve the effects of being suitable for large-scale popularization and application, easy to implement, and ingenious in design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0053] As we all know, cognitive power line carrier communication is a technology that uses the knowledge of the power line channel environment to improve the efficiency of power line carrier communication. Using this technology, it is possible to detect channel noise and dynamically allocate communication resources according to the detection results. The goal of stabilizing communication probability and improving communication efficiency. Due to the high flexibility of cognitive power line carrier communication, on the one hand, the baseband processor in the communication chip is required to have strong computing power; on the other hand, the baseband processor is also required to support various types of calculations, such as Figure 4 As shown, the embodiment of the present invention provides a schematic diagram of one of the cognitive power line carrier communication chips. P1, ..., P16 in the figure are various types of processors, and R1, ..., R16 are different types of p...

Embodiment 2

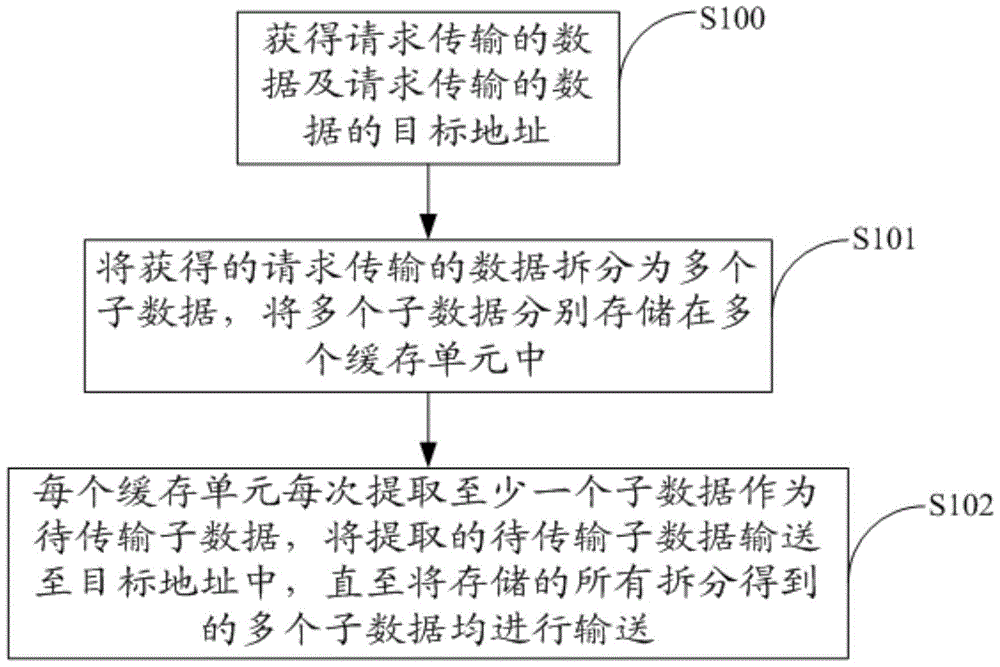

[0084] Such as Figure 8 As shown, the embodiment of the present invention provides an on-chip network interconnection device, including a plurality of cache units 600 for storing data; a splitting unit 601 for obtaining the data requested for transmission and the target address of the data requested for transmission , split the obtained data requested for transmission into a plurality of sub-data, and store the plurality of sub-data in the plurality of cache units 600 respectively; each cache unit 600 in the plurality of cache units 600 uses Each time extracting at least one sub-data from a plurality of stored sub-data as the sub-data to be transmitted, transporting the extracted sub-data to be transmitted to the target address of the data requested for transmission, until all the stored sub-data Multiple sub-data obtained by splitting are all sent.

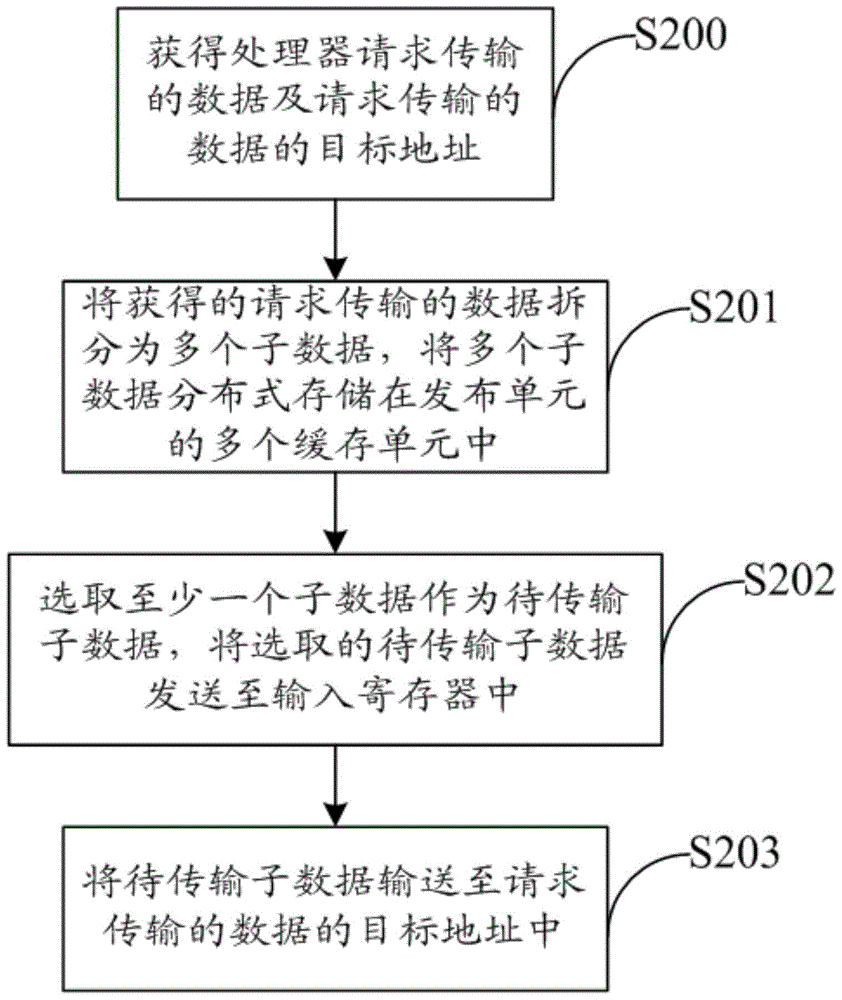

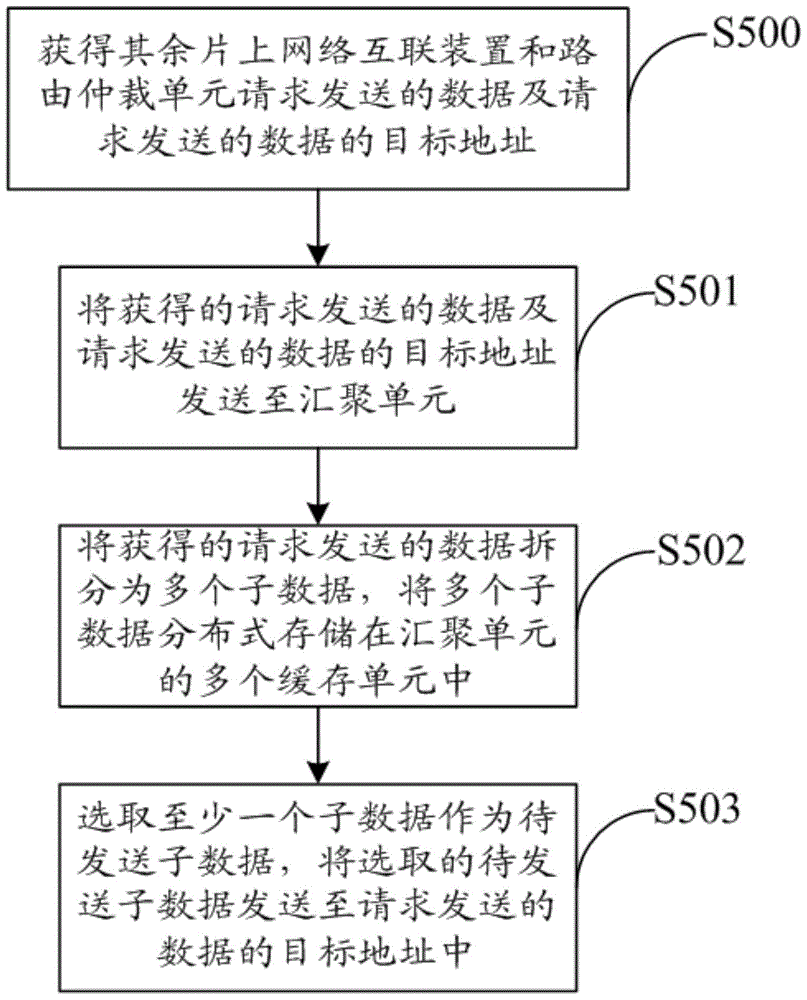

[0085] Based on the above structure, such as Figure 9 As shown, this embodiment provides one of the implementation solution...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More