Trigger of high speed and low power consumption

A flip-flop and low power consumption technology, applied in the direction of reducing power consumption, reducing power of field effect transistors, reducing power through control/clock signals, etc., can solve inapplicable, large on-resistance, and parasitic capacitance at the output of the flip-flop Large and other problems, to achieve the effect of no static power consumption and increased speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings; it should be understood that the preferred embodiments are only for illustrating the present invention, rather than limiting the protection scope of the present invention.

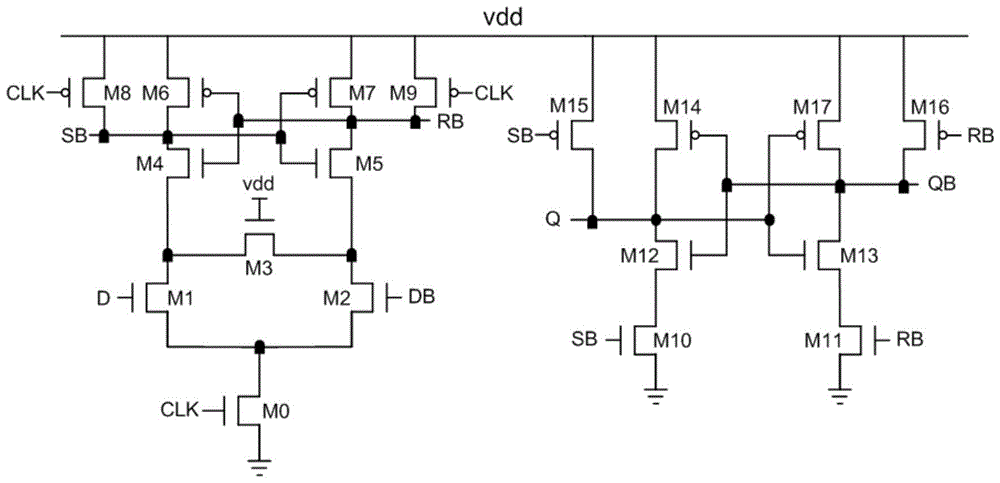

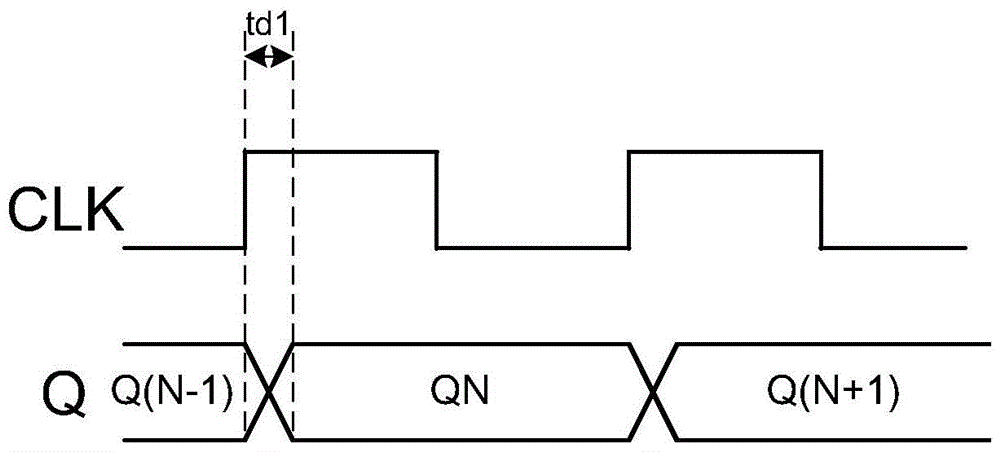

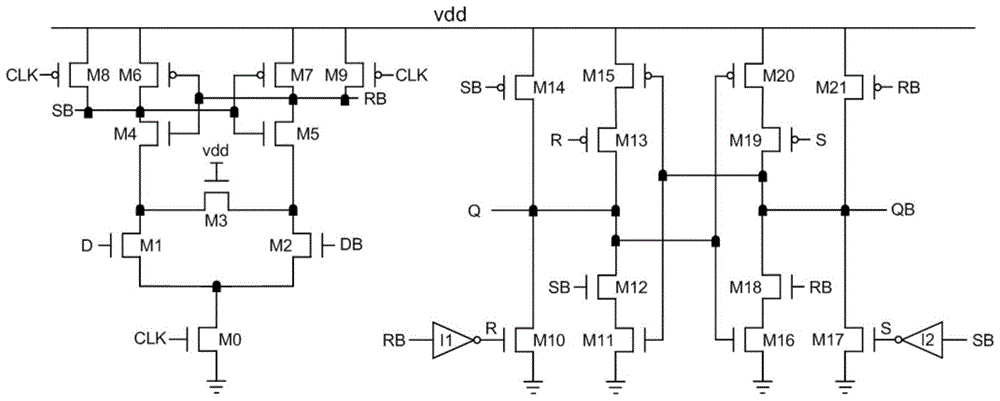

[0028] The schematic diagram of the structure of the high-speed low-power flip-flop proposed by the present invention is as follows: Figure 7 As shown, a high-speed low-power flip-flop includes a control signal generating circuit, an enabling unit, and a latch structure. The latch structure includes a first input terminal, a second input terminal, a first output terminal, and a second input terminal. Two output terminals, a first enable terminal, a second enable terminal and a ground terminal, the enable unit includes a first enable circuit and a second enable circuit, the output signal X of the control signal generating circuit and the external control The signal D is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More