A double grid line array substrate, test method, display panel and display device

A technology of array substrates and double gate lines, which is applied in semiconductor/solid-state device testing/measurement, semiconductor devices, electrical components, etc., can solve problems such as defective pixels, failure to detect, and increased costs, so as to improve pixel detection rate, Improve product quality and improve the effect of product quality control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

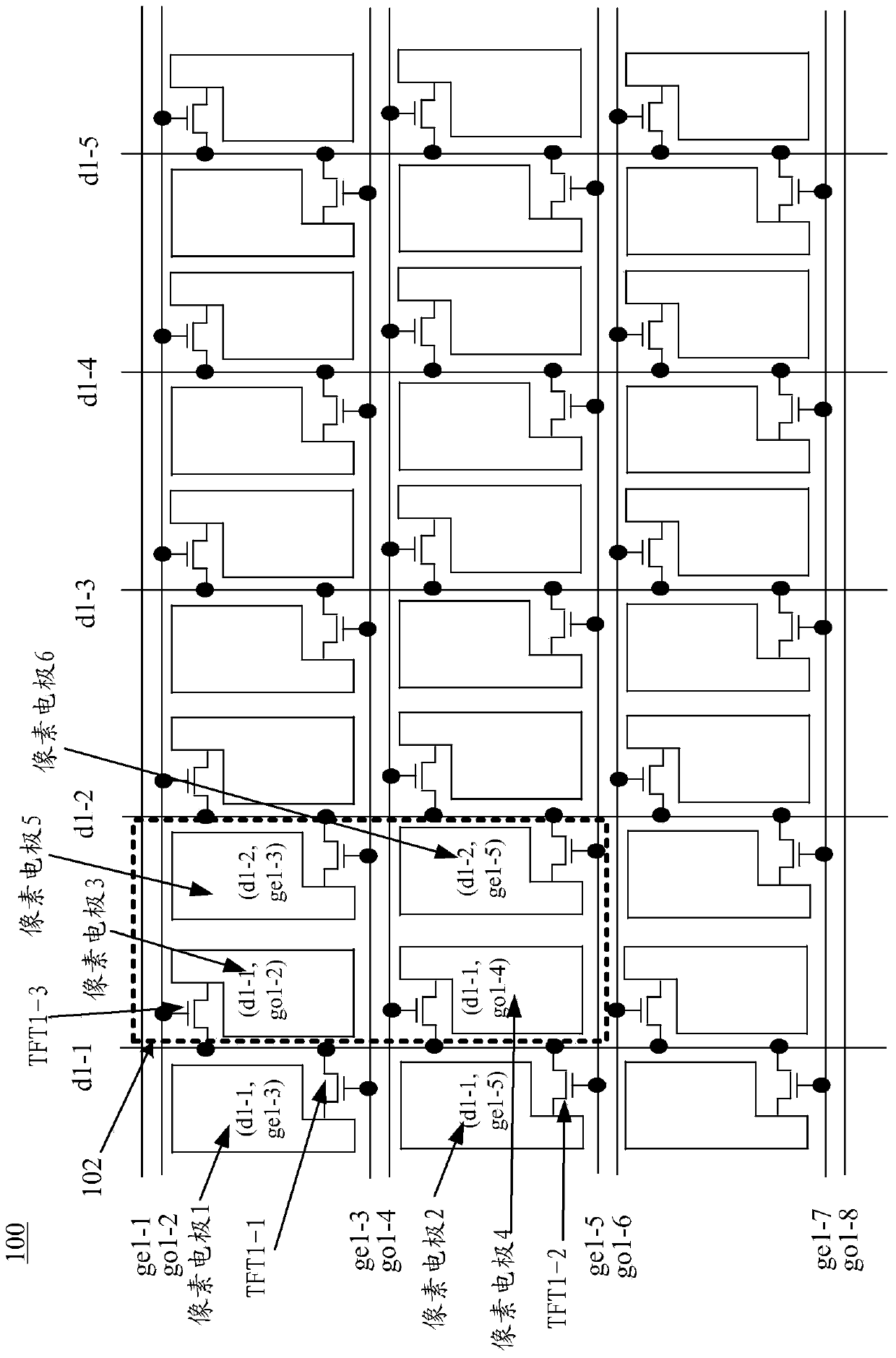

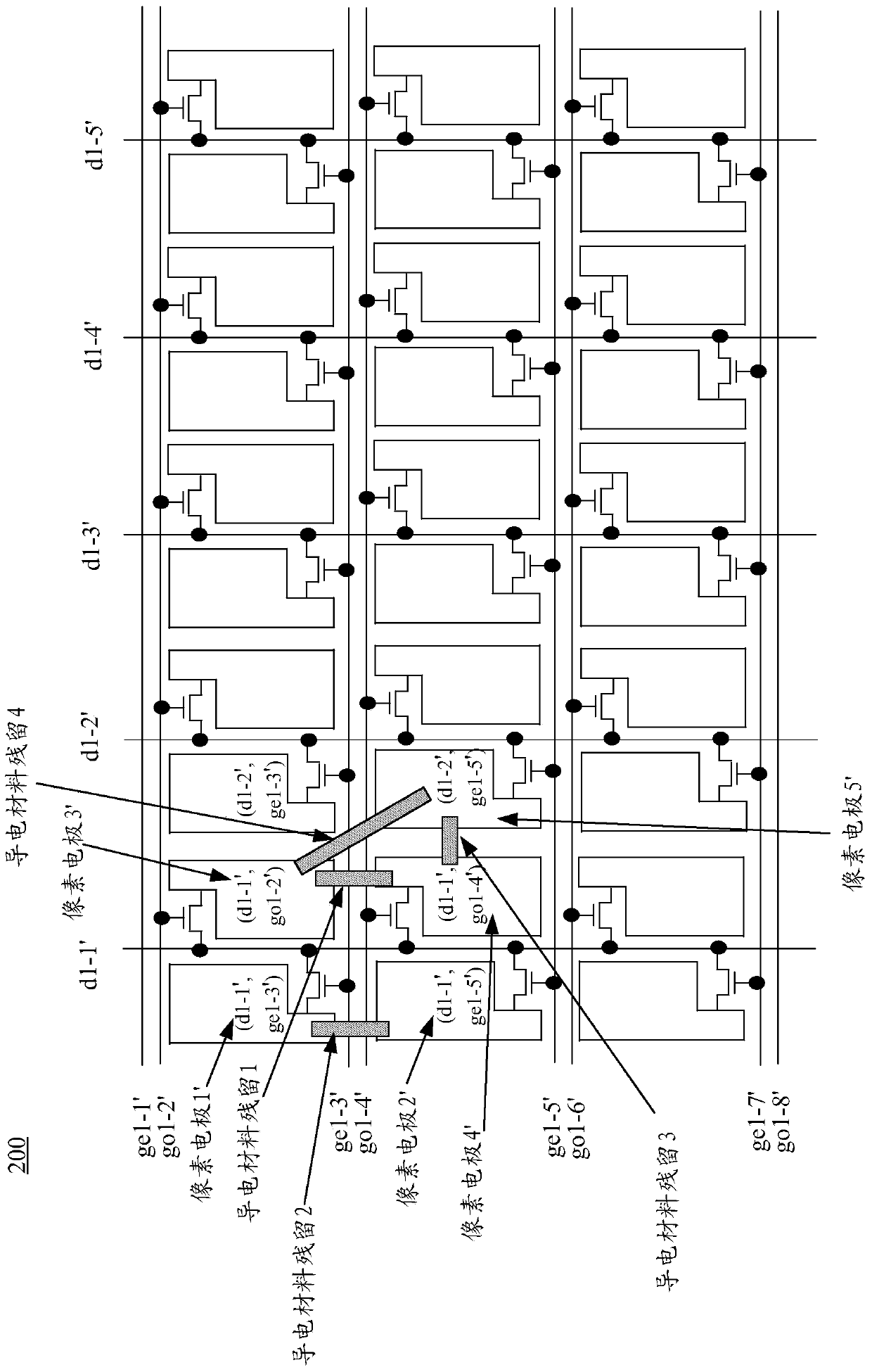

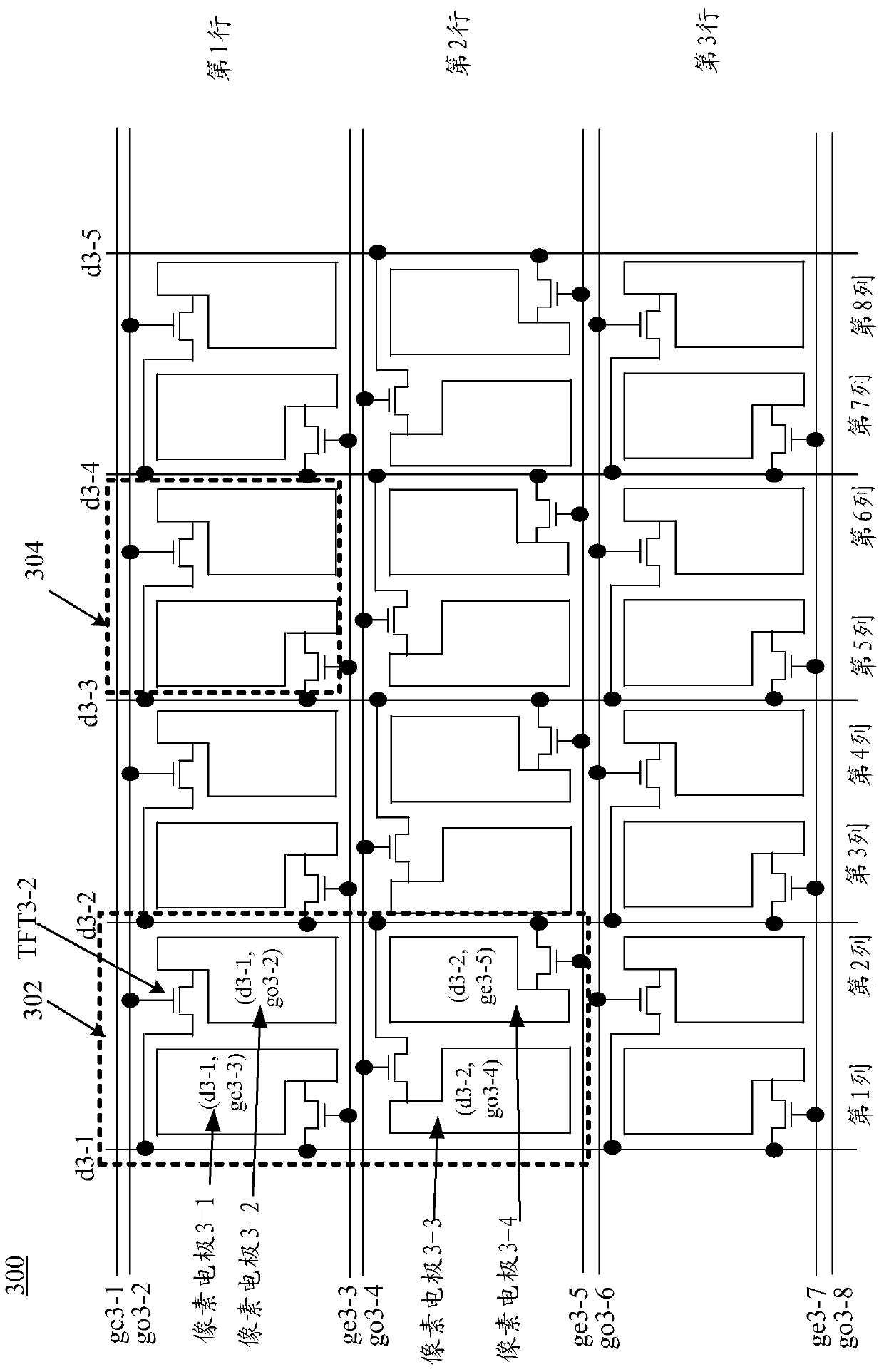

[0033] Embodiments of the present disclosure are described below with reference to the accompanying drawings. In the following description, numerous specific details are set forth in order to enable those skilled in the art to more fully understand and practice the present disclosure. It will be apparent, however, to one skilled in the art that the present disclosure may be practiced without some of these specific details. Furthermore, it should be understood that the disclosure is not limited to the particular embodiments described. Rather, it is conceivable to implement the present disclosure in any combination of the features and elements described below, regardless of whether they relate to different embodiments. Accordingly, the following aspects, features, embodiments and advantages are by way of illustration only and should not be considered elements or limitations of the claims unless explicitly stated in the claims.

[0034] As used herein, a gate line including "ge...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More