A recovery circuit for improving the temperature instability of negative bias voltage of sslc level conversion circuit

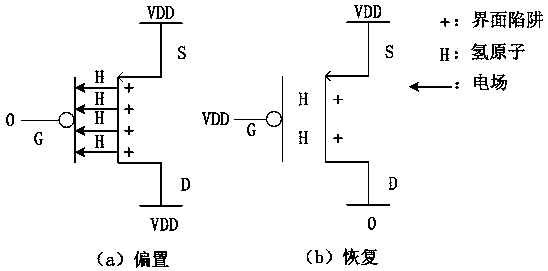

A technology of negative bias temperature and conversion circuit, which is applied in the direction of logic circuit, logic circuit connection/interface arrangement, logic circuit coupling/interface using field effect transistor, etc., which can solve the problem of affecting the performance and service life of PMOS transistors, level conversion Circuit can not work properly and other problems, to achieve the effect of improving static power consumption, suppressing negative drift, and suppressing leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

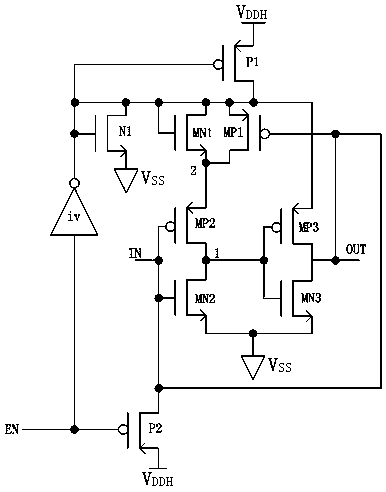

[0023] Hereinafter, the present invention will be described in detail with reference to the accompanying drawings and the embodiments.

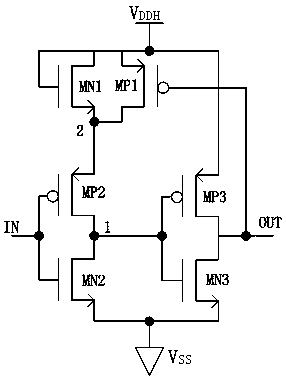

[0024] Reference figure 2 with image 3 As shown, a recovery circuit for improving the negative bias temperature instability of an SSLC level conversion circuit, the circuit includes an SSLC level conversion circuit and an NBTI effect recovery unit;

[0025] The SSLC level conversion circuit includes PMOS transistors MP1, MP2, MP3 and NMOS transistors MN1, MN2, MN3. The sources of MP1 and MP3 are connected, and the gate of MP1 is connected to the drain of MP3 and MN3, respectively. The drain is connected to the source of MP2 and MN1, the gate of MP2 is connected to the gate of MN2, and the drain of MP2 is connected to the drain of MN2 and the gate of MP3, respectively;

[0026] The gate and drain of the MN1 are connected to the source of MP1, and the source of the MN2 is connected to the low-level terminal V SS , The gate of MN2 is connected to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More